ARM Cortex-M3/M4 权威指南 笔记【一】技术综述

一、Cortex-M3/M4 处理器的一般信息

1.1 处理器类型

ARM Cortex-M 为 32 位 RISC(精简指令集)处理器,其具有:

- 32位寄存器

- 32位内部数据通路

- 32位总线接口

除了 32 位数据,Cortex-M 处理器(以及其他任何 ARM 处理器)还可以高效地处理 8 位和 16 位数据。Cortex-M3/M4 处理器还支持涉及 64 位数据的多种运算(如乘和累加)。

Cortex-M3/M4 处理器都具有三级流水线(取指、译码和执行),它们都基于哈佛总线架构,取指令和数据访问可以同时执行。

ARM Cortex-M 处理器的存储器系统使用 32 位寻址,地址空间最大为 4GB。存储器映射是一致的,这就意味着尽管总线接口有多个,4GB 存储器空间却只有一个。存储器空间包括程序代码、数据、外设以及处理器内的调试支持部件。

与其他任何 ARM 处理器相同,Cortex-M 处理器基于一种加载一存储架构。这也就意味着数据需要从存储器中加载和处理后,使用多个单独的指令写回存储器。例如,要增加 SRAM 中存储的数据值,处理器需要使用一条指令从 SRAM 中读出数据,并且将数据放到处理器的寄存器中,然后使用第二条指令增加寄存器中的数据值,最后使用第三条指令将数值写回存储器。处理器内部的寄存器细节一般被称作编程模型。

1.2 处理器架构

处理器只是微控制器芯片中的一部分。存储器系统、外设和各种接口特性由微控制器供应商开发。因此,从低成本的微控制器产品到高端的多处理器产品,可以发现 Cortex-M 处理器用在诸多设备中,不过这些设备的架构相同。对于 ARM 处理器,架构一般指两个方面:

架构:指令集架构(ISA)编程模型(对软件可见)以及调试方法(对调试器可见)。

微架构:接口信号、指令执行时序以及流水线阶段等实现相关的细节,微架构为处理器设计相关的。

对于多年来发布的不同 ARM 处理器,ARM 架构存在多个版本。例如,Cortex-M3/M4 处理器都基于 ARMv7-M 架构。一个指令集架构可以包含多个微架构设计,如不同数量的流水线阶段和不同类型的总线接口等。

要了解 ARMv7-M 架构的细节,可以参考 ARMv7-M 架构参考手册(也被称作 ARMv7-MARM)的内容。该文献包括:

- 指令集细节

- 编程模型

- 异常模型

- 存储器模型

- 调试架构

待补充...

1.3 指令集

Cortex-M 处理器使用的指令集名为 Thumb (其中包括16 位 Thumb 指令和更新的 32 位 Thumb 指令),Cortex-M3/M4 处理器用到了 Thumb-2 技术,它允许 16 位和 32 位指令的混合使用,以获取更高的代码密度和效率。

ARM7TDMI 等经典的 ARM 处理器具有两种操作状态:

- 32 位的 ARM 状态

- 16 位的 Thumb 状态

在 ARM 状态中,指令是 32 位的,内核能够以很高的性能执行所有支持的指令。而对于 Thumb 状态,指令是16位的,这样可以得到很好的代码密度,不过 Thumb 指令却不具有ARM 指令的所有功能,要完成特定的操作,可能需要更多的指令。

要同时得到两者的优势,许多用于经典 ARM 处理器的应用程序混合使用了ARM 和 Thumb 代码。不过这种混合编码的方式并不是非常理想,它会带来状态间切换的开销(执行时间和指令数),而且两个状态的分离还增加了软件编译过程的复杂度,对于不是很熟练的开发人员来说,优化代码更加困难。

随着 Thumb-2 技术的引人,Thumb 指令被扩展为支持 16 位和 32 位两种解码方式,现在,无须在两个不同操作状态间切换就可以满足所有的处理需求。事实上,Cortex-M 处理器根本不支持 32位的 ARM 指令甚至中断处理都可以完全在 Thummb 状态中

- 无状态切换开销,节省执行时间和指令空间。

- 无须指定源文件中的 ARM 状态或 Thumb 状态,

- 开发软件也更容易。在获得最佳的代码密度和效率的同时,还能很容易地达到高性能。

- 利用 Thumb-2 技术,与 ARM7TDMI 等经典处理器相比,Thumb 指令集已经得到很大的扩展。注意,尽管所有的 Cortex-M 处理器都支持 Thumb-2 技术,它们实现的 Thumb ISA 子集不尽相同。

| 指令组 | Cortex-M0、M1 | Cortex-M3 | Cortex-M4 | 具有 FPU 的 Cortex-M4 |

| 16 位 ARMv6-M 指令 | • | • | • | • |

| 32 位间接跳转链接指令 | • | • | • | • |

| 32 位系统指令 | • | • | • | • |

| 16 位ARMv7-M 指令 | • | • | • | |

| 32 位ARMv7-M 指令 | • | • | • | |

| DSP 扩展 | • | • | ||

| 浮点指令 | • |

有些 Thumb 指令集中定义的指令在当前的 Cortex-M 处理器中是不支持的,如协处理器指令(尽管可能会增加经过存储器映射的独立的数据处理引擎)。同样,有些其他的经典 ARM 处理器中的Thumb 指令也不再支持了,如带有立即数的跳转链接并交换状态(BLX)(用于将处理器状态从Thumb切换到ARM)、几个修改处理器状态指令(CPS)以及 SETEND(端设置)指令,它们都是随着架构 v6 引人的。

1.4 模块框图

从较高的层级来看,Cortex-M3和Cortex-M4是非常相似的。尽管它们在内部数据通路设计上存在巨大差异,处理器的一些部分还是相似的,如取指缓冲,部分指令译码和执行阶段以及 NVIC。另外,“内核”层级外的部件基本上是相同的。

Cortex-M3/M4 处理器包含处理器内核、嵌套向量中断控制器(NVIC),SysTick 定时器以及可选的浮点单元(用于 Cortex-M4)。除了这些以外,处理器中还有一些内部总线系统、可选的存储器保护单元(MPU)以及支持软件调试操作的一组部件。内部总线连接可以将处理器和调试产生的传输送到设计的各个部分。

Cortex-M3/M4 处理器是高度可配置的。例如,调试特性是可选的,若产品需要支持调试,片上系统设计人员可以将调试部件去掉,这样可以显著降低设计的硅片面积。有些情况下,芯片设计人员还可以选择降低硬件指令断点和数据监视点比较器的数量,以降低系统的门数量。许多系统特性也是可配置的,如中断输入的数量、支持的中断优先级的数量以及 MPU 等。

所示的框图为ARM提供给芯片设计人员的参考。芯片供应商也可以对其进行修改,定制调试接口等调试支持部件或增加设备相关的低功耗特性等(例如,增加某种唤醒中断控制器)。

Cortex-M3和Cortex-M4处理器的顶层具有多个总线接口

1.5 储存器系统

Cortex-M3/M4 处理器本身并不包含存储器(没有程序存储器、SRAM或缓存),它们具有通用的片上总线接口,因此,微控制器供应商可以将它们自己的存储器系统添加到系统中。

一般来说,微控制器供应商需要将下面的部件添加到存储器系统中:

- 程序存储器,一般是Flash

- 数据存储器,一般是SRAM

- 外设

这样,不同微控制器产品可能会具有不同的存储器配置、不同的存储器大小和类型,以及不同的外设。

Cortex-M 处理器的总线接口为 32 位宽,且基于高级微控制器总线架构(AMBA)标准。AMBA 中包含多个总线协议,任何芯片设计者都可以免费使用这些标准协议。AMBA 规范可以从 ARM 网站下载。由于这些标准协议的低硬件成本、效率以及开放性,它们大受芯片设计者的欢迎。

Cortex-M3/M4 处理器主要使用的总线接口协议为 AHB Lite(高级高性能总线),它用于程序存储器和系统总线接口。AHB Lite 协议为流水线结构的总线协议,可以在低硬件成本下实现高运行频率。高级外设总线(APB)接口为处理器使用的另外一种总线协议,它通常用于基于 ARM 的微控制器的总线系统。另外,APB 协议在 Cortx-M3/M4 处理器内部还用于调试支持。

与片外总线协议不同,AHBLite 和 APB 协议相对简单。这是因为芯片内的硬件配置是固定的,无须一种复杂的初始化协议来处理可能的配置(例如,无须支持类似于计算机技术中的“热插拔”)。

由于这种开发方式和通用的总线架构的使用。每位芯片设计者都可以为 ARM 处理器开发外设、存储器控制器以及片上存储器模块。这些设计通常被称作 IP,微控制器供应商可以在他们的产品中使用自己的外设设计或者其他公司的授权 IP。通过一种标准的总线协议,这些 IP 可以很轻松地被集成到一个大的设计中。如今,AMBA协议已经成为了片上总线系统的标准,可以在许多片上系统设备中找到这些设计,其中,也包括其他处理器设计公司的处理器。

1.6 中断和异常支持

Cortex-M3/M4 处理器中存在一个名为嵌套向量中断控制器(NVIC)的中断控制器,它是可编程的且其寄存器经过了存储器映射。NVIC 的地址固定,而且 NVIC 的编程模型对于所有的 Cortex-M 处理器都是一致的。

除了外设和其他外部输人的中断外,NVIC 还支持多个系统异常,其中,包括不可屏蔽中断(NMI)和处理器内部的其他异常源。

Cortex-M3/M4 处理器是可配置的,微控制器供应商能够决定 NVIC 设计实际支持的可编程中断优先级的数量。尽管 NVIC 的一些细节在不同的 Cortex-M3/M4 处理器间可能存在差异,中断/异常的处理和 NVIC 的异常模型却是相同的,它们定义在架构参考手册中。

二、Cortex-M3/M4 处理器的特性

目前,大多数主要微控制器供应商都在对基于 ARMCortex-M3/M4 处理器的微控制器出货。Cortex-M 处理器的哪些优势使得它们如此受欢迎?本节将会总结 Cortex-M3/M4 处理器的特点和优势。

2.1 性能

Cortex-M 处理器给微控制器产品带来了高性能。

- 三级流水线结构使得包括乘法在内的多数指令,可以在单周期内执行,同时允许微控制器设备运行较高的频率,一般可以超过 100MHz,而利用现代半导体生产工艺则可以达到 200MHz。甚至在运行和其他多数处理器产品相同的频率时,Cortex-M3/M4 处理器的时钟周期比(CPI)也会更高。这样每 MHz 就可以完成更多的任务,若要降低功耗,也可以让系统运行在较低的时钟率下。

- 由于多总线接口,指令和数据访问可以同时执行。

- 流水线结构的总线接口使得存储器系统可以运行较高的时钟频率。

- 由于指令集非常高效,执行复杂运算时可以使用较少的指令。

- 每次取指令都是 32 位的,而多数指令则是 16 位的,因此一次可以取两条指令,存储器接口上的多余带宽也带来了更高的性能和更佳的能耗效率。

由于处理器的高性能,之前无法用 8 位 / 16 位低成本微控制器开发的产品现在就可以实现。例如,无须换成高端的微处理器,也可以将低成本的图形接口添加到嵌人式设备中。

| 处理器 | Dhrystone 2.1/MHz | CoreMark/MHz |

| Cortex-M3 | 1.25 DMIPS/MHz | 3.32 |

| Cortex-M4 | 1.25 DMIPS/MHz | 3.38 |

| 具有FPU的Cortex-M4 | 1.25 DMIPS/MHz | 3.38 |

2.2 代码密度

与其他处理器架构相比,ARM Cortex-M 处理器使用的 Thumb 指令可以提供极佳的代码密度。许多软件开发人员在从 8 位微控制器移植时,会发现代码体积显著减小,而性能却得到很大的提升。Cortex-M 处理器的代码密度也比许多常用的 16 位和 32 位架构要高。另外,还有其他优势:

- 利用 Thumb-2 技术,无须状态切换开销就可以同时使用 16 位指令和 32 位指令,大多数简单操作可以用 16 位指令实现。

- 多种存储器寻址模式用于高效的数据访问。

- 多种存储器访问可以由单指令完成。

- Cortex-M3/M4 都支持硬件除法指令和乘累加(MAC)指令。Cortex-M3/M4 中的位域处理指令。

- Cortex-M4 支持单指令多数据(SIMD)指令。

- Cortex-M4 支持可选的单精度浮点指令。

除了低系统成本,高代码密度同样可以降低功耗,这是因为可以使用具有较小 Flash 存储器的设备。还可以将部分程序代码复制到 SRAM 中,这样在提高执行速度的同时,也无须担心占用太多的 SRAM 空间。

2.3 低功耗

低功耗是 Cortex-M 处理器的设计目标,许多 Cortex-M3/M4 微控制器产品在运行时功耗会低于200A/MHz(1.8V 供电时约为 0.36mW/MHz),而有些甚至会低于 100μA/MHz。Cortex-M 处理器的低功耗特性包括:

- Cortex-M3 面向低成本微控制器设计,它们的硅片面积不能太大(门数低)。由于具有 SIMD 指令和可选的浮点单元,Cortex-M4 要稍微大一些。三级流水线设计可以很好地平衡性能和硅片大小。

- 由于 Cortex-M 处理器的高代码密度,软件开发者可以使用具有较小程序存储器的设备来实现自己的产品,这样可以降低功耗。

- Cortex-M 处理器具有多个低功耗特性,其中,包括定义在架构中的多个休眠模式和集成的架构时钟支持,这样当处理器的某部分不使用时,可以将这部分的时钟电路关闭。

- 完全静态、同步以及可综合的设计使得处理器在生成时可以使用任何低功耗或标准的半导体工艺技术。对于从版本 2 开始的 Cortex-M3 以及当前所有版本的 Cortex-M4,处理器中存在一个名为唤醒中断控制器(WIC)的可选硬件单元,它可以使能状态保持功率门(SRPG)等低功耗技术。

由于这些低功耗特性的存在,Cortex-M 处理器非常受嵌人式产品设计者的欢迎,他们总是会寻找能够改进自己的可移动产品电池寿命的方法。除了较长的电池寿命,微控制器的低功耗也有助于降低电磁干扰(EMI),而且可能会简化电源设计(或者减小电池尺寸),因此,可以降低系统成本。

3.4 储存器系统

Cortex-M3/M4处理器支持多种存储器特性:

- 可寻址存储器空间共为4GB,且以32位寻址,无须将存储器分页。

- 所有的 Cortex-M 处理器的存储器映射定义都是一致的,预定义的存储器映射使得处理器设计可以为哈佛总线架构进行优化,而且访问处理器内经过存储器映射的外设(如NVC)也非常容易。

- 流水线结构的 AHB Lite 总线接口可以提供高速且低等待的传输,AHB Lite 接口支持 32 位、16 位和 8 位数据的高效传输。总线协议还允许插人等待状态、支持总线错误条件及允许多个总线主控共用总线。

- 可选的位段特性。SRAM 和外设空间中存在两个可位寻址的区域,通过位段别名地址修改的位数值会被自动转换为位段区域的读一修改一写的原子操作。

- 多处理器系统设计的排他访问,适用于多处理器系统中的信号量操作。

- 支持小端或大端的存储器系统。Cortex-M3/M4 处理器既可以运行在小端模式,也可以运行在大端模式。不过,基本上所有的微控制器都是要么为小端要么为大端的,不会两者兼有。多数Cortex-M3 微控制器产品使用小端。

- 可选的存储器保护单元(MPU)。

3.5 储存器保护单元

MPU 为 Cortex-M3/M4 处理器中的可选特性,微控制器供应商可以决定是否使用 MPU。MPU 为监控总线传输的可编程设备,需要通过软件(一般是嵌入式 OS)配置若 MPU 存在,应用程序可以将存储器空间分为多个部分,并为每个部分定义访问权限。当违反访问规则时,错误异常就会产生,错误异常处理则会分析问题,而且如果可能,将错误加以修复。

MPU可以有多种使用方式。一般情况下,OS 会设置 MPU 以保护 OS 内核和其他特权任务使用的数据,防止恶意用户程序的破坏。而且 OS 也可以选择将不同用户任务使用的存储器隔离开来。这些处理有助于检测系统错误,并且提高了系统在处理错误情况时的健壮性。MPU 也可以将系统配置为只读的,防止意外擦除 SRAM 中的数据或覆盖指令代码。MPU 默认禁止,若应用不需要存储器保护特性,就无须将其初始化。

3.6 中断处理

Cortex-M3/M4 处理器中存在一个复杂的中断控制器,其被称作嵌套向量中断空制器(NVIC)。NVIC 具有多个特性:

- 支持最多 240 个中断输人、不可屏蔽中断(NMI)输人和多个系统异常。每个中断(NMI除外)都可以被单独使能或禁止。

- 中断和多个系统异常具有可编程的优先级。对于Cortex-M3/M4,优先级可以在运行时动态修改(注意,Cortex-M0/M0 不支持优先级的动态修改)。

- 嵌套中断/异常以及中断/号常按照优先级的自动处理。

- 向量中断/异常。这就意味着处理器会自动取出中断/异常向量,无须软件确定产生的是哪个中断/异常。

- 向量表可以重定位在存储器中的多个区域。

- 低中断等待。对于具有零等待状态的存储器系统,中断等待仅为12个周期,。中断和多个异常可由软件触发。

- 多个优化用于降低不同异常上下文切换时的中断处理开销。中断/异常屏蔽功能可以将所有的中断和异常(NMI除外)屏蔽掉,或者将中断/异常屏蔽为某个优先级之下。

为了支持这些特性,NVIC 使用了多个可编程寄存器。这些寄存器经过了存储器映射,而 CMSIS-Core 则为大多数常见的中断控制任务提供了所需的寄存器定义和访问函数(API)这些访问函数易于使用,而且多数可用于 Cortex-M0 等其他 Cortex-M 处理器。

向量表为系统存储器的一部分,其中存有中断和系统异常的起始地址。向量表默认位于存储器空间的开头(地址0x0),不过,若需要,向量表偏移可以在运行时变为其他值。对于大多数应用程序,向量表可以在编译时被设置为应用程序映像的一部分,且在运行时保持不变。

3.7 OS支持和系统级特性

Cortex-M3/M4 处理器在设计时就考虑了对嵌人式 OS 的高效支持。它们具有一个内置的系统节拍定时器 SysTick,可以为 OS 定时提供周期性定时中断。由于SysTick 定时器在所有的 Cortex-M3 和Cortex-M4 设备中都存在,嵌入式 OS 的源代码可以很容易地就能用在所有的这些设备上,而无须为设备相关的定时器进行修改。

Cortex-M3/M4 具有两个栈指针:

- OS内核和中断用的主栈指针(MSP)

- 应用任务用的进程栈指针(PSP)

这样,OS 内核用的栈就和应用任务的栈分离开来了,可靠性得到提高的同时,栈空间的使用也得到了优化。没有 OS 的简单应用可以只使用 MSP。为了进一步提高可靠性,Cortex-M3/M4 支持独立的特权和非特权操作模式,处理器在启动后默认处于特权模式。当使用 OS 且执行用户任务时,用户任务可以在非特权操作模式中执行,这样可以增强某些限制,如阻止对一些 NVIC 寄存器的访问。特权和非特权操作模式也可以同 MPU 一道,防止非特权任务访问某些存储器区域。这样,用户任务就无法破坏 OS 内核以及其他任务的数据,因此,也就提高了系统的稳定性。

大多数简单的应用根本不会使用非特权模式,不过在构建需要高可靠性的嵌入式系统时通过特权和非特权任务的分离,当某个非特权任务出错后,系统可能还会继续执行。Cortex-M 处理器还具有一些错误处理。当检测到一个错误时(例如,访问非法存储器地址),错误异常就会被触发,这样,可以避免进一步的系统错误,并且可以分析问题。

3.8 Cortex-M4的特殊性

Cortex-M4 处理器在很多方面都和 Cortex-M3 类似。不过,它还具有 Cortex-M3 中不存在的一些特性,其中,包括 DSP 扩展和可选的单精度浮点单元。

Cortex-M4 的 DSP 扩展包括:

- 8 位和 16 位单指令多数据(SIMD)指令。这些指令允许多个数据操作的并行执行。SIMD 最常用的应用为音频处理,其左右声道的计算可以同时执行。它还可用于图像处理,图形像素的 R-G-B 或 C-M-Y-K 元素可以用 8 位 SIMD 数据表示,且可以并行处理。

- 支持多个饱和运算指令,其中,包括SIMD形式的,这样可以避免在出现上溢/下溢时,计算结果产生大的畸变。

- 单周期 16 位、双 16 位以及 32 位乘累加(MAC)。尽管 Cortex-M3 也支持几个 MAC 指令,而 Cortex-M4 的 MAC 指令则具有更多选项,其中,包括寄存器的高低 16 位多种组合的乘法以及SIMD 形式的 16 位 MAC。另外,Cortex-M4 处理器中的 MAC 运算可以在单周期内完成,而 Cortex-M3 则需要花费几个周期。

Cortex-M4 中可选的浮点单元(FPU)则包括:

- 符合 IEEE754 标准的单精度浮点单元。为了应对浮点运算,Cortex-M4 处理器支持多个浮点指令,同样还存在多个指令可用于单精度和半精度浮点数据间的转换。

- 浮点单元支持融合 MAC 运算,它可以提高 MAC 结果的精度。

- 若不需要浮点单元就可以将它关闭,这样可以降低功耗。

为了支持额外的指令以及满足 DSP 的高性能需求,Cortex-M4 内部的数据通路和 Cortex-M3 处理器不同。由于这些差异,Cortex-M4 的一些指令所花费的时钟周期要少。

为了全部发挥 Cortex-M4 中 DSP 部分的作用,ARM 通过 CMSIS-DSP 项目提供了一个 DSP 库。该库是免费的,可用于 Cortex-M4、Cortex-M3 处理器,甚至 Cortex-M0+ 及 Cortex-M0 处理器也可以使用。

3.10 调试支持

Cortex-M3/M4 处理器具有丰富的调试特性,可以降低软件开发的难度。除了暂停和单步等标准的调试特性外,在无须昂贵设备的前提下,还可以利用跟踪特性查看程序执行的细节。

Cortex-M3/M4 处理器的 Flash 补丁和断点单元(FPB)中存在最多 8 个用于断点的硬件比较器(6 个用于指令地址,2个用于数据地址)。在触发时,处理器可被暂停,或将传输重映射到 SRAM 区域。利用重映射特性,只读的存储器位置也可以被修改,例如,可以利用一小块可编程存储器为掩膜 ROM 补上部分程序。这样,即使主程序代码位于掩膜 ROM 中,也可以修正代码错误或者进行改进。

Cortex-M3/M4 处理器的数据监视点和跟踪(DWT)单元中还存在最多 4 个硬件数据监视点比较器。在访问所选择的数据时,这些比较器会产生监视点事件并暂停处理器,或者在无须暂停处理器的情况下产生可由跟踪接口收集的跟踪信息。集成开发环境(IDE)中的调试器可以将数据值和其他信息呈现出来,并将数据值的改变图像化。DWT可用于产生异常事件跟踪和基本概况信息,也通过跟踪接口输出。

Cortex-M3/M4 处理器还具有一个可选的嵌人式跟踪宏单元(ETM)模块,其可用于产生指令跟踪。通过该模块可以查看执行过程中的程序流,它在调试复杂软件时非常重要,而且还可用于详细概况和代码盖分析。

Cortex-M3/M4 处理器的调试可以通过两种接口实现:

- JTAG连接或名为串行线调试

- (SWD)的两线接口

许多开发工具供应商都同时支持 JTAG 和 SWD 协议。跟踪信息可以由单线的串行线查看(SWV)接口收集,或者若所需的跟踪带宽较大时(如使用指令跟踪时),也可以使用一种跟踪端口接口(一般为5针)。跟踪和调试接口可以合并到一个接头中。

3.11 可扩展性

Cortex-M 处理器并非仅用于低成本的微控制器产品。

目前,可以发现不少多处理器产品中都包含 Cortex-M3/M4 处理器。其中包括:

- 具有多个 Cortex-M 处理器的微控制器,如 NXP 的 LPC4300。

- 在具有一个或多个 Cortex-M 处理器的高端数字信号处理设备中,用作主处理器或额外的 DSP数据处理引擎,如 TexasInstruments 的 Concerto 产品系列就将一个 Cortex-M3 处理器与 DSP 内核放在了一起。

- 在具有一个或多个 Cortex-M 处理器的复杂片上系统中,用作协处理器。例如,TexasInstruments 的 OMAP5 将一个 Cortex-A15 和两个 Cortex-M4 处理器放在一个器件中。

- 在具有一个或多个 Cortex-M 处理器的复杂片上系统中,用作电源管理或系统控制。

- 在具有一个或多个 Cortex-M 处理器的复杂片上系统中,充当有限状态机(FSM)。

利用 ARM Cortex-M 系统设计套件等多种 AMBA 总线架构解决方案,Cortex-M 处理器也可以支持多处理器系统。

另外,Cortex-M3/M4 处理器具有以下支持多处理器系统设计的特性:

- 排他访问指令。Cortex-M3 和 Cortex-M4 处理器支持多个排他访问指令,它们为成对出现的特殊的存储访问指令,用于信号量变量的加载和存储操作或手动排他操作。通过总线架构中增加的硬件支持,处理器可以确定对一个共享数据存储器区域的访问是否成功执行(例如,在操作期间没有其他的处理器访问同一区域)。

- 可扩展的调试支持。Cortex-M 处理器的调试系统基于 CoreSight 架构,可扩展对多处理器的支持,共用一个调试连接和跟踪接口。

- 事件通信接口。Cortex-M3/M4 处理器支持一种简单的事件通信接口,在多处理器系统中,可以让一些处理器进入休眠模式以降低功耗,而在某个处理器中的信号量操作完成等事件发生时,则可以将处理器唤醒。

可扩展性的另外一个方面体现在,对于可以找到的基于 Cortex-M 处理器的微控制器产品,由于所有的 Cortex-M 处理器在编程模型、中断处理和包括调试在内的软件开发方面都非常类似,因此可以很容易地为自己的嵌入式系统切换不同的处理器,以满足不同的性能、系统级和价格需求。

相关文章:

ARM Cortex-M3/M4 权威指南 笔记【一】技术综述

一、Cortex-M3/M4 处理器的一般信息 1.1 处理器类型 ARM Cortex-M 为 32 位 RISC(精简指令集)处理器,其具有: 32位寄存器32位内部数据通路32位总线接口 除了 32 位数据,Cortex-M 处理器(以及其他任何 A…...

12.项目结构

后端结构 ruoyi-admin 项目启动的入口 提供了两种启动方式 1.RuoYiApplication基于springboot,内置tomcat,直接运行。 2.RuoYiServletInitializer将springboot项目打成一个war包,用外置的servlet容器来运行。 通用功能的controller 后台登录相关的、权限控制相关的、数据字…...

保研考研机试攻略:python笔记(4)

🐨🐨🐨15各类查找 🐼🐼二分法 在我们写程序之前,我们要定义好边界,主要是考虑区间边界的闭开问题。 🐶1、左闭右闭 # 左闭右闭 def search(li, target): h = len(li) - 1l = 0#因为都是闭区间,h和l都可以取到并且相等while h >= l:mid = l + (h - l) // 2…...

高阶C语言|枚举与联合

💬 欢迎讨论:在阅读过程中有任何疑问,欢迎在评论区留言,我们一起交流学习! 👍 点赞、收藏与分享:如果你觉得这篇文章对你有帮助,记得点赞、收藏,并分享给更多对C语言感兴…...

【天梯赛】L1-104 九宫格(C++)

易忽略的错误:开始习惯性地看到n就以为是n*n数组了,实际上应该是9*9的固定大小数组,查了半天没查出来 题面 L1-104 九宫格 - 团体程序设计天梯赛-练习集 代码实现 #include<bits/stdc.h> using namespace std; //易错:开…...

现代C++多线程基础 -忆苦思甜pthread_mutex

c 老古董 文章目录 c 老古董pthread_mutex概念常用apipthread_mutex_initpthread_mutex_lockpthread_mutex_trylockpthread_mutex_unlockpthread_mutex_destroy 案例 pthread_mutex 概念 互斥锁 mutex是一种简单的加锁的方法来控制对共享资源的访问,mutex只有两种…...

soular基础教程-使用指南

soular是TikLab DevOps工具链的统一帐号中心,今天来介绍如何使用 soular 配置你的组织、工作台,快速入门上手。  1. 账号管理 可以对账号信息进行多方面管理,包括分配不同的部门、用户组等,从而确保账号权限和职责…...

网络安全网格架构(CSMA) 网络安全框架csf

CSRF:Cross Site Request Forgy(跨站请求伪造) 用户打开另外一个网站,可以对本网站进行操作或攻击。容易产生传播蠕虫。 CSRF攻击原理: 1、用户先登录A网站 2、A网站确认身份返回用户信息 3、B网站冒充用户信息而不是直接获取用…...

基于DeepSeek API和VSCode的自动化网页生成流程

1.创建API key 访问官网DeepSeek ,点击API开放平台。 在开放平台界面左侧点击API keys,进入API keys管理界面,点击创建API key按钮创建API key,名称自定义。 2.下载并安装配置编辑器VSCode 官网Visual Studio Code - Code Editing…...

【AI时代】Page Assist - 本地 AI 模型的 Web UI (谷歌浏览器) 本地DeepSeek启用联网功能

Page Assist - 本地 AI 模型的 Web UI 一、部署本地模型 参考教程:https://blog.csdn.net/Bjxhub/article/details/145536134二、安装插件 Page Assist 浏览器谷歌商店搜索 Page Assist ,安装该插件。 注意:需要一点科学的魔法。 三、使用…...

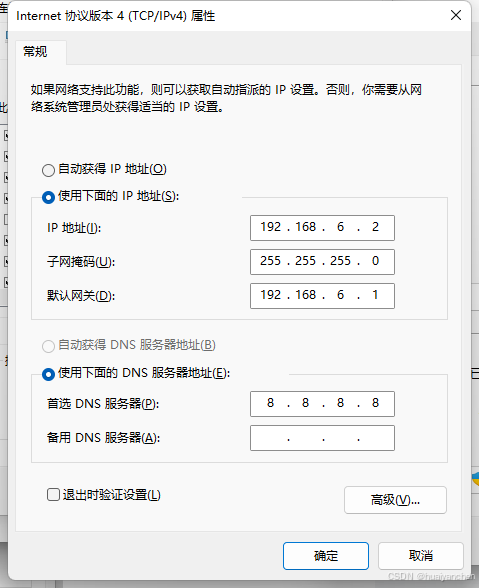

电脑IP地址自定义

1.连接WIFI 2.打开控制面板 3.打开网络共享中心 4.选择想要修改的WIFI 点击连接的WIFI选择属性 点击要修改的配置协议IPV4/IPV6 设置IP地址为需要的地址...

python卷积神经网络人脸识别示例实现详解

目录 一、准备 1)使用pytorch 2)安装pytorch 3)准备训练和测试资源 二、卷积神经网络的基本结构 三、代码实现 1)导入库 2)数据预处理 3)加载数据 4)构建一个卷积神经网络 5࿰…...

EX_25/2/11

将 epoll 服务器 客户端拿来用 客户端: 写一个界面,里面有注册登录 服务器:处理注册和登录逻辑,注册的话将注册的账号密码写入数据库,登录的话查询数据库中是否存在账号,并验证密码是否正确 额外功能&a…...

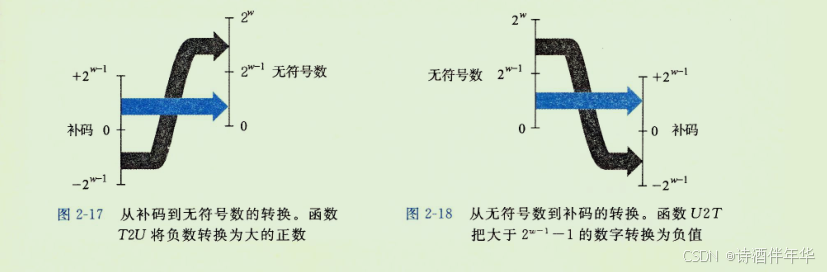

二.2 整数表示(2.1-2.4)

在本节中,我们描述用位来编码整数的两种不同的方式:一种只能表示非负数,而另一种能够表示负数、零和正数。后面我们将会看到它们在数学属性和机器级实现方面密切相关。我们还会研究扩展或者收缩一个已编码整数以适应不同长度表示的效果。 图2…...

中间件-安装Minio-集成使用(ubantu-docker)

目录 1、安装docer 2、运行以下命令拉取MinIO的Docker镜像 3、检查当前所有Docker下载的镜像 4、创建目录 5、创建Minio容器并运行 6、SDK操作 FileUploader.java 1、安装docer 参考这篇:Linux安装Docker 2、运行以下命令拉取MinIO的Docker镜像 docker pull…...

夸克网盘多链接批量保存,自动同步更新,批量分享

最近夸克网盘有点火,好多资源都上夸克网盘了,做了一个夸克网盘的批量化程序,已经打包好了,不用配置代码环境就能用 夸克网盘工具:https://pan.quark.cn/s/c22f3451a6ab 百度网盘工具:https://pan.quark.cn…...

)

2025清华:DeepSeek从入门到精通.pdf(附下载)

本文是一份关于如何深入理解和使用DeepSeek技术的全面指南,由清华大学新闻与传播学院新媒体研究中心元宇宙文化实验室的余梦珑博士后及其团队编撰。DeepSeek是一家中国科技公司,专注于通用人工智能(AGI)的研发,其开源推…...

【AIGC】在VSCode中集成 DeepSeek(OPEN AI同理)

在 Visual Studio Code (VSCode) 中集成 AI 编程能力,可以通过安装和配置特定插件来实现。以下是如何通过 Continue 和 Cline 插件集成 DeepSeek: 一、集成 DeepSeek 获取 DeepSeek API 密钥:访问 DeepSeek 官方网站,注册并获取 …...

android动态设置是否允许应用卸载

摘要:通过广播设置全局参数控制应用是否允许卸载,全局参数在Launcher和PackageInstaller两个模块中使用到。此功能可用于MDM后台控制是否允许设备卸载应用。 1. 静态注册广播 由于系统安装和卸载的功能集中在PackageInstaller模块中,为了更…...

基于微信小程序的博物馆预约系统的设计与实现

hello hello~ ,这里是 code袁~💖💖 ,欢迎大家点赞🥳🥳关注💥💥收藏🌹🌹🌹 🦁作者简介:一名喜欢分享和记录学习的在校大学生…...

)

【2026年蚂蚁集团暑期实习- 3月29日-开发岗-第二题- 质数合数】(题目+思路+JavaC++Python解析+在线测试)

题目内容 在数论中,质数是大于 $1 $且仅能被 $1 和自身整除的正整数;合数是大于和自身整除的正整数;合数是大于和自身整除的正整数;合数是大于 1$ 且除了 $1 $和自身外还有其他正因子的正整数。 给定一个长度为$ n$ 的数组 { a1,a2,…,ana_1,a_2,…,a_na...

聊聊永磁同步电机里的那点“扰动“破事

两种负载扰动观测器设计思路,pmsm仿真 仿真基于离散模型,观测器设计基于m文件,方便移植到c验证 包含:(1)1.5延时补偿(2)扩张龙伯格扰动观测器(ESO)设计&#…...

OTA电路仿真实战:用Virtuoso617分析频率响应与相位特性

OTA电路仿真实战:用Virtuoso617分析频率响应与相位特性 在模拟电路设计领域,运算跨导放大器(OTA)作为核心构建模块,其性能直接决定了整个系统的表现。本文将带您深入Virtuoso617的仿真世界,通过实战案例解…...

掌握NeuralForecast:构建企业级时间序列预测解决方案

掌握NeuralForecast:构建企业级时间序列预测解决方案 【免费下载链接】neuralforecast Nixtla/neuralforecast - 一个Python库,提供统一的接口来训练和预测时间序列数据,使用神经网络方法,如N-BEATS和N-HITS,以及传统的…...

)

C语言数组操作:3种移除元素方法实战对比(附LeetCode真题解析)

C语言数组操作:3种移除元素方法实战对比(附LeetCode真题解析) 在算法面试和日常编程中,数组操作是最基础也最常考察的技能点之一。移除数组中特定元素这类看似简单的任务,却能很好地检验程序员对内存管理、算法效率和…...

Sora.FM零基础部署指南:3步上手AI视频生成工具的Linux实践方案

Sora.FM零基础部署指南:3步上手AI视频生成工具的Linux实践方案 【免费下载链接】sorafm 项目地址: https://gitcode.com/GitHub_Trending/so/sorafm Sora.FM是一款基于Sora AI技术的开源视频生成平台,支持通过文本描述创建高质量AI视频。本指南专…...

Unix哲学:一切皆文件与网络通信的统一抽象

目录 Unix哲学:一切皆文件与网络通信的统一抽象 1. Unix哲学的核心:“一切皆文件” 2. 统一接口:Unix I/O操作 3. 文件描述符:操作的“取货单” 4. 网络通信:套接字作为特殊文件 5. 总结:抽象的力量 前…...

如何通过AI技术提升图表创作效率?Next AI Draw.io全攻略

如何通过AI技术提升图表创作效率?Next AI Draw.io全攻略 【免费下载链接】next-ai-draw-io 项目地址: https://gitcode.com/GitHub_Trending/ne/next-ai-draw-io 技术人员日常工作中常会遇到这样的困境:花几小时绘制的架构图需要频繁修改&#x…...

IIS网站部署实战:从基础配置到安全优化

1. IIS网站部署基础配置 第一次在Windows Server上部署IIS网站时,我踩了不少坑。记得当时为了调试一个简单的ASP网站,折腾了整整一个下午。现在回想起来,其实只要掌握几个关键步骤,就能轻松完成基础部署。 首先需要在服务器管理器…...

解锁DeerFlow:零基础搭建智能研究环境完全指南

解锁DeerFlow:零基础搭建智能研究环境完全指南 【免费下载链接】deer-flow DeerFlow is a community-driven framework for deep research, combining language models with tools like web search, crawling, and Python execution, while contributing back to th…...