FPGA/Verilog HDL/AC620零基础入门学习——8*8同步FIFO实验

实验要求

该项目主要实现一个深度为8、位宽为8bit的同步FIFO存储单元。模块功能应包括读控制、写控制、同时读写控制、FIFO满状态、FIFO空状态等逻辑部分。

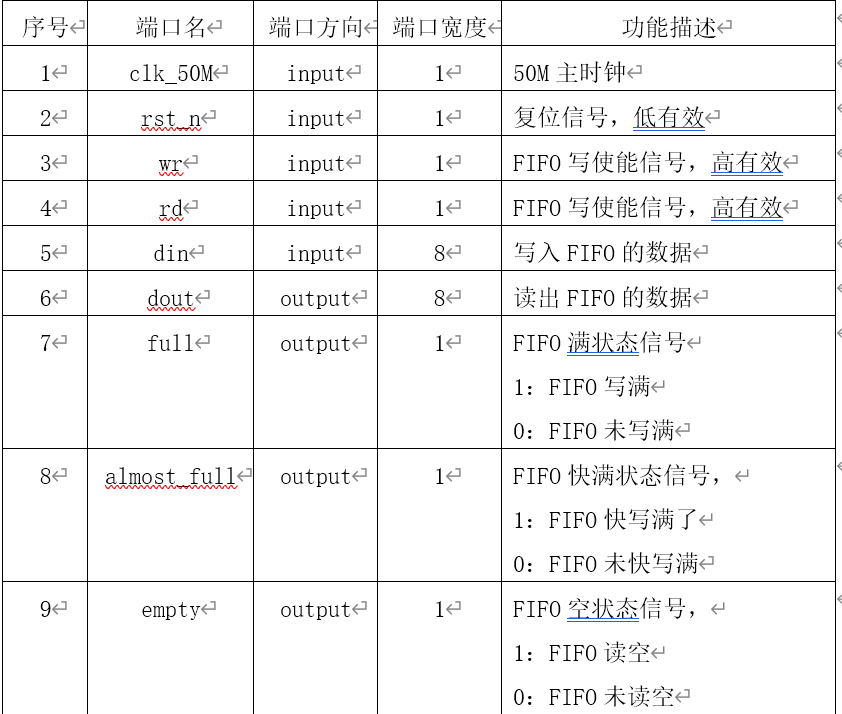

该项目由一个功能模块和一个testbench组成。其中功能模块的端口信号如下表所示。

提示:

(1)设定一个写地址waddr[2:0],每来一个写使能wr,则写地址加一;

(2)设定一个读地址raddr[2:0],每来一个读使能rd,则读地址加一;

(3)若同时读写,则读写地址不变,只是将输入数据din直接赋值给dout;

(4)FIFO中数据的个数cout=waddr-raddr;

(5)状态指示:

- 当cout=8时,FIFO满(full=1);

- 当cout=6时,FIFO快满了(almost_full=1);

- 当cout=4时,FIFO半满(半空)(half=1);

- 当cout=2时,FIFO快空了(almost_empty=1);

- 当cout=0时,FIFO空(empty=1);

sfifo

module sfifo(clk,rst_n,data_in,wr,rd,full,empty,data_out,sfifo_cnt,half,almost_empty,almost_full);input clk;input rst_n;input [7:0] data_in;input wr;input rd;output full;output empty;output almost_full;output almost_empty;output half;output [7:0] data_out;output [3:0] sfifo_cnt;wire clk;wire rst_n;wire [7:0] data_in;wire wr;wire rd;wire full;wire empty;wire almost_full;wire almost_empty;wire half;reg [7:0] data_out;reg [3:0] sfifo_cnt;`define DEL 1 // Clock-to-output delayreg [7:0] sfifo_ram[0:7]; // sfifo_ram initializedreg [2:0] rd_ptr; // Read pointerreg [2:0] wr_ptr; // Write pointer assign empty = ( sfifo_cnt == 0 ) ? 1 : 0; //Empty signalassign full = ( sfifo_cnt == 8 ) ? 1 : 0; //Full signalassign almost_full = ( sfifo_cnt == 6 ) ? 1 : 0; //Almost Full signalassign almost_empty = ( sfifo_cnt == 2 ) ? 1 : 0;//Almost Empty signalassign half = ( sfifo_cnt == 4 ) ? 1 : 0;//HALF signal// sfifo_cnt changed// 当读有效, cnt--// 当写有效, cnt++always @( posedge clk or negedge rst_n) beginif( ~rst_n ) beginsfifo_cnt <= #`DEL 4'h0;endelse if( rd && ~wr ) beginsfifo_cnt <= #`DEL sfifo_cnt - 1;endelse if( ~rd && wr ) beginsfifo_cnt <= #`DEL sfifo_cnt + 1;endelse begin sfifo_cnt <= sfifo_cnt;endend always @( posedge clk or negedge rst_n) beginif( ~rst_n ) beginrd_ptr <= #`DEL 3'h0;endelse if( rd ) beginif( rd_ptr == 3'h7 ) beginrd_ptr <= #`DEL 3'h0;endelse beginrd_ptr <= #`DEL rd_ptr +1;endendelse beginrd_ptr <= rd_ptr;endend always @( posedge clk or negedge rst_n) beginif( ~rst_n ) beginwr_ptr <= #`DEL 3'h0;endelse if( wr ) beginif( wr_ptr == 3'h7 ) beginwr_ptr <= #`DEL 3'h0;endelse beginwr_ptr <= #`DEL wr_ptr +1;endendelse beginwr_ptr <= wr_ptr;endend always @( posedge clk or negedge rst_n) beginif( ~rst_n ) begindata_out <= #`DEL 8'h0;endelse if( wr ) beginsfifo_ram[wr_ptr] <= #`DEL data_in;endelse if( rd ) begin data_out <= #`DEL sfifo_ram[rd_ptr];endend endmodule

sfifo_test

module sfifo_test();reg clk;reg rst_n;reg [7:0] data_in;reg wr;reg rd;wire full;wire empty;wire almost_full;wire almost_empty;wire half;wire [7:0] data_out;wire [3:0] sfifo_cnt;initial beginrst_n=1;clk=0;wr=0;rd=0;data_in=0;#1 rst_n=0;#5 rst_n=1;#3 wr=1;#5 rd=1;#5 rd=0;#5 wr=0;#5 wr=1;#10 rd=1;#10 rd=0;endalways begin#5 clk=~clk;endalways @(posedge clk or negedge rst_n) beginif (~rst_n) begindata_in<=0;wr<=0;rd<=0;endelse begindata_in<=$random;endendinitial begin$dumpfile ("F:/Robei/practice/prac_07_sfifo/sfifo_test.vcd");$dumpvars;#5000;$stop;end//---Module instantiation---sfifo sfifo1(.clk(clk),.rst_n(rst_n),.data_in(data_in),.wr(wr),.rd(rd),.full(full),.empty(empty),.almost_full(almost_full),.almost_empty(almost_empty),.half(half),.data_out(data_out),.sfifo_cnt(sfifo_cnt));endmodule

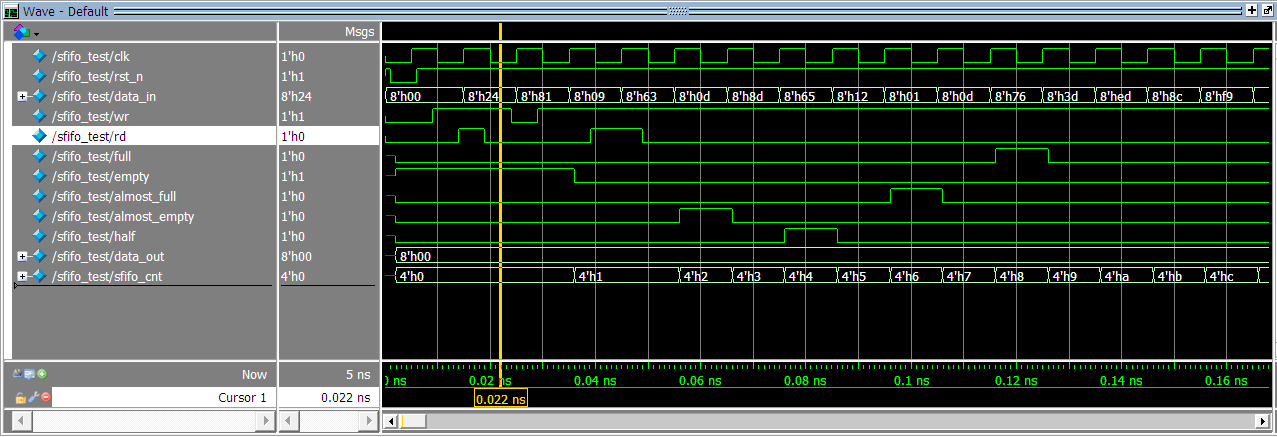

实验结果

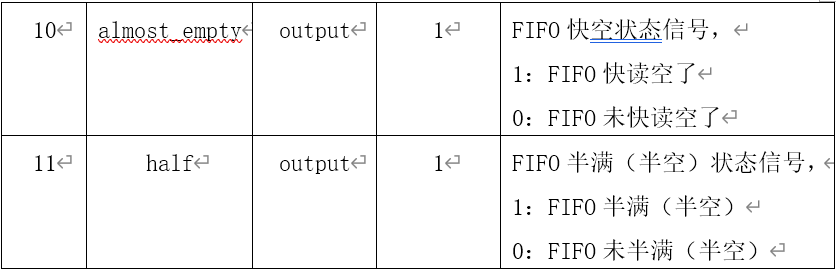

整体波形

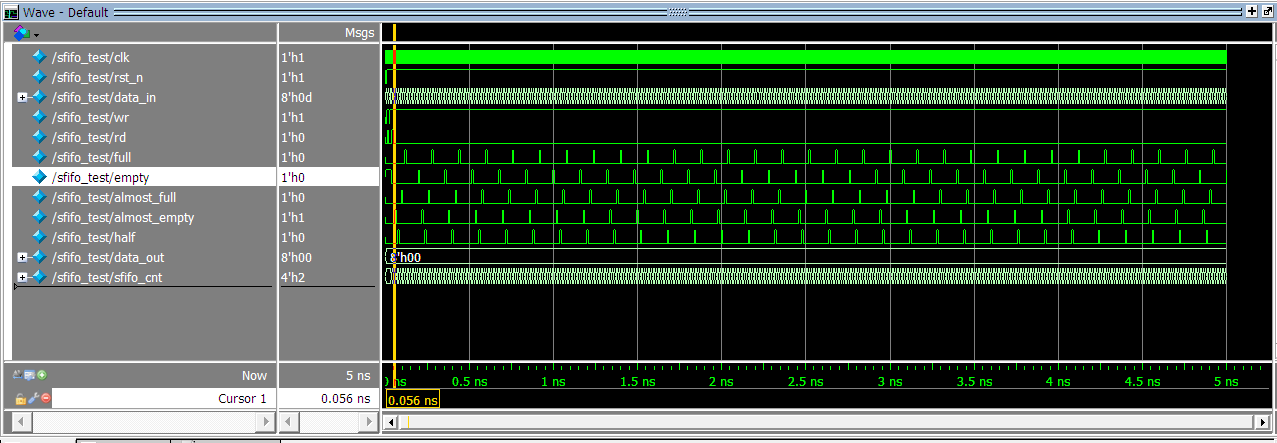

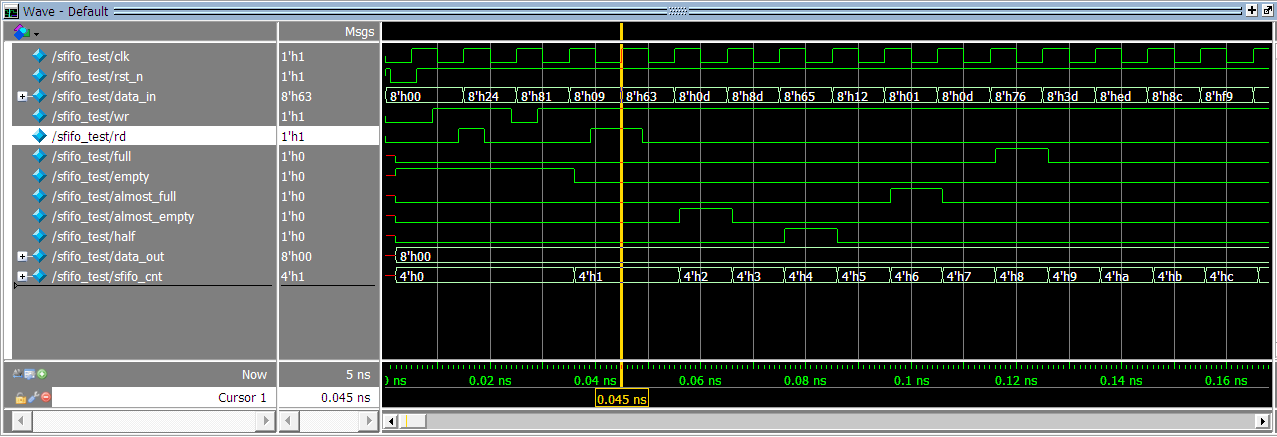

读

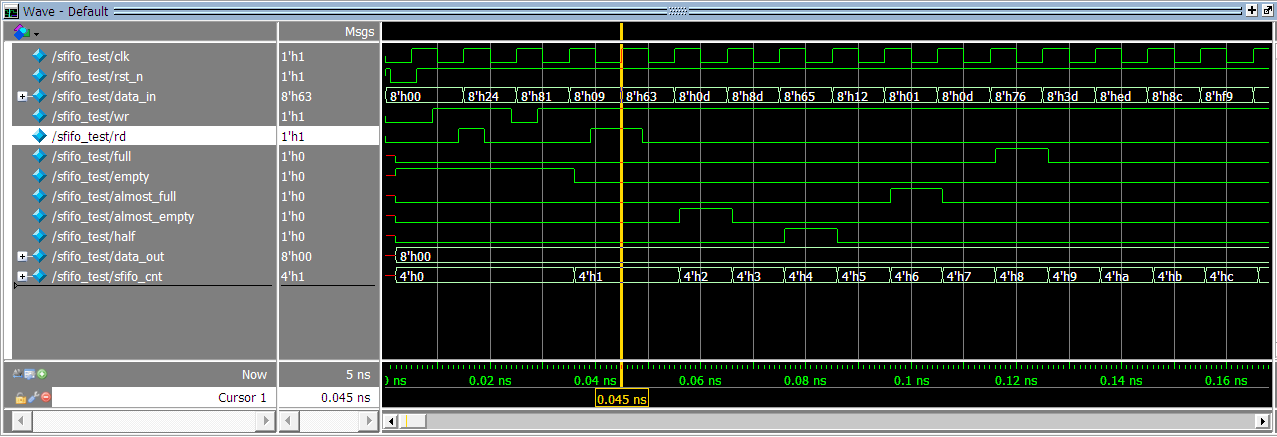

写

同时读写

相关文章:

FPGA/Verilog HDL/AC620零基础入门学习——8*8同步FIFO实验

实验要求 该项目主要实现一个深度为8、位宽为8bit的同步FIFO存储单元。模块功能应包括读控制、写控制、同时读写控制、FIFO满状态、FIFO空状态等逻辑部分。 该项目由一个功能模块和一个testbench组成。其中功能模块的端口信号如下表所示。 提示: (1&a…...

shell脚本

shell函数 函数分类: 系统函数 自定义函数 常用系统函数: basename 从指定路径中获取文件名 dirname 从指定路径中获取目录名,去掉文件名 自定义函数 # 函数的定义 函数名 () { 命令 # 使用$n获取函数的参数 [return 返回…...

不部署服务端调用接口,前端接口神器json-server

简介 json-server 是一款小巧的接口模拟工具,一分钟内就能搭建一套 Restful 风格的 API,尤其适合前端接口测试使用。 只需指定一个 json 文件作为 api 的数据源即可,使用起来非常方便,30秒入门,基本上有手就行。 进阶…...

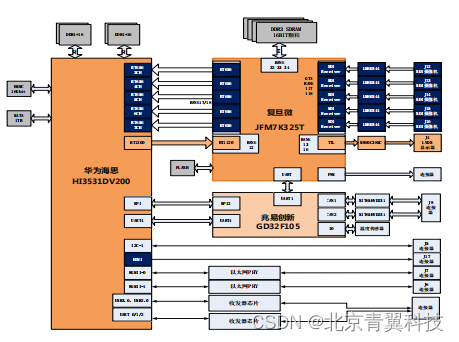

国产化:复旦微JFM7K325T +华为海思 HI3531DV200 的综合视频处理平台

板卡概述 TES714 是自主研制的一款 5 路 HD-SDI 视频采集图像处理平台,该平台采用上海复旦微的高性能 Kintex 系列 FPGA 加上华为海 思的高性能视频处理器 HI3531DV200 来实现。 华为海思的 HI3531DV200 是一款集成了 ARM A53 四核处理 器性能强大的神经网络引擎…...

)

Ceph入门到精通- stderr raise RuntimeError(‘Unable to create a new OSD id‘)

/bin/podman: stderr raise RuntimeError(Unable to create a new OSD id) podman ps |grep osd.0 podman stop osd.0 容器id 重新添加osd.0 集群目录 cd /var/lib/ceph/e8cde810-e4b8-11ed-9ba8-98039b976596/1109 ls1110 rm -rf osd.01111 ceph orch daemon add osd…...

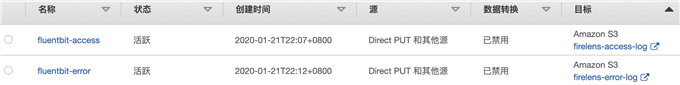

AWSFireLens轻松实现容器日志处理

applog应用程序和fluent-bit共享磁盘,日志内容是json格式数据,输出到S3也是JSON格式 applog应用部分在applog目录: Dockerfile文件内容 FROM alpine RUN mkdir -p /data/logs/ COPY testlog.sh /bin/ RUN chmod 777 /bin/testlog.sh ENTRYP…...

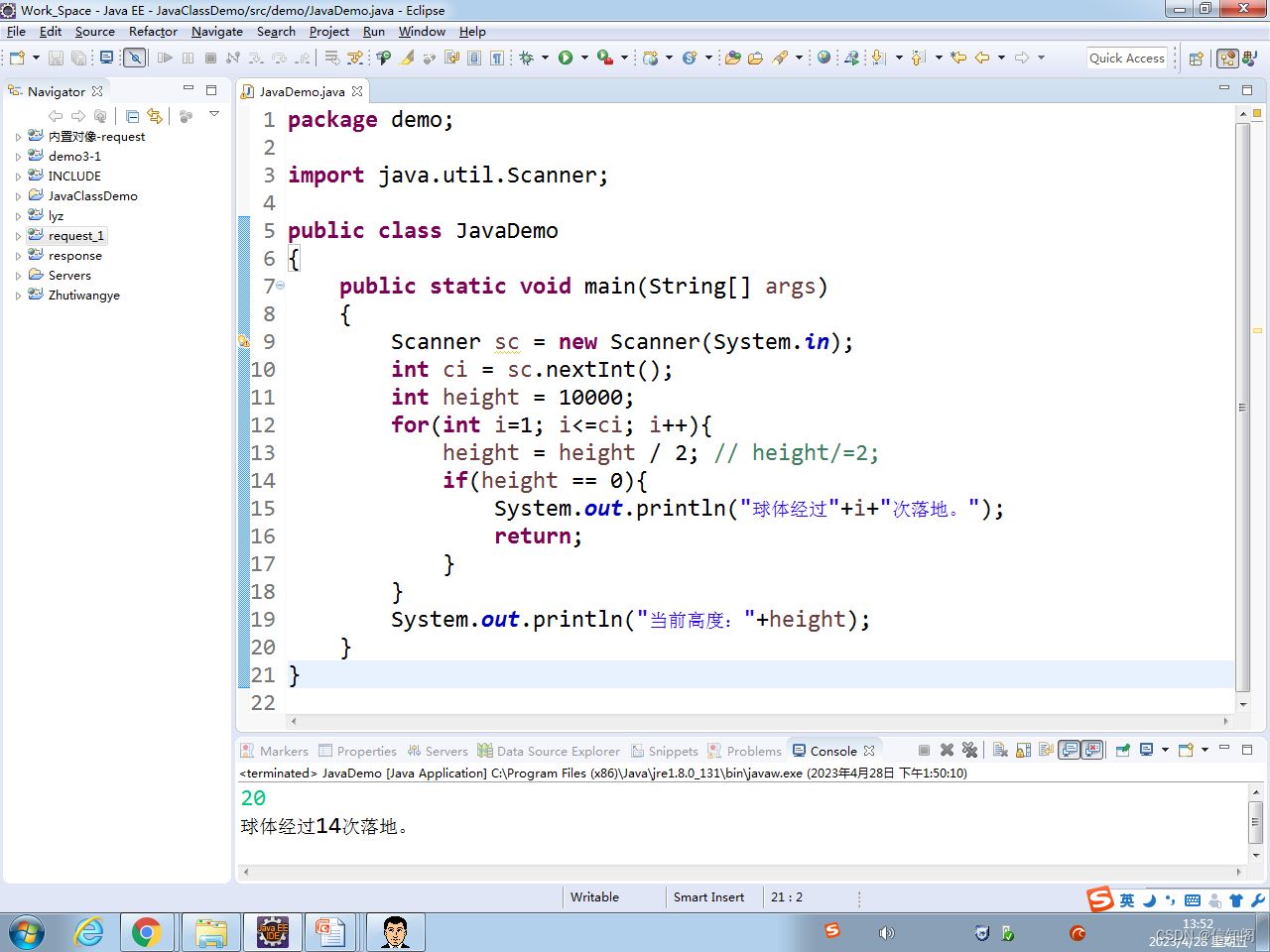

Java程序设计入门教程--案例:自由落体

程序模拟物体从10000米高空掉落后的反弹行为。 球体每落地一次,就会反弹至原高度的一半。按用户输入的弹跳次数,计算球体每次弹跳的高度。 实现过程: 1. 新建项目; 2. 接收 用户输入的弹跳次数: (1&#…...

Qt音视频开发44-本地摄像头推流(支持分辨率/帧率等设置/实时性极高)

一、前言 本地摄像头推流和本地桌面推流类似,无非就是采集的设备源头换成了本地摄像头设备而不是桌面,其他代码完全一样。采集本地摄像头实时视频要注意的是如果设置分辨率和帧率,一定要是设备本身就支持的,如果不支持那就歇菜&a…...

SpringCloud学习(七)——统一网关Gateway

文章目录 1. 网关介绍2. 网关搭建2.1 引入依赖2.2 创建启动类2.3 编写配置2.4 测试 3. 路由断言工厂4. 路由过滤器4.1 过滤器配置4.2 全局过滤器4.3 过滤器执行顺序 5. 跨域问题处理 1. 网关介绍 到现在,我们可以使用Nacos对不同的微服务进行注册并管理配置文件&am…...

《花雕学AI》31:ChatGPT--用关键词/咒语/提示词Prompt激发AI绘画的无限创意!

你有没有想过用AI来画画?ChatGPT是一款基于GPT-3的聊天模式的AI绘画工具,它可以根据你输入的关键词/咒语/提示词Prompt来生成不同风格和主题的画作。Prompt是一些简短的文字,可以用来指导ChatGPT的创作过程。在这篇文章中,我将展示…...

计算机组成原理9控制单元的结构

9.1操作命令的分析 取值周期间址周期执行周期中断周期 取指周期数据流 PC存放下条指令的地址给MAR访问存储器相应单元,将数据取出来送给MDR寄存器,MDR取出来的内容送给IR指令寄存器,然后对指令进行译码,把指令的操作码部分取出…...

MySQL数据备份和恢复

MySQL数据备份和恢复 数据备份 mysqldump是MySQL数据库备份工具,可以备份MySQL数据库中的数据和结构,生成.sql文件,方便数据的迁移和恢复。 使用mysqldump工具前一定要配置环境变量 打开开始菜单,搜索“环境变量”。点击“编辑…...

)

数据结构与算法之链表: Leetcode 237. 删除链表中的节点 (Typescript版)

删除链表中的节点 https://leetcode.cn/problems/delete-node-in-a-linked-list/ 描述 有一个单链表的 head,我们想删除它其中的一个节点 node。 给你一个需要删除的节点 node 。你将 无法访问 第一个节点 head。 链表的所有值都是 唯一的,并且保证给…...

继承的相关介绍---C++

一、概念及定义 概念: 继承(inheritance)机制是面向对象程序设计使代码可以复用的最重要的手段,它允许程序员在保持原有类特性的基础上进行扩展,增加功能,这样产生新的类,称派生类。继承呈现了面向对象程序设计的层次结…...

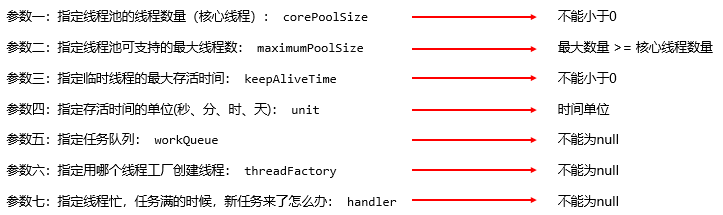

Java多线程深入探讨

1. 线程与进程2. 创建和管理线程2.1. 继承Thread类2.2. 实现Runnable接口2.3 利用Callable、FutureTask接口实现。2.4 Thread的常用方法 3. 线程同步3.1. synchronized关键字3.1.1同步代码块:3.1.2 同步方法: 3.2. Lock接口 4. 线程间通信5. 线程池5.1 使…...

SpringCloud全面学习笔记之进阶篇

目录 前言微服务保护初识Sentinel雪崩问题及解决方案雪崩问题超时处理仓壁模式熔断降级流量控制总结 服务保护技术对比Sentinel介绍和安装微服务整合Sentinel 流量控制快速入门流控模式关联模式链路模式小结 流控效果warm up排队等待 热点参数限流全局参数限流热点参数限流案例…...

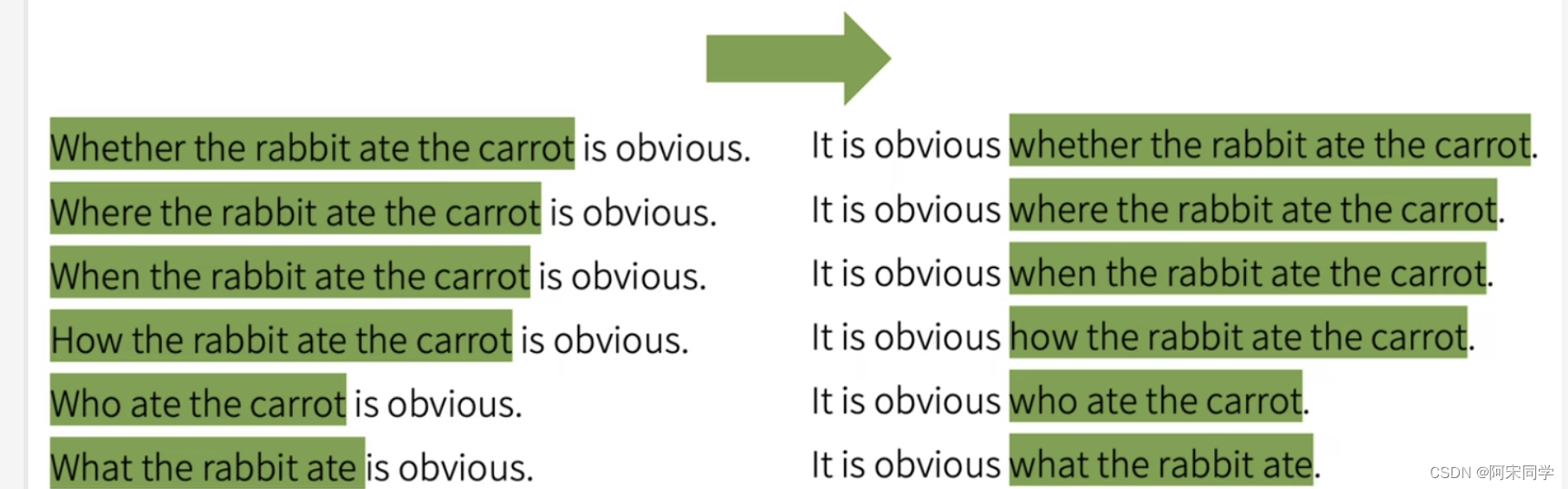

英语中主语从句的概念及其用法,例句(不断更新)

主语从句的原理 主语从句是一种充当整个句子主语的从句,主语从句构成的句子,是要以引导词开头的。它可以用名词性从属连词、关系代词或关系副词引导。主语从句通常位于谓语动词之前,用于表示动作、状态或事件的主体。 以下是一些常用的引导主…...

、子序列,字符串的子串、子序列)

数组的子数组(亚阵列)、子序列,字符串的子串、子序列

数组 子数组 一个或连续多个数组中的元素组成一个子数组 子数组最少包含一个元素 数组 {1, 2, 3} 的子数组是 {1}, {1, 2}, {1, 2, 3}, {2}, {2, 3}, 和 {3}. 子序列 子序列就是在原来序列中找出一部分组成的序列 子序列不一定连续 相对位置还是不变 但是ÿ…...

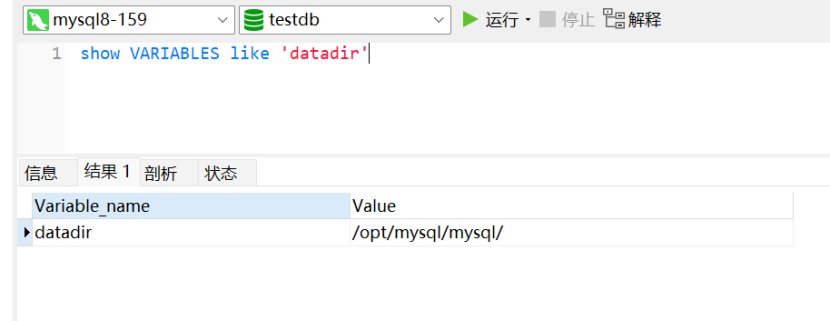

MySQL 知识:迁移数据目录到其他路径

一、系统环境 操作系统:Centos 7 已安装环境:MySQL 8.0.26 二、开始操作 2.1 关闭SELinux 为了提高 Linux 系统的安全性,在 Linux 上通常会使用 SELinux 或 AppArmor 实现强制访问控制(Mandatory Access Control MACÿ…...

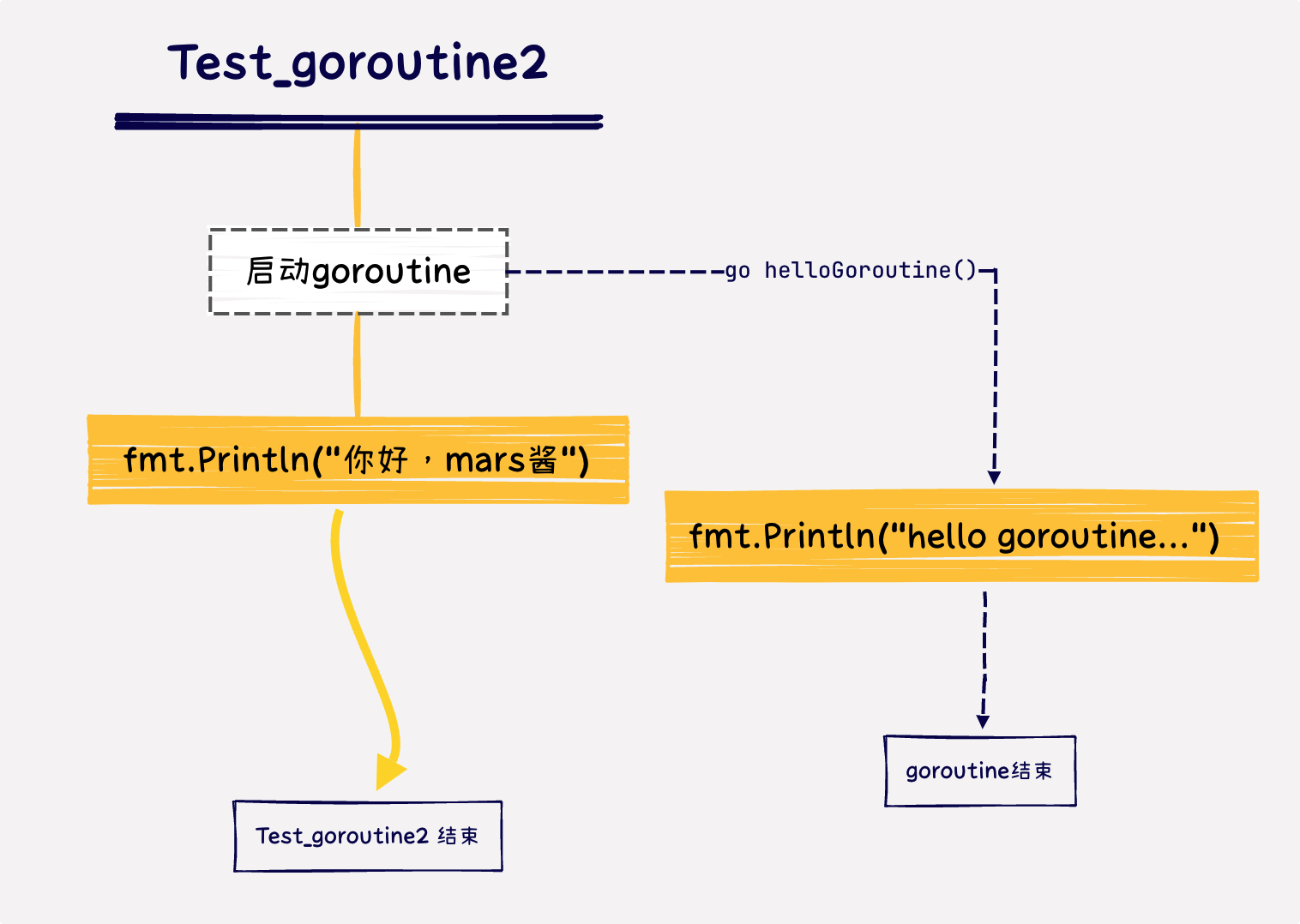

Go | 一分钟掌握Go | 8 - 并发

作者:Mars酱 声明:本文章由Mars酱编写,部分内容来源于网络,如有疑问请联系本人。 转载:欢迎转载,转载前先请联系我! 前言 当今编程界,一个好的编译型语言如果不支持并发,…...

全球供应链重塑下的半导体与PC板行业:工程师的挑战与韧性构建

1. 从“分裂的联盟”到工程师的十字路口 最近翻看行业旧闻,读到一篇2019年EE Times上Rick Merritt的评论文章,标题叫“State of the Disunion”。文章本身探讨的是当时科技行业在政治与全球化张力下的处境,但最让我印象深刻的,是评…...

face-recognition.js 模型训练与保存:构建可复用的人脸识别系统

face-recognition.js 模型训练与保存:构建可复用的人脸识别系统 【免费下载链接】face-recognition.js Simple Node.js package for robust face detection and face recognition. JavaScript and TypeScript API. 项目地址: https://gitcode.com/gh_mirrors/fa/f…...

协作边缘AI与联邦学习如何重塑去中心化能源系统

1. 项目概述:当边缘智能遇见分布式能源如果你和我一样,在能源或者物联网行业摸爬滚打多年,就会深刻感受到一个趋势:能源系统的“大脑”正在从云端下沉,从中心走向边缘。过去,我们习惯于将海量的传感器数据—…...

边缘计算中的3D占据映射技术与Gleanmer SoC优化

1. 边缘计算时代的3D占据映射技术革新在自动驾驶汽车穿越复杂城市道路时,在AR眼镜试图将虚拟物体精准叠加到现实场景时,设备都需要实时理解周围环境的3D结构。传统解决方案如激光雷达点云只能提供稀疏的空间采样,而基于体素的OctoMap虽然能构…...

ARM架构ACTLR寄存器详解与性能优化实践

1. ARM架构中的ACTLR寄存器深度解析在ARMv7/v8架构中,系统寄存器扮演着处理器与操作系统间的关键接口角色。作为其中的特殊存在,ACTLR(Auxiliary Control Register)辅助控制寄存器为开发者提供了对处理器底层行为的精细控制能力。…...

JAVA学习之JAVASE基础

集合列表ListArrayList利用空参创建的集合,在底层创建一个默认长度为0的数组添加第一个元素时,底层会创建一个新的长度为10的数组存满时,会扩容1.5倍一次存多个元素,1.5倍还不够,则新创建的数组长度以实际为准LinkedLi…...

GLM-ASR开源语音识别引擎:基于GLM架构的端到端实践指南

1. 项目概述:一个开源的、基于GLM架构的语音识别引擎最近在语音识别(ASR)这个圈子里,一个名为“GLM-ASR”的开源项目引起了我的注意。它来自zai-org组织,顾名思义,其核心是将自然语言处理领域大放异彩的GLM…...

)

SITS 2026闭门工作坊流出的7个LLM推理性能反模式(含3个被主流框架默认启用的致命配置)

更多请点击: https://intelliparadigm.com 第一章:AI原生性能优化:SITS 2026 LLM推理加速实战技巧 在 SITS 2026 基准测试中,LLM 推理延迟与显存带宽利用率成为关键瓶颈。AI 原生优化并非简单套用传统 CUDA kernel 调优ÿ…...

docker-maven-plugin 源码解析:深入理解插件架构与实现原理

docker-maven-plugin 源码解析:深入理解插件架构与实现原理 【免费下载链接】docker-maven-plugin Maven plugin for running and creating Docker images 项目地址: https://gitcode.com/gh_mirrors/doc/docker-maven-plugin 一、插件核心架构概览 docker-…...

AI编程效率革命:Cursor Rules配置实战与团队协作指南

1. 项目概述:从“Cursor Rules”看现代开发者的效率革命最近在GitHub上看到一个名为usrrname/cursorrules的项目,这个标题乍一看有点意思,它直接点明了两个核心要素:cursor和rules。对于深度使用Cursor这款AI代码编辑器的开发者来…...