Verilog | FIFO简单实现

FIFO( First Input First Output)简单说就是指先进先出,也是缓存机制的一种,下面是我总结的 FIFO 的三大用途:

1)提高传输效率,增加 DDR 带宽的利用率。比如我们有 4 路视频数据缓存到 DDR 中去,比较笨的方法是,每个通道视频数据对应一颗 DDR。现在对于 DDR 来说非常浪费,因为现在的 DDR3 可以跑 1600Mbps DDR4 可以跑到2400Mbps,如果你还是把一路视频数据对应一颗 DDR 显然严重浪费了带宽。加入 FIFO 后,只要把 4 路数据先缓存进入 DDR,在缓存的过程中,快速得把数据从 FIFO 取出并且写入到 DDR 中,只要 FIFO 没有满就不会出现数据丢失。现在我们带宽够用,FIFO 给的足够大就可以确保数据不丢失。

2)数据位宽转换,比如我们有 32bit 的数据需要转换成 128bit 或者 32bit 的数据需要转换成 8bit,那么用 FIFO 来转换也是非常方便的。

3)跨时钟域的应用,比如数据是 2 个不同步的时钟,那么我们就可以用 FIFO 实现跨时钟域的传输。

以上总计的三点,很多时候是混合使用的。

FIFO的重点和难点是空满状态的判断。

同步FIFO

同步FIFO是指读写数据使用的是同一个时钟,所以不用进行跨时钟域处理。有两种设计方法:高位扩展法和计数器法

本程序设置了统计FIFO内部数据数量的计数器cnt,并根据计数器的大小判断空满。设FIFO的深度是DEPTH,如果cnt==0,说明FIFO内没有数据;如果cnt==DEPTH,说明FIFO已存满。

计数器根据读写信号自增或者自减。当读写同时进行时,计数器数值不变;当有效写入时计数器减1;当有效读取时,计数器加1。

`timescale 1ns/1ns

/**********************************RAM************************************/

module dual_port_RAM #(parameter DEPTH = 16,parameter WIDTH = 8)(input wclk,input wenc,input [$clog2(DEPTH)-1:0] waddr //深度对2取对数,得到地址的位宽。,input [WIDTH-1:0] wdata //数据写入,input rclk,input renc,input [$clog2(DEPTH)-1:0] raddr //深度对2取对数,得到地址的位宽。,output reg [WIDTH-1:0] rdata //数据输出

);reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];always @(posedge wclk) beginif(wenc)RAM_MEM[waddr] <= wdata;

end always @(posedge rclk) beginif(renc)rdata <= RAM_MEM[raddr];

end endmodule /**********************************SFIFO************************************/

module sfifo#(parameter WIDTH = 8,parameter DEPTH = 16

)(input clk , input rst_n ,input winc ,input rinc ,input [WIDTH-1:0] wdata ,output reg wfull ,output reg rempty ,output wire [WIDTH-1:0] rdata

);reg [$clog2(DEPTH)-1:0] waddr, raddr;reg [$clog2(DEPTH) :0] cnt;always@(posedge clk or negedge rst_n) beginif(~rst_n)waddr <= 0;elsewaddr <= winc&~wfull? waddr+1: waddr;endalways@(posedge clk or negedge rst_n) beginif(~rst_n)raddr <= 0;elseraddr <= rinc&~rempty? raddr+1:raddr;endalways@(posedge clk or negedge rst_n) beginif(~rst_n)cnt <= 0;else if(rinc&~rempty&winc&~wfull)cnt <= cnt;else if(winc&~wfull)cnt <= cnt + 1;else if(rinc&~rempty)cnt <= cnt - 1;elsecnt <= cnt;endalways@(posedge clk or negedge rst_n) beginif(~rst_n) beginwfull = 0;rempty = 0;endelse beginwfull = cnt == DEPTH;rempty = cnt == 0;endenddual_port_RAM #(.DEPTH(DEPTH ),.WIDTH(WIDTH ))myRAM(.wclk (clk ), .wenc (winc&~wfull ), .waddr(waddr ), .wdata(wdata ), .rclk (clk ), .renc (rinc&~rempty), .raddr(raddr ), .rdata(rdata ));

endmodule

异步FIFO

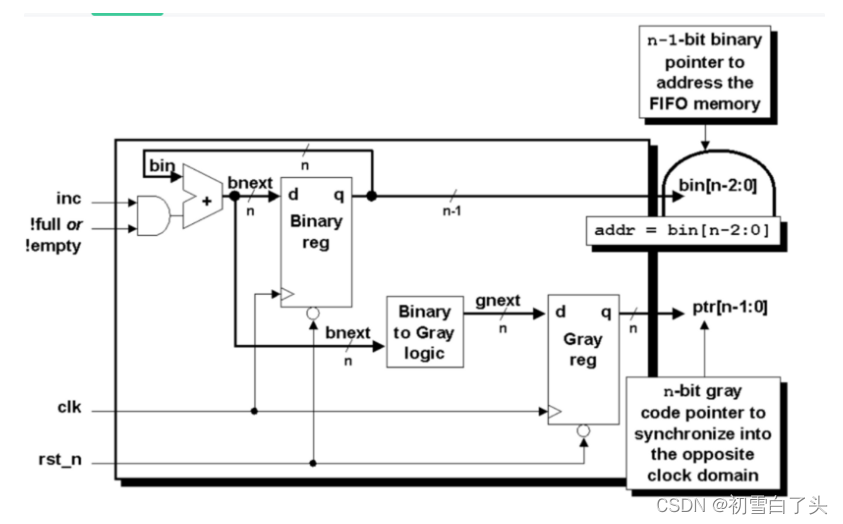

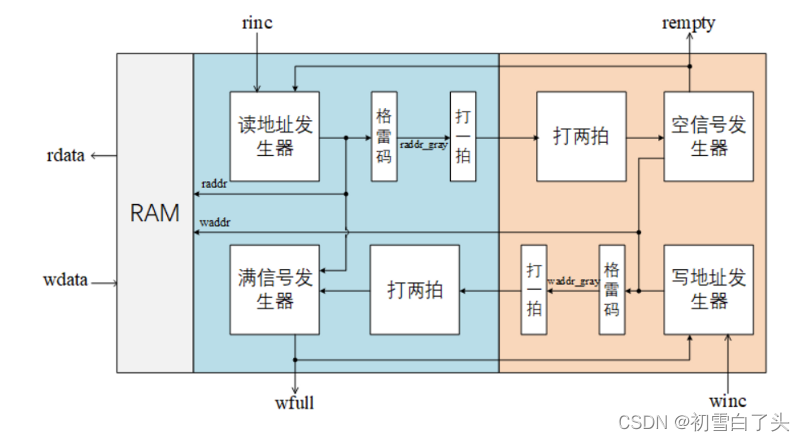

异步FIFO的与同步FIFO的核心区别是它的读时钟和写时钟是不同步的。所以用对比读写地址的方法产生空满信号时,要进行跨时钟域处理。为了降低亚稳态可能性,异步FIFO还引入了格雷码。同时,格雷码也更方便产生空满信号。

| 二进制 | 写地址 | 读地址 | 格雷码 | 写地址 | 读地址 |

|---|---|---|---|---|---|

| 空FIFO | 0 0000 | 0 0000 | 0 0000 | 0 0000 | |

| 写满 | 1 0000 | 0 0000 | 1 1000 | 0 0000 | |

| 读空 | 1 0000 | 1 0000 | 1 1000 | 1 1000 | |

| 写满 | 0 0000 | 1 0000 | 0 0000 | 1 1000 | |

| 读空 | 0 0000 | 0 0000 | 0 0000 | 0 0000 |

FIFO深度为16时,地址位宽位5,当最高位和次高位不相同,其余位相同认为是写满;当所有位相同认为是读空。

异步FIFO主要包含四部分:读写地址发生器、格雷码的产生与打拍、空满信号发生器以及RAM。

`timescale 1ns/1ns/***************************************RAM*****************************************/

module dual_port_RAM #(parameter DEPTH = 16,parameter WIDTH = 8)(input wclk,input wenc,input [$clog2(DEPTH)-1:0] waddr //深度对2取对数,得到地址的位宽。,input [WIDTH-1:0] wdata //数据写入,input rclk,input renc,input [$clog2(DEPTH)-1:0] raddr //深度对2取对数,得到地址的位宽。,output reg [WIDTH-1:0] rdata //数据输出

);reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];always @(posedge wclk) beginif(wenc)RAM_MEM[waddr] <= wdata;

end always @(posedge rclk) beginif(renc)rdata <= RAM_MEM[raddr];

end endmodule /***************************************AFIFO*****************************************/

module asyn_fifo#(parameter WIDTH = 8,parameter DEPTH = 16

)(input wclk , input rclk , input wrstn ,input rrstn ,input winc ,input rinc ,input [WIDTH-1:0] wdata ,output wire wfull ,output wire rempty ,output wire [WIDTH-1:0] rdata

);parameter addr_width = $clog2(DEPTH);//写指针--二进制reg [addr_width:0]wptr_bin,rptr_bin;always@(posedge wclk or negedge wrstn)beginif(!wrstn) wptr_bin <= 0;else if(winc && !wfull) wptr_bin <= wptr_bin +1;else ;end//读指针--二进制always@(posedge rclk or negedge rrstn)beginif(!rrstn) rptr_bin <= 0;else if(rinc && !rempty) rptr_bin <= rptr_bin +1;else ;end// 指针二进制转格雷码wire [addr_width:0]wptr_gray,rptr_gray;assign wptr_gray = wptr_bin ^ wptr_bin>>1;assign rptr_gray = rptr_bin ^ rptr_bin>>1;//reg [addr_width:0]wptr,rptr;always @(posedge wclk or negedge wrstn)beginif(!wrstn) wptr <= 0;else wptr <= wptr_gray;end// always @(posedge rclk or negedge rrstn)beginif(!rrstn) rptr <= 0;else rptr <= rptr_gray;end// 经两级锁存器进行时钟同步reg [addr_width:0]sync_r2w,rptr_temp,sync_w2r,wptr_temp;// 写时针同步always @(posedge wclk or negedge wrstn)beginif(!wrstn) beginsync_r2w <= 0 ;rptr_temp <= 0;endelse beginrptr_temp <= rptr;sync_r2w <= rptr_temp;endend// 读时针同步always @(posedge rclk or negedge rrstn)beginif(!rrstn) beginsync_w2r <= 0 ;wptr_temp <= 0;endelse beginwptr_temp <= wptr;sync_w2r <= wptr_temp;endend// 判断写满读空状态assign wfull = wptr == {~sync_r2w[addr_width:addr_width-1],sync_r2w[addr_width-2:0]};assign rempty = rptr == sync_w2r;// 读数据(调用ram)dual_port_RAM #(.DEPTH(DEPTH),.WIDTH(WIDTH))dual_port_RAM(.wclk(wclk),.wenc(winc && !wfull),.waddr(wptr_bin[addr_width-1:0]),.wdata(wdata),.rclk(rclk),.renc(rinc && !rempty),.raddr(rptr_bin[addr_width-1:0]),.rdata(rdata));endmodule

补充

- 空和满时,读写指针末尾不一定全是0哦。换句话说,fifo的工作过程不一定是:先写满再读空再写满再读空这样的,也可能是边读边写,甚至可能同时读写。因此假设读指针为10011,写指针为00011(二进制),这也是fifo满。

- 亚稳态是在时钟跳变时,寄存器采样到一个逻辑0和逻辑1参考电压的中间值,这是亚稳态的概念。而亚稳态经过一段时间逐渐恢复成逻辑0或1,而具体会成为0还是1这件事是无法预测的。说回来,出现亚稳态的原因根源是被采样信号在时钟沿发生了跳变。一般情况下,同步时钟在保证setup和hold的情况下不会出现亚稳态(这也同步时钟不需要转格雷码的原因),而异步时钟相位关系无法设定,有可能同步前的信号正好在目标时钟沿跳变,有概率出现亚稳态,使用格雷码降低这种概率。一旦格雷码在跳变时也出现亚稳态,因为亚稳态最终也会恢复成逻辑0或1嘛,所以亚稳态后的格雷码相比于跳变前也可能会出现两种情况:正常跳变或者没有跳变。对于正常跳变,当然不会对结果产生任何影响;对于非正常跳变也就是格雷码没有跳变,会使被同步的指针更加保守,而可能加剧假空或者假满的程度,但不会造成功能错误,这也是选择用格雷码跨时钟的重要原因。

相关文章:

Verilog | FIFO简单实现

FIFO( First Input First Output)简单说就是指先进先出,也是缓存机制的一种,下面是我总结的 FIFO 的三大用途: 1)提高传输效率,增加 DDR 带宽的利用率。比如我们有 4 路视频数据缓存到 DDR 中去,比较笨的方法是&#x…...

设计模式应用场景

设计模式简介 工厂模式(Factory Pattern):使用工厂方法创建对象,而不是使用new关键字直接实例化对象。 抽象工厂模式(Abstract Factory Pattern):提供一个创建一系列相关对象的接口,…...

还在老一套?STM32使用新KEIL5的IDE,全新开发模式RTE介绍及使用

Keil新版本出来了,推出了一种全新开发模式RTE框架( Run-Time Environment),更好用了。然而网上的教程资料竟还都是把Keil5当成Keil4来用,直接不使用这个功能。当前正点原子或野火的教程提供的例程虽有提到Keil5,但也是基本上当Kei…...

Java时间类(十一) -- Date类工具类 -- Java获取当天、本周、本月、本年 开始及结束时间

目录 1. 今天的日期如下: 2. DateUtils工具类的源代码: 3. 测试类 1. 今天的日期如下:...

Alma Linux 9.2、Rocky Linux 9.2现在是RHEL 9.2的替代品

随着Red Hat Enterprise Linux (RHEL) 9.2的发布,Alma Linux 9.2和Rocky Linux 9.2成为了RHEL 9.2的备选替代品。这两个Linux发行版旨在提供与RHEL兼容的功能和稳定性,以满足那些需要企业级操作系统的用户需求。本文将详细介绍Alma Linux 9.2和Rocky Lin…...

推荐5款提高生活和工作效率的好帮手

在这个数字化时代,软件工具已经深深地影响和改变了我们的生活和工作。有着各种各样的软件工具,它们都可以在特定的领域内让我们变得更加高效,完成复杂的任务。选择一款适合你的软件工具,不但可以极大地释放生产力,也可以让生活变得更加便捷。 1.桌面图标管理工具——TileIconi…...

美团小组长薪资被应届生员工倒挂7K,不把老员工当人?

一位美团的小管理爆出,无意中看到了整个部门薪资,本以为自己算比较高的,但看完之后整个人都傻眼了。小组长的职位月薪28K,而手下组员却是35K,当天晚上抽了一包烟也没想明白是为什么。 楼主表示,自己是美团的…...

【Java多线程案例】使用阻塞队列实现生产者消费者模型

前言 本篇文章讲解多线程案例之阻塞队列。主要讲解阻塞队列的特性、实际开发中常用的到的生产者消费者模型,以及生产者消费者模型解耦合、削峰填谷的好处。并且使用 Java 多线程模拟实现一个生产者消费者模型、阻塞队列版的生产者消费者模型。 文章从什么是阻塞队列…...

Spark 3:Spark Core RDD持久化

RDD 的数据是过程数据 RDD 的缓存 # coding:utf8 import timefrom pyspark import SparkConf, SparkContext from pyspark.storagelevel import StorageLevelif __name__ __main__:conf SparkConf().setAppName("test").setMaster("local[*]")sc SparkC…...

字节跳动五面都过了,结果被刷了,问了hr原因竟说是...

摘要 说在前面,面试时最好不要虚报工资。本来字节跳动是很想去的,几轮面试也通过了,最后没offer,自己只想到几个原因:1、虚报工资,比实际高30%;2、有更好的人选,这个可能性不大&…...

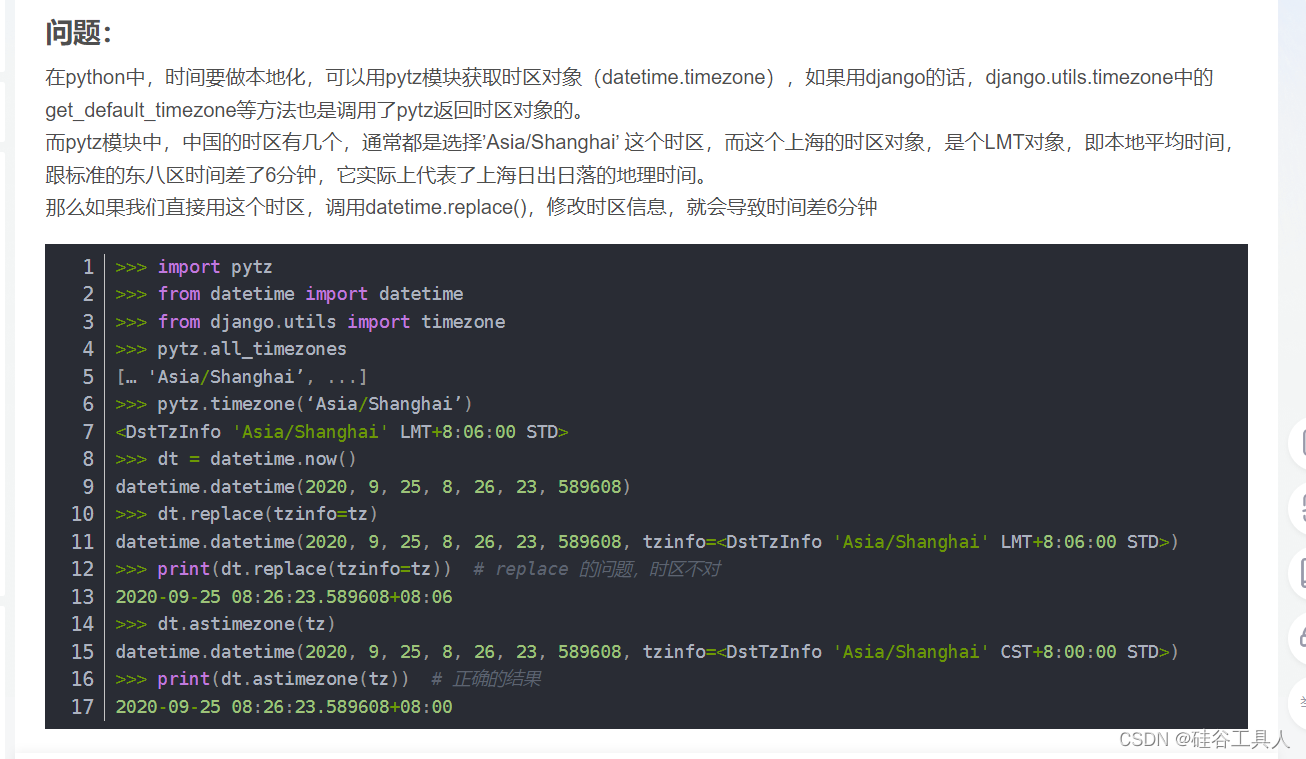

Python日期带时区转换工具类总结

文章目录 1.背景2. 遇到的坑3. 一些小案例3.1 当前日期、日期时间、UTC日期时间3.2 昨天、昨天UTC日期、昨天现在这个时间点的时间戳3.3 日期转时间戳3.4 时间戳转日期3.5 日期加减、小时的加减 4. 总结5. 完整的编码 1.背景 最近项目是国际项目,所以需要经常需要用…...

视频会议产品对比分析

内网视频会议系统如何选择?有很多单位为了保密,只能使用内部网络,无法连接互联网,那些SaaS视频会议就无法使用。在内网的优秀视频会议也有很多可供选择,以下是几个常用的: 1. 宝利通:它支持多种…...

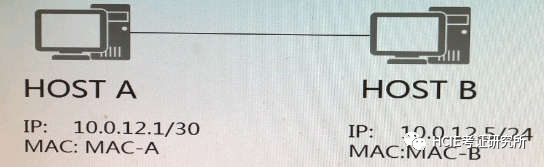

每日一练 | 华为认证真题练习Day47

1、某台路由器输出信息如下,下列说法错误的是?(多选) A. 本路由器开启了区域认证 B. 本设备出现故障,配置的Router Id和实际生效的Router ID不一致 C. 本设备生效的Router Id为10.0.12.1 D. 本设备生效的Router Id为…...

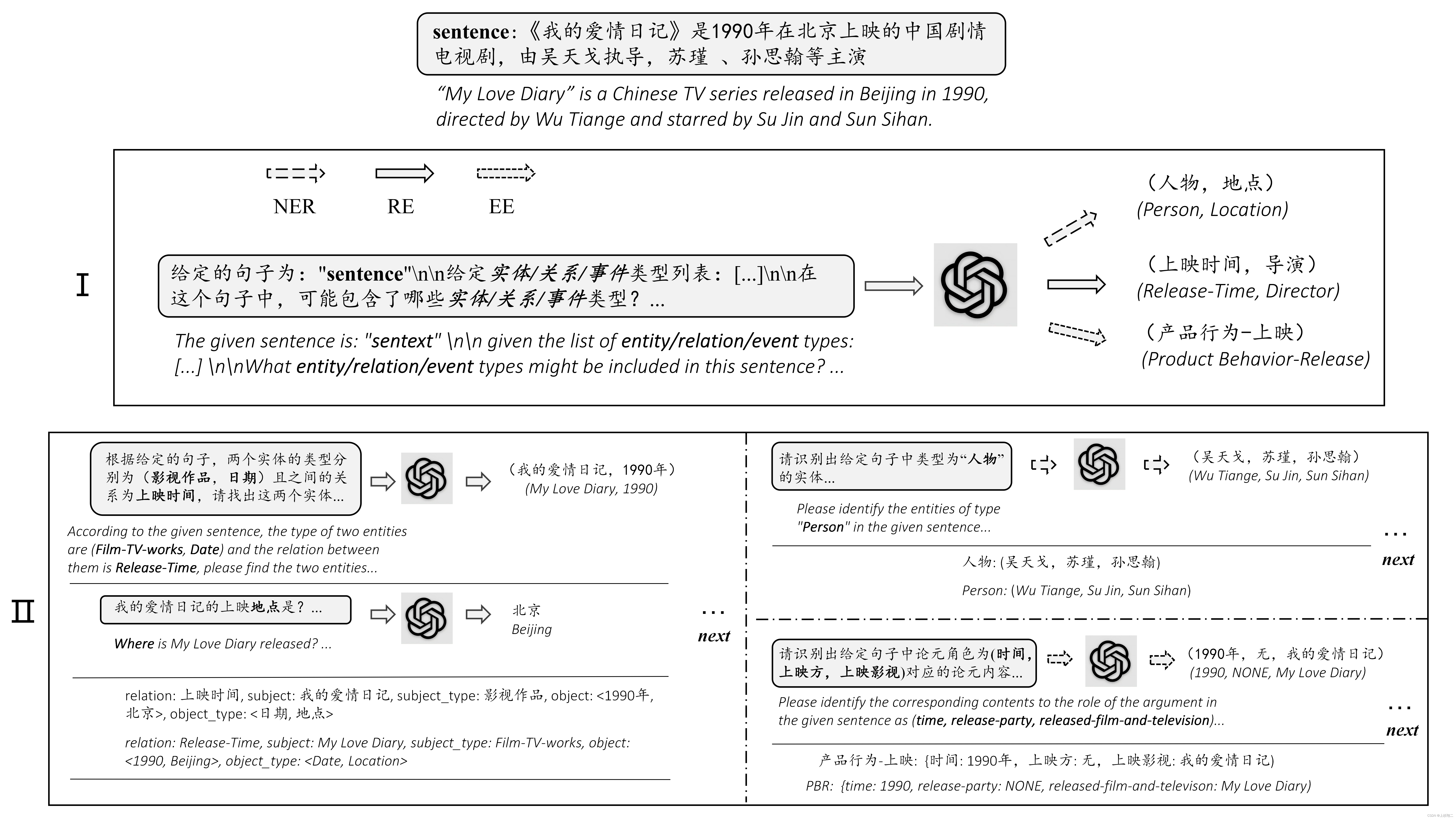

ChatIE(LLM大模型用于信息抽取)

Zero-Shot Information Extraction via Chatting with ChatGPT paper:https://arxiv.org/abs/2302.10205 利用ChatGPT实现零样本信息抽取(Information Extraction,IE),看到零样本就能大概明白这篇文章将以ChatGPT作为…...

提升企业管理效率的利器——ADManager Plus

在当今信息时代,企业的规模和复杂性不断增长,管理各个方面变得愈发具有挑战性。而在企业管理中,活跃目录(Active Directory)起着至关重要的作用。它是一种用于组织内部的用户、计算机、组和其他对象进行集中管理的目录…...

《入侵的艺术》读书心得:第六章:渗透测试中的智慧与愚昧

第六章:渗透测试中的智慧与愚昧 这些想法是愚昧的 1.任何期待渗透测试结果是“毫无破绽”、“无懈可击”…都是极其愚昧的: 第一层含义:测试的不可穷尽性原理(同软件测试) 第二层含义:作为优秀甚至只是合…...

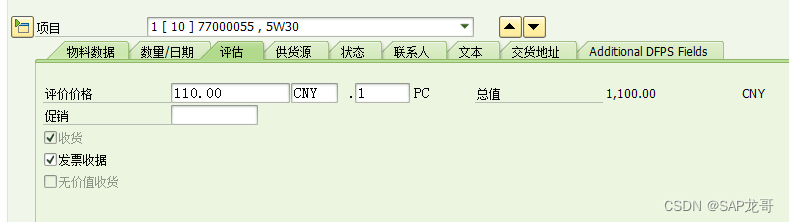

SAP-MM-采购申请-价值特性

采购申请审批在维护价值特性时要注意是抬头价值还是行价值,要确定选择哪个,配置时对应配置。 1、创建价值特性CT04 字段名称:CEBAN-GSWRT,和CEBAN-GFWRT 抬头总价值:CEBAN-GFWRT;如果选择的是抬头审批&am…...

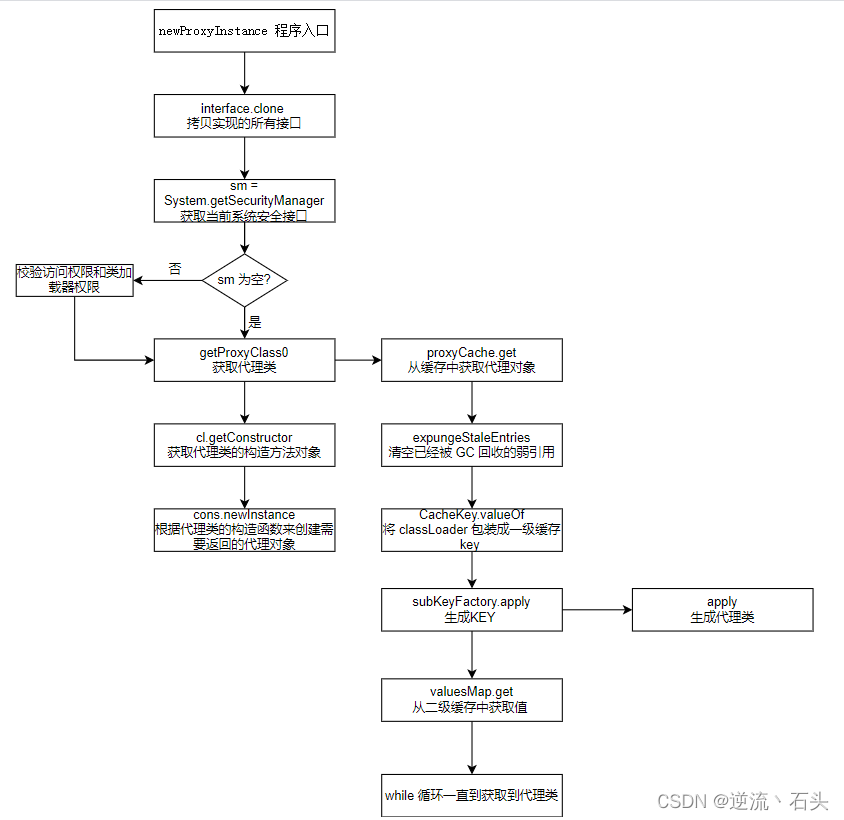

设计模式 - 代理模式

基本介绍: 代理模式:为一个对象提供一个替身,以控制对这个对象的访问。即通过代理 对象访问目标对象.这样做的好处是:可以在目标对象实现的基础上,增强额外的 功能操作,即扩展目标对象的功能。被代理的对象可以是远程对象、创建开销大的对象或需要安全控…...

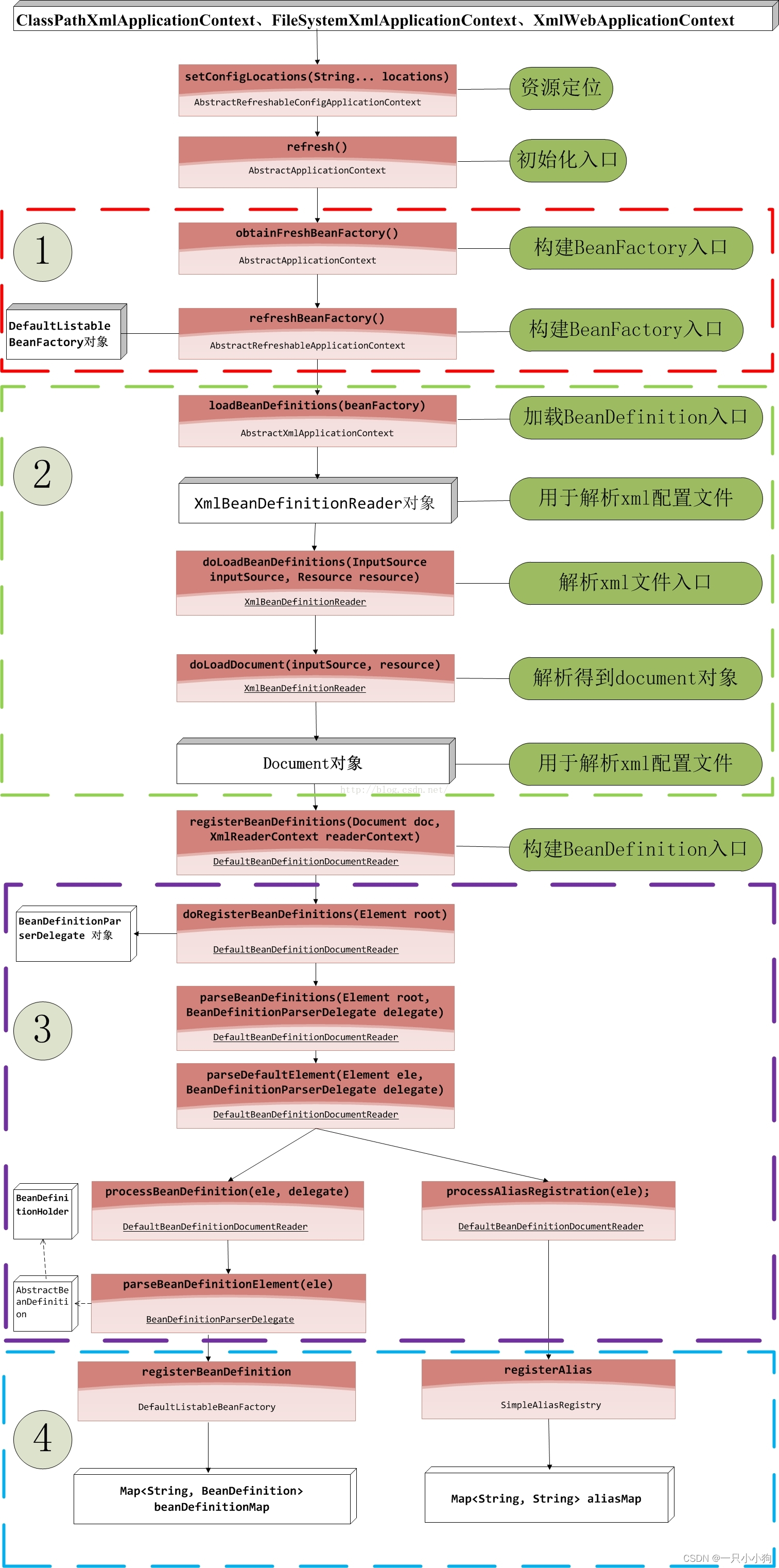

IOC初始化 IOC启动阶段 (Spring容器的启动流程)

[toc](IOC初始化 IOC启动阶段 (Spring容器的启动流程)) IOC初始化 IOC启动阶段 (Spring容器的启动流程) Resource定位过程:这个过程是指定位BeanDefinition的资源,也就是配置文件(如xml)的位置,并将其封装成Resource对…...

)

Java后端入职第四天,就被要求代码回退(Git回退实战)

一、需求背景 初入职场,由于自己的失误或者对git不熟悉,把被人的代码给冲突掉了,然后需要立马回滚,对于新手开发,应该比较常见吧!或者,比较多一种情况,错误把工程add了到了暂存区,比如一些本地配置,本来就不应该提交的,又或者,开发中只提交部分代码,又想最新的提…...

的内存分配机制)

深入解析C语言malloc(0)的内存分配机制

1. 深入解析 malloc(0) 的行为机制在 C 语言编程中,内存管理是一个基础但极其重要的话题。malloc 函数作为动态内存分配的核心工具,其行为规范在 C 标准中有明确定义。然而,当我们遇到像 malloc(0) 这样的边界情况时,事情就变得有…...

escodegen浏览器端使用教程:在Web环境中实现代码生成

escodegen浏览器端使用教程:在Web环境中实现代码生成 【免费下载链接】escodegen ECMAScript code generator 项目地址: https://gitcode.com/gh_mirrors/es/escodegen escodegen是一个强大的ECMAScript代码生成器,它能够将抽象语法树(AST)转换回…...

5分钟上手Velocity动态主题动画:让界面动效随用户偏好智能切换

5分钟上手Velocity动态主题动画:让界面动效随用户偏好智能切换 【免费下载链接】velocity Accelerated JavaScript animation. 项目地址: https://gitcode.com/gh_mirrors/ve/velocity Velocity是一款高性能的JavaScript动画库,专注于提供流畅、高…...

文心一言搜索优化,做好这件事就赢了一半

如果你在文心一言上铺了几百篇内容,但品牌词一问,AI还是引用别人——你缺的不是数量,是质量锚点。文心一言的算法有一套对“优质可信内容”的隐形成交系统,没通过质检的内容,发再多也是无效库存。去年我们实测过一个案…...

实现堆和用堆实现排序数组

什么是堆 就是完全二叉树 前h-1层都是满的 最后一层可以不满,但从左到右必须连续。 逻辑上是链 物理上是数组 首先,实现堆 一、定义一个结构体,用来存3个值 a就是的数组地址 size是有效元素的个数 capacity是总容量,size…...

智慧校园厂家怎么选?看懂这 5 个核心功能再决定不迟

✅作者简介:合肥自友科技 📌核心产品:智慧校园平台(包括教工管理、学工管理、教务管理、考务管理、后勤管理、德育管理、资产管理、公寓管理、实习管理、就业管理、离校管理、科研平台、档案管理、学生平台等26个子平台) 。公司所有人员均有多…...

07_微服务划分与团队人数之渐进式拆分与团队演进

微服务划分与团队人数之渐进式拆分与团队演进 体系内容 演进方法:单体优先、边界识别、服务化拆分、平台能力沉淀 组织演进:小团队、部落-小队、平台团队、架构治理机制 Spring Cloud Alibaba 路线:Nacos、Gateway、Sentinel、RocketMQ、Seata 逐步引入 决策重点:什么时候…...

)

Rancher国内网络卡脖子?手把手教你配置私有镜像仓库(避坑RKE2 registries.yaml)

Rancher国内网络优化实战:私有镜像仓库配置全指南 引言 对于国内Kubernetes从业者来说,Rancher无疑是一款强大的集群管理工具。但在实际部署过程中,许多团队都遇到过因网络问题导致镜像拉取失败的困扰。想象一下,当你正准备部署一…...

高速移动场景下无线信道的延迟-多普勒域建模与优化

1. 高速移动场景下的无线信道挑战 想象一下你正坐在时速120公里的高铁上刷视频,突然画面开始卡顿——这就是典型的高速移动场景通信问题。当收发端相对速度超过100km/h时,传统无线信道模型就会像老式收音机遇到隧道一样"失灵"。我在参与某车企…...

读懂?)

claw-code 源码详细分析:子系统目录地图——几十个顶层包如何用五条轴(会话 / 工具 / 扩展 / 入口 / 桥接)读懂?

范围:src/ 下 顶层包(含 */__init__.py 的目录)与 与会话/runtime 强相关的根模块;与 result/01_start.md 第十三节、「清单—路由—会话」叙事一致。1. 为什么用五条轴 src/ 里同时存在: 大量占位包(读 re…...