状态机思想编程

1. LED流水灯的FPGA代码

在这个任务中,首先我们会使用状态机的思想来设计一个LED流水灯的控制逻辑。LED流水灯一般需要依次点亮不同的LED,并且循环播放。我们将其分为几个状态,每个状态控制一个或一组LED灯。

状态机设计

假设我们有8个LED(从LED0到LED7),流水灯的效果是依次点亮每一个LED,最终循环回第一个LED。

状态机的实现步骤

- 设计一个3位的状态寄存器,用于表示当前LED的状态(点亮的LED)。

- 在每个时钟周期,更新状态寄存器,控制下一个LED点亮。

- 当状态寄存器达到最后一个LED时,重新回到第一个LED。

Verilog 代码实现:

module led_fsm(input clk, // 时钟信号input rst_n, // 复位信号,低电平有效output reg [7:0] led // 8个LED的输出

);// 定义状态reg [2:0] state; // 3位状态寄存器,用于表示当前的LEDreg [2:0] next_state; // 下一个状态// 状态定义parameter S0 = 3'b000, // LED0S1 = 3'b001, // LED1S2 = 3'b010, // LED2S3 = 3'b011, // LED3S4 = 3'b100, // LED4S5 = 3'b101, // LED5S6 = 3'b110, // LED6S7 = 3'b111; // LED7// 状态机逻辑:根据当前状态和时钟,决定下一个状态always @ (posedge clk or negedge rst_n) beginif (~rst_n) state <= S0; // 复位时回到初始状态elsestate <= next_state;end// 下一个状态逻辑always @ (state) begincase(state)S0: next_state = S1;S1: next_state = S2;S2: next_state = S3;S3: next_state = S4;S4: next_state = S5;S5: next_state = S6;S6: next_state = S7;S7: next_state = S0;default: next_state = S0; // 默认状态endcaseend// 根据当前状态控制LED的输出always @ (state) begincase(state)S0: led = 8'b00000001;S1: led = 8'b00000010;S2: led = 8'b00000100;S3: led = 8'b00001000;S4: led = 8'b00010000;S5: led = 8'b00100000;S6: led = 8'b01000000;S7: led = 8'b10000000;default: led = 8'b00000001; // 默认状态endcaseendendmodule

测试代码:

接下来编写一个简单的测试平台,用于仿真测试这个LED流水灯的设计。

module tb_led_fsm;reg clk;reg rst_n;wire [7:0] led;// 实例化待测试模块led_fsm uut (.clk(clk),.rst_n(rst_n),.led(led));// 时钟生成always begin#5 clk = ~clk; // 10ns周期的时钟end// 初始化信号initial beginclk = 0;rst_n = 0;#10 rst_n = 1; // 10ns后解除复位#100; // 等待足够的时间以观察流水灯效果$stop; // 停止仿真end// 监视LED的变化initial begin$monitor("At time %t, LED = %b", $time, led);endendmodule

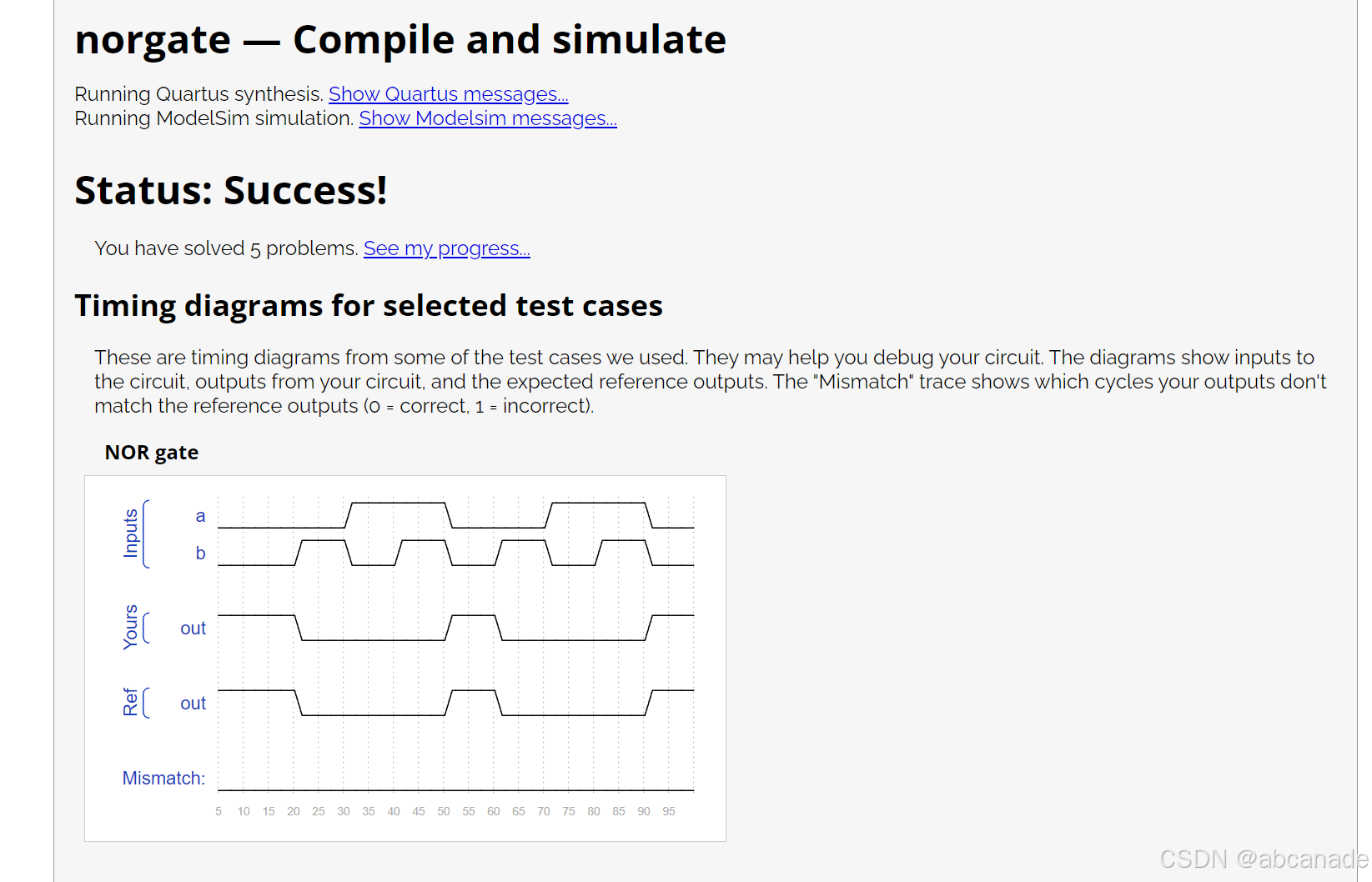

仿真分析:

- 使用ModelSim打开工程。

- 编译Verilog代码。

- 运行仿真,查看led的变化。

DE2-115板验证:

- 将上述Verilog代码加载到DE2-115 FPGA开发板中。

- 使用Qsys或SystemVerilog工具进行配置。

- 编写一个简单的约束文件,确保LED和时钟信号正确连接。

- 使用Quartus II编译和烧录程序到FPGA开发板,观察LED的流水灯效果。

2. CPLD与FPGA的主要技术区别

CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)的主要区别:

-

架构:

- CPLD通常具有较少的逻辑资源,采用宏单元(宏块)结构。

- FPGA具有更多的逻辑单元,采用可编程逻辑阵列结构,适用于更复杂的应用。

-

容量:

- CPLD的逻辑资源较少,适合简单的逻辑控制任务。

- FPGA具有更大的逻辑资源和更高的逻辑密度,适合复杂的并行处理和高性能任务。

-

功耗:

- CPLD功耗较低,适合低功耗应用。

- FPGA相对功耗较高,尤其是高密度FPGA。

-

速度:

- CPLD的时钟频率较低,适合较慢的应用。

- FPGA可以支持更高的时钟频率,适用于高速处理任务。

-

配置方式:

- CPLD配置速度较快,通常不需要外部配置存储。

- FPGA通常需要外部配置存储,配置速度较慢。

适用场合:

- CPLD:适用于简单的逻辑控制、时序电路、状态机等低密度任务。

- FPGA:适用于高速计算、数字信号处理(DSP)、视频处理、通信等需要大量并行计算的复杂应用。

3. hdlbits FPGA教程在线学习

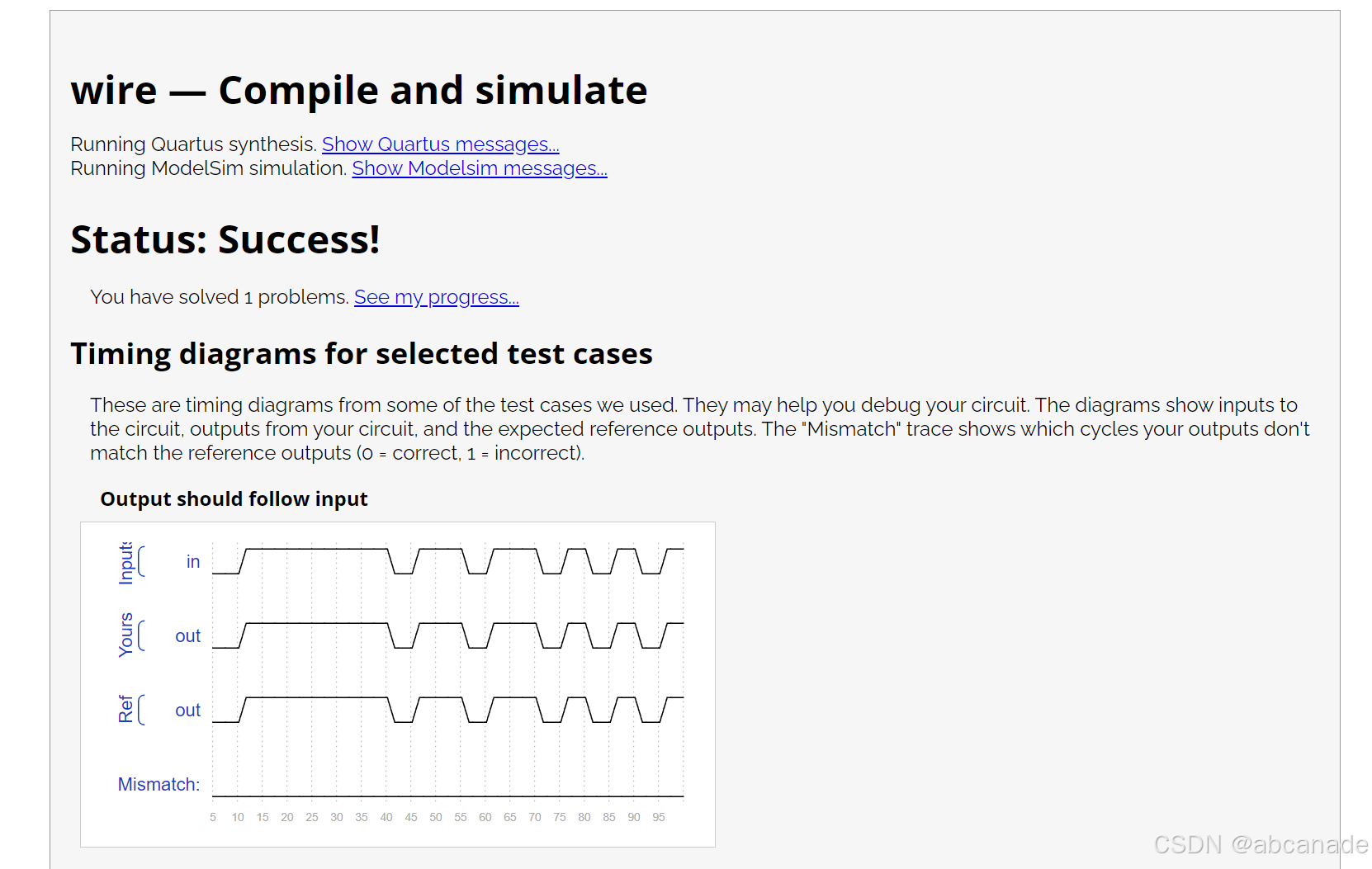

1.Wire

创建一个具有一个输入和一个输出的模块,其行为类似于电线。

与物理导线不同,Verilog 中的导线(和其他信号)是定向的。这意味着信息只在一个方向上流动,从(通常是一个)源到接收器(该源通常也称为将值驱动到导线上的驱动程序)。在Verilog"连续赋值"(assign left_side = right_side;)中,右侧信号的值被驱动到左侧的导线上。分配是"连续的",因为即使右侧的值发生变化,分配也会一直继续。连续分配不是一次性事件。assign left_side = right_side;

模块上的端口也有一个方向(通常是输入或输出)。输入端口由模块外部的东西驱动,而输出端口则驱动外部的东西。从模块内部查看时,输入端口是驱动器或源,而输出端口是接收器。

下图说明了电路的每个部分如何对应于Verilog代码的每个位。模块和端口声明创建电路的黑色部分。您的任务是通过添加要连接到 的语句来创建一条线路(绿色)。开箱即用的部件不是您关心的问题,但您应该知道,通过将测试线束的信号连接到顶部_模块的端口,可以测试您的电路。

module top_module( input in, output out );assign out = in;

endmodule

2 Four wires

创建一个具有 3 个输入和 4 个输出的模块,其行为类似于建立这些连接的电线:

a -> w

b -> x

b -> y

c -> z

下图说明了电路的每个部分如何对应于Verilog代码的每个位。从模块外部,有三个输入端口和四个输出端口。当您有多个赋值语句时,它们在代码中的显示顺序无关紧要。与编程语言不同,赋值语句(“连续赋值”)描述事物之间的连接,而不是将值从一个事物复制到另一个事物的操作。现在也许应该澄清的一个潜在的混淆来源是:这里的绿色箭头代表电线之间的连接,但本身不是电线。模块本身已经声明了 7 条导线(命名为 a、b、c、w、x、y 和 z)。这是因为,除非另有说明,否则声明实际上声明了一条线。写 input wire a 写 input a 是一样的.。因此,这些语句不是在创建导线,而是在已经存在的 7 根导线之间创建连接。

module top_module( input a,b,c,output w,x,y,z );assign w = a;assign x = b,y = b;assign z = c;

endmodule

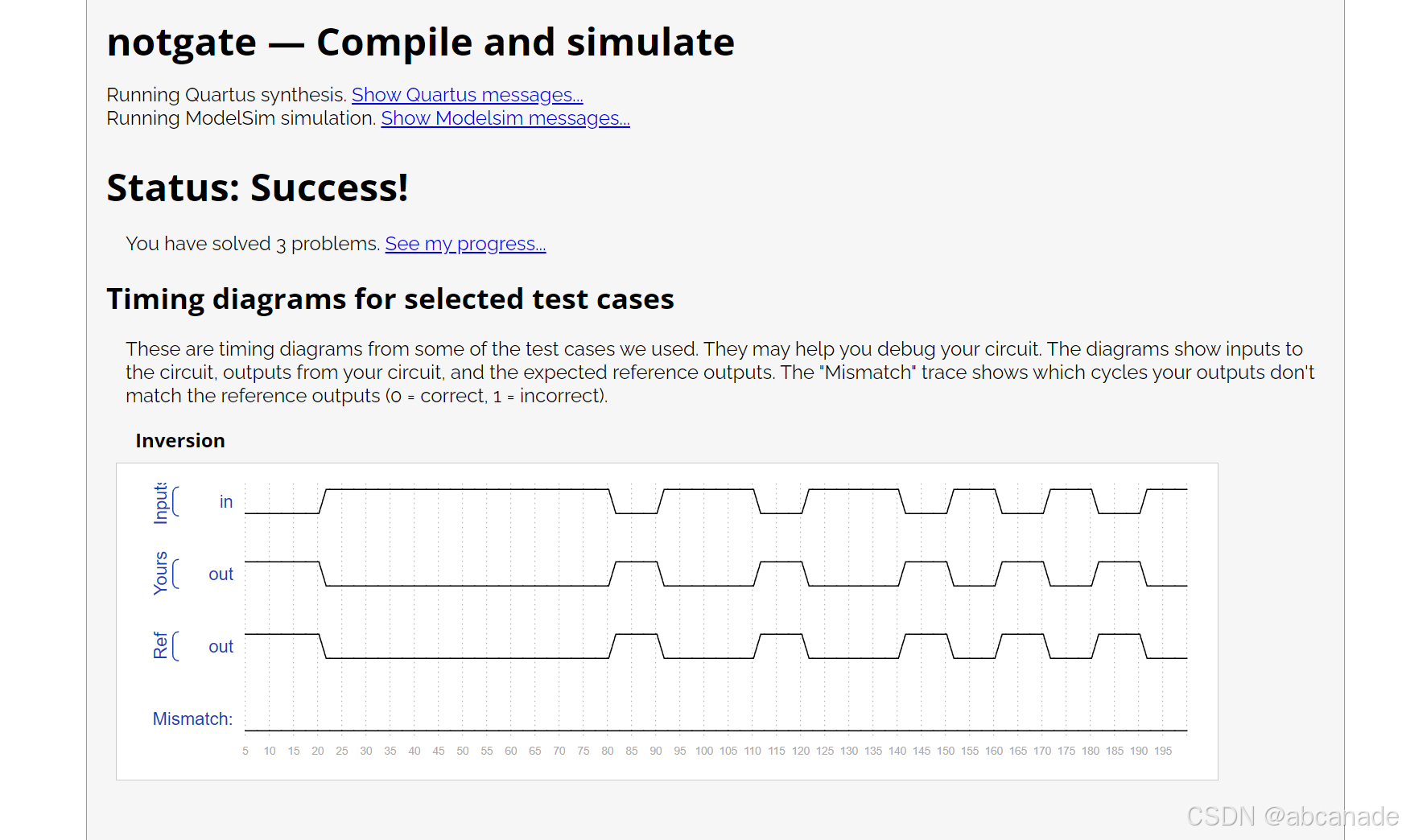

3 Inverter

创建一个实现 NOT 门的模块。该电路类似于线,但略有不同。当从电线连接到电线时,我们将实现逆变器(或"非门")而不是普通电线。使用assign语句。assign语句将持续将in的非转换为out。

module top_module( input in, output out );assign out = ~in;

endmodule

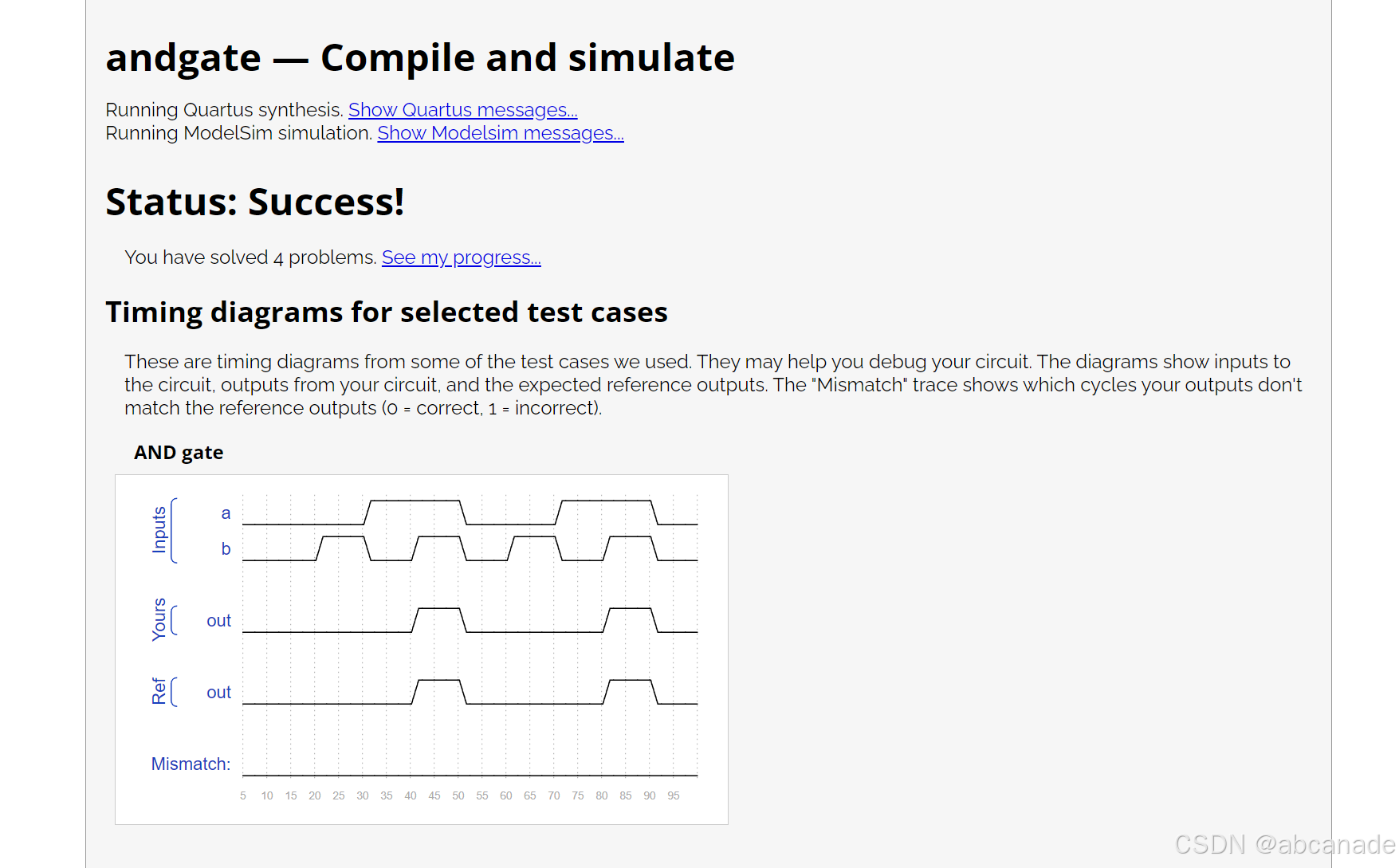

4 AND gate

创建实现 AND 门的模块。

该电路现在有三条导线(a、b和out)。导线a和b已经具有由输入端口驱动的值。但wire out目前并不是由任何因素驱动的。写一个assign语句,用a和b的AND信号输出。

请注意,该电路与NOT门非常相似,只是多了一个输入。如果听起来不一样,那是因为我已经开始描述信号是被驱动的(已知值由附加到它的某个东西决定)还是不是被某个东西驱动的。输入线由模块外部的东西驱动。assign语句将把一个逻辑电平驱动到一条线上。正如您所料,一条导线不能有多个驱动器(如果有,其逻辑级别是多少?),没有驱动程序的导线将有一个未定义的值(在合成硬件时通常被视为0)。

module top_module( input a, input b, output out );assign out = a & b;

endmodule

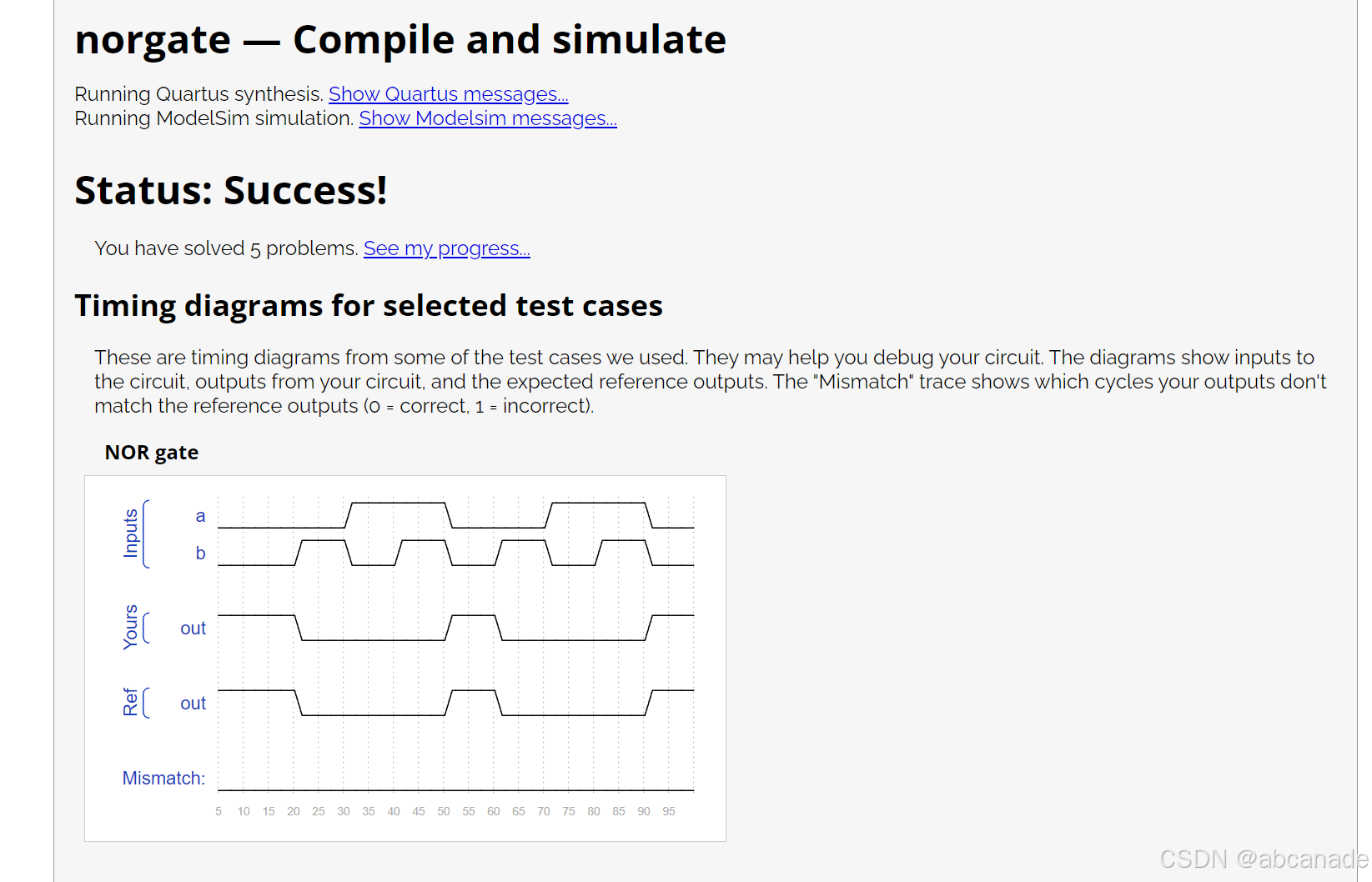

5 NOR gate

创建一个实现或非门的模块。或非门是输出反转的或门。在Verilog中编写NOR函数时需要两个运算符。

assign语句用一个值驱动一条线(或者更正式地称为“网”)。该值可以是任意复杂的函数,只要它是组合函数(即无内存、无隐藏状态)。assign语句是一种连续赋值,因为每当其任何输入发生变化时,都会“重新计算”输出,就像一个简单的逻辑门一样。

module top_module( input a, input b, output out );assign out = ~(a | b);

endmodule

相关文章:

状态机思想编程

1. LED流水灯的FPGA代码 在这个任务中,首先我们会使用状态机的思想来设计一个LED流水灯的控制逻辑。LED流水灯一般需要依次点亮不同的LED,并且循环播放。我们将其分为几个状态,每个状态控制一个或一组LED灯。 状态机设计 假设我们有8个LED…...

第二十八章:Python可视化图表扩展-和弦图、旭日图、六边形箱图、桑基图和主题流图

一、引言 在数据可视化领域,除了常见的折线图、柱状图和散点图,还有一些高级图表类型可以帮助我们更直观地展示复杂数据关系。本文将介绍五种扩展图表:和弦图、旭日图、六边形箱图、桑基图和主题流图。这些图表在展示数据关系、层次结构和流量…...

基于vue框架的重庆美食网站的设计与实现kt945(程序+源码+数据库+调试部署+开发环境)带论文文档1万字以上,文末可获取,系统界面在最后面。

系统程序文件列表 项目功能:用户,美食分类,美食菜品 开题报告内容 基于Vue框架的重庆美食网站的设计与实现开题报告 一、选题背景与意义 (一)选题背景 重庆,作为中国西南地区的璀璨明珠,以其独特的地理位置和丰富…...

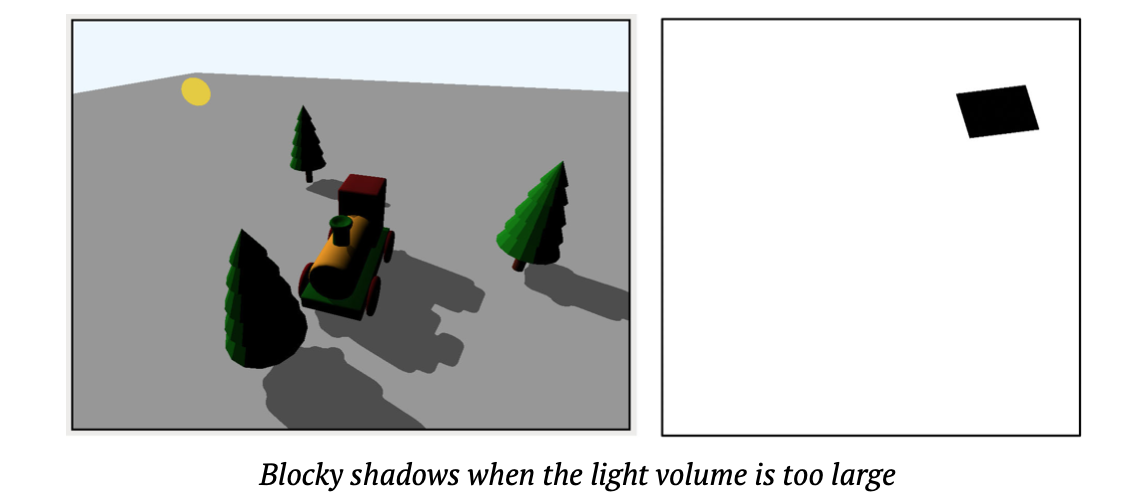

Metal学习笔记十三:阴影

在本章中,您将了解阴影。阴影表示表面上没有光。当另一个表面或对象使对象与光线相遮挡时,您会看到对象上的阴影。在项目中添加阴影可使您的场景看起来更逼真,并提供深度感。 阴影贴图 阴影贴图是包含场景阴影信息的纹理。当光线照射到物体…...

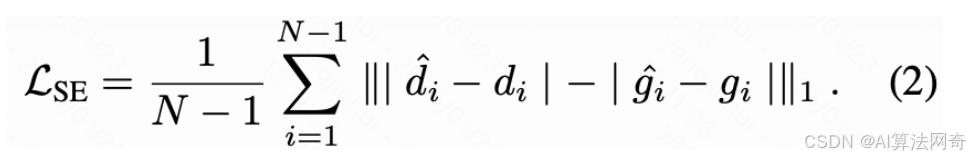

时间梯度匹配损失 TGMLoss

目录 时间梯度匹配损失(Temporal Gradient Matching Loss, TGM Loss) 完整示例,该损失函数常用于视频预测、运动平滑等任务,通过约束预测序列的时间梯度与真实序列一致来提升时序连续性 训练测试demo代码: 时间梯度匹配损失(Temporal Gradient Matching Loss, TGM Los…...

iPhone XR:一代神机,止步于此

什么样的 iPhone ,才配称为一代神机? 我曾经用过iPhone 4S、iPhone 6S Plus、iPhone 8 Plus,iPhone SE2、iPhone XR、iPhone 13、iPhone 14 Plus、iPhone 15/Pro。 不管硬件再怎么卷,不管囊中是否羞涩,主力机基本没考…...

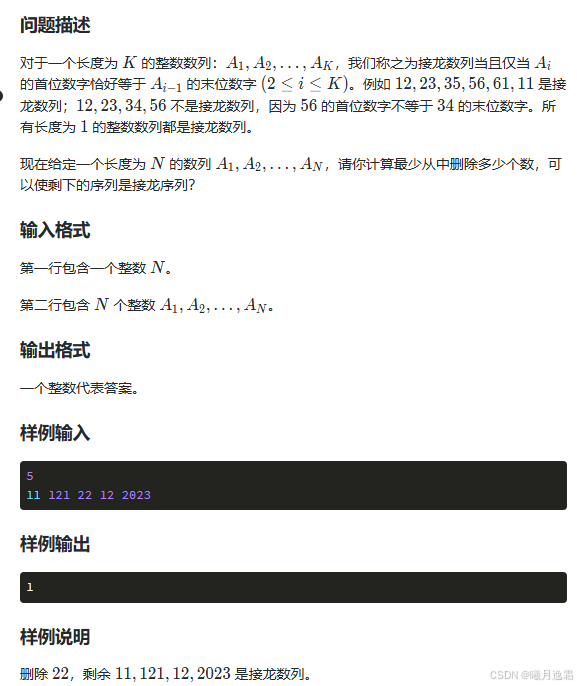

第十四届蓝桥杯省赛真题解析(含C++详细源码)

第十四届蓝桥杯省赛 整数删除满分思路及代码solution1 (40% 双指针暴力枚举)solution 2(优先队列模拟链表 AC) 冶炼金属满分代码及思路 子串简写满分思路及代码solution 1(60% 双指针)solution 2࿰…...

OpenAI即将开源!DeepSeek“逼宫”下,AI争夺战将走向何方?

OpenAI 终于要 Open 了。 北京时间 4 月 1 日凌晨,OpenAI 正式宣布:将在未来几个月内开源一款具备推理能力的语言模型,并开放训练权重参数。这是自 2019 年 GPT-2 部分开源以来,OpenAI 首次向公众开放核心模型技术。 【图片来源于…...

mysql 8.0.27-docker

安装 可以略过本步 https://dev.mysql.com/downloads/https://dev.mysql.com/downloads/ 镜像查询与安装 先查询: docker search mysql 明显会报错 Error response from daemon: Get "https://index.docker.io/v1/search?qmysql&n25": dial tcp…...

使用NVM下载Node.js管理多版本

提示:我解决这个bug跟别人思路可能不太一样,因为我是之前好用,换个项目就不好使了,倦了 文章目录 前言项目场景一项目场景二解决方案:下载 nvm安装 nvm重新下载所需Node 版本nvm常用命令 项目结构说明 前言 提示&…...

交易引擎中的设计模式

在WtHftEngine.cpp中,主要运用了以下几种设计模式,结合代码结构具体分析如下: 1. 观察者模式(Observer Pattern) 核心应用场景:实时市场数据的分发机制 代码体现: // 行情到达时分发给订阅…...

WebSocket创建流程)

(自用)WebSocket创建流程

在Spring Boot项目中新建WebSocket服务,可以按照以下详细步骤进行操作: 1.创建Spring Boot项目 可以通过Spring Initializr(<>)快速创建一个新的Spring Boot项目,添加Spring Web和Spring Boot DevTools依赖&…...

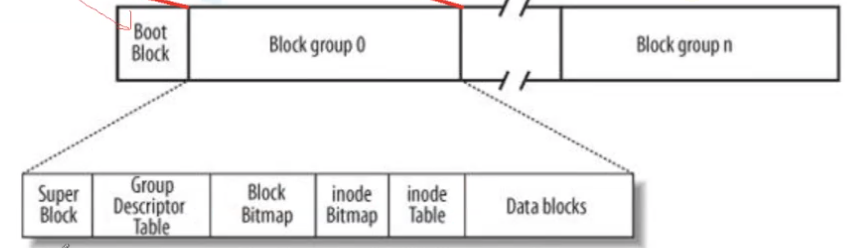

Linux——文件(2)文件系统

我们知道,文件在没有被打开时是放在磁盘中的,通常我们未打开的文件数量要远远大于打开的文件数量,而且我们要想打开一个文件,首先需要知道文件在磁盘的位置才能打开,但问题是,面对磁盘中成百上千个文件&…...

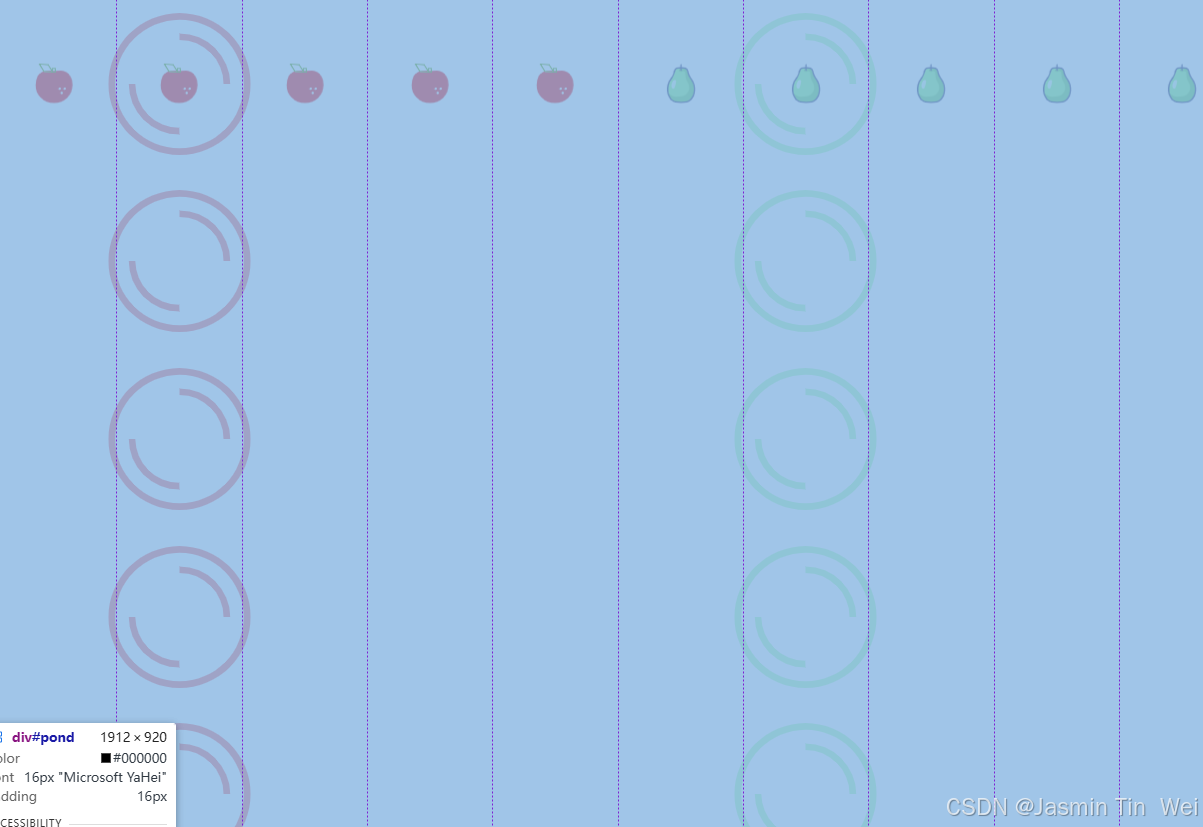

蓝桥杯 web 水果拼盘 (css3)

做题步骤: 看结构:html 、css 、f12 分析: f12 查看元素,你会发现水果的高度刚好和拼盘的高度一样,每一种水果的盘子刚好把页面填满了,所以咱们就只要让元素竖着排列,加上是竖着,排不下的换行…...

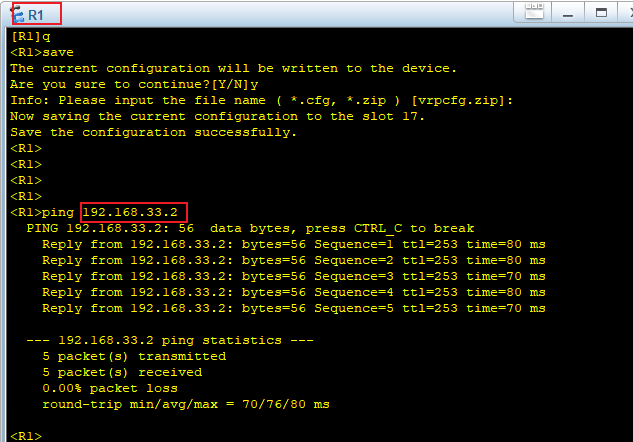

【eNSP实验】RIP协议

RIP协议介绍 RIP(路由信息协议)是一种基于距离向量的内部网关协议,适用于小型网络。它通过跳数(最多15跳)衡量路径成本,定期与相邻路由器交换路由表。RIPv1使用广播更新且不支持子网,RIPv2新增…...

)

SQL Server常见问题的分类解析(二)

SQL Server常见问题解析100例(31-60) 七、数据库设计与维护问题 表设计不合理导致性能瓶颈问题:大表缺少分区,字段类型过大(如VARCHAR(MAX))。解决方案:使用分区表(PARTITION BY RANGE),优化字段类型。 索引过多导致写入性能下降问题:过度索引导致INSERT/UPDATE变慢…...

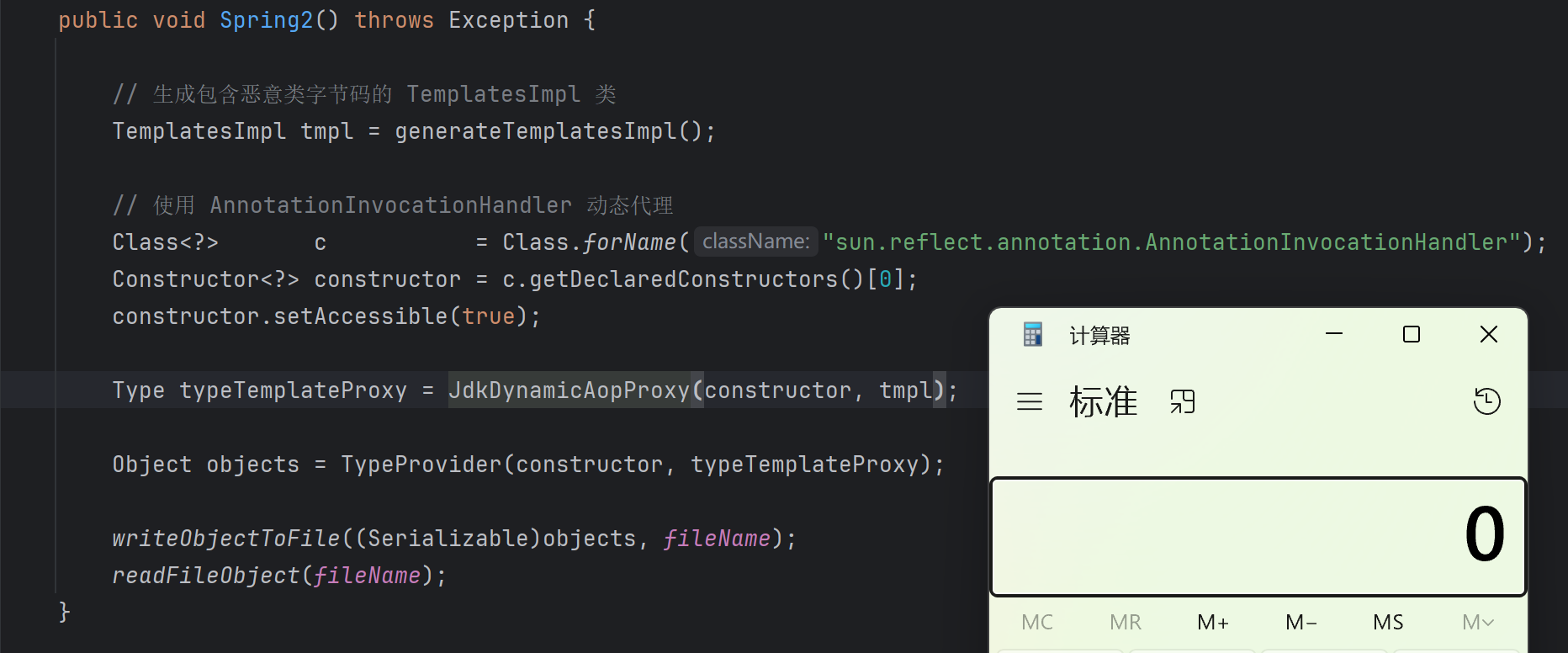

JAVA反序列化深入学习(十三):Spring2

让我们回到Spring Spring2 在 Spring1 的触发链上有所变换: 替换了 spring-beans 的 ObjectFactoryDelegatingInvocationHandler使用了 spring-aop 的 JdkDynamicAopProxy ,并完成了后续触发 TemplatesImpl 的流程 简而言之,换了一个chain&am…...

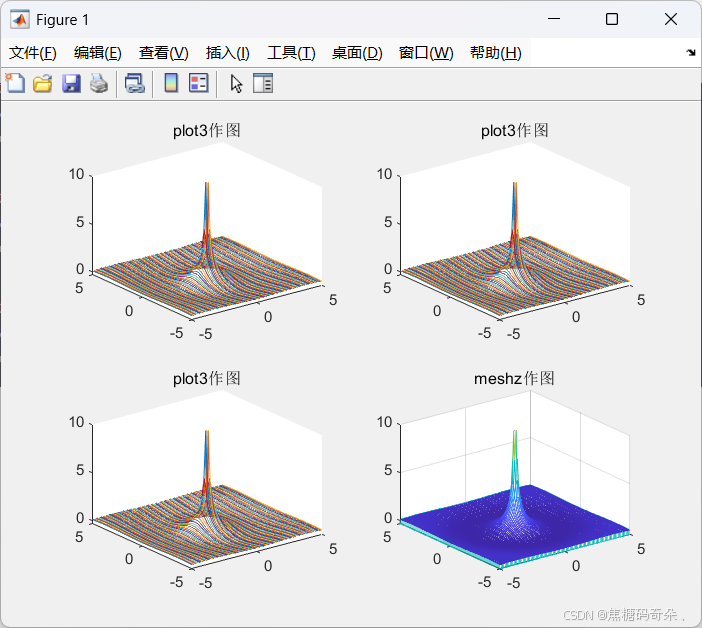

Matlab:三维绘图

目录 1.三维曲线绘图命令:plot3 实例——绘制空间直线 实例——绘制三角曲线 2.三维曲线绘图命令:explot3 3.三维网格命令:mesh 实例——绘制网格面 实例——绘制山峰曲面 实例——绘制函数曲线 1.三维曲线绘图命令:plot3 …...

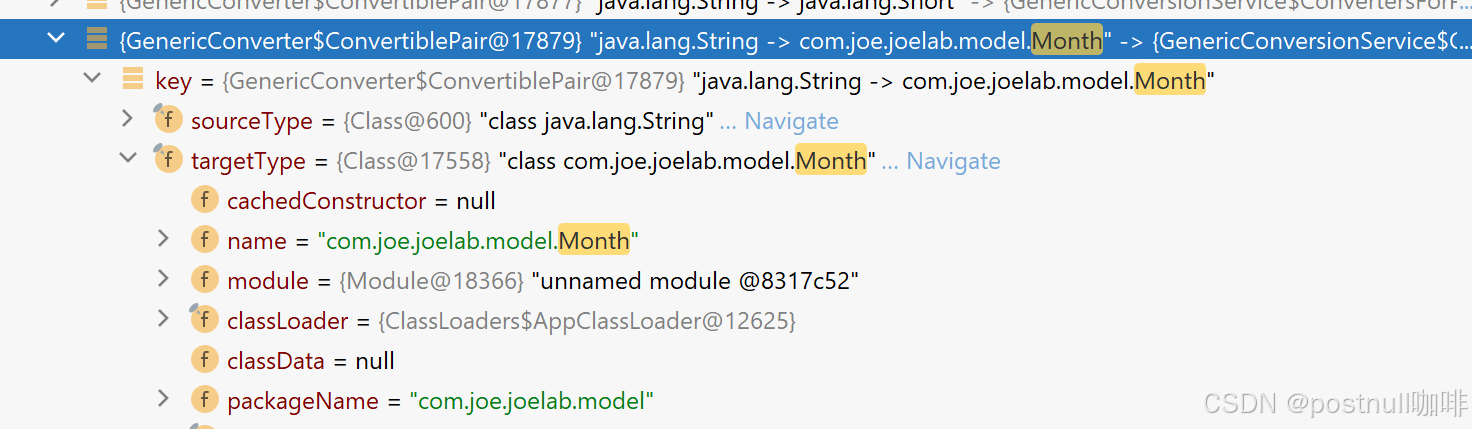

学透Spring Boot — 016. 魔术师 - Spring MVC Conversion Service 类型转换

本文是我的《学透Spring Boot》专栏的第16篇文章,了解更多请移步我的专栏: Postnull的专栏《学透Spring Boot》 目录 遇到问题 日期格式的转换 实现需求 创建转换器 注册转换器 编写Controller 访问测试 存在的问题 解决问题 源码分析 总结 …...

Spring Boot开发三板斧:高效构建企业级应用的核心技法

🧑 博主简介:CSDN博客专家、CSDN平台优质创作者,获得2024年博客之星荣誉证书,高级开发工程师,数学专业,拥有高级工程师证书;擅长C/C、C#等开发语言,熟悉Java常用开发技术,…...

)

人脸考勤管理一体化系统(人脸识别系统,签到打卡)

人脸考勤管理一体化系统 项目介绍 本项目是基于Flask、SQLAlchemy、face_recognition库的人脸考勤管理一体化系统。 系统通过人脸识别技术实现员工考勤打卡、人脸信息采集、人脸模型训练等功能。 项目采用前后端分离的技术框架,基于Flask轻量级Web框架搭建后端服务…...

Hive基础查询完全指南:从SELECT到复杂查询的10大核心技巧)

大数据(4.3)Hive基础查询完全指南:从SELECT到复杂查询的10大核心技巧

目录 背景一、Hive基础查询核心语法1. 基础查询(SELECT & FROM)2. 条件过滤(WHERE)3. 聚合与分组(GROUP BY & HAVING)4. 排序与限制(ORDER BY & LIMIT) 二、复杂查询实战…...

手搓多模态-03 顶层和嵌入层的搭建

声明:本代码非原创,是博主跟着国外大佬的视频教程编写的,本博客主要为记录学习成果所用。 我们首先开始编写视觉模型这一部分,这一部分的主要功能是接收一个batch的图像,并将其转化为上下文相关的嵌入向量,…...

【经验分享】将qt的ui文件转换为py文件

🌟 嗨,我是命运之光! 🌍 2024,每日百字,记录时光,感谢有你一路同行。 🚀 携手启航,探索未知,激发潜能,每一步都意义非凡。 首先简单的设计一个U…...

常用的国内镜像源

常见的 pip 镜像源 阿里云镜像:https://mirrors.aliyun.com/pypi/simple/ 清华大学镜像:https://pypi.tuna.tsinghua.edu.cn/simple 中国科学技术大学镜像:https://pypi.mirrors.ustc.edu.cn/simple/ 豆瓣镜像:https://pypi.doub…...

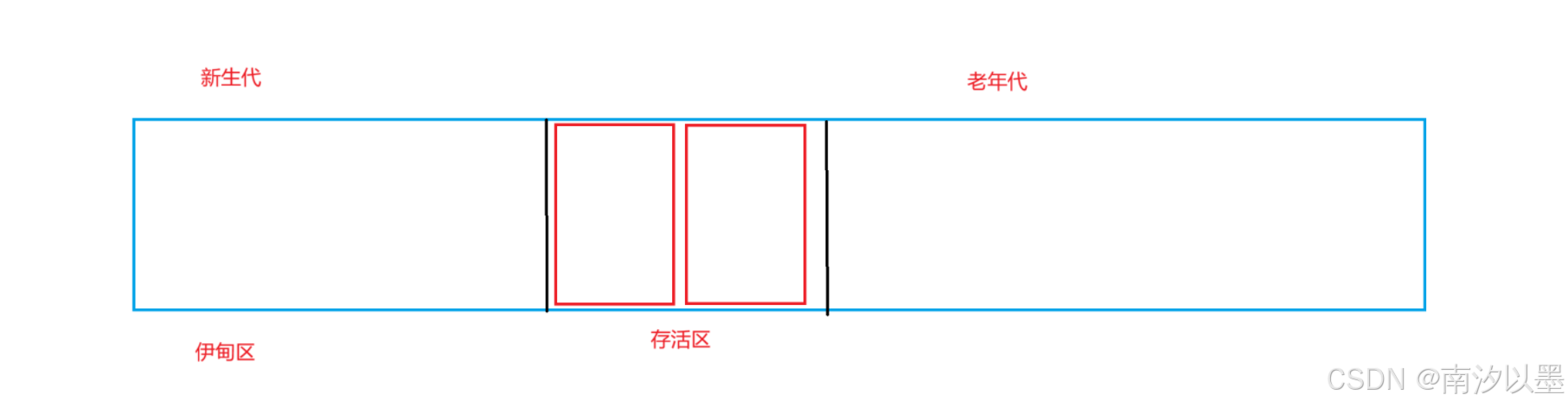

探秘JVM内部

在我们编写Java代码,点击运行后,会发生什么事呢? 首先,Java源代码会经过Java编译器将其编译成字节码,放在.class文件中 然后这些字节码文件就会被加载到jvm中,然后jvm会读取这些文件,调用相关…...

在HarmonyOS NEXT 开发中,如何指定一个号码,拉起系统拨号页面

大家好,我是 V 哥。 《鸿蒙 HarmonyOS 开发之路 卷1 ArkTS篇》已经出版上市了哈,有需要的朋友可以关注一下,卷2应用开发篇也马上要出版了,V 哥正在紧锣密鼓的写鸿蒙开发实战卷3的教材,卷3主要以项目实战为主࿰…...

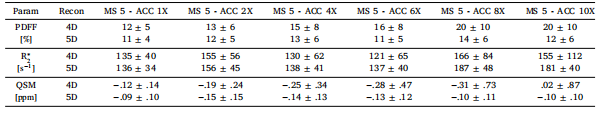

利用空间-运动-回波稀疏性进行5D图像重建,以实现自由呼吸状态下肝脏定量磁共振成像(MRI)的加速采集|文献速递--深度学习医疗AI最新文献

Title 题目 5D image reconstruction exploiting space-motion-echo sparsity foraccelerated free-breathing quantitative liver MRI 利用空间-运动-回波稀疏性进行5D图像重建,以实现自由呼吸状态下肝脏定量磁共振成像(MRI)的加速采集 …...

Qt5 Mac系统检查休眠

在开发跨平台应用程序时,有时候我们需要检测系统的状态,比如是否处于休眠或唤醒状态。Qt是一个强大的跨平台应用开发框架,支持多种操作系统,包括Windows、Linux、macOS等。在这个场景下,我们关注的是如何在Qt5.10中检测到系统是否休眠以及在Mac上实现这一功能。本文将深入…...

ZKmall开源商城B2B2C电商用户隐私信息保护策略:数据脱敏全链路实践

随着业务的不断拓展和用户规模的持续扩大,用户隐私信息的保护也面临着前所未有的挑战。下面将深入探讨ZKmall开源商城在数据脱敏方面的实践,以及针对B2B2C电商用户隐私信息的具体保护策略。 数据脱敏,又称数据去标识化或数据匿名化࿰…...