华为数字芯片机考2025合集3已校正

1. 题目内容

下列说法正确的是()。

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 异步 FIFO 采用格雷码是为了省功耗 | ✗ | 格雷码用于消除多比特信号跨时钟域的位跳变风险,与功耗无关 |

| B | 单比特信号打两拍可以完全避免亚稳态 | ✗ | 双触发器同步仅降低亚稳态概率,无法完全消除 |

| C | 异步处理需考虑发送和接收时钟的频率关系 | ✓ | 异步 FIFO 需评估写/读时钟速率差,防止溢出或空读 |

| D | 尽量将异步和同步逻辑剥离开,分别在不同模块实现 | ✓ | 同步/异步逻辑分离是设计规范,降低跨时钟域风险 |

1.2 详细解析

-

选项 A:

- 格雷码的核心作用:消除多比特信号跨时钟域的位跳变风险,而非省功耗。

- 异步 FIFO 的功耗优化:通过时钟门控(Clock Gating)或电源门控(Power Gating)实现。

-

选项 B:

- 亚稳态的不可消除性:双触发器同步仅降低亚稳态概率(MTBF 公式决定),无法完全消除。

- MTBF 公式:

MTBF = e^(t/τ) / (f × a),其中 t 为同步时间,τ 为触发器时间常数。

-

选项 C:

- 异步 FIFO 的时钟频率关系:需评估写/读时钟速率差,设计 FIFO 深度(

FIFO_depth >= (写速率 - 读速率) × 最大延迟)。 - 其他异步处理:如握手协议,也需考虑时钟频率关系。

- 异步 FIFO 的时钟频率关系:需评估写/读时钟速率差,设计 FIFO 深度(

-

选项 D:

- 同步/异步逻辑分离:

- 同步逻辑:基于时钟信号设计,时序可控。

- 异步逻辑:跨时钟域处理,需特殊同步机制(如 FIFO、握手协议)。

- 设计规范:分离同步/异步逻辑,降低跨时钟域风险,提高代码可读性和可维护性。

- 同步/异步逻辑分离:

2. 最终答案

正确答案:C

关键结论:

- C 选项正确:异步处理需考虑时钟频率关系(如异步 FIFO 的写/读时钟速率差)。

- D:同步/异步逻辑分离是设计规范,降低跨时钟域风险,但有时必须。

- A 选项错误:格雷码用于消除位跳变风险,与功耗无关。

- B 选项错误:双触发器同步无法完全消除亚稳态。

2. 从综合出电路的电路看第一段代码比第二段代码优化的地方是(C)

解析:

第一段代码:

- 仅在A&B为真时更新D,其他时候保持D不变

- 综合后会产生带使能端的寄存器

第二段代码:

- 在每个时钟周期都会更新D值

- 综合后会产生普通寄存器

优化点:

- 第一段代码电路更简单(C正确)

- 第一段代码确实更省功耗(B正确)

- 第一段代码也更简练(A正确)

但题目要求"从综合出电路的电路看",最直接的优化是电路简单性(C),其他选项更多是从代码层面或功能层面考虑。

3. 在SV中,上述代码执行完后,result的值为1’b0(B)

解析:

- a=2’b1z(二进制10或高阻态z)

- b=2’b10(明确二进制10)

- 在SystemVerilog中,当比较操作数包含z或x时:

- == 操作会返回x(未知)

- === 操作才会进行精确比较

- 因此result=(a==b)的结果是x,不是1’b0

- 所以选B(错误)

4. 以下不能抑制异步电路问题的是(D)

解析:

异步电路问题主要指亚稳态问题,抑制方法包括:

A. 寄存三拍 - 有效降低亚稳态概率

B. 双向握手 - 可靠的异步通信协议

C. 格雷码转换 - 用于多bit信号同步

D. 缓存输出 - 不能解决亚稳态问题,只是数据暂存

因此D选项不能有效抑制异步电路问题。

5、亚稳态对电路影响极大,下面哪种做法对降低亚稳态发生概率是无效的(C)

解析:

降低亚稳态概率的有效方法:

A. 增加打拍级数 - 有效(但边际效益递减)

B. 使用亚稳态硬化寄存器 - 有效

D. 缩短打拍逻辑间delay - 有效(减少亚稳态传播时间)

无效方法:

C. 提高工作时钟 - 反而会增加亚稳态概率(时钟越快,MTBF越低)

6、无复位寄存器会引入不定态,因此设计中禁止使用无复位寄存器(B)

解析:

- 无复位寄存器确实可能引入不定态

- 但在某些场景(如数据通路)可以使用,只要确保上电后会被正常写入

- 不是完全禁止,所以选B(错误)

7、bufif0 # (5:7:9, 8:10:12, 15:18:21)b1 (lo1.1o2, dir)。其中第一个5:7:9表示什么(A)

解析:

Verilog延迟值格式:

#(rise_delay, fall_delay, turn-off_delay)

第一个5:7:9表示:

min:typ:max 的上升延迟

8、在时钟上升沿时采样到start有效开始…(C)

解析:

关键点:

- a连续或间断出现3次高电平:使用"go to"重复操作符[->]

- 正确语法是:a[->3]

只有C选项正确使用了[->3]:

property p0:

@(posedge clk) $rose(start) |-> ##2 (a[->3]) ##1 stop;

endproperty

9、对于FPGA内部的RAM而言,以下哪个说法是错误的(A)

解析:

伪双端口RAM特性:

- 一个端口只读,一个端口只写(不是两个端口都可读写)

- 可以有独立时钟(B正确)

- 单端口RAM特性(C、D正确)

因此A选项描述错误(说两个端口都有独立读写控制)

10. 题目内容

关于静态时序分析(STA),哪项说法是错误的?()

1. 解题步骤

1.1 STA 的核心特性

| 特性 | 说明 |

|---|---|

| 不依赖仿真向量 | 基于时序约束分析,无需测试激励(A 正确) |

| 不验证功能 | 仅检查时序,不验证逻辑功能(B 正确) |

| 分析速度快 | 相比动态仿真更快(C 正确) |

| 适用范围 | 仅适用于同步路径,异步路径需特殊处理(D 错误) |

1.2 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 不需要仿真向量 | ✓ | STA 基于约束分析,无需仿真激励 |

| B | 不能验证设计的功能 | ✓ | STA 仅检查时序,不验证功能 |

| C | 分析速度快 | ✓ | 相比动态仿真,STA 速度更快 |

| D | 可以分析同步路径和异步路径 | ✗ | STA 仅分析同步路径,异步路径需标记为 false_path |

2. 最终答案

正确答案:D

关键结论:

- STA 只能分析同步路径,异步路径需通过

set_false_path或set_clock_groups标记。 - 其他选项(A、B、C)均正确描述了 STA 的特性。

总结

| 选项 | 正误 | 核心考点 |

|---|---|---|

| D | ✗ | STA 仅适用于同步路径分析 |

11. 题目内容

验证环境中提到的参考模型(Reference Model)只支持不带时序的功能建模,不支持时序建模()。

1. 解题步骤

1.1 参考模型(Reference Model)的作用

- 功能建模:

- 模拟 DUT(Design Under Test)的预期行为,生成预期输出。

- 支持时序建模:参考模型可以包含时序行为(如延迟、流水线等),但通常以功能正确性为主,时序细节可能简化。

1.2 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 错误 | ✓ | 参考模型可以包含时序行为(如协议延迟、流水线阶段) |

| B | 正确 | ✗ | 参考模型不仅限于纯组合逻辑,可支持时序建模 |

2. 最终答案

正确答案:A(错误)

关键结论:

- 参考模型 可以 支持时序建模(如模拟协议延迟、流水线行为),但通常以功能正确性为核心目标。

- 题目说法过于绝对,因此 A(错误) 是正确答案。

补充说明

- 何时使用时序建模:

- 在验证高速接口(如 PCIe、DDR)时,参考模型可能需要模拟协议规定的时序行为。

- 简化时序的场景:

- 若只验证功能正确性,时序细节可交由断言或时序检查工具处理。

12. 题目内容

如果该 class 会被继承,则该 class 所有定义的 function/task 都需要加 virtual()。

1. 解题步骤

1.1 virtual 关键字的作用

virtual方法:- 允许子类重写(override)父类的方法。

- 未加

virtual的方法在子类中无法重写。

1.2 是否需要全部加 virtual

- 必要性:

- 只有需要被重写的方法才需加

virtual。 - 不需要重写的方法无需加

virtual。

- 只有需要被重写的方法才需加

- 反例:

- 工具类(Utility Class)中的方法通常无需重写,不应加

virtual。

- 工具类(Utility Class)中的方法通常无需重写,不应加

1.3 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 错误 | ✓ | 只有需要重写的方法才需加 virtual,非全部 |

| B | 正确 | ✗ | 仅需为可能被重写的方法加 virtual |

2. 最终答案

正确答案:A(错误)

关键结论:

- 只有需要被重写的方法才需加

virtual,并非所有方法都需要。 - 题目说法过于绝对,因此 A(错误) 是正确答案。

补充说明

- 何时使用

virtual:- 父类方法可能被重写时(如基类中的通用行为)。

- 何时无需

virtual:- 工具类方法(如数学计算、字符串处理)。

- 不希望子类重写的方法(如关键功能)。

13. 题目内容

下列选项表达式逻辑实现功能,与图中电路实现功能不同的是()。

1. 解题步骤

1.1 电路功能分析

假设图中电路功能为:A·S + B·S'(A 与 S 相或,B 与 S 非相或,再相与)。

1.2 选项分析

| 选项 | 表达式 | 是否与电路功能相同 | 依据 |

|---|---|---|---|

| A | (A+S’)(B+S) | ✗ | 展开后包含额外项(A·B) |

| B | A·B + A·S + B·S’ + S·S’ | ✗ | 包含冗余项(A·B 和 S·S’) |

| C | A·S + B·S’ | ✓ | 与电路功能一致 |

| D | A(B+S’) + S(B+S) | ✗ | 展开后包含额外项(A·B 和 S·B) |

2. 最终答案

正确答案:A、B、D

14. 题目内容

关于下面约束,说法正确的是()。

constraint ST { (a == 0) -> (b == 0) }

1. 解题步骤

1.1 约束逻辑分析

- 含义:如果

a == 0,则b == 0。 - 逆否命题:如果

b != 0,则a != 0。

1.2 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 如果 a != 0,则 b != 0 | ✗ | 原命题无法推出此结论 |

| B | 如果 b != 0,则 a != 0 | ✓ | 逆否命题成立 |

| C | 如果 b == 0,则 a == 0 | ✗ | 原命题无法推出此结论 |

2. 最终答案

正确答案:B

15. 题目内容

有关中断,以下说法不正确的是?()

1. 解题步骤

1.1 中断特性分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 芯片中断引脚送出的中断信号一般采用脉冲信号 | ✗ | 中断信号可以是电平或脉冲 |

| B | 中断读清方式是指在 CPU 完成对中断指示寄存器的读操作后将中断指示寄存器清零 | ✓ | 正确描述读清机制 |

| C | 中断存在边缘触发方式和电平触发方式 | ✓ | 两种触发方式均存在 |

| D | 1 根中断管脚可以复用多个芯片内部中断 | ✓ | 中断复用是常见设计 |

2. 最终答案

正确答案:A

16. 题目内容

以下低功耗措施中,哪种不是降低电路翻转率的方法?()

1. 解题步骤

1.1 降低翻转率的措施

| 选项 | 描述 | 是否降低翻转率 | 依据 |

|---|---|---|---|

| A | 重新安排“if-else”表达式,将毛刺或快变化信号移至逻辑锥体前部 | ✗ | 优化逻辑顺序,减少毛刺 |

| B | 采用 Gray 码或 One-hot 码作为状态机编码 | ✓ | 减少状态跳变时的翻转位数 |

| C | 在不进行算术运算时,使模块输入保持不变,不让新操作数进入 | ✓ | 减少无效操作 |

| D | 减少电路中的 glitch | ✓ | 减少毛刺导致的额外翻转 |

2. 最终答案

正确答案:A

总结

| 题号 | 正确答案 | 核心考点 |

|---|---|---|

| 13 | A、B、D | 逻辑表达式与电路功能对比 |

| 14 | B | SystemVerilog 约束逻辑 |

| 15 | A | 中断信号特性 |

| 16 | A | 低功耗设计方法 |

17. 题目内容

以下 SV 程序的运行结果为()。

class Test; bit [31:0] addr; function void display_addr; $display("%h", addr); endfunction

endclass:Test initial begin Test t1; t1 = new(); t1.display_addr();

end

1. 解题步骤

1.1 代码分析

- 类定义:

Test类包含一个 32-bit 变量addr和一个显示addr值的方法display_addr。

- 初始化块:

- 创建

Test类的实例t1。 - 调用

t1.display_addr()显示addr的值。

- 创建

1.2 变量默认值

bit类型默认值:0。- 因此,

addr的默认值为32'h00000000。

1.3 输出结果

$display("%h", addr)会输出addr的十六进制值,即00000000。

2. 最终答案

正确答案:D(0)

18. 题目内容

以下信号命名中不符合 Verilog 语法的是()。

1. 解题步骤

1.1 Verilog 命名规则

- 合法字符:字母(A-Z, a-z)、数字(0-9)、下划线(_)、美元符号($)。

- 首字符:不能是数字或美元符号。

1.2 选项分析

| 选项 | 信号名 | 是否符合语法 | 依据 |

|---|---|---|---|

| A | 1_2CorrectName | ✗ | 首字符为数字,非法 |

| B | CNTO | ✓ | 符合命名规则 |

| C | _R1_D2 | ✓ | 符合命名规则 |

| D | COunT | ✓ | 符合命名规则 |

2. 最终答案

正确答案:A(1_2CorrectName)

19. 题目内容

关于三段式状态机的描述,下列说法正确的是()。

1. 解题步骤

1.1 三段式状态机特点

- 状态转移逻辑:

- 描述状态转移条件和规律,通常为 组合逻辑(B 错误)。

- 状态寄存器:

- 用于存储当前状态,为 时序逻辑(D 正确)。

- 输出逻辑:

- 可以是组合逻辑或时序逻辑(A 错误)。

- default 态:

- 必须指定,避免状态机进入非法状态(C 错误)。

1.2 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 输出必须是寄存器输出 | ✗ | 输出可以是组合逻辑 |

| B | 描述状态转移条件和规律的逻辑是时序逻辑 | ✗ | 状态转移逻辑为组合逻辑 |

| C | 描述状态转移时,可以不指定 default 态 | ✗ | 必须指定 default 态 |

| D | 描述状态迁移的逻辑为时序逻辑 | ✓ | 状态寄存器为时序逻辑 |

2. 最终答案

正确答案:D

20. 题目内容

有关功耗,以下说法不正确的是?()

1. 解题步骤

1.1 功耗分析

- 设计层次与优化效果:

- 设计层次越高,优化效果越好(A 正确)。

- 动态功耗公式:

P_dynamic ∝ C × V^2 × f,电压和频率越高,动态功耗越大(B 正确)。

- 低功耗设计目标:

- 在性能、面积、功耗之间找到平衡(C 正确)。

- 工艺发展与功耗:

- 先进工艺下,静态功耗(漏电流)增加,动态功耗降低(D 错误)。

1.2 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 设计层次越高,功耗优化效果越好 | ✓ | 高层优化更有效 |

| B | 电压越大,频率越高,动态功耗越高 | ✓ | 动态功耗公式 |

| C | 低功耗设计目标是找到最佳平衡 | ✓ | 设计目标权衡 |

| D | 单位面积动态和静态功耗随工艺发展呈下降趋势 | ✗ | 静态功耗随工艺发展增加 |

2. 最终答案

正确答案:D

21. 题目内容

generate for 循环语句中使用的标尺变量可定义为 integer()。

1. 解题步骤

1.1 generate for 循环变量类型

- 标尺变量:必须定义为

genvar类型,不能是integer。

1.2 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 正确 | ✗ | 标尺变量必须为 genvar |

| B | 错误 | ✓ | integer 不可用于 generate for 循环 |

2. 最终答案

正确答案:B

22. 题目内容

Interface 中可以定义信号、函数、任务、class 对象;也可以有 always,initial 语句块()。

1. 解题步骤

1.1 Interface 的功能

- 支持定义:信号、函数、任务。

- 不支持定义:class 对象、always/initial 语句块。

1.2 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 错误 | ✓ | Interface 不支持 class 对象和 always/initial 语句块 |

| B | 正确 | ✗ | 描述不完全正确 |

2. 最终答案

正确答案:A

23. 题目内容

下列不属于动态数组内建函数的是()。

1. 解题步骤

1.1 动态数组内建函数

size():返回数组大小。delete():删除数组内容。new[]:动态分配数组空间。length():不存在,正确函数为size()。

1.2 选项分析

| 选项 | 函数 | 是否属于动态数组内建函数 | 依据 |

|---|---|---|---|

| A | delete() | ✓ | 动态数组内建函数 |

| B | size() | ✓ | 动态数组内建函数 |

| C | new[] | ✓ | 动态数组内建函数 |

| D | length() | ✗ | 不存在,应为 size() |

2. 最终答案

正确答案:D

24. 题目内容

isolation cell 是下面哪种低功耗技术必需的()。

1. 解题步骤

1.1 低功耗技术与 isolation cell

- Power Gating:

- 需要 isolation cell 隔离掉电模块的输出。

- Clock Gating:无需 isolation cell。

- Multi_Vdd:无需 isolation cell。

- AVS:无需 isolation cell。

1.2 选项分析

| 选项 | 技术 | 是否需要 isolation cell | 依据 |

|---|---|---|---|

| A | Power Gating | ✓ | 必需 |

| B | Clock Gating | ✗ | 无需 |

| C | Multi_Vdd | ✗ | 无需 |

| D | AVS | ✗ | 无需 |

2. 最终答案

正确答案:A

25. 题目内容

a1 和 a2 的检查效果完全一样:()

property p1: @(posedge clk) a |=> b |=> c;

endproperty

a1: assert property(p1); property p2: @(posedge clk) a ##1 b ##1 |-> c;

endproperty

a2: assert property(p2);

1. 解题步骤

1.1 属性分析

- p1:

a |=> b |=> c等价于a ##1 b ##1 c。

- p2:

a ##1 b ##1 |-> c等价于a ##1 b ##1 c。

1.2 检查效果

- p1 和 p2 的逻辑完全一致,检查效果相同。

2. 最终答案

正确答案:B(正确)

26. 题目内容

漏电流(Leakage Current)与逻辑电路设计的工作频率无关()。

1. 解题步骤

1.1 漏电流特性

- 漏电流:主要由晶体管漏电引起,与工作频率无关。

- 动态功耗:与工作频率相关。

2. 最终答案

正确答案:B(正确)

27. 题目内容

reg signed [0:4] c; c = 8’h8f; 赋值后 c 的值是多少?()

1. 解题步骤

1.1 位宽与符号扩展

- c 的位宽:5-bit 有符号数。

- 8’h8f:二进制

10001111,截取低 5-bit 为01111。 - 有符号数解析:

01111为+15。

2. 最终答案

正确答案:A(15)

28. 题目内容

在 Verilog 中,"assign din[31:0] = 32’hFF00_ABC4;assign dout[31:0] = (din << 2) >> 4。dout 的值是多少?()

1. 解题步骤

1.1 计算过程

- din << 2:

32'hFF00_ABC4左移 2 位,结果为32'hFC02_AF10。

- >> 4:

- 右移 4 位,结果为

32'h0FC02_AF1。

- 右移 4 位,结果为

2. 最终答案

正确答案:D(32’h0FC02AF1)

29. 题目内容

假设输入信号 X 位宽为 12bit,InA 位宽为 6bit,InB 位宽为 17bit,实现 Y = X * InA + InB 功能,并要求不损失精度,那么输出信号 Y 位宽应不小于()。

1. 解题步骤

1.1 位宽计算

- X * InA:

- 12-bit × 6-bit = 18-bit。

- + InB:

- 18-bit + 17-bit = 19-bit。

2. 最终答案

正确答案:C(19bit)

30. 题目内容

在 Verilog 设计中,下列说法不正确的是()。

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 如果 setup 时间不满足,可以尝试降低时钟频率解决 | 错误 | 降低时钟频率可以缓解 setup 时间问题,但题目问的是“不正确”的说法,因此 A 是正确的解决方法,但题目要求选不正确选项 |

| B | 在边沿敏感时序逻辑代码中,应使用非阻塞赋值 (<=) | 正确 | Verilog 规范要求时序逻辑使用非阻塞赋值 |

| C | 要求 always 块产生组合逻辑时使用阻塞赋值 (=) | 正确 | 组合逻辑推荐使用阻塞赋值 |

| D | 模运算符 “%” 是不可综合的 | 错误 | 模运算符在某些综合工具中是可综合的(但可能效率低),因此说法不完全正确 |

2. 最终答案

正确答案:A, D

31. 题目内容

对于设计中所使用的 Pipeline,说法中正确的有()。

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 使用 Pipeline 会导致数据延时增加,但如果工作频率不变,系统的吞吐量不会改变 | 错误 | Pipeline 会增加延迟,但通常能提高吞吐量(单位时间处理更多数据) |

| B | 使用 Pipeline 会对时序有好处,STA 更容易通过 | 正确 | 流水线分割关键路径,改善时序 |

| C | 使用 Pipeline 一定可以减少面积 | 错误 | Pipeline 可能增加寄存器数量,导致面积增大 |

| D | 使用 Pipeline 可能会导致面积增大 | 正确 | 流水线通常需要额外寄存器,可能增加面积 |

2. 最终答案

正确答案:B, D

32. 题目内容

下列哪些设计可能会对芯片 DFT(可测试性设计)产生不利影响?()

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 门控时钟设计 | 影响 | 门控时钟可能导致测试时钟控制困难 |

| B | 使用双沿时钟设计 | 影响 | 双沿时钟增加测试复杂度 |

| C | 内部三态门总线 | 影响 | 三态总线在测试时可能冲突 |

| D | 使用内部产生的时钟 | 影响 | 内部时钟难以同步测试时钟 |

2. 最终答案

正确答案:A, B, C, D

33. 题目内容

下列表达式中,哪些可以使用一个或多个二输入与非门器件实现?()

1. 解题步骤

1.1 选项分析

(注:二输入与非门是通用逻辑门,可组合实现任意逻辑)

| 选项 | 描述 | 可实现性 | 实现方式 |

|---|---|---|---|

| A | 常数 1 | 可以 | 与非门输入接相同信号(如 A NAND A) |

| B | A | 可以 | A NAND 1(或双重否定) |

| C | A+B(或逻辑) | 可以 | 德摩根定律转换 |

| D | AB(与逻辑) | 可以 | 与非门后接非门(或双重与非) |

2. 最终答案

正确答案:A, B, C, D

34. 题目内容

多比特信号 A 在时钟域 clk_a 存在从 8’d100 到 8’d101 的变化过程中,若在时钟域 clk_b 直接采用 D 触发器采样,可能采样到数据是()。

1. 解题步骤

1.1 选项分析

由于 clk_a 和 clk_b 是异步时钟域,直接采样多比特信号可能发生 亚稳态(Metastability) 和 数据不一致(Data Inconsistency),导致采样到的数据可能是:

- 8’d100(原数据)

- 8’d101(新数据)

- 中间值(由于比特间偏移导致的错误值)

但题目给出的选项均为 8’d100 或 8’d101 的不同表示形式(二进制、十六进制、十进制),没有错误的中间值选项。因此,可能采样到的数据是:

- A. 8’h65(十六进制 0x65 = 十进制 101)

- B. 8’b01100101(二进制 01100101 = 十进制 101)

- C. 8’h64(十六进制 0x64 = 十进制 100)

- D. 8’d100(十进制 100)

由于题目未提供中间错误值的选项,因此 所有选项均可能被采样到(正确的原数据或新数据的不同表示)。

2. 最终答案

正确答案:A, B, C, D(所有选项均可能被采样到)

注意:在实际跨时钟域采样时,可能会采样到错误值(如部分比特变化导致的中间值),但本题选项均为正确数据的表示方式,因此全选。

35. 题目内容

Formality 支持的等价性验证包括()。

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 支持性 |

|---|---|---|

| A | 门级网表对门级网表 | 支持 |

| B | RTL 级对 RTL 级 | 支持 |

| C | RTL 级对门级网表 | 支持 |

2. 最终答案

正确答案:A, B, C

36. 题目内容

以下三段代码,说法正确的是:()

1. 解题步骤

1.1 代码分析

- 代码①:异步复位逻辑(

rst_n在敏感列表中,且为下降沿触发)。 - 代码②:无复位逻辑,仅有时钟触发的寄存器。

- 代码③:同步复位逻辑(

rst_n仅在时钟上升沿时生效)。

1.2 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | ②属于无复位寄存器,其 PPA(Power, Performance, Area)更优 | 正确 | 无复位逻辑节省面积和功耗 |

| B | ①属于异步复位逻辑 | 正确 | rst_n 在敏感列表中,且为下降沿触发 |

| C | 同步复位和异步复位都是在复位时将寄存器状态初始化,所以没有区别 | 错误 | 同步复位和异步复位在实现和时序上有显著区别 |

| D | ③属于同步复位逻辑,rst_n 可能通过组合逻辑连接到寄存器 D 端 | 正确 | 同步复位逻辑中,rst_n 仅在时钟上升沿生效 |

2. 最终答案

正确答案:A, B, D

37. 题目内容

基于 FPGA 和 ASIC 芯片设计的差异需要关注的有()。

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 时钟复位 | 正确 | FPGA 和 ASIC 在时钟复位设计上有差异 |

| B | 时钟频率 | 正确 | FPGA 时钟频率通常低于 ASIC |

| C | memory 控制 | 正确 | FPGA 和 ASIC 的 memory 架构和控制方式不同 |

| D | 上下电流程 | 正确 | FPGA 和 ASIC 的上下电流程设计不同 |

2. 最终答案

正确答案:A, B, C, D

38. 题目内容

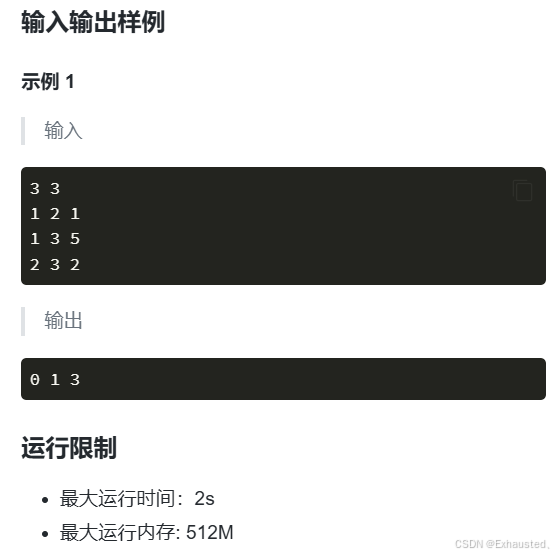

报文处理设计规格:()

- 支持的报文长度为 36‐256 字节,其余长度的报文直接丢弃;

- 接收的报文长度小于 64 字节时填充 PAD(任意数据)使报文长度达到 64 字节,然后再转发;

下面描述错误的是:()

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 因为填充 PAD 是任意数据,因此随便挑一组特殊值,例如全 0 验证即能够保证功能正确 | 错误 | 填充数据应覆盖多种情况,不能仅用单一值验证 |

| B | 因为大于 256B 的报文被丢弃了,所以不需要验证该点 | 错误 | 需要验证丢弃功能是否正确 |

| C | 因为小于 36B 的报文被丢弃了,所以不需要验证该点 | 错误 | 需要验证丢弃功能是否正确 |

| D | 该报文处理长度的边界点包含两个值,分别为 36 和 256 | 正确 | 边界点为 36 和 256 |

2. 最终答案

正确答案:A, B, C

39. 题目内容

下列哪些必须是在 Post‐Layout 时序仿真中使用的?()

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | Post‐Layout 网表 | 正确 | Post‐Layout 仿真需要布局布线后的网表 |

| B | 综合网表 | 错误 | 综合网表用于综合后仿真,而非 Post‐Layout 仿真 |

| C | 标准延时格式文件(SDF) | 正确 | SDF 文件包含布局布线后的延时信息 |

| D | RTL 代码 | 错误 | RTL 代码用于功能仿真,而非 Post‐Layout 仿真 |

2. 最终答案

正确答案:A, C

40. 题目内容

当模块的代码覆盖率达到 100% 时,下列说法错误的是()。

1. 解题步骤

1.1 选项分析

| 选项 | 描述 | 正误 | 依据 |

|---|---|---|---|

| A | 并不能确保验证工作已经完成 | 正确 | 代码覆盖率 100% 不意味着功能验证充分 |

| B | 可确认各类用例的激励构造已经完备 | 错误 | 代码覆盖率不能完全反映激励构造的完备性 |

| C | 可确认各种边界点的测试已经足够充分 | 错误 | 代码覆盖率不能完全反映边界点测试的充分性 |

| D | 可确认功能验证充分 | 错误 | 代码覆盖率不能完全反映功能验证的充分性 |

2. 最终答案

正确答案:B, C, D

相关文章:

华为数字芯片机考2025合集3已校正

1. 题目内容 下列说法正确的是()。 1. 解题步骤 1.1 选项分析 选项描述正误依据A异步 FIFO 采用格雷码是为了省功耗✗格雷码用于消除多比特信号跨时钟域的位跳变风险,与功耗无关B单比特信号打两拍可以完全避免亚稳态✗双触发器同步仅降低…...

控制 ElementUI el-table 树形表格多选框的显示层级

1、你可以通过 selectable 属性来控制哪些行可以选择(显示多选框) <el-table:data"tableData"row-key"id"default-expand-all:tree-props"{children: children, hasChildren: hasChildren}"select"handleSelect&…...

go语言应该如何学习

以下是学习Go语言的高效路径及关键技巧,结合多个优质来源整理而成,适合不同基础的学习者: 一、基础语法快速入门(1-2周) 1、环境搭建 下载安装Go SDK,配置GOPATH和GOROOT环境变量,推荐使用Go…...

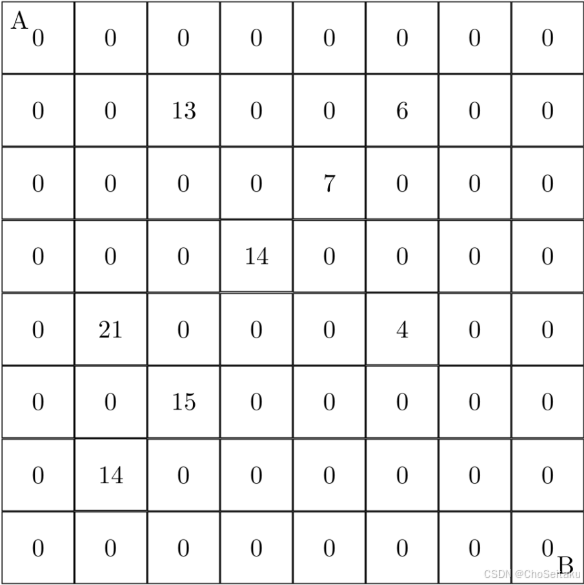

NO.84十六届蓝桥杯备战|动态规划-路径类DP|矩阵的最小路径和|迷雾森林|过河卒|方格取数(C++)

路径类dp是线性dp的⼀种,它是在⼀个nm的矩阵中设置⼀个⾏⾛规则,研究从起点⾛到终点的⽅案数、最⼩路径和或者最⼤路径和等等的问题 矩阵的最小路径和_牛客题霸_牛客网 状态表⽰: dp[i][j]表⽰:到达[i, j]位置处,最⼩…...

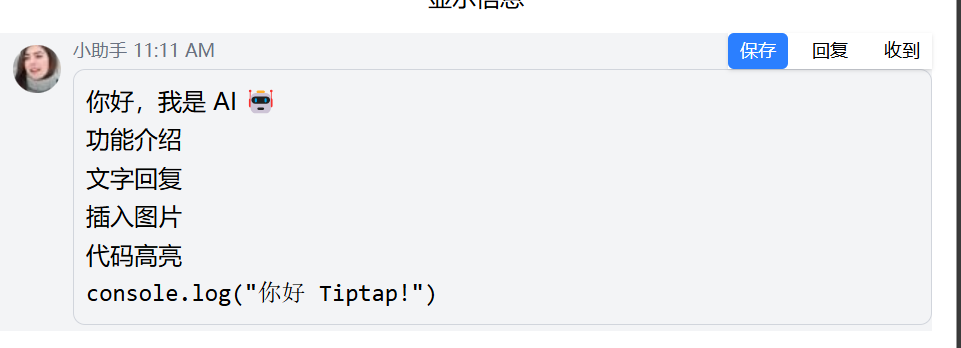

React + TipTap 富文本编辑器 实现消息列表展示,类似Slack,Deepseek等对话框功能

经过几天折腾再折腾,弄出来了,弄出来了!!! 消息展示 在位编辑功能。 两个tiptap实例1个用来展示 消息列表,一个用来在位编辑消息。 tiptap灵活富文本编辑器,拓展性太好了!!! !!! 关键点&#x…...

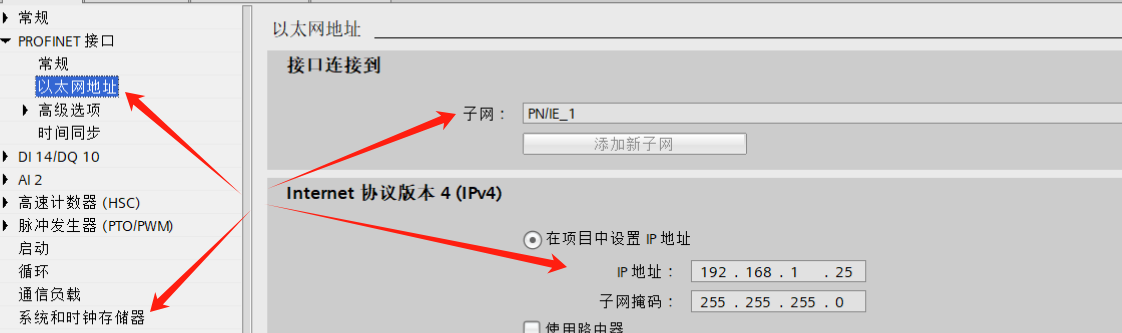

博途 TIA Portal之1200做主站与汇川EASY的TCP通讯

前言,虽然已经做了几篇关于TCP通讯的文章,但是不同的PLC之间的配合可能不同,下面将演示这种差异。 关于汇川EASY做从站的配置请参见下方链接文章:汇川EASY系列之以太网通讯(套接字socket做从站)_汇川以太网tcp套接字fb块-CSDN博客 1、硬件准备: 1200PLC,汇川EASY320…...

蓝桥杯速成刷题清单(上)

一、1.排序 - 蓝桥云课 (快速排序)算法代码: #include <bits/stdc.h> using namespace std; const int N 5e5 10; int a[N];int main() {int n;cin >> n;for (int i 0; i < n; i) {cin >> a[i];}sort(a, a n);for …...

力扣第444场周赛

这次力扣周赛对我来说难度确实大, 只做出两题, 但还是想分享一下的做题经验和感受 1. 移除最小数对使数组有序 I 题目链接:力扣 给你一个数组 nums,你可以执行以下操作任意次数: 选择 相邻 元素对中 和最小 的一对。如果存在多个这样的对&a…...

Redis 持久化机制详解:RDB/AOF 过程、优缺点及配置。Redis持久化中的Fork与Copy-on-Write技术解析。

Redis 持久化机制详解:RDB/AOF 过程、优缺点及配置 一、RDB 持久化过程及特性 核心机制 生成快照:通过 fork 子进程生成内存数据的二进制快照文件(.rdb),父进程继续处理请求。写时复制(Copy-On-Write&…...

Go并发背后的双引擎:CSP通信模型与GMP调度|Go语言进阶(4)

为什么需要理解CSP与GMP? 当我们启动一个Go程序时,可能会创建成千上万个goroutine,它们是如何被调度到有限的CPU核心上的?为什么Go能够如此轻松地处理高并发场景?为什么有时候我们的并发程序会出现奇怪的性能瓶颈&…...

docker内安装达梦8数据库

1. 其他机器上实现挂载ISO # 1. 确保挂载点目录存在(你已经创建了dm8目录) ls -ld dm8# 2. 使用正确的mount命令挂载ISO sudo mount -o loop dm8_20250117_HWarm920_kylin10_sp1_64.iso dm8# 3. 验证是否挂载成功 mount | grep dm8 ls dm82. docker内运…...

UDP怎么样实现可靠传输?

如果需要在基于UDP的应用中实现可靠传输(例如确保数据不丢失、按顺序到达等),通常需要在应用层实现相应的机制。 1. 确认应答机制 应用层可以使用确认应答机制来确保数据的可靠传输。当发送方发送一个数据包时,接收方收到数据包…...

代码随想录算法训练营Day25

一、力扣93.复原IP地址【medium】 题目链接:力扣93.复原IP地址 left x300 视频链接:代码随想录 1、思路 时间复杂度: O ( n ) O(n) O(n) 2、代码 class Solution:def restoreIpAddresses(self, s: str) -> List[str]:n len(s)ans []…...

Linux服务器——Samba服务器

简介 Samba 是一个开源的跨平台文件共享服务,允许 Linux/Unix 系统与 Windows 系统实现文件和打印机的共享与互操作。其核心协议为 SMB/CIFS(Server Message Block / Common Internet File System),是 Windows 网络中…...

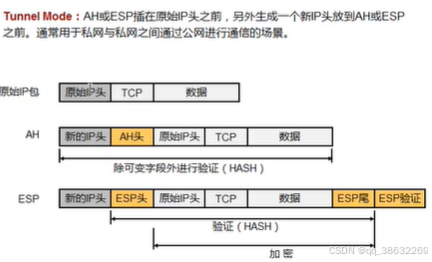

华为网路设备学习-17

目录 一、加密算法 二、验证算法 三、IPsec协议 1.IKE协议(密钥交换协议) ①ISAKMP(Internet Security Association and Key Management Protocol)互联网安全关联和密钥管理协议 ②安全关联(SA) ③…...

各开源协议一览

在 GitHub 上,开源项目通常会使用一些常见的开源协议来定义项目的使用、修改和分发规则。以下是目前 GitHub 上最常见的几种开源协议及其差异和示例说明: TL;DR 协议宽松程度是否强制开源专利保护适用场景MIT最宽松否无希望代码被广泛使用Apache 2.0宽松…...

解决python manage.py shell ModuleNotFoundError: No module named xxx

报错如下: python manage.py shellTraceback (most recent call last):File "/Users/z/Documents/project/c/manage.py", line 10, in <module>execute_from_command_line(sys.argv)File "/Users/z/.virtualenvs/c/lib/python3.12/site-packa…...

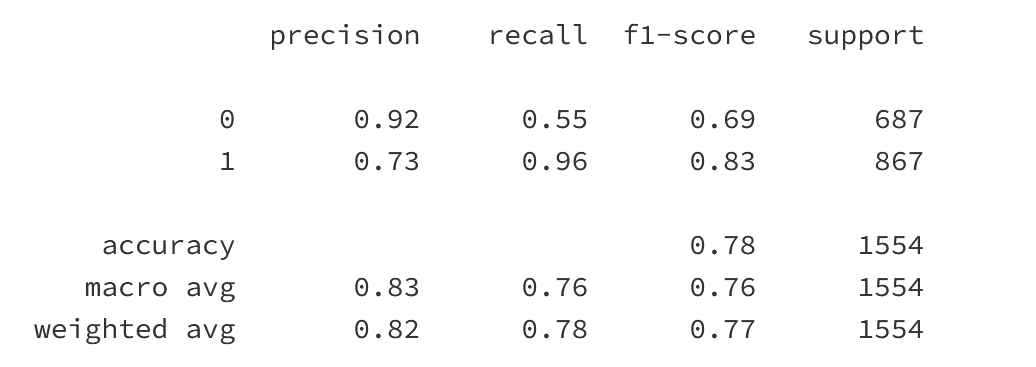

机器学习12-集成学习-案例

参考 【数据挖掘】基于XGBoost的垃圾短信分类与预测 【分类】使用XGBoost算法对信用卡交易进行诈骗预测 银行卡电信诈骗危险预测(LightGBM版本) 【数据挖掘】基于XGBoost的垃圾短信分类与预测 基于XGBoost的垃圾短信分类与预测 我分享了一个项目给你《【数据挖掘】基于XG…...

使用Ubuntu18恢复群晖nas硬盘数据外接usb

使用Ubuntu18恢复群晖nas硬盘数据外接usb 1. 接入硬盘2.使用Ubuntu183.查看nas硬盘信息3. 挂载nas3.1 挂载损坏nas硬盘(USB)3.2 挂载当前运行的nas 4. 拷贝数据分批传输 5. 新旧数据对比 Synology NAS 出现故障,DS DiskStation损坏,则可以使用计算机和 U…...

微服务系统记录

记录下曾经工作涉及到微服务的相关知识。 1. 架构设计与服务划分 关键内容 领域驱动设计(DDD): 利用领域模型和限界上下文(Bounded Context)拆分业务,明确服务边界。通过事件风暴(Event Storm…...

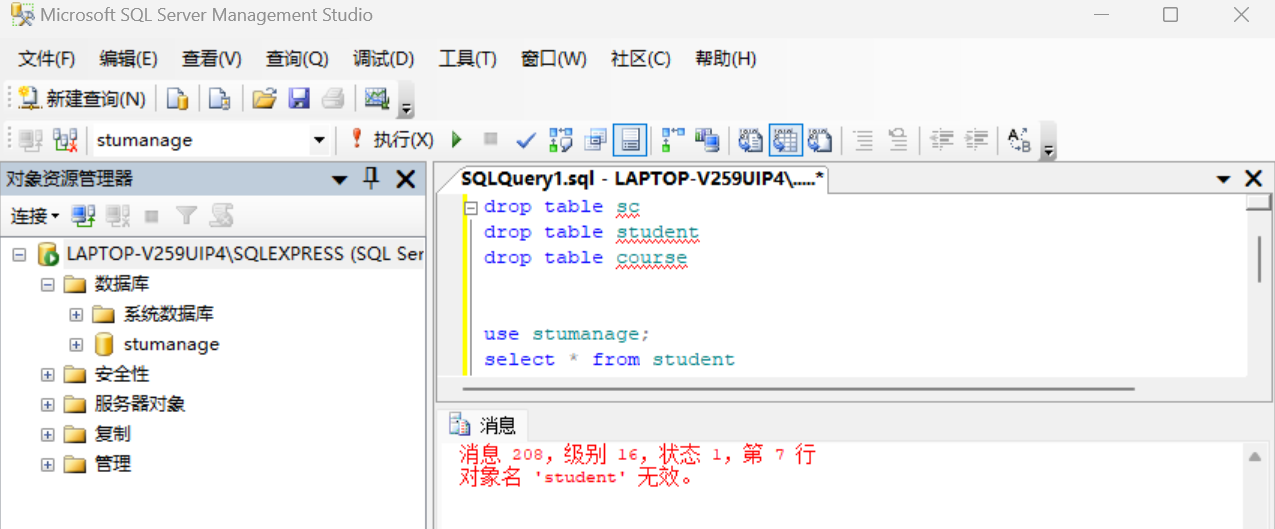

【数据库原理及安全实验】实验二 数据库的语句操作

目录 指导书原文 实操备注 指导书原文 【实验目的】 1) 掌握使用SQL语言进行数据操纵的方法。 【实验原理】 1) 面对三个关系表student,course,sc。利用SQL语句向表中插入数据(insert),然后对数据进行delete&…...

python 微信小程序支付、查询、退款使用wechatpy库

首先使用 wechatpy 库,执行以下命令进行安装 pip install wechatpy 1、 直连商户支付 import logging from django.http import JsonResponse from django.views.decorators.http import require_http_methods from wechatpy.pay import WeChatPay from wechatpy.…...

)

蓝桥杯备赛学习笔记:高频考点与真题预测(C++/Java/python版)

2025蓝桥杯备赛学习笔记 ——高频考点与真题预测 一、考察趋势分析 通过对第13-15届蓝桥杯真题的分析,可以发现题目主要围绕基础算法、数据结构、数学问题、字符串处理、编程语言基础展开,且近年逐渐增加动态规划、图论、贪心算法等较难题目。 1. 基…...

【BFT帝国】20250409更新PBFT总结

2411 2411 2411 Zhang G R, Pan F, Mao Y H, et al. Reaching Consensus in the Byzantine Empire: A Comprehensive Review of BFT Consensus Algorithms[J]. ACM COMPUTING SURVEYS, 2024,56(5).出版时间: MAY 2024 索引时间(可被引用): 240412 被引:…...

Linux-CentOS-7—— 配置静态IP地址

文章目录 CentOS-7——配置静态IP地址VMware workstation的三种网络模式配置静态IP地址1. 编辑虚拟网络2. 确定网络接口名称3. 切换到网卡所在的目录4. 编辑网卡配置文件5. 查看网卡文件信息6. 重启网络服务7. 测试能否通网8. 远程虚拟主机(可选) 其他补…...

Jupyter Lab 无法启动 Kernel 问题排查与解决总结

📄 Jupyter Lab 无法启动 Kernel 问题排查与解决总结 一、问题概述 🚨 现象描述: 用户通过浏览器访问远程服务器的 Jupyter Lab 页面(http://xx.xx.xx.xx:8891/lab)后,.ipynb 文件可以打开,但无…...

算法训练之位运算

♥♥♥~~~~~~欢迎光临知星小度博客空间~~~~~~♥♥♥ ♥♥♥零星地变得优秀~也能拼凑出星河~♥♥♥ ♥♥♥我们一起努力成为更好的自己~♥♥♥ ♥♥♥如果这一篇博客对你有帮助~别忘了点赞分享哦~♥♥♥ ♥♥♥如果有什么问题可以评论区留言或者私信我哦~♥♥♥ ✨✨✨✨✨✨ 个…...

linux入门三:Linux 编辑器

一、轻量级编辑器:快速上手的首选 1.1 Leafpad:极简主义的轻量之选 核心特点 轻量快速:体积小、启动快,资源占用极低,适合低配设备或快速编辑简单文件。 无复杂功能:仅支持基础文本编辑,界面…...

C++设计模式+异常处理

#include <iostream> #include <cstring> #include <cstdlib> #include <unistd.h> #include <sstream> #include <vector> #include <memory> #include <stdexcept> // 包含异常类using namespace std;// 该作业要求各位写一…...

HttpServletRequest是什么

HttpServletRequest 是 Java Servlet API 中的一个接口,表示 HTTP 请求对象。它封装了客户端(如浏览器)发送到服务器的请求信息,并提供了访问这些信息的方法。 1. 基本概念 作用: HttpServletRequest 提供了一种机制&…...