verilog和system verilog常用数据类型以及常量汇总

int和unsigned

在 Verilog-2001 中,没有 int 和 unsigned 这样的数据类型。这些关键字是 SystemVerilog 的特性,而不是 Verilog-2001 的一部分。

Verilog-2001 的数据类型

在 Verilog-2001 中,支持的数据类型主要包括以下几种:

1. 基本数据类型

-

reg:- 用于存储组合逻辑或时序逻辑中的值。

- 可以定义为标量(

reg a;)或向量(reg [31:0] data;)。

-

wire:- 用于表示连续赋值信号(如连线)。

- 也可以定义为标量或向量。

-

integer:- 一个 32 位的有符号整数类型,通常用于仿真中的循环计数器等。

- 示例:

integer i;

-

real:- 表示浮点数,主要用于仿真,不能综合。

- 示例:

real r = 3.14;

-

time:- 用于存储时间值,主要用于仿真。

- 示例:

time t;

2. 向量和数组

-

向量声明:

- 支持定义多位的信号,例如

reg [7:0] data;。 - 可以是有符号或无符号的(默认是无符号)。

- 支持定义多位的信号,例如

-

数组声明:

- 数组可以基于

reg或wire定义,但只能是一维的。 - 示例:

reg [7:0] mem [0:255];定义了一个 256 个元素的 8 位寄存器数组。

- 数组可以基于

3. 用户定义的类型

- 在 Verilog-2001 中,不支持像 SystemVerilog 那样的复杂用户定义类型(如

typedef)。

SystemVerilog 的扩展:int 和 unsigned

如果你需要使用 int 和 unsigned 类型,说明你在使用 SystemVerilog,而不是 Verilog-2001。以下是这两个关键字的含义:

-

int:- 一个 32 位的有符号整数类型。

- 示例:

int a = -10;

-

unsigned:- 用于修饰其他整数类型,使其变为无符号。

- 示例:

int unsigned b = 4294967295; // 32 位无符号整数

总结

- Verilog-2001 不支持

int和unsigned数据类型。 - 如果你需要这些特性,必须切换到 SystemVerilog。

- 在 Verilog-2001 中,可以通过

reg、wire、integer等基本类型来实现类似的功能,但需要注意它们的行为与 SystemVerilog 的类型有所不同。

bit,localparam和parameter

在 Verilog-2001 和 SystemVerilog 中,localparam 和 parameter 都是用于定义常量的关键字,但它们的使用场景和作用范围有所不同。至于 bit,它并不是 Verilog-2001 的标准数据类型,而是 SystemVerilog 引入的一个新特性。

1. parameter

定义与用途

parameter用于定义模块中的常量值,这些值可以在模块实例化时被覆盖。- 它们主要用于定义一些可配置的参数,如延时、宽度等。

示例

module example #(parameter WIDTH=8)(input [WIDTH-1:0] in, output [WIDTH-1:0] out);// 模块实现

endmodule// 实例化并覆盖参数

example #(.WIDTH(16)) inst (.in(a), .out(b));

2. localparam

定义与用途

localparam是 Verilog-2001 引入的一种特殊类型的参数,其值不能在模块实例化时被修改。- 主要用于定义局部使用的常量,通常是为了提高代码的可读性和维护性。

示例

module example;localparam DELAY = 5;reg [31:0] count;always @(posedge clk) beginif (count == DELAY)count <= 0;elsecount <= count + 1;end

endmodule

3. bit

定义与用途

bit是 SystemVerilog 引入的数据类型,表示一个单比特(1 位)的变量,默认为无符号类型。- 它的主要优势在于简洁性和明确性,特别是在处理布尔逻辑或状态标志时非常有用。

示例

bit flag; // 等价于 reg flag;

bit [7:0] data; // 等价于 reg [7:0] data;

区别与联系

parameter vs localparam

-

可覆盖性:

parameter:可以在模块实例化时被覆盖。localparam:不能在模块实例化时被覆盖,主要用于内部使用。

-

作用范围:

parameter:可以影响模块外部的行为,因为它们可以在实例化时被修改。localparam:仅限于定义模块内部使用的常量,确保这些常量不会被外部修改。

bit 数据类型

bit是 SystemVerilog 特有的,不适用于 Verilog-2001。- 在 Verilog-2001 中,通常使用

reg来代替bit,但reg可以有多种解释(例如既可以表示寄存器也可以表示单比特),而bit更加明确地表示单比特无符号数据。

常量和数据类型

常量本身并不属于数据类型,而是属于值的范畴。它们是通过特定的数据类型来存储和表示的。换句话说,常量是指其值在定义后不能被改变的实体,而数据类型决定了这些常量(以及变量)可以存储什么样的值及如何解释这些值。

数据类型与常量的关系

- 数据类型:定义了变量或常量可以存储的数据种类、范围以及操作方式。例如,在 Verilog 中常见的数据类型包括

reg、wire、integer等。 - 常量:指那些在程序执行期间其值不会发生变化的量。可以通过不同的数据类型来定义常量,比如使用

parameter或localparam在 Verilog 中定义常量,或者使用const关键字在 SystemVerilog 中定义常量。

Verilog 中的常量定义

1. parameter

- 用于定义模块级别的常量,可以在实例化模块时被覆盖。

- 示例:

module example #(parameter WIDTH=8)(input [WIDTH-1:0] in, output [WIDTH-1:0] out);// 模块实现 endmodule

2. localparam

- 类似于

parameter,但是它的值不能在模块实例化时被修改,主要用于模块内部。 - 示例:

module example;localparam DELAY = 5;reg [31:0] count;always @(posedge clk) beginif (count == DELAY)count <= 0;elsecount <= count + 1;end endmodule

3. integer 和其他基本类型中的常量

- 虽然

integer是一种数据类型,但你可以将它用作常量的载体。 - 示例:

integer const_value = 10; // 这里不是真正的常量定义,仅示例说明

SystemVerilog 中的常量增强

在 SystemVerilog 中,除了支持 Verilog 的 parameter 和 localparam 外,还引入了更直接的方式定义常量:

1. const

- 可以用于定义不可更改的变量。

- 示例:

const int fixed_value = 100;

2. bit 类型的常量

- 使用

bit类型定义单比特或向量形式的常量。 - 示例:

bit flag = 1'b1; // 单比特常量 bit [7:0] byte_const = 8'hAA; // 8位向量常量

总结

- 常量:指的是值不变的实体,并不属于数据类型本身。

- 数据类型:决定常量或变量的存储形式和操作方式。

- 在硬件描述语言(如 Verilog 和 SystemVerilog)中,我们通过特定的数据类型(如

reg、wire、integer、bit等)结合parameter、localparam或const来定义常量,从而确保某些值在设计过程中保持不变,同时明确这些值的存储格式和使用方法。

Reg,wire数据类型赋值的规则

在 Verilog 中,reg 和 wire 是两种最基本的数据类型,它们的使用和赋值规则有显著的区别。以下是详细说明以及示例代码,解释哪些赋值是合法的,哪些是非法的。

1. reg 数据类型的赋值规则

特点

reg类型变量用于存储值,可以是标量(1 位)或向量(多位)。- 它的值只能在过程块(如

always块或initial块)中被赋值。 reg类型不能直接连接到连续赋值语句(assign)。

合法赋值

以下是对 reg 的合法赋值方式:

module reg_example;reg a; // 标量 regreg [3:0] b; // 向量 reginitial begina = 1'b1; // 标量赋值b = 4'b1010; // 向量赋值#10; // 延迟 10 时间单位a = 0; // 再次赋值b = b + 1; // 对 reg 进行操作并赋值end

endmodule

非法赋值

以下是对 reg 的非法赋值方式:

module illegal_reg_example;reg a;assign a = 1'b1; // 非法:不能对 reg 使用连续赋值

endmodule

错误原因:

reg类型必须在过程块(always或initial)中赋值,不能直接用assign语句进行连续赋值。

2. wire 数据类型的赋值规则

特点

wire类型表示物理连线,用于连接模块之间的信号。- 它的值只能通过连续赋值语句(

assign)或者模块实例化端口连接来赋值。 wire类型不能在过程块(always或initial)中直接赋值。

合法赋值

以下是对 wire 的合法赋值方式:

module wire_example;wire a; // 标量 wirewire [3:0] b; // 向量 wireassign a = 1'b1; // 连续赋值assign b = 4'b1010; // 连续赋值// 模块实例化时连接 wiresub_module inst (.out(b), .in(a));

endmodulemodule sub_module(input in, output out);assign out = in; // 连续赋值

endmodule

非法赋值

以下是对 wire 的非法赋值方式:

module illegal_wire_example;wire a;initial begina = 1'b1; // 非法:不能在过程块中对 wire 赋值end

endmodule

错误原因:

wire类型必须通过assign语句或模块端口连接赋值,不能在过程块中直接赋值。

3. reg 和 wire 的区别总结

| 特性 | reg | wire |

|---|---|---|

| 用途 | 存储值 | 表示连线 |

| 赋值方式 | 在过程块(always/initial)中赋值 | 通过 assign 或模块端口连接赋值 |

| 是否需要驱动 | 不需要持续驱动 | 必须有驱动源(如 assign 或模块) |

| 默认值 | 无默认值,未初始化时为不定态 (x) | 无默认值,未驱动时为高阻态 (z) |

4. 综合示例

以下是一个综合示例,展示 reg 和 wire 的正确使用方式:

module example;reg clk; // 时钟信号reg reset; // 复位信号wire [3:0] out; // 输出信号// 连续赋值 wireassign out = (reset == 1'b1) ? 4'b0000 : 4'b1111;// 过程块中赋值 reginitial beginclk = 0;reset = 1; // 初始复位#10;reset = 0; // 取消复位endalways #5 clk = ~clk; // 生成时钟信号

endmodule

解释

reg的使用:clk和reset是reg类型,在initial和always块中赋值。

wire的使用:out是wire类型,通过assign语句根据reset的值动态计算。

- 合法性:

- 所有赋值都符合

reg和wire的规则。

- 所有赋值都符合

5. 总结

reg:- 只能在过程块(

always或initial)中赋值。 - 不能使用

assign语句赋值。

- 只能在过程块(

wire:- 只能通过

assign语句或模块端口连接赋值。 - 不能在过程块中直接赋值。

- 只能通过

理解这些规则对于正确编写 Verilog 代码非常重要,因为违反这些规则会导致编译错误或仿真行为异常。

wire和reg与输入输出端口

在 Verilog 中,模块之间的输入输出端口连接有特定的规则和方式。这些规则不仅影响到如何正确地实例化子模块,还涉及到如何将信号(如 wire 和 reg)与模块的端口进行连接。下面详细解释了这些规则,并提供了示例。

1. 输入端口 (input)

- 输入端口用于接收来自其他模块或顶层模块的信号。

- 输入端口只能连接到

wire类型或者表达式(即可以是常量、连线逻辑等),不能直接连接到reg类型变量。

示例

module top;wire in_wire;reg in_reg;// 正确:使用 wire 连接到 input 端口sub_module inst (.in(in_wire));// 错误:尝试使用 reg 直接连接到 input 端口// sub_module inst (.in(in_reg)); // 不允许initial beginin_wire = 1'b0;#10 in_wire = 1'b1;end

endmodulemodule sub_module(input in);// 模块实现

endmodule

2. 输出端口 (output)

- 输出端口用于向其他模块传递信号。

- 输出端口可以连接到

wire或者reg,具体取决于是否在过程块中赋值:- 如果在过程块中赋值(如

always块),则需要声明为reg类型。 - 如果通过连续赋值语句 (

assign) 赋值,则应声明为wire类型。

- 如果在过程块中赋值(如

示例

module top;wire out_wire;reg out_reg;// 使用 wire 连接到 output 端口sub_module inst1 (.out(out_wire));// 使用 reg 连接到 output 端口sub_module inst2 (.out(out_reg));endmodulemodule sub_module(output out);// 如果在 always 块中赋值,则 out 应该是 reg 类型reg temp_reg;assign out = temp_reg; // 合法:通过 assign 赋值给 wire 类型的 outputalways @(posedge clk) begintemp_reg <= 1'b1; // 在 always 块中赋值end

endmodule

3. 双向端口 (inout)

- 双向端口同时具有输入和输出的功能,通常用于总线通信(如三态总线)。

- 双向端口必须连接到

wire类型,因为它们需要支持高阻态 (z) 来表示未驱动状态。

示例

module top;wire bus;// 正确:双向端口必须连接到 wiretristate_buffer buffer_inst (.data(bus), .enable(enable), .data_in(data_in));endmodulemodule tristate_buffer(input enable, data_in, inout data);assign data = enable ? data_in : 1'bz; // 三态缓冲器实现

endmodule

4. 实际应用中的连接规则

wire 与端口的连接

wire可以连接到任何类型的端口(input,output,inout),这是最常见的做法。- 示例:

module top;wire in_wire;wire out_wire;sub_module inst (.in(in_wire), .out(out_wire)); endmodulemodule sub_module(input in, output out);// 模块实现 endmodule

reg 与端口的连接

reg只能连接到output端口,且该端口应在过程块中被赋值。- 示例:

module top;wire in_wire;reg out_reg;sub_module inst (.in(in_wire), .out(out_reg)); endmodulemodule sub_module(input in, output out);always @(posedge clk) beginif (in)out <= 1'b1;elseout <= 1'b0;end endmodule

reg 不能直接连接到 input 或 inout 端口

reg类型的变量不能直接连接到input或inout端口,因为它们不是连续赋值模型的一部分。- 示例(错误用法):

module top;reg in_reg;// 错误:试图将 reg 直接连接到 input 端口// sub_module inst (.in(in_reg)); // 不合法 endmodule

5. 总结

input:只能连接到wire类型或表达式,不能直接连接到reg。output:可以连接到wire或reg,但如果是过程块赋值则应使用reg,如果是连续赋值则应使用wire。inout:必须连接到wire类型,因为它们需要支持高阻态。

相关文章:

verilog和system verilog常用数据类型以及常量汇总

int和unsigned 在 Verilog-2001 中,没有 int 和 unsigned 这样的数据类型。这些关键字是 SystemVerilog 的特性,而不是 Verilog-2001 的一部分。 Verilog-2001 的数据类型 在 Verilog-2001 中,支持的数据类型主要包括以下几种: …...

Dify升级-linux环境下使用zip离线安装方式部署升级

Dify安装时Linux服务器到github网络不好,git clone拉去不下来代码。使用本地windows电脑下载zip包形式上传进行了安装。但是随着dfiy版本升级,本地使用最新版本的,也需要进行下升级。参考升级指导以及自己环境情况,升级步骤如下。…...

)

容器修仙传 我的灵根是Pod 第9章 时空禁术(Job与CronJob)

第三卷:上古遗迹元婴篇 第9章 时空禁术(Job与CronJob) 极北冰渊深处,万丈冰层下封印着上古禁术「轮回溯光阵」。 林衍的混沌灵根突然结出冰霜——这不是寒冷所致,而是阵法中逸散的时空乱流。冰壁上刻满血色符文&…...

)

Web3.0的认知补充(去中心化)

涉及开发技术: Vue Web3.js Solidity 基本认知 Web3.0含义: 新一代互联网思想:去中心化及用户为中心的互联网 数据:可读可写可授权 核心技术:区块链、NFT 应用:互联网上应用 NFT &…...

【Python网络爬虫实战指南】从数据采集到反反爬策略

目录 前言技术背景与价值当前技术痛点解决方案概述目标读者说明 一、技术原理剖析核心概念图解核心作用讲解关键技术模块说明技术选型对比 二、实战演示环境配置要求核心代码实现案例1:静态页面抓取(电商价格)案例2:动态页面抓取&…...

Atlas 800I A2 离线部署 DeepSeek-R1-Distill-Llama-70B

一、环境信息 1.1、硬件信息 Atlas 800I A2 1.2、环境信息 注意:这里驱动固件最好用商业版,我这里用的社区版有点小问题 操作系统:openEuler 22.03 LTS NPU驱动:Ascend-hdk-910b-npu-driver_24.1.rc3_linux-aarch64.run NPU固…...

基于SpringBoot+Vue的影视系统(源码+lw+部署文档+讲解),源码可白嫖!

摘要 时代在飞速进步,每个行业都在努力发展现在先进技术,通过这些先进的技术来提高自己的水平和优势,影视推荐系统当然不能排除在外。影视系统是在实际应用和软件工程的开发原理之上,运用Java语言以及Spring Boot、VUE框架进行开…...

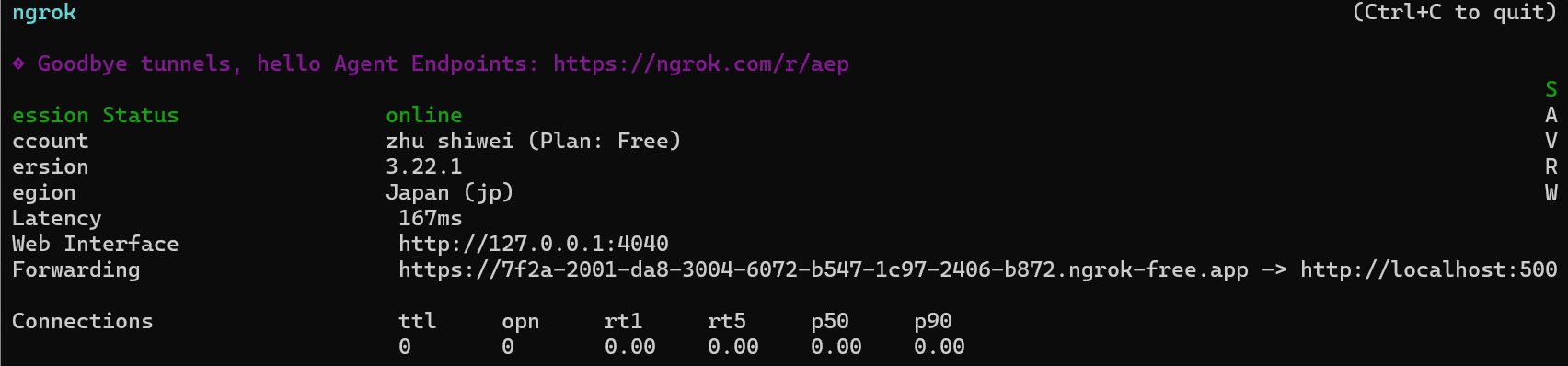

搭建Stable Diffusion图像生成系统实现通过网址访问(Ngrok+Flask实现项目系统公网测试,轻量易部署)

目录 前言 背景与需求 🎯 需求分析 核心功能 网络优化 方案确认 1. 安装 Flask 和 Ngrok 2. 构建 Flask 应用 3. 使用 Ngrok 实现内网穿透 4. 测试图像生成接口 技术栈 实现流程 优化目标 实现细节 1. 迁移到Flask 2. 持久化提示词 3. 图像下载功能 …...

Java 21 的“无类主”特性:简化编程的第一步

在Java编程中,编写一个简单的“Hello, World!”程序通常需要以下代码: public class HelloWorld {public static void main(String[] args) {System.out.println("Hello, World!");} }这种结构包含了许多对初学者来说难以理解的概念ÿ…...

AI | 最近比较火的几个生成式对话 AI

关注:CodingTechWork 引言 生成式对话 AI 正在迅速改变我们与机器交互的方式,从智能助手到内容创作,其应用范围广泛且深远。本文将深入探讨几款当前热门的生成式对话 AI 模型,包括 Kimi、DeepSeek、ChatGPT、文心一言、通义千问和…...

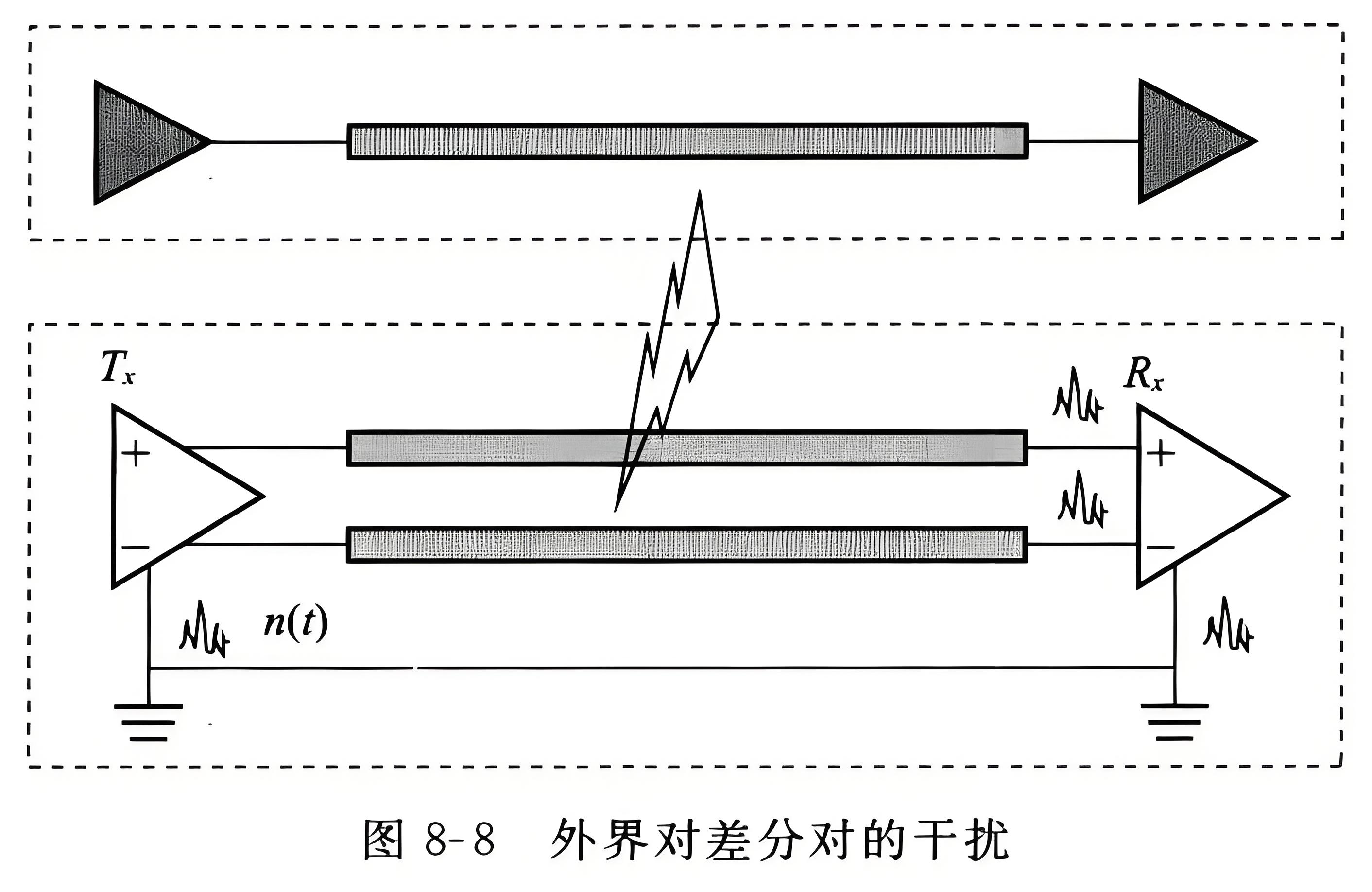

差分信号抗噪声原理:

差分信号抗噪声原理: 差分信号除了能很好地解决发送和接收参考点电位不同的问题外,差分信号的另一个重要优势就是在一定条件下其抗干扰能力比单端信号更强。对于单端信号传输,外界对它的干扰噪声直接叠加在信号上,接收端直接检测输…...

6 种AI实用的方法,快速修复模糊照片

照片是我们记录生活的重要方式。但有时,由于各种原因,照片会变得模糊,无法展现出我们想要的效果。幸运的是,随着人工智能(AI)技术的发展,现在有多种方法可以利用 AI 修复模糊照片,让…...

JavaScript 的“积木”:函数入门与实践

引言:告别重复,拥抱模块化 想象一下,你在写代码时发现,有几段逻辑几乎一模一样,需要在不同的地方反复使用。你是选择每次都复制粘贴,还是希望能像搭积木一样,把这段逻辑封装起来,需…...

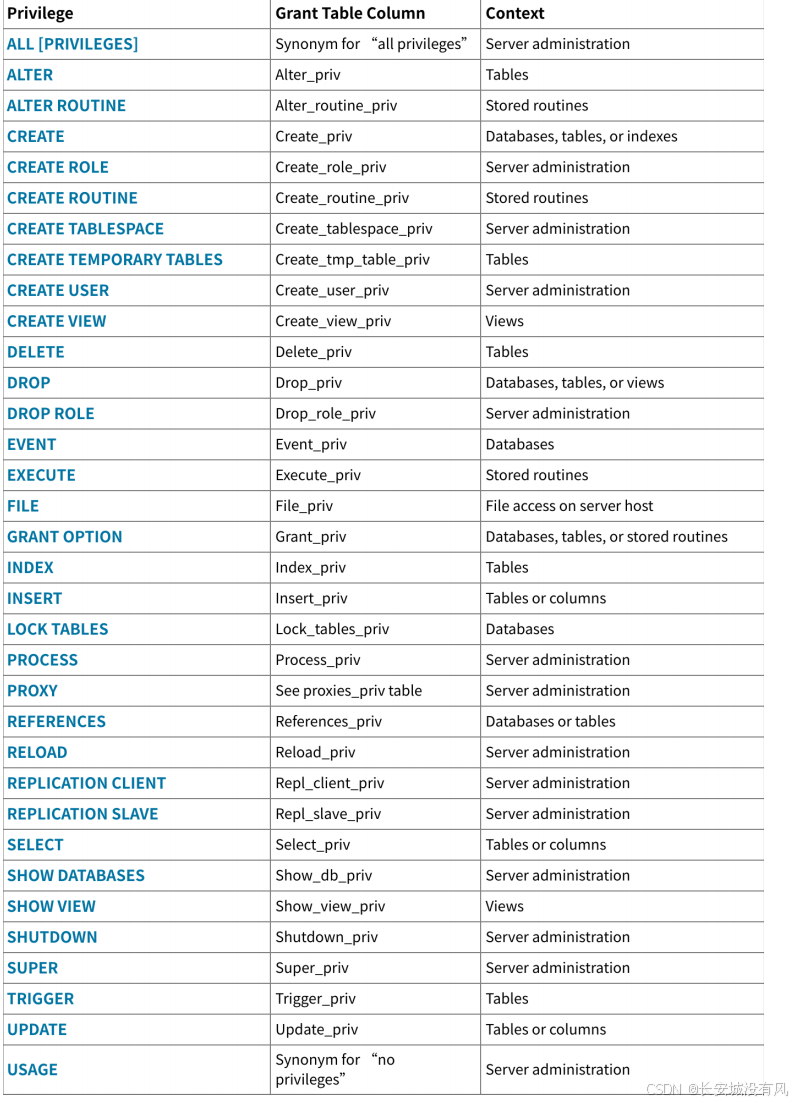

从入门到精通【MySQL】视图与用户权限管理

文章目录 📕1. 视图✏️1.1 视图的基本概念✏️1.2 试图的基本操作🔖1.2.1 创建视图🔖1.2.2 使用视图🔖1.2.3 修改数据🔖1.2.4 删除视图 ✏️1.3 视图的优点 📕2. 用户与权限管理✏️2.1 用户🔖…...

C++中的next_permutation全排列函数

目录 什么是全排列用法实现原理自定义比较函数 注意事项相关题目1.AB Problem2.P1088 火星人 什么是全排列 全排列是指从一组元素中按照一定顺序(按字典序排列)取出所有元素进行排列的所有可能情况。 例如,对于集合{1,2,3},它的全排列包括&a…...

修改el-select背景颜色

修改el-select背景颜色 /* 修改el-select样式--直接覆盖默认样式(推荐) */ ::v-deep .el-select .el-input__inner {background-color: #1d2b72 !important; /* 修改输入框背景色 */color: #fff; } ::v-deep .el-select .el-input__wrapper {background-…...

dockercompose文件仓库

mysql version: 3 # 使用docker-compose的版本,根据需要可以调整# 创建数据目录 # mkdir -p /home/docker/mysql/mysql_data # mkdir -p /home/docker/mysql/mysql_logs # 给予适当的权限(确保MySQL容器可以读写这些目录) # chmod 777 /ho…...

【C++入门:类和对象】[3]

C入门:类和对象 拷贝构造(拷贝初始化) 拷贝构造是构造函数的重载 class Date { public:Date(int year1,int month1,int day1) { _yearyear; _monthmonth; _dayday; } Date(const Date& d)//(拷贝构造,把d1传参给d)引用传参不改变使用const //注意使用&,不然会无穷递…...

【mdlib】0 全面介绍 mdlib - Rust 实现的 Markdown 工具集

mdlib 是由开发者 bahdotsh 创建的一个多功能 Markdown 工具集合,包含两个主要组件:一个轻量级 Markdown 解析库和一个功能完善的个人 Wiki 系统。该项目完全采用 Rust 实现,兼具高性能与跨平台特性。 核心组件 Markdown 解析库 特性&#…...

今日CSS学习浮动->定位

------------------------------------------------------------------------------------------------------- CSS的浮动 float 属性用于创建浮动框,将其移动到一边,直到左边缘或右边缘触及包含块或另一个浮动框的边缘。 float 属性定义元素在哪个方向浮…...

如何实现Spring Boot应用程序的安全性:全面指南

在现代 Web 开发中,安全性是 Spring Boot 应用程序的核心需求,尤其是在微服务、云原生和公开 API 场景中。Spring Boot 结合 Spring Security 提供了一套强大的工具,用于保护应用程序免受常见威胁,如未经授权的访问、数据泄露、跨…...

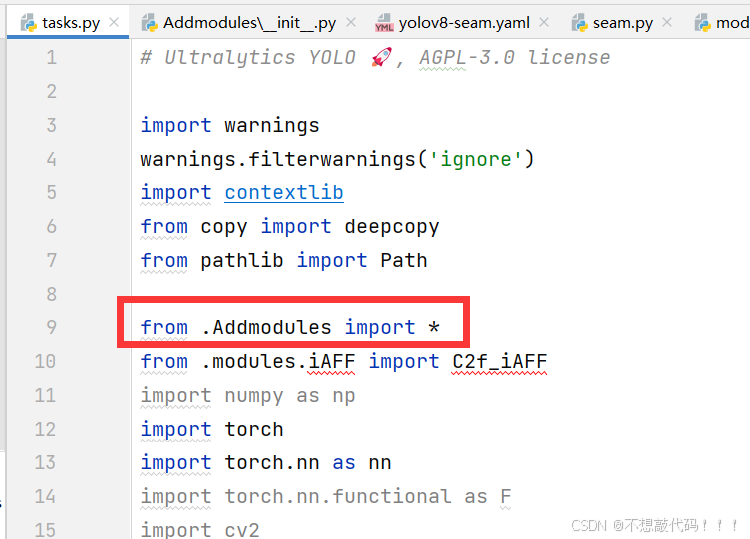

YOLOv8融合CPA-Enhancer【提高恶略天气的退化图像检测】

1.CPA介绍 CPA-Enhancer通过链式思考提示机制实现了对未知退化条件下图像的自适应增强,显著提升了物体检测性能。其插件式设计便于集成到现有检测框架中,并在物体检测及其他视觉任务中设立了新的性能标准,展现了广泛的应用潜力。 关于CPA-E…...

Python 项目环境配置与 Vanna 安装避坑指南 (PyCharm + venv)

在进行 Python 项目开发时,一个干净、隔离且配置正确的开发环境至关重要。尤其是在使用像 PyCharm 这样的集成开发环境 (IDE) 时,正确理解和配置虚拟环境 (Virtual Environment) 是避免许多常见问题的关键。本文结合之前安装 Vanna 库时遇到的问题&#…...

第52讲:农业AI + 区块链——迈向可信、智能、透明的未来农业

目录 一、为什么农业需要“AI+区块链”? 二、核心应用场景解读 1. 农产品溯源系统 2. 农业信贷与保险精准评估 3. 农业碳足迹追踪与碳汇交易 三、案例实战分享:智能溯源 + 区块链合约 四、面临挑战与展望 五、总结 在数字农业时代,“AI” 和 “区块链” 是两股不容忽…...

)

模板偏特化 (Partial Specialization)

C 模板偏特化 (Partial Specialization) 模板偏特化允许为模板的部分参数或特定类型模式提供定制实现,是 静态多态(Static Polymorphism) 的核心机制之一。以下通过代码示例和底层原理,全面解析模板偏特化的实现规则、匹配优先级…...

【防火墙 pfsense】1简介

(1) pfSense 有以下可能的用途: 边界防火墙 路由器 交换机 无线路由器 / 无线接入点 (2)边界防火墙 ->要充当边界防火墙,pfSense 系统至少需要两个接口:一个广域网(WAN࿰…...

Qt UDP组播实现与调试指南

在Qt中使用UDP组播(Multicast)可以实现高效的一对多网络通信。以下是关键步骤和示例代码: 一、UDP组播核心机制 组播地址:使用D类地址(224.0.0.0 - 239.255.255.255)TTL设置:控制数据包传播范围(默认1,同一网段)网络接口:指定发送/接收的物理接口二、发送端实现 /…...

线上助农产品商城小程序源码介绍

基于ThinkPHPFastAdminUniApp开发的线上助农产品商城小程序源码,旨在为农产品销售搭建一个高效、便捷的线上平台,助力乡村振兴。 一、技术架构 该小程序源码采用了ThinkPHP作为后端框架,FastAdmin作为快速开发框架,UniApp作为跨…...

【maven-7.1】POM文件中的属性管理:提升构建灵活性与可维护性

在Maven项目中,POM (Project Object Model) 文件是核心配置文件,而属性管理则是POM中一个强大但常被低估的特性。良好的属性管理可以显著提升项目的可维护性、减少重复配置,并使构建过程更加灵活。本文将深入探讨Maven中的属性管理机制。 1.…...

基于Matlab的车牌识别系统

1.程序简介 本模型基于MATLAB,通过编程创建GUI界面,基于Matlab的数字图像处理,对静止的车牌图像进行分割并识别,通过编写matlab程序对图像进行灰度处理、二值化、腐蚀膨胀和边缘化处理等,并定位车牌的文字,实现字符的…...