ZYNQ笔记(二十):Clocking Wizard 动态配置

版本:Vivado2020.2(Vitis)

任务:ZYNQ PS端 通过 AXI4Lite 接口配置 Clocking Wizard IP核输出时钟频率

目录

一、介绍

二、寄存器定义

三、配置

四、PS端代码

一、介绍

Xilinx 的 Clock Wizard IP核 用于在 FPGA 中生成和管理时钟信号。它支持 动态重配置(Dynamic Reconfiguration),允许在运行时通过 AXI4-Lite 接口 或 DRP 接口(这两个接口都是在配置IP核时的可选接口) 修改时钟参数(如频率、相位等),而无需重新编程 FPGA。

-

AXI4-Lite 接口:用于软件(如 MicroBlaze/Zynq PS)动态修改时钟参数

-

DRP(Dynamic Reconfiguration Port):硬件接口,直接访问 Clock Wizard 配置寄存器

二、寄存器定义

参考文章:

AMD Technical Information Portal

[小梅哥FPGA] 如何通过动态重配置实现FPGA时钟的实时频率/相位/占空比调整?

如何使用AXI4接口对PLL/MMCM输出时钟的频率和相位进行动态重配置 - Xilinx Vivado 开发板 - 芯路恒电子技术论坛 - Powered by Discuz!

每个寄存器数据为32位4字节,大部分寄存器地址间隔0x04。

| 寄存器名 | 寄存器地址 | 功能 |

| Software Reset Register (SRR) | C_BASEADDR+0X00 | 写入0x0000_000A可复位PLL/MMCM |

| Status Register (SR) | C_BASEADDR+0X04 | Locked信号,Bit[0] = locked,值为1时代表输出时钟稳定 |

| Clock Configuration Register 0 | C_BASEADDR+0X200 | 反馈时钟分、倍频控制,value = 系数*1000 Bit[25:16] = CLKFBOUT_FRAC Multiply(仅MMCM才有,VCO的1/8小数倍频系数) Bit[15:8] = CLKFBOUT_MULT(VCO整数倍频系数) Bit[7:0] = DIVCLK_DIVIDE(VCO分频系数) |

| Clock Configuration Register 1 | C_BASEADDR+0X204 | 反馈时钟相位控制,value = 相位*1000 Bit[31:0] = CLKFBOUT_PHASE |

| Clock Configuration Register 2 | C_BASEADDR+0X208 | CLKOUT0分频系数,value = 分频系数*1000 Bit[7:0] = CLKOUT0_DIVIDE Bit[17:8] = CLKOUT0_FRAC Divide(仅MMCM才有,CLKOUT0的1/8小数倍频系数) |

| Clock Configuration Register 3 | C_BASEADDR+0X20C | CLKOUT0相位配置,value = 相位*1000 Bit[31:0] = CLKOUT0_PHASE |

| Clock Configuration Register 4 | C_BASEADDR+0X210 | CLKOUT0占空比配置,value = 占空比*1000 Bit[31:0] = CLKOUT0_DUTY |

| Clock Configuration Register 5 | C_BASEADDR+0X214 | CLKOUT1分频系数,不支持小数分频,value = 分频系数*1000 Bit[7:0] = CLKOUT1_DIVIDE |

| ...... | ...... | ...... |

| Clock Configuration Register 23 | C_BASEADDR+0X25C | Bit[0] = LOAD, 置 1 加载配置寄存器的值到内部寄存器,并在下一周期置0 Bit[1] = SADDR, 写 0 将默认 GUI 中的参数加载到动态配置中; 写 1 将配置寄存器参数加载到动态配置中 |

三、配置

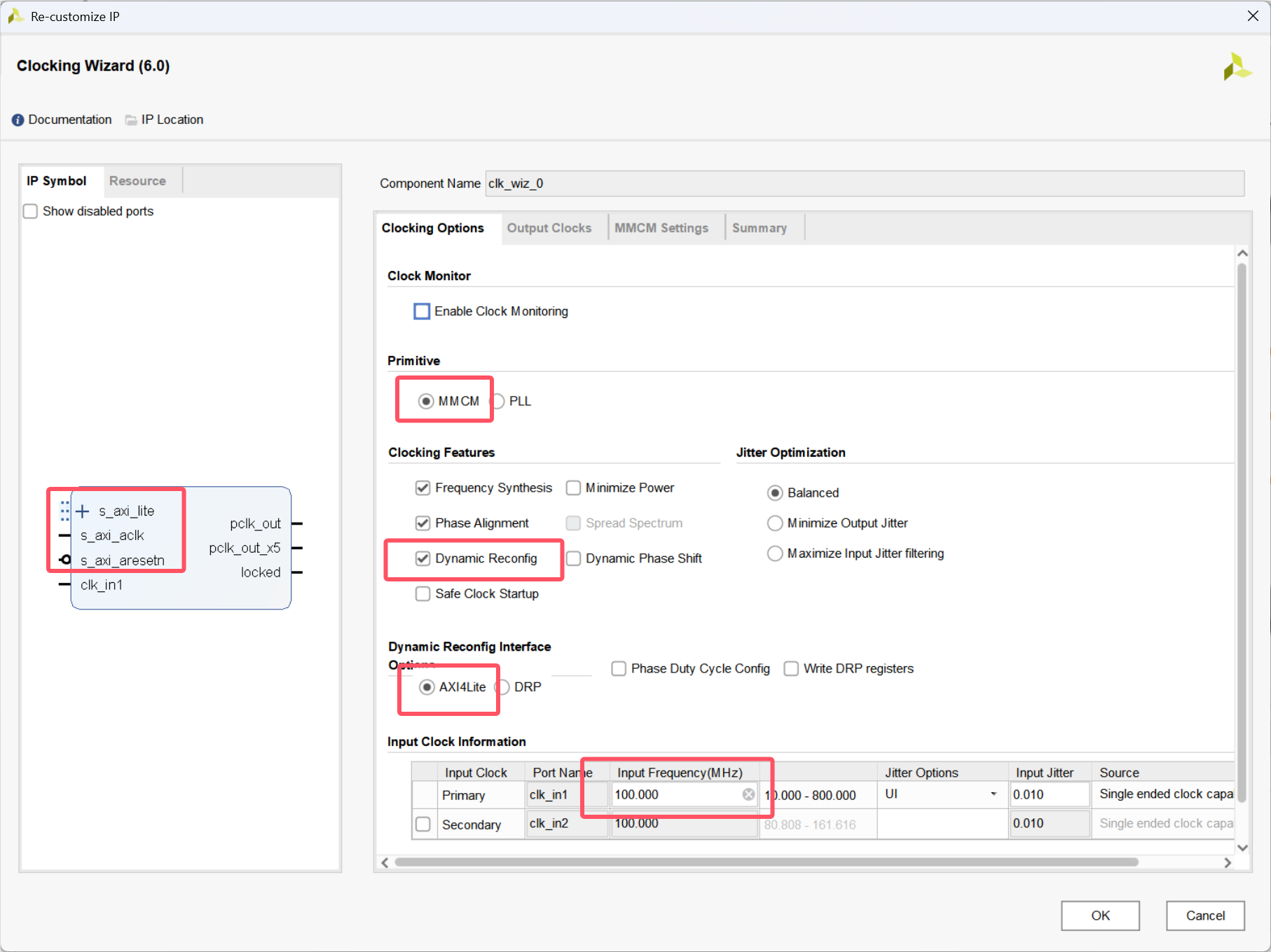

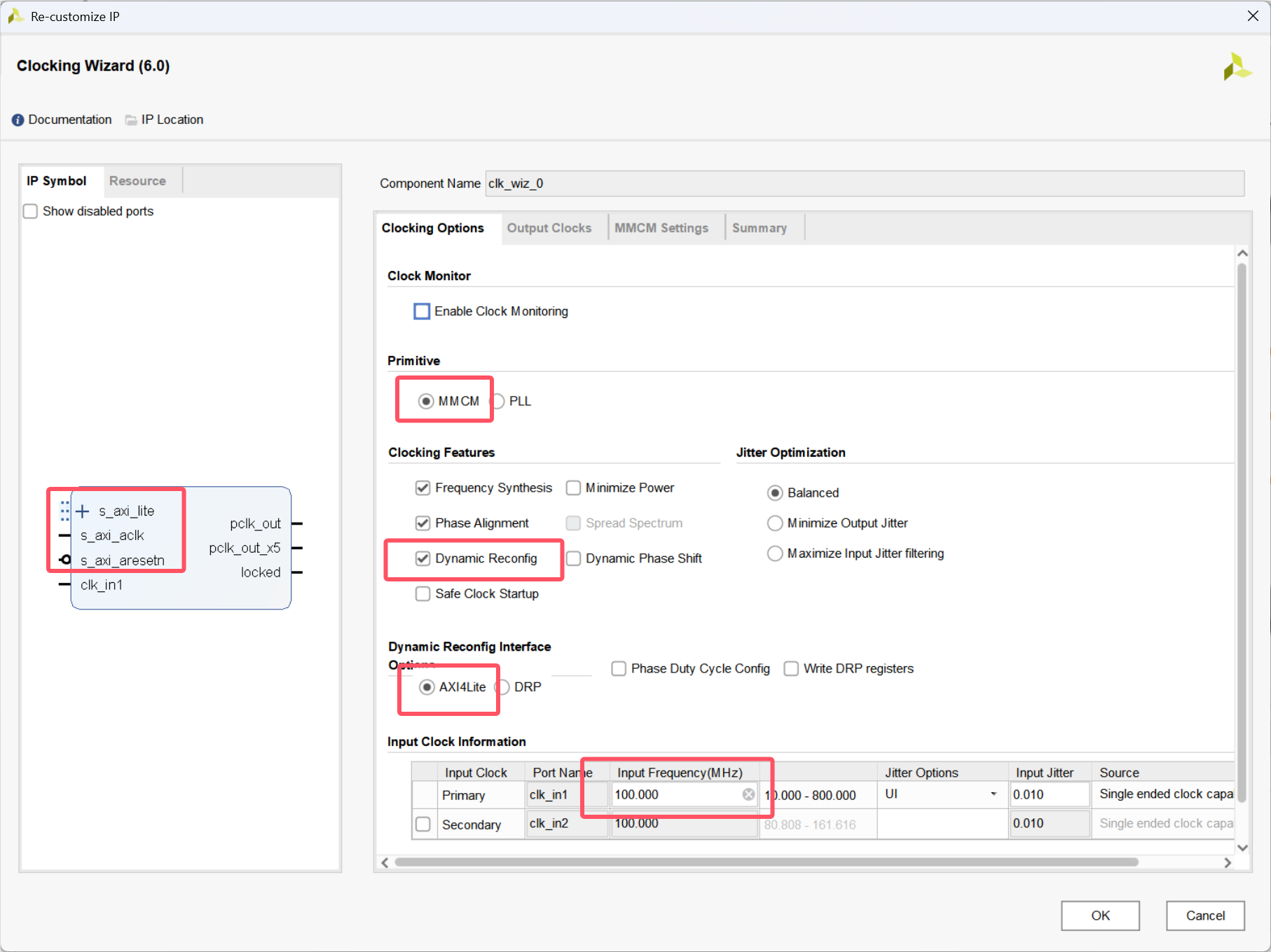

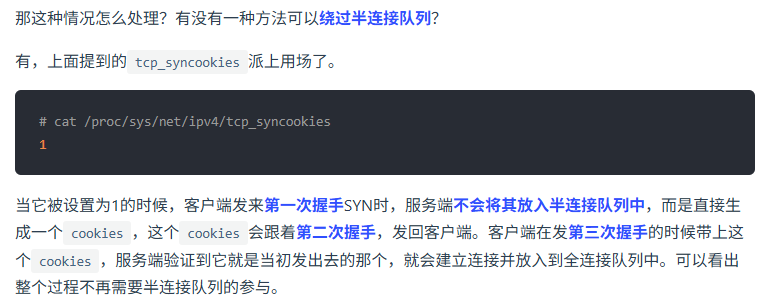

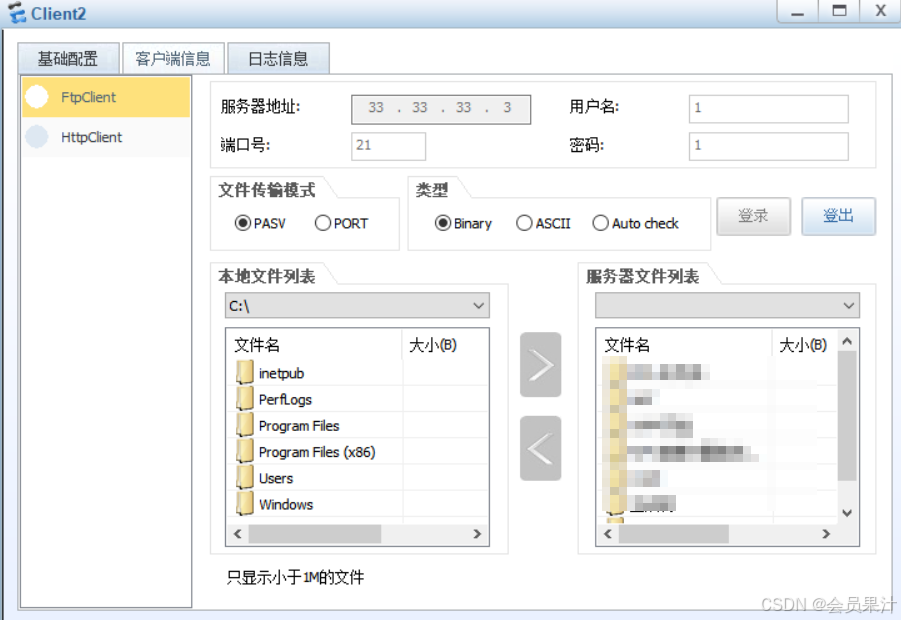

本次通过 ZYNQ PS 端进行配置, Clocking Wizard 配置如下:MMCM、勾选动态配置(频率配置)、AXI4Lite 接口(PS 通过该接口配置)、输入频率100MHz(根据实际频率设置)

四、PS端代码

参考的正点原子的代码,并他的基础上进行修改,因为源码实现只有一个输出时钟端口的 clk_wiz 的频率配置,修改为有两个时钟输出端口的 clk_wiz 频率配置,(但是我发现正点原子的小数部分设置没有除以8,我测试输出时钟输入给 DVI 转化模块驱动 HDMI 时,除以8后才对上时序频率,显示屏才出现图像,但是正点原子的驱动 LCD 的例程都没有除以8,可能存在精度问题,希望有搞清楚的可以在评论区补充一下):

clk_wiz.h:

#ifndef CLK_WIZ_H_

#define CLK_WIZ_H_#include "xil_types.h"#define CLK_SR_OFFSET 0x04 //Status Register//clk_out0

#define CLK_CFG0_OFFSET 0x200 //Clock Configuration Register 0

#define CLK_CFG2_OFFSET 0x208 //Clock Configuration Register 2//clk_out1

#define CLK_CFG5_OFFSET 0x214 //Clock Configuration Register 5

#define CLK_CFG7_OFFSET 0x222 //Clock Configuration Register 7#define CLK_CFG23_OFFSET 0x25C //Clock Configuration Register 23void clk_wiz_cfg(u32 clk_device_id, double freq0, double freq1);#endif /* CLK_WIZ_H_ */clk_wiz.c

#include "xclk_wiz.h"

#include "clk_wiz.h"

#include "xparameters.h"#define CLK_WIZ_IN_FREQ 100 //时钟IP核输入100MhzXClk_Wiz clk_wiz_inst; //时钟IP核驱动实例//时钟IP核动态重配置

//参数1:时钟IP核的器件ID

//参数2:时钟IP核输出的时钟0频率 单位:MHz

//参数3:时钟IP核输出的时钟1频率 单位:MHz

void clk_wiz_cfg(u32 clk_device_id, double freq0, double freq1)

{double div_factor = 0;u32 div_factor_int = 0;u32 dviv_factor_frac = 0;u32 clk_divide = 0;u32 status = 0;//初始化XCLK_WizXClk_Wiz_Config *clk_cfg_ptr;clk_cfg_ptr = XClk_Wiz_LookupConfig(clk_device_id);XClk_Wiz_CfgInitialize(&clk_wiz_inst,clk_cfg_ptr,clk_cfg_ptr->BaseAddr);//配置输入时钟倍频/分频系数(多个时钟输出就只用配置一次,后面都用这一个标准进行分配输出)XClk_Wiz_WriteReg(clk_cfg_ptr->BaseAddr,CLK_CFG0_OFFSET,0x00000a01); //10倍频,1分频(输出频率不能超过(CLK_WIZ_IN_FREQ*10/1)MHz)//配置输出时钟0频率if(freq0 <= 0){//计算分频系数div_factor = CLK_WIZ_IN_FREQ * 10 / freq0;div_factor_int = (u32)div_factor; //(取整)分频系数整数部分dviv_factor_frac = (u32)((div_factor - div_factor_int) * 1000 /8); //(取整)分频系数小数部分的8分之一(针对mmcm)clk_divide = div_factor_int | (dviv_factor_frac<<8);xil_printf("div_factor_0: %d.%d\n", div_factor_int,dviv_factor_frac*8); // 打印设置的分频系数//配置分频系数XClk_Wiz_WriteReg(clk_cfg_ptr->BaseAddr,CLK_CFG2_OFFSET,clk_divide);}//配置输出时钟0频率if(freq1 <= 0){//计算分频系数div_factor = CLK_WIZ_IN_FREQ * 10 / freq1;div_factor_int = (u32)div_factor;dviv_factor_frac = (u32)((div_factor - div_factor_int) * 1000 /8);clk_divide = div_factor_int | (dviv_factor_frac<<8);xil_printf("div_factor_1: %d.%d\n", div_factor_int,dviv_factor_frac*8); // 打印设置的分频系数//配置分频系数XClk_Wiz_WriteReg(clk_cfg_ptr->BaseAddr,CLK_CFG7_OFFSET,clk_divide);}// 调试(可选):打印当前寄存器值/*xil_printf("After config:\n");xil_printf("CLK_CFG0: 0x%08X\n", XClk_Wiz_ReadReg(clk_cfg_ptr->BaseAddr, CLK_CFG0_OFFSET));xil_printf("CLK_CFG2: 0x%08X\n", XClk_Wiz_ReadReg(clk_cfg_ptr->BaseAddr, CLK_CFG2_OFFSET));xil_printf("CLK_CFG5: 0x%08X\n", XClk_Wiz_ReadReg(clk_cfg_ptr->BaseAddr, CLK_CFG5_OFFSET));xil_printf("CLK_CFG7: 0x%08X\n", XClk_Wiz_ReadReg(clk_cfg_ptr->BaseAddr, CLK_CFG7_OFFSET));*///加载重配置的参数XClk_Wiz_WriteReg(clk_cfg_ptr->BaseAddr,CLK_CFG23_OFFSET,0x00000003);//获取时钟IP核的状态,判断是否重配置完成while(1){status = XClk_Wiz_ReadReg(clk_cfg_ptr->BaseAddr,CLK_SR_OFFSET);if(status&0x00000001) //Bit0 Locked信号return ;}

}函数调用

#include "xclk_wiz.h"

#include "clk_wiz.h"#define CLK_WIZ_ID XPAR_CLK_WIZ_0_DEVICE_ID //时钟IP核器件IDint main()

{double freq0 = 74.25;double freq1 = 371.25;//配置时钟IP输出频率(单位MHz)clk_wiz_cfg(CLK_WIZ_ID, freq0 , freq1);...return 0;

}相关文章:

ZYNQ笔记(二十):Clocking Wizard 动态配置

版本:Vivado2020.2(Vitis) 任务:ZYNQ PS端 通过 AXI4Lite 接口配置 Clocking Wizard IP核输出时钟频率 目录 一、介绍 二、寄存器定义 三、配置 四、PS端代码 一、介绍 Xilinx 的 Clock Wizard IP核 用于在 FPGA 中生成和管理…...

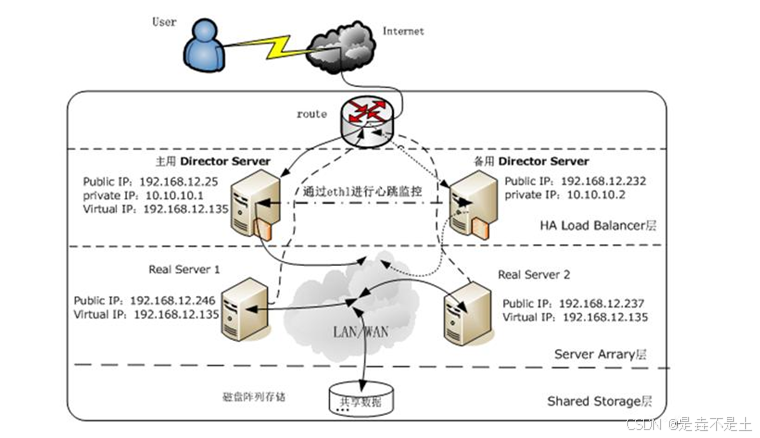

探秘高可用负载均衡集群:企业网络架构的稳固基石

目录 高可用负载均衡集群 一、集群的本质与核心价值 二、高可用集群与负载均衡集群的定义 高可用集群(HA Cluster) 负载均衡集群(Load Balance Cluster) 三.高可用与负载均衡的完美融合 四.…...

JAVA:ResponseBodyEmitter 实现异步流式推送的技术指南

1、简述 在许多场景下,我们希望后端能够以流式、实时的方式推送数据给前端,比如消息通知、日志实时展示、进度条更新等。Spring Boot 提供了 ResponseBodyEmitter 机制,可以让我们在 Controller 中异步地推送数据,从而实现实时流式输出。 样例代码:https://gitee.com/lh…...

CSS- 1.1 css选择器

本系列可作为前端学习系列的笔记,代码的运行环境是在HBuilder中,小编会将代码复制下来,大家复制下来就可以练习了,方便大家学习。 HTML系列文章 已经收录在前端专栏,有需要的宝宝们可以点击前端专栏查看! 系…...

ABP-Book Store Application中文讲解 - Part 2: The Book List Page

本章用于介绍如何创建Book List Page。 TBD 1. 汇总 ABP-Book Store Application中文讲解-汇总-CSDN博客 2. 前一章 ABP-Book Store Application中文讲解 - Part 1: Creating the Server Side 项目之间的引用关系。 目录 1. 多语言配置 1.1 zh-Hans.json 1.2 en.jso…...

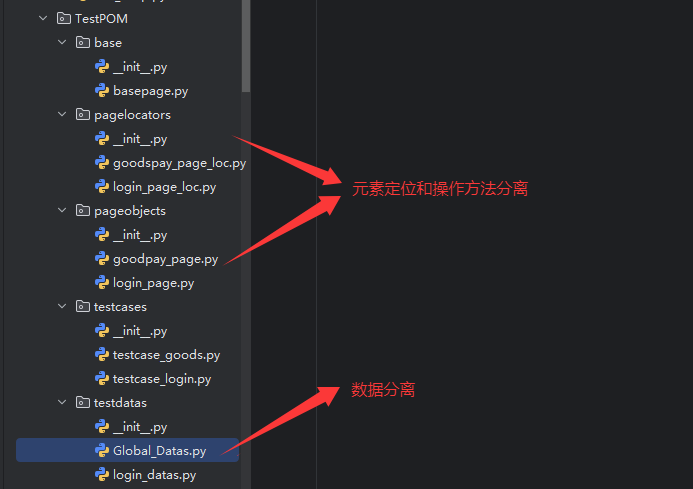

08 web 自动化之 PO 设计模式详解

文章目录 一、什么是 POM二、如何基于 POM 进行自动化框架架构?1、base 层封装2、pageobjects 层封装3、TestCases 层封装 三、元素和方法分离&数据分离1、哪些部分可以进行分离2、示例代码 四、总结 一、什么是 POM POM page object model 页面对象模型 WEB 自…...

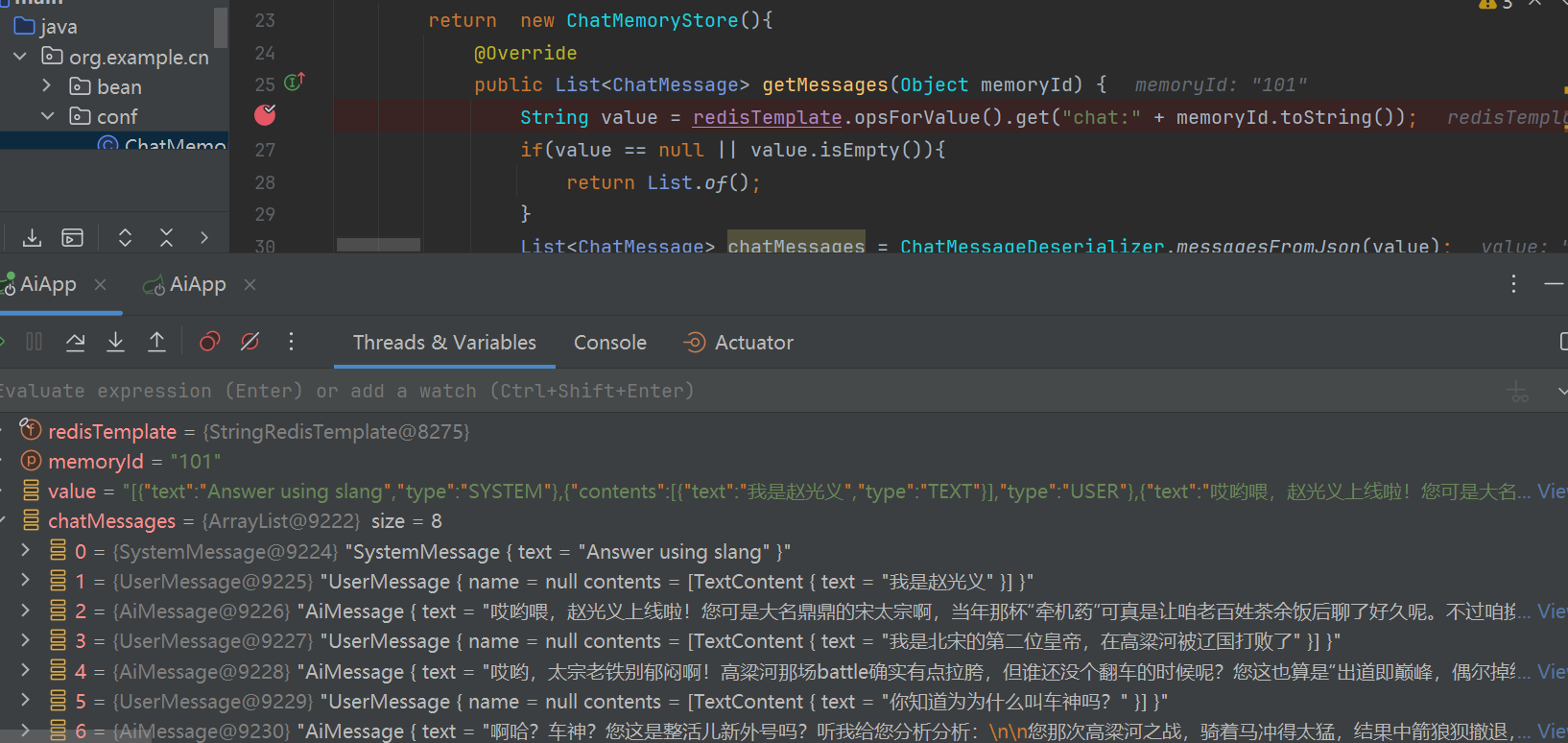

langchain4j集成QWen、Redis聊天记忆持久化

langchain4j实现聊天记忆默认是基于进程内存的方式,InMemoryChatMemoryStore是具体的实现了,是将聊天记录到一个map中,如果用户大的话,会造成内存溢出以及数据安全问题。位了解决这个问题 langchain4提供了ChatMemoryStore接口&am…...

WebGL图形编程实战【7】:变换流水线 × 坐标系与矩阵精讲

变换流水线 #mermaid-svg-Omabd9LSNCdIvWqB {font-family:"trebuchet ms",verdana,arial,sans-serif;font-size:16px;fill:#333;}#mermaid-svg-Omabd9LSNCdIvWqB .error-icon{fill:#552222;}#mermaid-svg-Omabd9LSNCdIvWqB .error-text{fill:#552222;stroke:#552222;…...

在Angular中使用Leaflet构建地图应用

Leaflet是一个用于创建地图的JavaScript库,它包含许多功能,并且非常适用于移动设备。 准备 nodejs: v20.15.0 npm: 10.7.0 angular: 19.2.10 创建一个地图应用工程 npx angular/cli new my-leaflet-app --stylecss --routingfalse --skip-tests提示 …...

鸿蒙next播放B站视频横屏后的问题

(此文讨论范围为b站视频链接,且不包括b站直播链接;android/iOS的webview播放b站视频完全没有这么多问题) 1、竖屏播放没问题 从一个竖屏页p1点击进入视频页p2,p2页仍为竖屏; p2页有一Web组件,…...

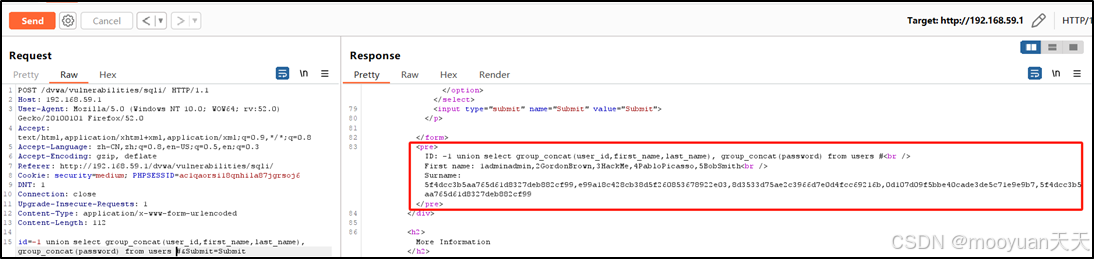

DVWA靶场通关笔记-SQL注入(SQL Injection Medium级别)

目录 一、SQL Injection 二、代码审计(Medium级别) 1、源码分析 (1)index.php (2)Medium.php 2、渗透思路 (1)SQL安全问题分析 (2)SQL渗透思路 三、…...

vue异步导入

vue的异步导入 大家开发vue的时候或多或少路由的异步导入 component: () >import(“/views/A_centerControl/intelligent-control/access-user-group”),当然这是路由页面,那么组件也是可以异步导入的 使用方式 组件的异步导入非常简单,主要是一个…...

【Redis】压缩列表

目录 1、背景2、压缩列表【1】底层结构【2】特性【3】优缺点 1、背景 ziplist(压缩列表)是redis中一种特殊编码的双向链表数据结构,主要用于存储小型列表和哈希表。它通过紧凑的内存布局和特殊的编码方式来节省内存空间。 2、压缩列表 【1…...

2025年,如何制作并部署一个完整的个人博客网站

欢迎访问我的个人博客网站:欢迎来到Turnin的个人博客 github开源地址:https://github.com/Re-restart/my_website 前言 2024年年初,从dji实习回来之后,我一直想着拓宽自己的知识边界。在那里我发现虽然大家不用java,…...

.NET 8 + Angular WebSocket 高并发性能优化

.NET 8 Angular WebSocket 高并发性能优化。 .NET 8 WebSocket 高并发性能优化 WebSocket 是一种全双工通信协议,允许客户端和服务端之间保持持久连接。在高并发场景下,优化 WebSocket 的性能至关重要。以下是针对 .NET 8 中 WebSocket 高并发性能优化…...

腾讯云运营开发 golang一面

redis为什么单线程会快 每秒10w吞吐量 io多路复用 一个文件描述符整体拷贝;调用epoll_ctl 单个传递 内核遍历文件描述符判断是否有事件发送;回调函数列表维护 修改有事件发送的socket为可读或可写,返回整个文件描述符;返回链…...

一个简单的静态页面

这个页面采用了现代化的 UI 设计,包括卡片式布局、微交互动画、分层设计和响应式结构。页面结构清晰,包含导航栏、英雄区域、功能介绍、产品特性、用户评价和联系表单等完整组件,可作为企业官网或产品介绍页面的基础模板。 登录后复制 <!D…...

使用 163 邮箱实现 Spring Boot 邮箱验证码登录

使用 163 邮箱实现 Spring Boot 邮箱验证码登录 本文将详细介绍如何使用网易 163 邮箱作为 SMTP 邮件服务器,实现 Spring Boot 项目中的邮件验证码发送功能,并解决常见配置报错问题。 一、为什么需要邮箱授权码? 出于安全考虑,大…...

多模态大语言模型arxiv论文略读(六十八)

Image-of-Thought Prompting for Visual Reasoning Refinement in Multimodal Large Language Models ➡️ 论文标题:Image-of-Thought Prompting for Visual Reasoning Refinement in Multimodal Large Language Models ➡️ 论文作者:Qiji Zhou, Ruoc…...

APS「多目标平衡算法」如何破解效率与弹性的永恒博弈

APS(高级计划与排程)系统作为企业智能制造的核心引擎,通过整合需求预测、产能规划、生产调度、物料管理及数据分析等模块,构建了覆盖产品全生产流程的“感知-决策-执行-优化”闭环体系。 精准需求预测 APS系统通过构建需求特征数…...

网张实验操作-防火墙+NAT

实验目的 了解防火墙(ENSP中的USG5500)域间转发策略配置、NAT(与路由器NAT配置命令不同)配置。 网络拓扑 两个防火墙连接分别连接一个内网,中间通过路由器连接。配置NAT之后,内网PC可以ping公网…...

)

Spring 中常见的属性注入方式(XML配置文件)

在 Spring 中,XML 配置属性注入。 以下是几种常见的属性注入方式及其对应的简单示例代码。 1. 构造器注入 构造器注入是指通过类的构造函数来设置依赖项。 示例类: public class MyService {private final MyRepository myRepository;public MyService(MyRepository myRe…...

让 - 艾里克・德布尔与斯普林格出版公司:科技变革下的出版业探索

在数字化浪潮席卷全球的当下,传统出版行业面临着前所未有的挑战与机遇。《对话 CTO,驾驭高科技浪潮》的第 10 章聚焦于让 - 艾里克・德布尔(Jean - Eric Debeure)及其所在的斯普林格出版公司(Springer Publishing Comp…...

【技巧】离线安装docker镜像的方法

回到目录 【技巧】离线安装docker镜像的方法 0. 为什么需要离线安装? 第一、 由于docker hub被墙,所以 拉取镜像需要配置国内镜像源 第二、有一些特殊行业服务器无法接入互联网,需要手工安装镜像 1. 可以正常拉取镜像服务器操作 服务器…...

05 web 自动化之 selenium 下拉鼠标键盘文件上传

文章目录 一、下拉框操作二、键盘操作三、鼠标操作四、日期控件五、滚动条操作六、文件上传七、定位windows窗口及窗口的元素总结:页面及元素常用操作 一、下拉框操作 from selenium.webdriver.support.select import Select import time from selenium.webdriver.…...

《Python星球日记》 第73天:情感分析与主题建模

名人说:路漫漫其修远兮,吾将上下而求索。—— 屈原《离骚》 创作者:Code_流苏(CSDN)(一个喜欢古诗词和编程的Coder😊) 目录 一、情感分析基础1. 情感分析的应用场景2. 基于规则的方法3. 基于深度学习的方法3.1 使用LSTM进行情感分析3.2 基于BERT的情感分析二、主题建模…...

数学复习笔记 10

前言 我觉得数学的高分乃至满分属于那些,聪明,坚韧,勇敢,细致的人。我非常惭愧自己不是这样的人,我在生活中发现了这样的同学,和他们交流的时候我常常感到汗流浃背,因为他们非常扎实的基础知识…...

07 web 自动化之 Unittest 应用:测试报告装饰器断言

文章目录 一、常见的第三方库结合 unittest 生产 html 格式测试报告1、HtmlTestRunner2、BeatifulReport 二、装饰器 unittest.skip 强制跳过&条件跳过三、unittest的常用断言方法 一、常见的第三方库结合 unittest 生产 html 格式测试报告 1、HtmlTestRunner 官网下载 …...

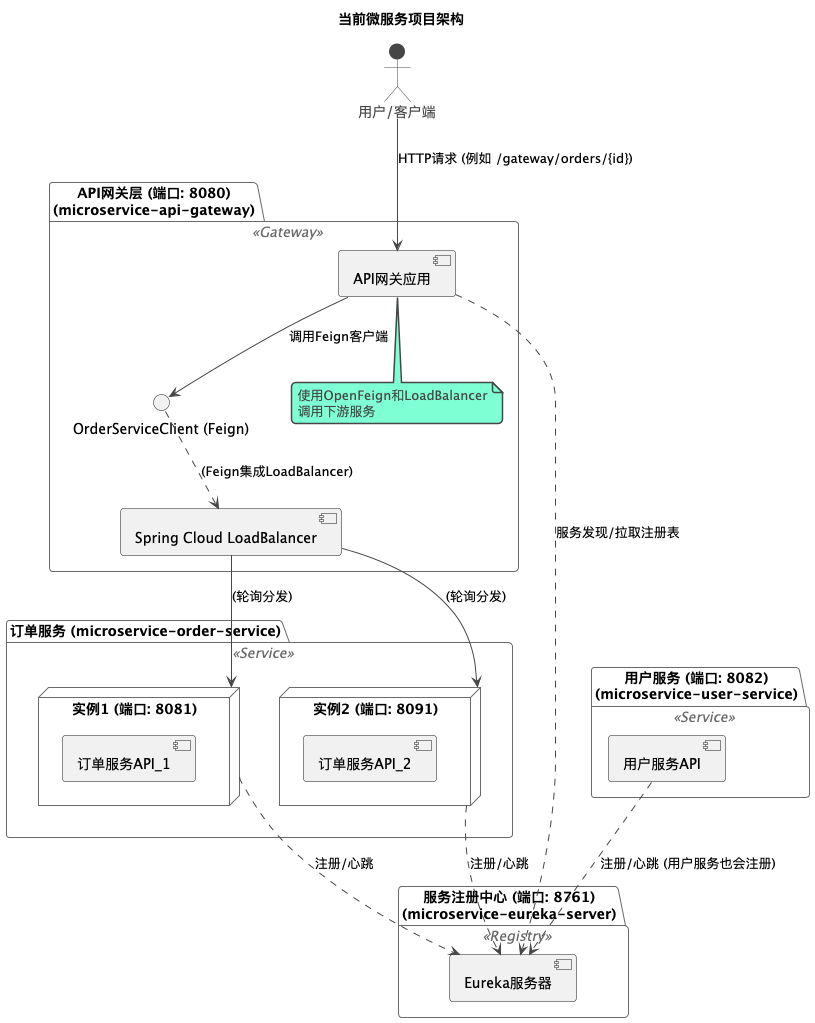

Spring Cloud探索之旅:从零搭建微服务雏形 (Eureka, LoadBalancer 与 OpenFeign实战)

引言 大家好!近期,我踏上了一段深入学习Spring Cloud构建微服务应用的旅程。我从项目初始化开始,逐步搭建了一个具备服务注册与发现、客户端负载均衡以及声明式服务调用功能的基础微服务系统。本文旨在记录这一阶段的核心学习内容与实践成果…...

9.2.高并发系统

目录 一、高并发系统设计原则 核心设计哲学 • CAP权衡:一致性、可用性、分区容错性的场景化选择 • BASE理论:最终一致性与柔性事务的落地策略 性能与扩展性准则 • 水平扩展 vs 垂直扩展:无状态服务与有状态服务的扩展策略 • 异步化设计…...