Xilinx 7Series\UltraScale 在线升级FLASH STARTUPE2和STARTUPE3使用

一、FPGA 在线升级

FPGA 在线升级FLASH时,一般是通过逻辑生成SPI接口操作FLASH,当然也可以通过其他SOC经FPGA操作FLASH,那么FPGA就要实现在启动后对FLASH的控制。

对于7Series FPGA,只有CCLK是专用引脚,SPI接口均为普通IO可直接通过约束解决,CCLK产生需通过STARTUPE2产生。

对于UltraScale 及UltraScale+系列,所有FLASH配置引脚(包含CCLK和SPI)均为专用引脚,在bit运行时需通过STARTUPE3产生。

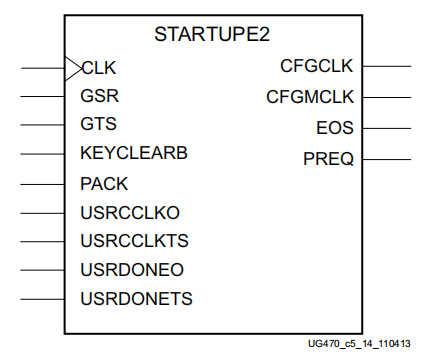

二、STARTUPE2

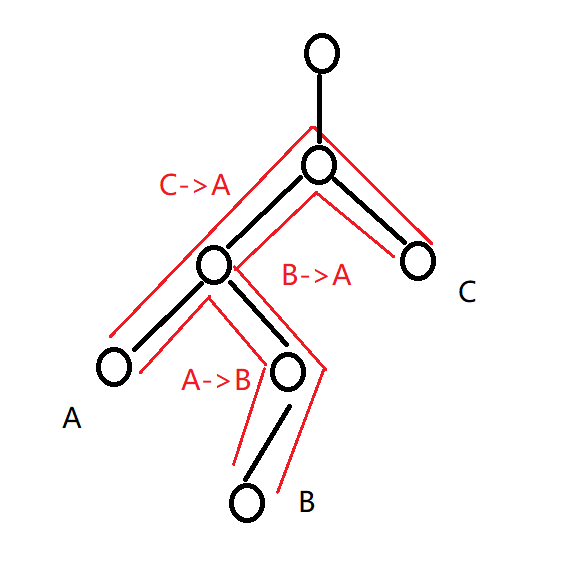

参考Xilinx ug470,STARTUPE2接口框图如下:

对SPI设置为X1,STARTUPE2例程如下:

STARTUPE2 #(.PROG_USR("FALSE"), // Activate program event security feature. Requires encrypted bitstreams..SIM_CCLK_FREQ(0.0) // Set the Configuration Clock Frequency(ns) for simulation.)STARTUPE2_spi (.CFGCLK(), // 1-bit output: Configuration main clock output.CFGMCLK( ), // 1-bit output: Configuration internal oscillator clock output.EOS(), // 1-bit output: Active high output signal indicating the End Of Startup..PREQ(), // 1-bit output: PROGRAM request to fabric output.CLK(1'b0), // 1-bit input: User start-up clock input.GSR(1'b0), // 1-bit input: Global Set/Reset input (GSR cannot be used for the port name).GTS(1'b0), // 1-bit input: Global 3-state input (GTS cannot be used for the port name).KEYCLEARB(1'b1), // 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM).PACK(1'b1), // 1-bit input: PROGRAM acknowledge input.USRCCLKO(i_SPI1_CLK), // 1-bit input: User CCLK input.USRCCLKTS(1'b0), // 1-bit input: User CCLK 3-state enable input.USRDONEO(1'b1), // 1-bit input: User DONE pin output control.USRDONETS(1'b1) // 1-bit input: User DONE 3-state enable output);assign o_QSPI_flash_MOSI = i_SPI1_MOSI;

assign o_QSPI_flash_CSB = i_SPI1_CSB;

assing o_SPI1_MISO = i_QSPI_flash_MISO;

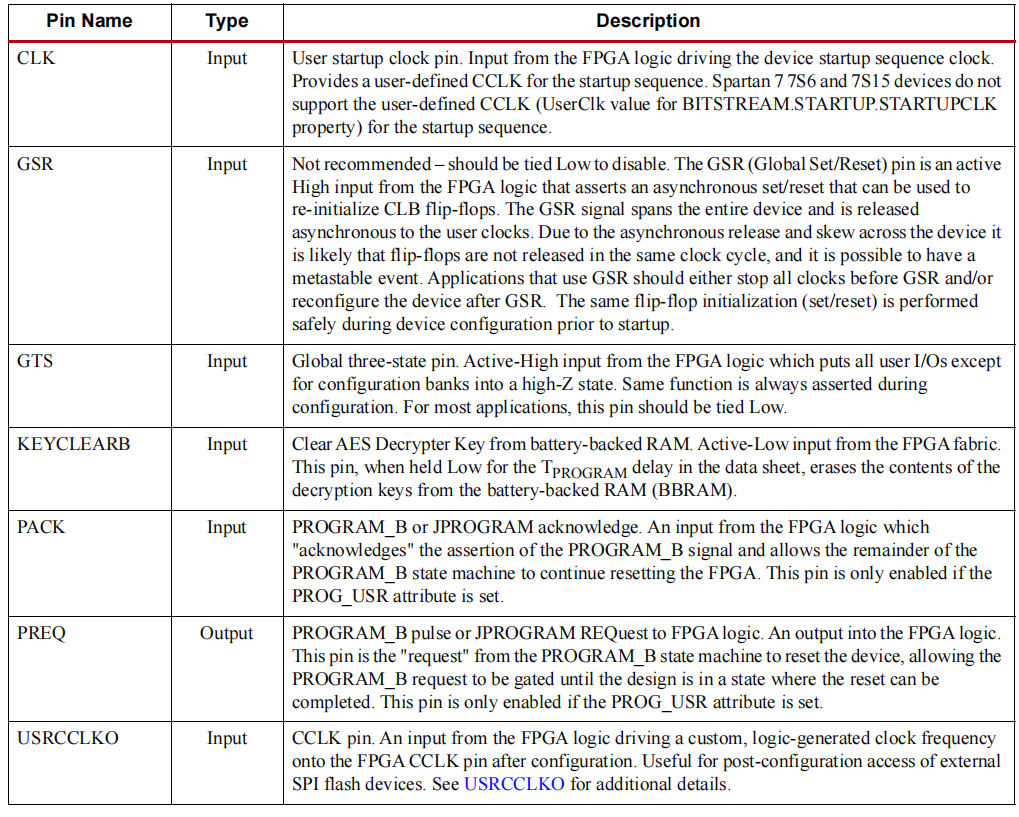

其中:

(1)o_QSPI_flash_MOSI、o_QSPI_flash_CSB、i_QSPI_flash_MISO、o_QSPI_flash_SCLK为连接到FLASH的信号,i_SPI1_MOSI、i_SPI1_CSB、o_SPI1_MISO、i_SPI1_CLK为FPGA内部产生或其他SOC产生的配置FLASH SPI信号,FPGA通过STARTUPE2 和逻辑完成这些信号和FLASH的连接;

(2)STARTUPE2 中USRCCLKO为输入,USRCCLKTS为三态控制信号,当USRCCLKTS=0,时USRCCLKO输出到CCLK,用于配置FLASH,因CCLK为专用管脚,故代码中不需要CCLK的描述;

(3)USRDONETS的控制与USRCCLKTS类似,USRDONETS=0,USRDONEO直接输出到FPGA的配置DONE引脚

(4)CFGCLK为输出的配置时钟,FPGA可用该时钟产生SPI逻辑,也可用其他时钟信号

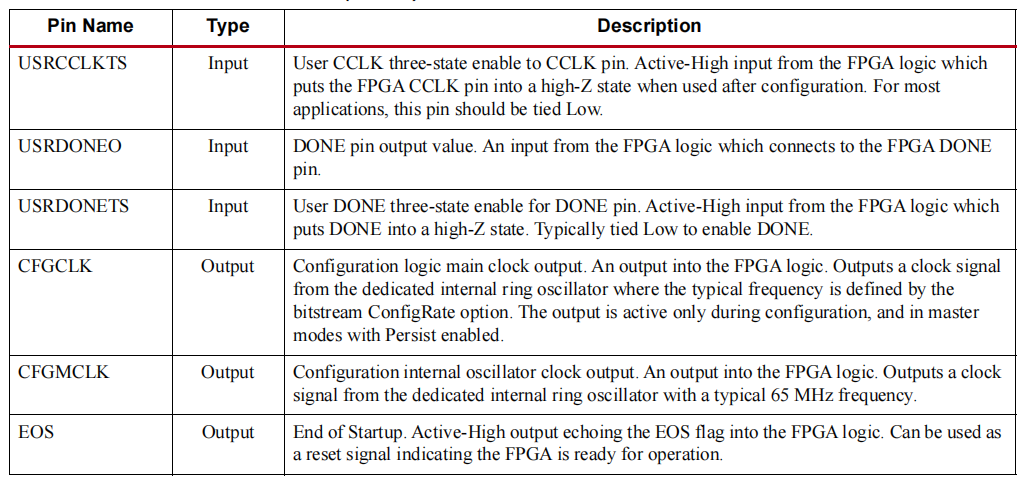

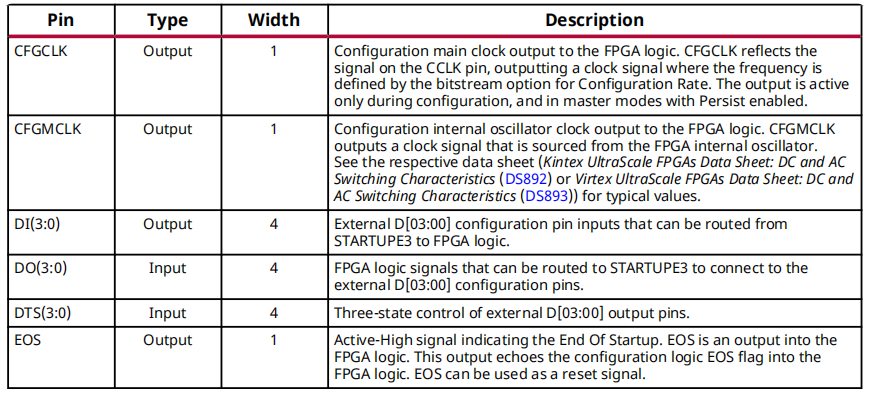

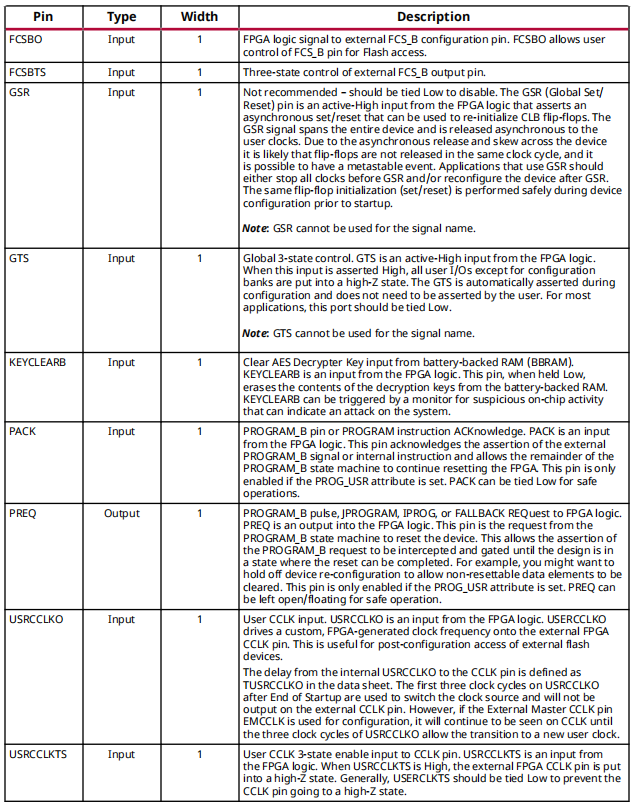

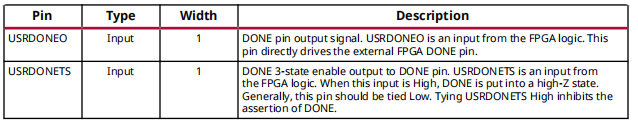

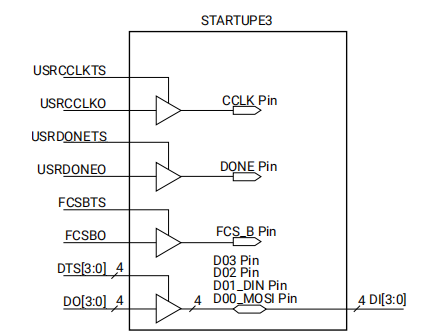

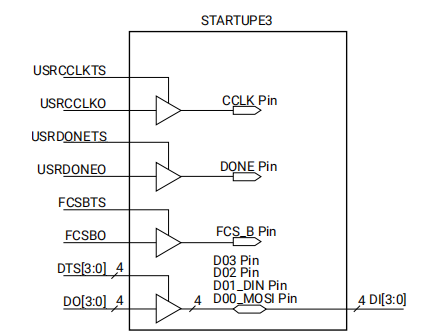

三、STARTUPE3

参考Xilinx ug570,STARTUPE3接口框图如下:

对SPI设置为X1,STARTUPE3例程如下:

wire [3:0] QSPI_in_null;STARTUPE3 #(.PROG_USR("FALSE"), // Activate program event security feature. Requires encrypted bitstreams..SIM_CCLK_FREQ(0.0) // Set the Configuration Clock Frequency (ns) for simulation.)STARTUPE3_inst (.CFGCLK(), // 1-bit output: Configuration main clock output..CFGMCLK(), // 1-bit output: Configuration internal oscillator clock output..DI({QSPI_in_null[3:2],i_QSPI_flash_MISO,QSPI_in_null[0]}), // 4-bit output: Allow receiving on the D input pin..EOS (), // 1-bit output: Active-High output signal indicating the End Of Startup..PREQ(), // 1-bit output: PROGRAM request to fabric output..DO({3'b111,o_QSPI_flash_MOSI}), // 4-bit input: Allows control of the D pin output..DTS(4'b0010), // 4-bit input: Allows tristate of the D pin..FCSBO(o_QSPI_flash_CSB), // 1-bit input: Controls the FCS_B pin for flash access..FCSBTS(1'b0), // 1-bit input: Tristate the FCS_B pin..GSR(1'b0), // 1-bit input: Global Set/Reset input (GSR cannot be used for the port)..GTS(1'b0), // 1-bit input: Global 3-state input (GTS cannot be used for the port name)..KEYCLEARB(1'b1 ), // 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM)..PACK(1'b1), // 1-bit input: PROGRAM acknowledge input..USRCCLKO(o_QSPI_flash_SCLK), // 1-bit input: User CCLK input..USRCCLKTS(1'b0), // 1-bit input: User CCLK 3-state enable input..USRDONEO(1'b1), // 1-bit input: User DONE pin output control..USRDONETS(1'b1) // 1-bit input: User DONE 3-state enable output.);

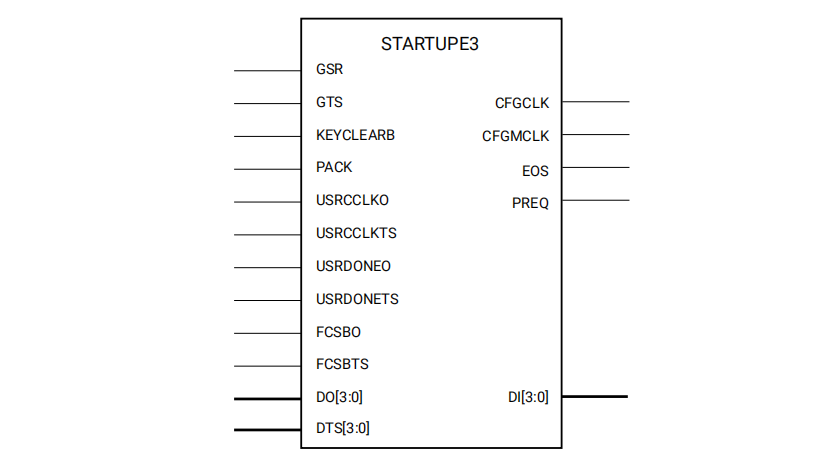

其中:

(1)o_QSPI_flash_MOSI、o_QSPI_flash_CSB、i_QSPI_flash_MISO、o_QSPI_flash_SCLK为FPGA内部产生或其他SOC产生的配置FLASH SPI信号,FPGA通过STARTUPE3 和逻辑完成这些信号和FLASH的连接,应CCLK和SPI均为专用管脚,故代码中不需要CCLK的描述;

(2)STARTUPE3 中USRCCLKO为输入,USRCCLKTS为三态控制信号,当USRCCLKTS=0,时USRCCLKO输出到CCLK,用于配置FLASH

(3)DO为FPGA输出到FLASH的QSPI 数据信号,例程采用了SPIx1,仅D0 MOSI有效,D3 D2设置为1,falsh WP_B和HOLD_B信号无效;

(4)DI为FLASH输入到FPGA的QSPI 数据信号,例程采用了SPIx1,仅D1 MISO有效;

(5)DTS为数据信号方向,例程采用了SPIx1,所以D0为MOSI,D1为MISO,其他为WP和HOLD信号,所以DTS设置为4’b0010

(4)FCSBO为FPGA输出到FLASH的FCSBO信号,FCSBTS=0表示由FPGA逻辑输出o_QSPI_flash_CSB到FLASH的CSB

(5)DTS为数据信号方向,例程采用了SPIx1,所以D0为MOSI,D1为MISO,其他为WP和HOLD信号,所以DTS设置为4’b0010

(6)USRDONETS的控制与USRCCLKTS类似,USRDONETS=0,USRDONEO直接输出到FPGA的配置DONE引脚

(7)CFGCLK为输出的配置时钟,FPGA可用该时钟产生SPI逻辑,也可用其他时钟信号

STARTUPE3有许多三态控制,如下图所示,当三态控制信号为0时,信号按下图中反向传输,为1是反向。

参考文件

ug570-ultrascale-configuration

ug470-ultrascale-configuration

相关文章:

Xilinx 7Series\UltraScale 在线升级FLASH STARTUPE2和STARTUPE3使用

一、FPGA 在线升级 FPGA 在线升级FLASH时,一般是通过逻辑生成SPI接口操作FLASH,当然也可以通过其他SOC经FPGA操作FLASH,那么FPGA就要实现在启动后对FLASH的控制。 对于7Series FPGA,只有CCLK是专用引脚,SPI接口均为普…...

数字孪生驱动的离散制造智能升级:架构设计与工程实践

针对离散制造行业多品种、小批量的生产特性,本文提出一种基于数字孪生的智能制造解决方案。以某国家级智能制造试点示范项目为载体,构建"云-边-端"协同的数字孪生系统,实现设备综合效率(OEE)提升28.7%、订单…...

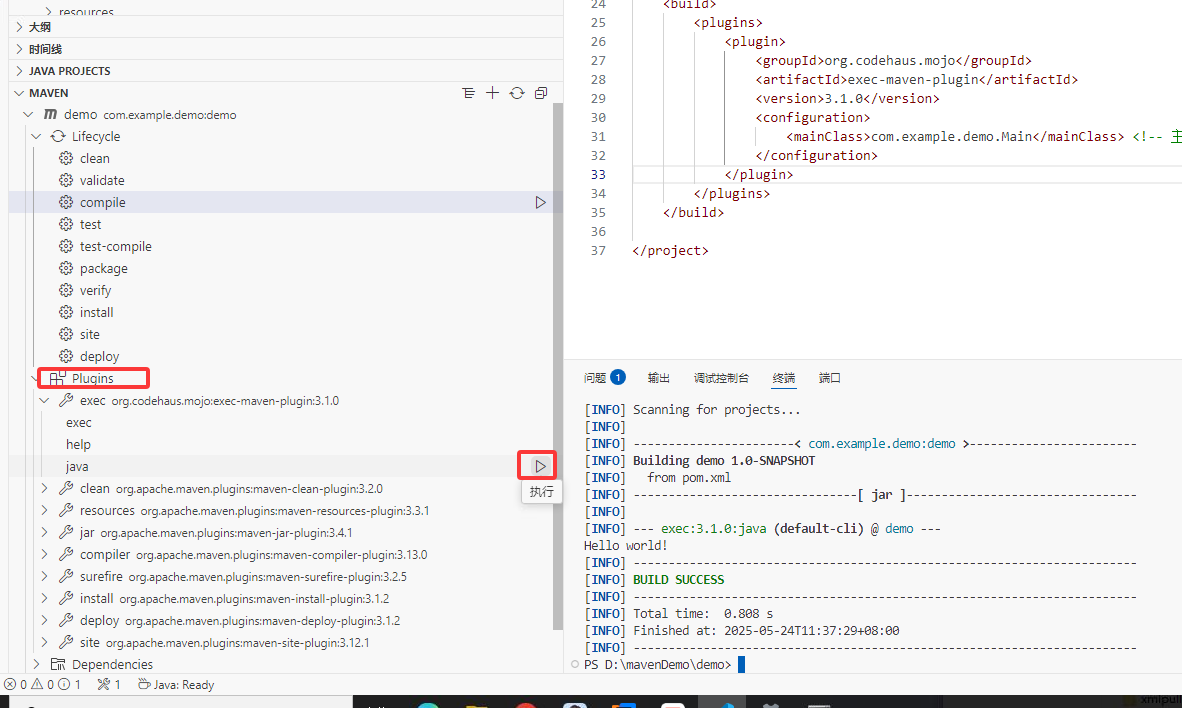

9.4在 VS Code 中配置 Maven

在 VS Code 中配置 Maven 需要完成 Maven 环境安装 一、安装 Maven(如果未安装) 下载 Maven 访问 Apache Maven 官网,下载最新版本的 Maven(如apache-maven-3.9.9-bin.zip)。 解压文件 将下载的 ZIP 文件解压到本地目…...

mmaction2——tools文件夹下

build_rawframes.py 用法示例 python tools/data/build_rawframes.py data/videos data/frames --task rgb --level 2 --ext mp4 --use-opencv --num-worker 8总结: 只需要 RGB 帧,推荐 --use-opencv,简单高效,无需额外依赖。 …...

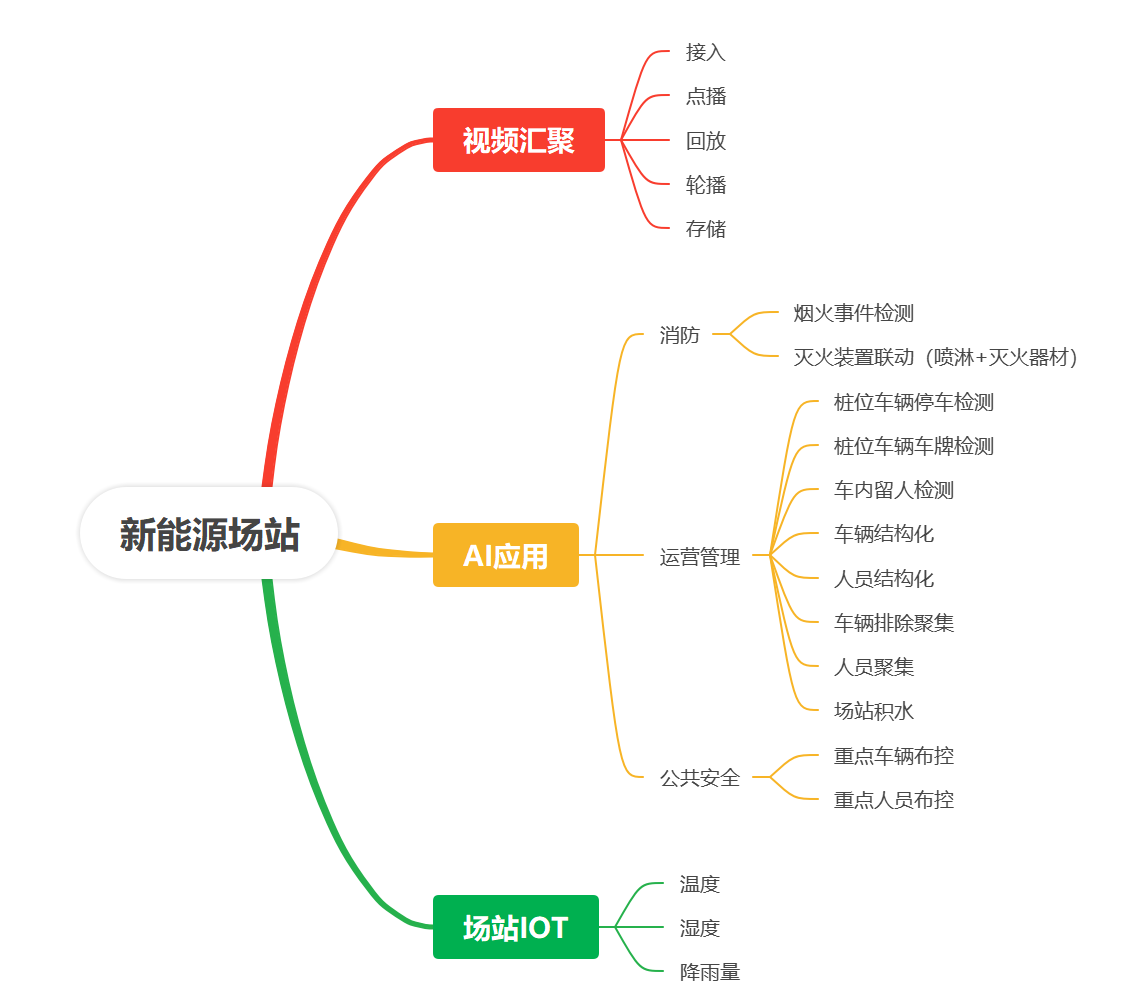

新能源汽车充电桩资源如何利用资源高效配置?

新能源汽车充电桩资源的高效配置是实现绿色交通转型的关键环节。随着新能源汽车保有量的快速增长,充电基础设施的供需矛盾日益凸显。如何优化充电桩资源布局、提升使用效率、平衡不同场景需求,成为当前亟待解决的问题。以下是几点关于充电桩资源高效配置…...

python 程序实现了毫米波大规模MIMO系统中的信道估计对比实验

python 程序实现了毫米波大规模MIMO系统中的信道估计对比实验 import numpy as np import matplotlib.pyplot as plt import tensorflow as tf from tensorflow.keras.models import Sequential, Model from tensorflow.keras.layers...

NTFS0x90属性和0xa0属性和0xb0属性的一一对应关系是index_entry中的index_node中VCN和runlist和bitmap

第一部分: 0: kd> dt _FILE_RECORD_SEGMENT_HEADER 0xc1241400 Ntfs!_FILE_RECORD_SEGMENT_HEADER 0x000 MultiSectorHeader : _MULTI_SECTOR_HEADER 0x008 Lsn : _LARGE_INTEGER 0x80e74aa 0x010 SequenceNumber : 5 0x012 Referen…...

PDF 编辑批量拆分合并OCR 识别

各位办公小能手们!你们有没有过被PDF文件折磨得死去活来的经历?反正我是有,每次要编辑PDF,那叫一个费劲啊!不过呢,今天我要给大家介绍一款神器——WPS PDF to Word,有了它,PDF编辑那…...

LeetCode --- 450周赛

题目列表 3550. 数位和等于下标的最小下标 3551. 数位和排序需要的最小交换次数 3552. 网格传送门旅游 3553. 包含给定路径的最小带权子树 II 一、数位和等于下标的最小下标 直接模拟计算数位和即可,代码如下 // C class Solution { public:int smallestIndex(ve…...

SpringBoot中消息转换器的选择

SpringBoot返回xml-CSDN博客 是返回JSON 还是XML 是由内容协商机制确认的,SpringBoot为了开发便利性,如果我没有该消息转换器,默认就返回了JSON,如果需要XML那么,引入 <dependency><groupId>com.fasterxml.jackson.dataformat</groupId><artifactId>…...

前端初学者入门指南:HTML5与CSS3核心知识详解)

(初级)前端初学者入门指南:HTML5与CSS3核心知识详解

对于前端初学者来说,掌握HTML5和CSS3的基础知识是构建现代化网页的第一步。本文将围绕语义化标签、多媒体嵌入、盒模型、Flexbox布局和Grid布局五大核心知识点展开,通过代码示例和详细解析帮助大家快速上手。 一、HTML5:从结构到交互的革新 …...

基于点标注的弱监督目标检测方法研究

摘要 在计算机视觉领域,目标检测需要大量精准标注数据,但人工标注成本高昂。弱监督目标检测通过低成本标注训练模型,成为近年研究热点。本文提出一种基于点标注的弱监督目标检测算法,仅需在图像中物体中心点标注,即可高…...

【RichTextEditor】 【分析2】RichTextEditor设置文字内容背景色

【RichTextEditor】 【分析2】RichTextEditor设置文字内容背景色 都说AI Coder的Cursor很牛,也付费用了, 但这个背景色,搞了一天也没改过来。 最后,让它分析该控件的层次结构及文本内容显示的位置。 然后,搞定&#…...

超越OpenAI CodeX的软件工程智能体:Jules

目前AI编码代理(coding agent)领域正迅速崛起,Google推出了一款名为Jules的非同步编码代理(asynchronous coding agent),主要针对专业开发者,与传统在开发环境中直接辅助编码的Cursor或Windsurf…...

Qt实战教程:设计并实现一个结构清晰、功能完整的桌面应用

概述 本文以文本编辑器项目作为示例,文本编辑器是一个非常适合新手入门的经典项目。它具备了桌面应用开发中的核心要素: 窗口管理菜单栏和工具栏文件操作(打开、保存)多文档支持(可选)国际化支持(多语言)插件系统(进阶扩展)通过这个项目,你将学习到如何使用Qt进行桌…...

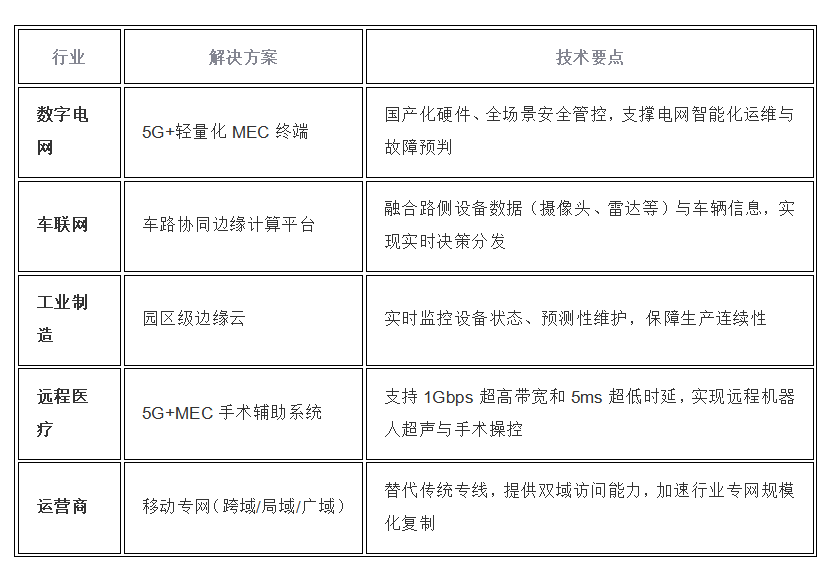

轻量化MEC终端 特点

MEC(多接入边缘计算)解决方案通过将计算能力下沉至网络边缘,结合5G网络特性,已在多个行业实现低延迟、高可靠、高安全的应用部署。以下从技术架构、核心优势及典型场景三方面进行总结: 一、技术架构 分层设计 MEC架…...

NIST提出新型安全指标:识别潜在被利用漏洞

美国国家标准与技术研究院(NIST)近日公布了一项突破性的安全指标,旨在评估哪些软件漏洞可能已被利用——即使相关组织尚未察觉。 这项由前NIST专家Peter Mell和网络安全与基础设施安全局(CISA)Jonathan Spring共同完成…...

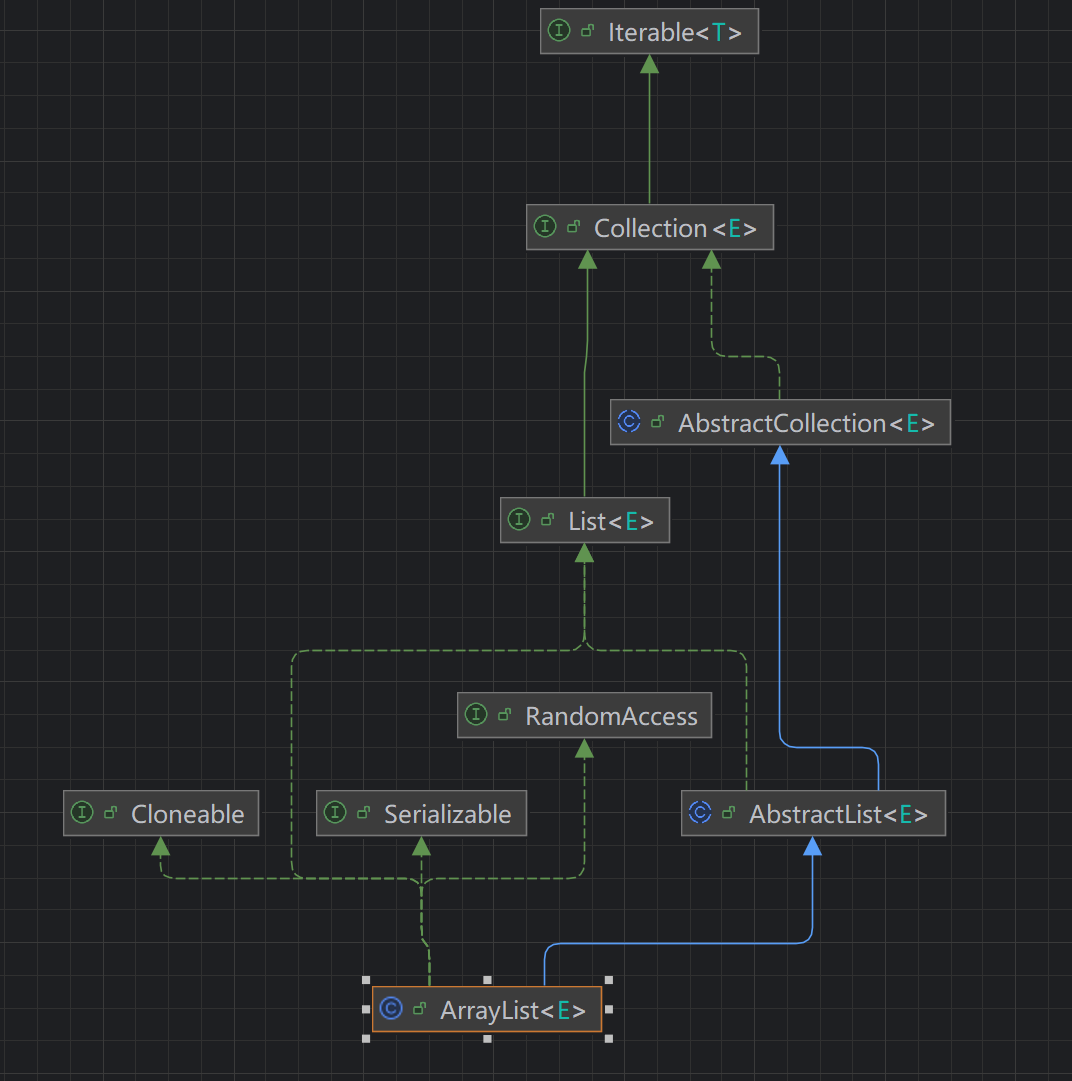

List介绍

什么是List 在集合框架中,List是一个接口,继承自Collection Collection也是一个接口,该接口中规范了后序容器中常用的一些方法 Iterable也是一个接口,表示实现该接口的类是可以逐个元素进行遍历的,具体如下࿱…...

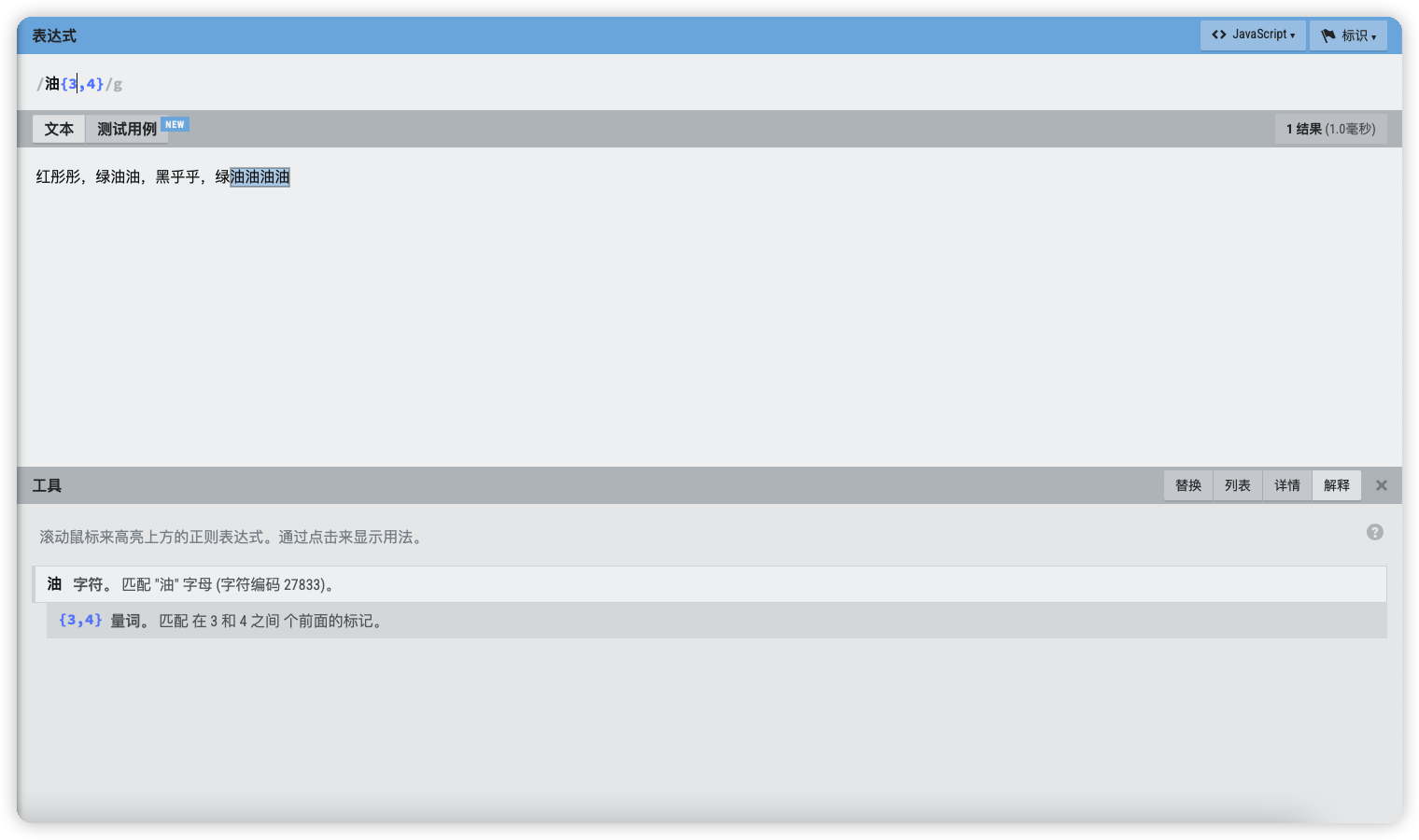

正则表达式全解:一文学会正则表达式【附在线正则表达式练习网站】

1.正则表达式的作用 案例演示 先给大家看一个例子,在以下文本中存储了一些职位信息: Python3 高级开发工程师 上海互教教育科技有限公司上海-浦东新区2万/月02-18满员 测试开发工程师(C++/python) 上海墨鹍数码科技有限公司上海-浦东新区2.5万/每月02-18未满员 Python3 …...

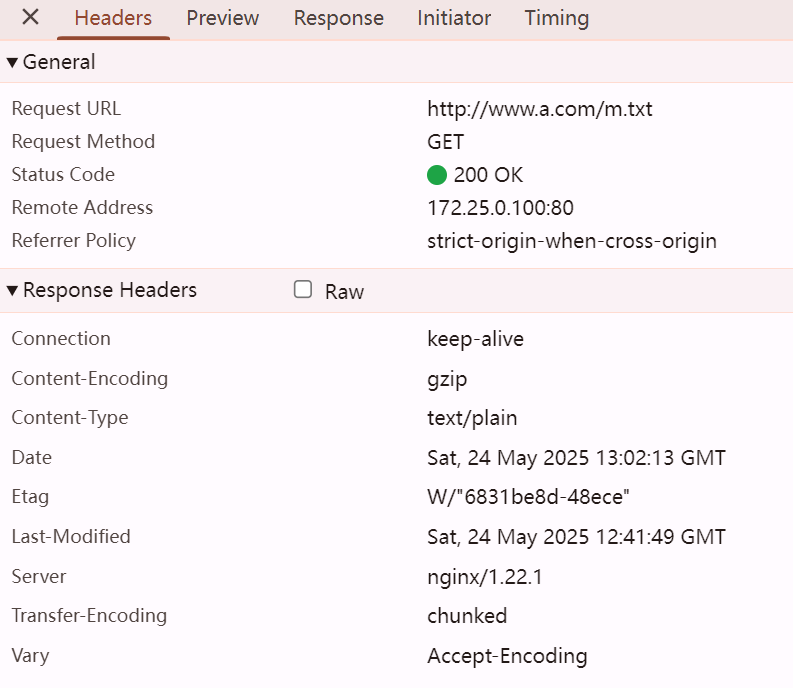

Nginx-详解(二)

nginx 常见模块 第三方模块是对nginx 的功能扩展,第三方模块需要在编译安装nginx 的时候使用参数-- add-modulePATH指定路径添加,有的模块是由公司的开发人员针对业务需求定制 开发的,有的模块是开源爱好者开发好之后上传到github进行开源的…...

解决 IntelliJ IDEA 配置文件中文被转义问题

在使用 IntelliJ IDEA 进行开发时,我们经常需要编辑各种配置文件(如 .properties、.xml、.json 等)。然而,许多开发者都遇到过这样的困扰:配置文件中的中文内容被自动转义成了 Unicode 编码,显示为类似 \u4…...

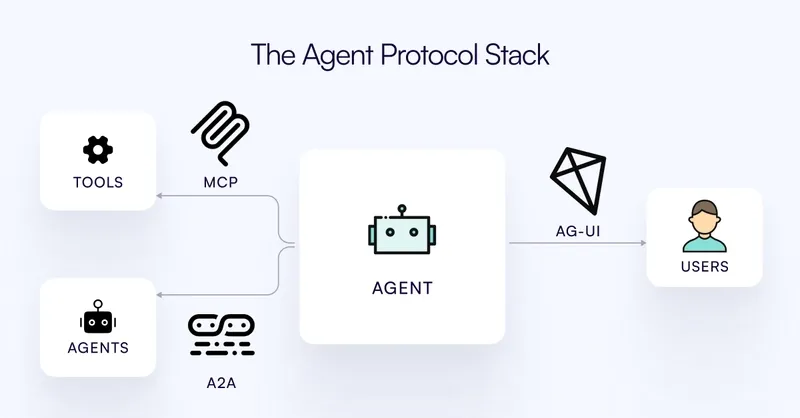

MCP、MCPHub、A2A、AG-UI概述

MCP Model Context Protocol,模型上下文协议,Anthropic于2024年开源的标准协议,旨在统一AI模型与数据源的交互方式,提升数据访问的便捷性和可靠性,提供标准化的工具调用、资源管理和提示词功能。 MCP的基本定义&…...

)

计算机视觉与深度学习 | Python实现CEEMDAN-ISOS-VMD-GRU-ARIMA时间序列预测(完整源码和数据)

以下是结合CEEMDAN、ISOS-VMD、GRU和ARIMA的时间序列预测的Python完整实现方案。本方案包含完整的代码、数据生成逻辑和实现细节说明。 完整代码实现 import numpy as np import pandas as pd from PyEMD import CEEMDAN from vmdpy import VMD from scipy.optimize import di…...

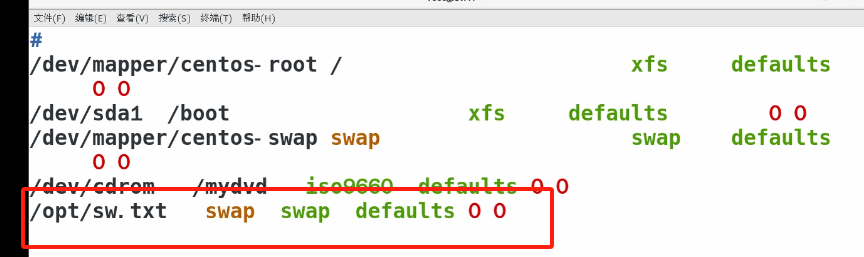

[Linux]磁盘分区及swap交换空间

linux磁盘分区 计算机容量单位:一般用B,KB,MB,GB,TB,PB,EB,ZB,YB,BB来表示。 它们之间的关系是: 1KB (Kilobyte 千字节)1024B, 1MB (Megabyte 兆…...

JAVA面向对象——对象和类的基本语法

JAVA面向对象——对象和类的基本语法 一、面向对象编程基础 1. 程序中的数据存储方式 基本类型:变量(如 int max 15;)。数据结构:数组(一维/二维)、对象(特殊数据结构,用于存储复…...

Linux常见指令合集+知识点

Linux有一条设计理念:Linux中一切皆文件;这样的设计理念让Linux可以用一种统一的方式对Linux中的不同文件/设备进行管理;(也就是键盘、显示器等在Linux中也算文件) 文件内容属性,指令一般都是对文件进行操…...

nginx 基于IP和用户的访问

nginx的下载 yum install nginx.x86_64 -y 启动服务 systemctl enable --now nginx.service 查看服务目录 [rootwebserver ~]# rpm -ql nginx /usr/bin/nginx-upgrade /usr/lib/systemd/system/nginx.service /usr/share/man/man3/nginx.3pm.gz /usr/share/man/man8/nginx…...

【Linux】系统程序−进度条

文章目录 一、准备知识1.回车与换行1.1 回车1.2 换行 2. 行缓冲区3. 倒计时程序 二、进度条程序1. 版本1 一、准备知识 在讲解进度条之前,先讲解几个概念 1.回车与换行 1.1 回车 回车:\r 作用:将光标移动到当前行的行首(水平回…...

Axure应用交互设计:动态面板嵌套实现超强体验感菜单表头

亲爱的小伙伴,在您浏览之前,烦请关注一下,在此深表感谢!如有帮助请订阅专栏! Axure产品经理精品视频课已登录CSDN可点击学习https://edu.csdn.net/course/detail/40420 课程主题:动态面板嵌套 主要内容:利用动态面板多层嵌套实现菜单表头 应用场景:广泛应用于表单表…...

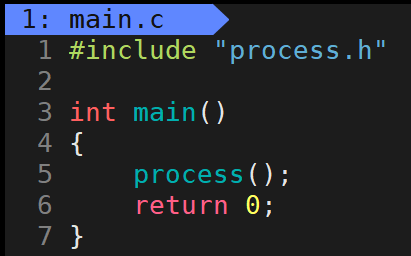

Linux(6)——第一个小程序(进度条)

目录 一、行缓冲区的概念 二、\r与\n 三、进度条代码书写与展示 1.如何表示进度条是在加载的 2.整体框架 3.书写 3.1makefile: 3.2process.h: 3.3process.c: 3.4main.c: 3.5美化 一、行缓冲区的概念 首先,我们来见一见行缓冲区,…...