FPGA纯verilog实现MIPI-DSI视频编码输出,提供工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- 我这里已有的 MIPI 编解码方案

- 3、设计思路框架

- 工程设计原理框图

- FPGA内部彩条

- RGB数据位宽转换

- RGB数据缓存

- MIPI-DSI协议层编码

- MIPI-DPHY物理层串化

- MIPI-LVDS显示屏

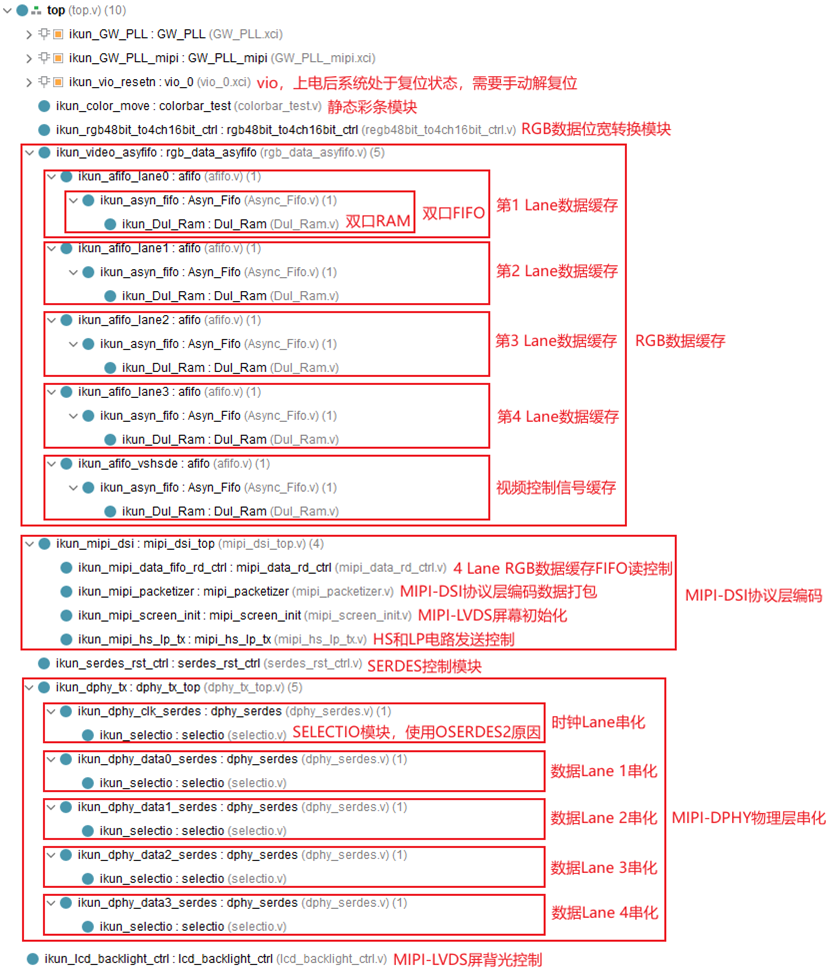

- 工程源码架构

- 4、工程源码1详解:Kintex7-325T版本

- 5、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 6、上板调试验证并演示

- 准备工作

- VIO解复位

- MIPI-DSI视频编码输出演示

- 7、工程源码获取

FPGA纯verilog实现MIPI-DSI视频编码输出,提供工程源码和技术支持

1、前言

FPGA实现MIPI视频编码现状:

MIPI视频编码分为DSI和D-PHY两大部分,其中D-PHY属于物理层,依托硬件,灵活性不高,方案不多;DSI属于协议层,依托代码,灵活性很高,方案很多;所以只要实现了D-PHY,MIPI-DSI解码其实就很灵活了;第一种D-PHY方案是使用FPGA内部资源实现,该方案优点是设计简单,缺点是硬件成本较高;第二种是使用专用的D-PHY芯片,比如MC20901,该方案优点是设计简单,缺点是硬件成本较高;本设计使用Xilinx系列FPGA纯verilog代码实现MIPI-DSI视频编码输出;

工程概述

本设计使用Xilinx 7系列FPGA纯verilog代码实现MIPI-DSI视频编码输出;首先FPGA内部生成1个1024x600的静态彩条视频作为输入源,彩条视频为Native接口;然后彩条视频送入视频位宽转换模块实现位宽转换功能,将输入的24bit像素数据转换为4路16bit像素数据,以便于后续模块生成4 Lane MIPI数据;然后4 Lane视频送入异步FIFO缓存模块,以实现数据跨时钟域转换;然后4 Lane视频送入MIPI-DSI协议层编码模块,按照DSI协议将输入的RGB视频进行编码处理,然后输出HS电路数据和LP电路数据;然后MIPI-DSI数据送入MIPI-DPHY物理层串化模块,将输入的4 Lane并行MIPI-DSI数据串化为4 Lane高速串行的差分信号,模块依托Xilinx官方的OSERDESE2和OBUFTDS实现串化和单端转差分处理;中途还要对MIPI-LVDS显示屏做初始化操作;最后MIPI-DSI编码视频直接送MIPI-LVDS显示屏显示即可;针对市场主流需求,本设计提供1套vivado工程源码,具体如下:

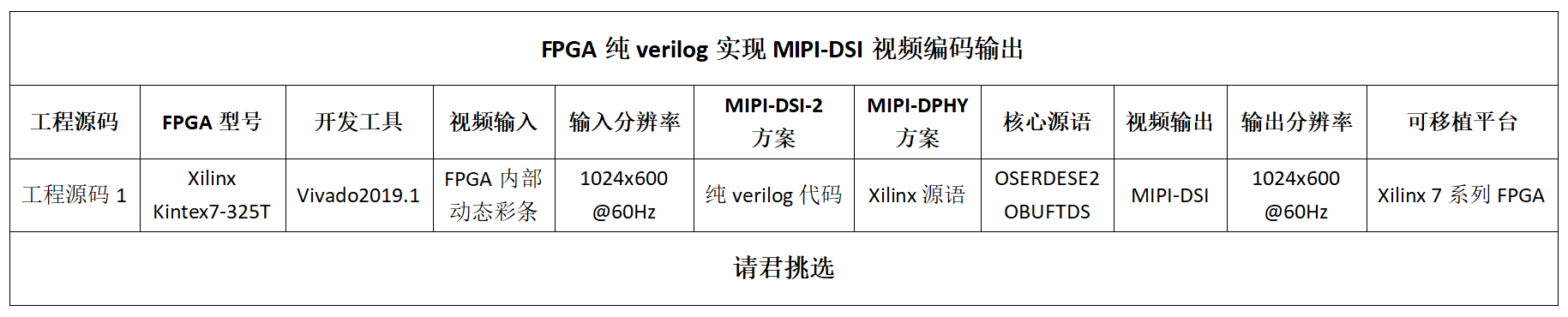

现对上述1套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为高云Kintex7-325T-xc7k325tffg900-2;首先FPGA内部生成1个1024x600的静态彩条视频作为输入源,彩条视频为Native接口;然后彩条视频送入视频位宽转换模块实现位宽转换功能,将输入的24bit像素数据转换为4路16bit像素数据,以便于后续模块生成4 Lane MIPI数据;然后4 Lane视频送入异步FIFO缓存模块,以实现数据跨时钟域转换;然后4 Lane视频送入MIPI-DSI协议层编码模块,按照DSI协议将输入的RGB视频进行编码处理,然后输出HS电路数据和LP电路数据;然后MIPI-DSI数据送入MIPI-DPHY物理层串化模块,将输入的4 Lane并行MIPI-DSI数据串化为4 Lane高速串行的差分信号,模块依托Xilinx官方的OSERDESE2和OBUFTDS实现串化和单端转差分处理;中途还要对MIPI-LVDS显示屏做初始化操作;最后MIPI-DSI编码视频直接送MIPI-LVDS显示屏显示即可,输出分辨率为1024x600@60Hz,MIPI-4 Lane;本工程适用于Xilinx 7系列FPGA实现MIPI-DSI视频编码输出应用;

本文详细描述了FPGA纯verilog实现MIPI-DSI视频编码输出的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网以及其他开源免费获取渠道等等),若大佬们觉得有所冒犯,请私信批评教育;部分模块源码转载自上述网络,版权归原作者所有,如有侵权请联系我们删除;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

我这里已有的 MIPI 编解码方案

我这里目前已有丰富的基于FPGA的MIPI编解码方案,主要是MIPI解码的,既有纯vhdl实现的MIPI解码,也有调用Xilinx官方IP实现的MIPI解码,既有2line的MIPI解码,也有4line的MIPI解码,既有4K分辨率的MIPI解码,也有小到720P分辨率的MIPI解码,既有基于Xilinx平台FPGA的MIPI解码也有基于Altera平台FPGA的MIPI解码,还有基于Lattice平台FPGA的MIPI解码,后续还将继续推出更过国产FPGA的MIPI解码方案,毕竟目前国产化方案才是未来主流,后续也将推出更多MIPI编码的DSI方案,努力将FPGA的MIPI编解码方案做成白菜价。。。

基于此,我专门建了一个MIPI编解码的专栏,并将MIPI编解码的博客都放到了专栏里整理,对FPGA编解码MIPI有项目需求或学习兴趣的兄弟可以去我的专栏看看,专栏地址如下:

点击直接前往专栏

3、设计思路框架

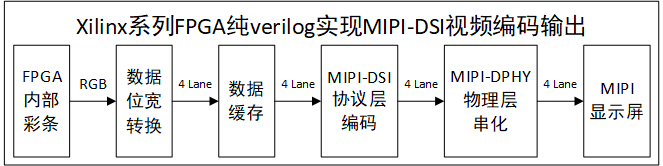

工程设计原理框图

工程设计原理框图如下:

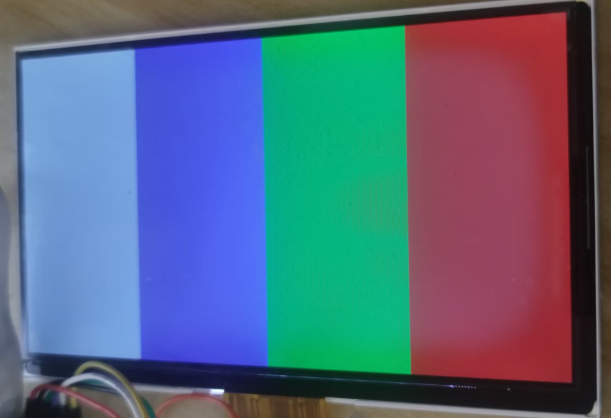

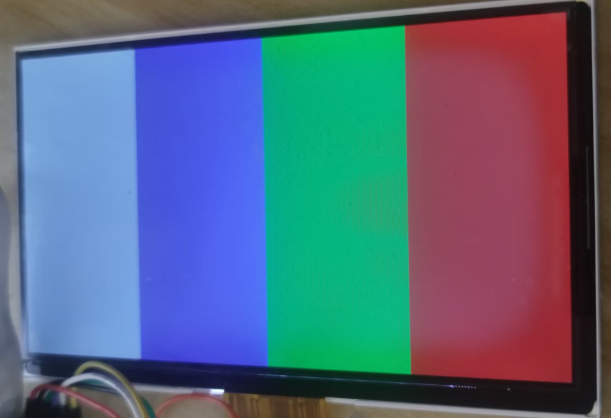

FPGA内部彩条

首先FPGA内部生成1个1024x600@60Hz的静态彩条视频作为输入源,彩条视频为Native接口,即常规的行同步信号、场同步信号、数据有效信号、像素数据等;FPGA内部彩条设计为4阶白、蓝、绿、红色彩条,如下:

FPGA内部彩条代码架构如下:

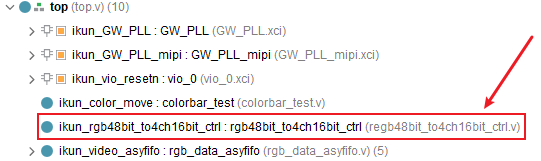

RGB数据位宽转换

然后彩条视频送入视频位宽转换模块实现位宽转换功能,将输入的24bit像素数据转换为4路16bit像素数据,以便于后续模块生成4 Lane MIPI数据;需要注意的是,24bit的彩条视频需要拓展至48bit,直接将单路的24bit RGB数据复制为2路即可;RGB数据位宽转换代码架构如下:

RGB数据缓存

然后4 Lane视频送入异步FIFO缓存模块,以实现数据跨时钟域转换;数据缓存使用纯verilog代码实现的异步FIFO实现;RGB数据缓存代码架构如下:

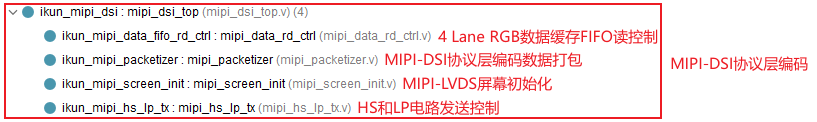

MIPI-DSI协议层编码

然后4 Lane视频送入异步FIFO缓存模块,以实现数据跨时钟域转换;然后4 Lane视频送入MIPI-DSI协议层编码模块,按照DSI协议将输入的RGB视频进行编码处理,然后输出HS电路数据和LP电路数据;MIPI-DSI协议层编码代码架构如下:

MIPI-DPHY物理层串化

然后MIPI-DSI数据送入MIPI-DPHY物理层串化模块,将输入的4 Lane并行MIPI-DSI数据串化为4 Lane高速串行的差分信号,模块依托Xilinx官方的OSERDESE2和OBUFTDS实现串化和单端转差分处理;MIPI-DPHY物理层串化代码架构如下:

MIPI-LVDS显示屏

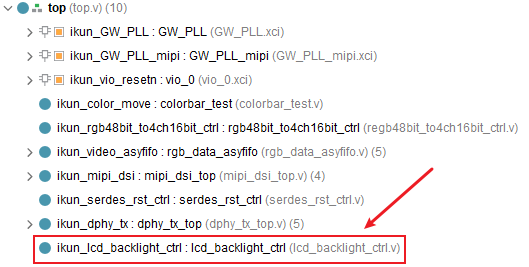

MIPI-LVDS显示屏分辨率为1024x600@60Hz;需要对MIPI-LVDS显示屏做初始化操作和背光控制,背光控制代码例化如下:

最后MIPI-DSI编码视频直接送MIPI-LVDS显示屏显示即可;MIPI-LVDS显示屏实物如下:

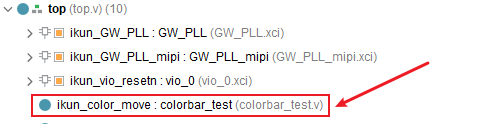

工程源码架构

工程源码架构如下:

4、工程源码1详解:Kintex7-325T版本

开发板FPGA型号:Kintex7-325T-xc7k325tffg900-2;

FPGA开发环境:Vivado2019.1;

输入:FPGA内部彩条,分辨率1024x600@60Hz;

输出:MIPI,分辨率1024x600@60Hz,4 Lane模式;

MIPI-DSI2-TX方案:纯verilog代码方案;

MIPI-D-PHY方案:纯verilog代码方案,OSERDESE2原语;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握Xilinx系列FPGA纯verilog实现MIPI-DSI视频编码输出的设计能力,以便能够移植和设计自己的项目;

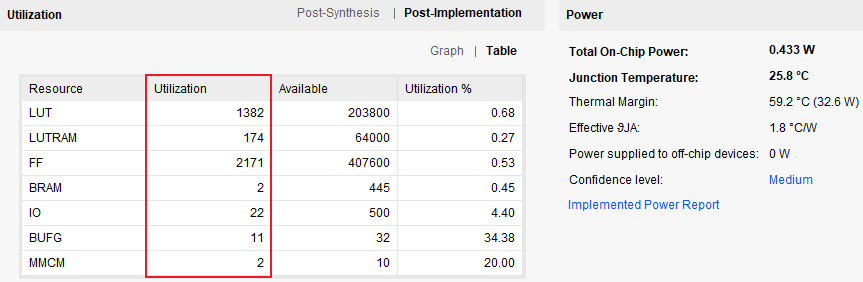

工程的资源消耗和功耗如下:

5、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

6、上板调试验证并演示

准备工作

FPGA开发板,推荐使用本博的开发板;

MIPI-LVDS显示屏;

开发板连接如下:

开发板上电后下载bit即可测试;

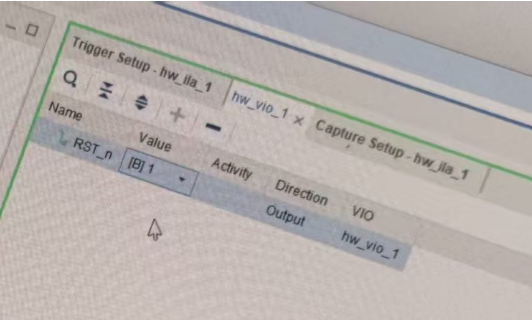

VIO解复位

由于上电后系统由VIO控制处于复位状态下,所以需要操作VIO进行解复位,如下:

即需要手动将RST_n设置为1;

MIPI-DSI视频编码输出演示

MIPI-DSI视频编码输出如下:

MIPI-TX原始

7、工程源码获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

FPGA纯verilog实现MIPI-DSI视频编码输出,提供工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目我这里已有的 MIPI 编解码方案 3、设计思路框架工程设计原理框图FPGA内部彩条RGB数据位宽转换RGB数据缓存MIPI-DSI协议层编码MIPI-DPHY物理层串化MIPI-LVDS显示屏工程…...

手写字魔法消除3:深度学习PmrNet神经网络实现图片修复(含训练代码、数据集和GUI交互界面)

第一步:PmrNet介绍 PmrNet是一种基于U-Net架构改进的深度学习网络,来自于论文《Practical Deep Raw Image Denoising on Mobile Devices》,这个网络聚焦于在移动设备上实现高效的原始图像(RAW)去噪(本文用来…...

大数据运维过程中常见的一些操作

大数据运维是确保大数据系统稳定运行、高效处理数据的关键环节。以下是大数据运维过程中常见的一些操作和任务: 1. 集群部署与配置 基础设施搭建:部署服务器、网络设备、存储系统,配置虚拟化环境(如 Docker、Kubernetes…...

opencv使用经典bug

opencv经典bug 1.bug介绍2.解决方案 1.bug介绍 D:\anaconda3\envs\yolo11s\python.exe F:\BYSJ\LX\yolov11-main\OCR_plateRecognition\plateRevise.py Traceback (most recent call last): File "F:\BYSJ\LX\yolov11-main\OCR_plateRecognition\plateRevise.py", l…...

劫持进程注入

劫持进程注入和远程线程注入的区别就是 远程线程注入是向一个正在运行中的进程注入 而劫持进程注入则是自己打开一个进程(以挂起的方式) 然后再进行注入的操作 这样做的原因是当进程在挂起的状态时他的所有线程都是处于未启用的阶段 这样就可以避免目标进程的反注入线程的…...

计算机基础——宏病毒防御与网络技术

文章目录 宏病毒详解与防范措施宏病毒简介宏病毒的特点宏病毒的传播途径宏病毒的防范措施宏病毒的检测与清除 自治计算机与自治系统解析什么是自治计算机?技术特点 自治系统(Autonomous System, AS)特点:自治系统类型 总结&#x…...

:架构、风险与防护全攻略)

深度解析互联网区(Internet ):架构、风险与防护全攻略

在企业网络架构中,互联网区(Internet Zone)是直接暴露在公网的关键区域,承载着Web服务、邮件服务、VPN接入等多种对外服务。由于其直接与互联网连接,安全防护尤为重要。本文将从定义、功能、设备组成、安全风险到防护措…...

2024Flutter面试题

1.Dart是值传递还是引用传递? dart是值传递。 每次调用函数,传递过去的都是对象的内存地址,而不是这个对象的赋值。 2.简述Dart语音特性 在Dart中,一切都是对象,所有的对象都是继承自Object Dart是强类型语言&#…...

C++内存学习

引入 在实例化对象时,不管是编译器还是我们自己,会使用构造函数给成员变量一个合适的初始值。 但是经过构造函数之后,我们还不能将其称为成员变量的初始化: 构造函数中的语句只能称为赋初值,而不能称作初始化 因为初…...

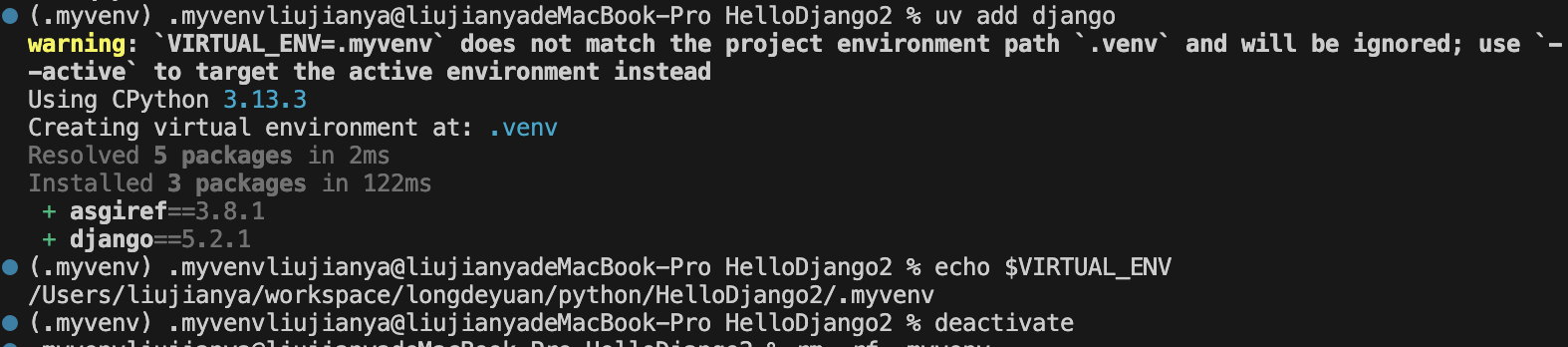

Python uv包管理工具使用详解

一、UV 工具概述 UV 是由 Astral 团队(Ruff 工具开发者)用 Rust 编写的新一代 Python 包管理器,旨在替代传统工具链(如 pip、virtualenv、poetry 等),提供以下核心优势 : 极速性能&a…...

[Linux] Linux 系统从启动到驱动加载

Linux 系统从启动到驱动加载 文章目录 Linux 系统从启动到驱动加载一、硬件上电与 BIOS/UEFI 阶段1. 1 硬件上电初始化1.2 BIOS/UEFI执行过程1.3 Bootloader加载细节 二、Bootloader 阶段三、Linux 内核初始化3.1 架构相关初始化(setup_arch)3.2 核心子系…...

基于微信小程序的云校园信息服务平台设计与实现(源码+定制+开发)云端校园服务系统开发 面向师生的校园事务小程序设计与实现 融合微信生态的智慧校园管理系统开发

博主介绍: ✌我是阿龙,一名专注于Java技术领域的程序员,全网拥有10W粉丝。作为CSDN特邀作者、博客专家、新星计划导师,我在计算机毕业设计开发方面积累了丰富的经验。同时,我也是掘金、华为云、阿里云、InfoQ等平台…...

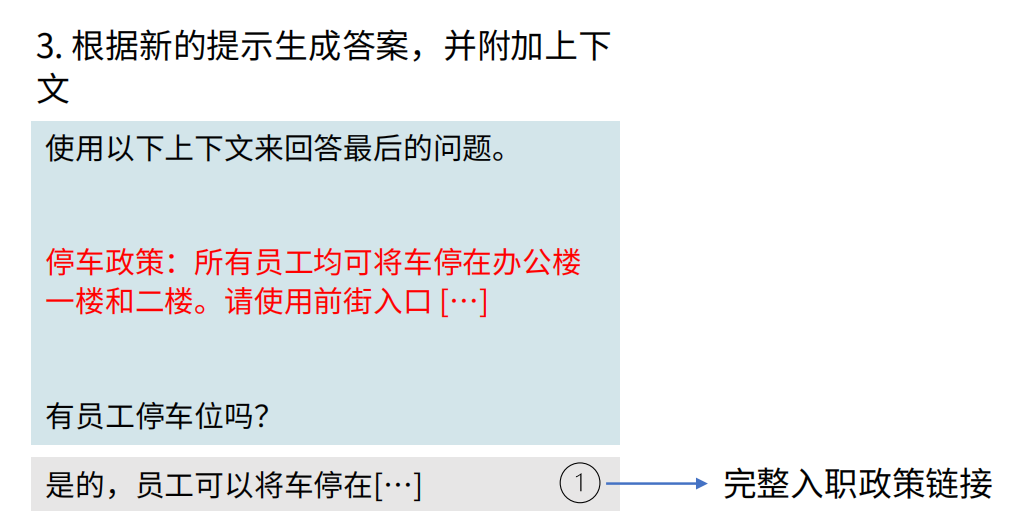

大语言模型的技术原理与应用前景:从Transformer到ChatGPT

目录 摘要 1. 引言 2. Transformer架构核心原理 2.1 自注意力机制 2.2 位置编码 2.3 前馈神经网络 3. 从GPT到ChatGPT的演进 3.1 GPT系列模型架构 3.2 训练流程优化 4. 应用场景与案例分析 4.1 代码生成 4.2 文本摘要 4.3 问答系统 5. 挑战与未来方向 5.1 当前技…...

如何编写GitLab-CI配置文件

创建文件 在根目录新建.gitlab-ci.yml文件. 该文件与项目其他文件一样, 同样受到版本控制, 所以可以在不同的分支下, 配置不同的持续集成脚本 YAML语法 配置文件遵循YAML语法, 关于该语法的内容, 自行搜索 参考 YAML 语言教程 关键词 根主要关键词一览 关键词含义可选备…...

生成式人工智能:重构软件开发的范式革命与未来生态

引言 生成式人工智能(GenAI)正以颠覆性力量重塑软件开发的底层逻辑。从代码生成到业务逻辑设计,从数据分析到用户交互,GenAI通过其强大的推理能力与场景适应性,将传统开发流程的“复杂工程”转化为“敏捷实验”&#…...

关于 java:4. 异常处理与调试

一、异常核心语法 1.1 try-catch-finally:异常捕获与处理结构 1)作用 用于捕获和处理程序运行过程中可能发生的异常 防止程序因异常中断,提高代码的鲁棒性(健壮性) 2)基本语法结构: try {…...

Java基础 Day26

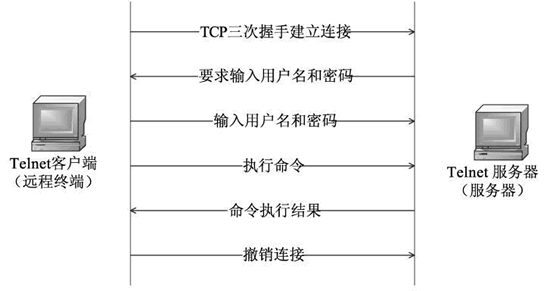

一、网络编程简介 1、概念 网络编程指在网络通信协议下,不同计算机上运行的程序,进行数据传输 2、软件架构 (1)CS架构(客户端和服务端) 在用户本地有一个客户端程序,在远程有一个服务器端程…...

android lifeCycleOwner生命周期

一 Fragment中 viewLifecycleOwner.repeatOnLifecycle(Lifecycle.State.STARTED) 什么时候执行? 让我分析一下相关问题: 关于 onPause 时的数据更新: viewLifecycleOwner.lifecycleScope.launch {viewLifecycleOwner.repeatOnLifecycle(Lifecycle.Sta…...

高防IP能抗住500G攻击吗?

在当今互联网环境中,网络安全问题日益严峻,尤其是针对网站的DDoS攻击,更是让众多站长头疼不已。而高防IP作为应对此类攻击的有效手段,其性能与稳定性成为了大家关注的焦点。那么,高防IP真的能抗住500G的超大流量攻击吗…...

工作流引擎-10-什么是 BPM?

工作流引擎系列 工作流引擎-00-流程引擎概览 工作流引擎-01-Activiti 是领先的轻量级、以 Java 为中心的开源 BPMN 引擎,支持现实世界的流程自动化需求 工作流引擎-02-BPM OA ERP 区别和联系 工作流引擎-03-聊一聊流程引擎 工作流引擎-04-流程引擎 activiti 优…...

day1-小白学习JAVA---JDK安装和环境变量配置(mac版)

JDK安装和环境变量配置 我的电脑系统一、下载JDK1、oracle官网下载适合的JDK安装包,选择Mac OS对应的版本。 二、安装三、配置环境变量1、终端输入/usr/libexec/java_home -V查询所在的路径,复制备用2、输入ls -a3、检查文件目录中是否有.bash_profile文…...

)

每日温度(力扣-739)

【题目描述】 给定一个整数数组 temperatures ,表示每天的温度,返回一个数组 answer ,其中 answer[i] 是指对于第 i 天,下一个更高温度出现在几天后。如果气温在这之后都不会升高,请在该位置用 0 来代替。 【输出输出样…...

QT中子线程触发主线程弹窗并阻塞等待用户响应-传统信号槽实现

目录 QT中子线程触发主线程弹窗并阻塞等待用户响应传统信号槽实现实现思路具体步骤1. 定义信号与槽2. 异步任务中触发弹窗3. 主线程处理弹窗4. 连接信号与槽关键点总结 更简单实现 QT中子线程触发主线程弹窗并阻塞等待用户响应 传统信号槽实现 场景需求:在子线程执…...

HarmonyOS鸿蒙系统深度运维指南

一、开发与调试环境全链路配置 工具链部署标准流程 HDC 3.0调试套件:支持分布式设备的跨端调试与性能分析,需配置端口转发规则(默认调试端口:8080)KaihongOS桌面开发环境:集成DevEco Studi…...

SpringBoot多租户系统的5种架构设计方案

多租户(Multi-tenancy)是一种软件架构模式,允许单个应用实例服务于多个客户(租户),同时保持租户数据的隔离性和安全性。 通过合理的多租户设计,企业可以显著降低运维成本、提升资源利用率,并实现更高效的服务交付。 本文将分享S…...

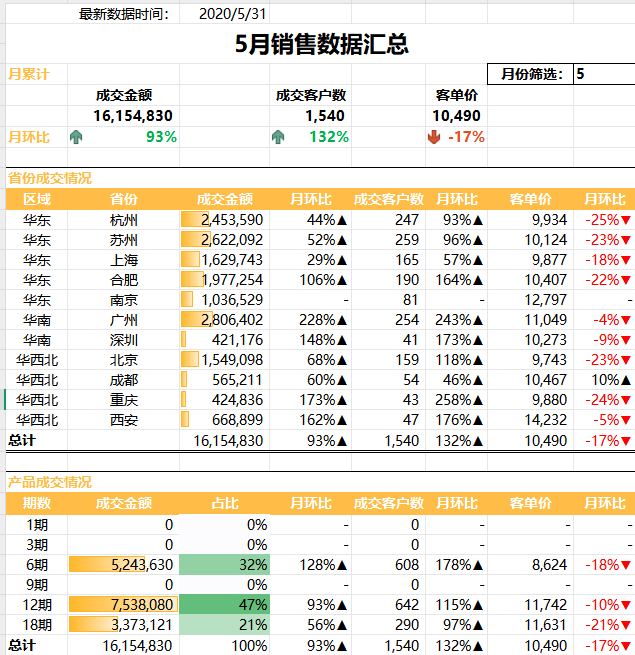

数据分析实战1(Excel制作报表)

Excel数据链接:【课程4.0】第2章_Excel.zip - 飞书云文档 1、拿到数据第一步 备份数据 ctrlshiftL:筛选 相关快捷键:(alt:自动求和、ctrlshift5:转换为%) 2、环比、同比 环比(本…...

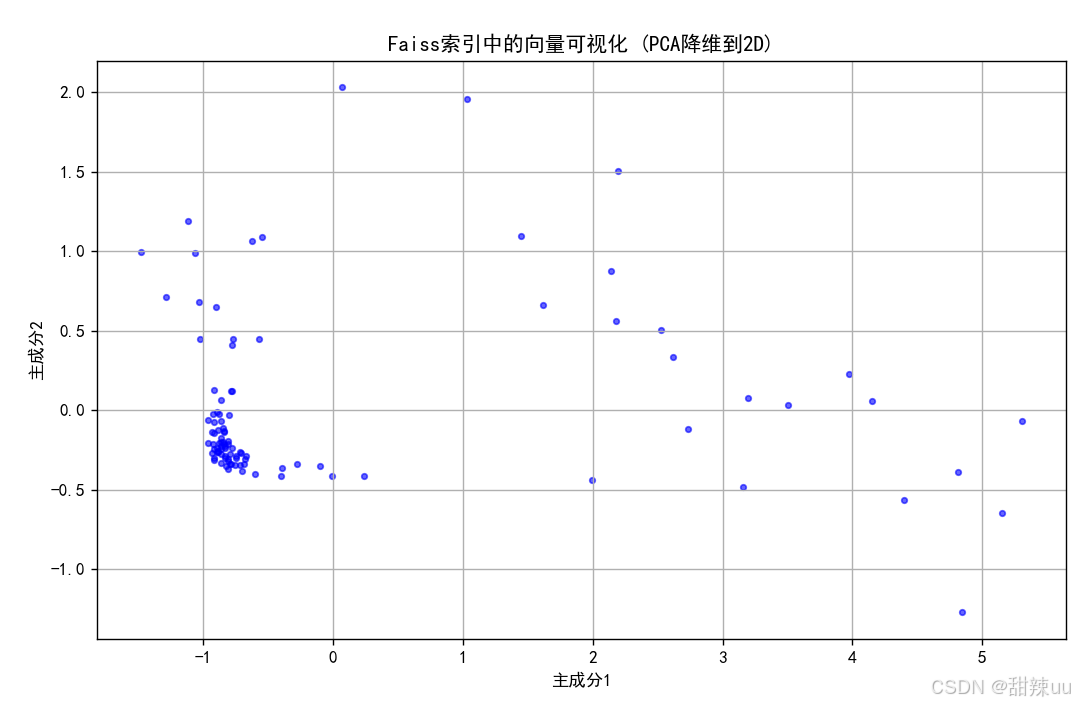

本地部署大模型llm+RAG向量检索问答系统 deepseek chatgpt

项目视频讲解: 本地部署大模型llm+RAG向量检索问答系统 deepseek chatgpt_哔哩哔哩_bilibili 运行结果:...

设备健康管理的战略升维:用预测性维护重构企业竞争力

第一章 传统维护的沉默成本:被低估的利润黑洞 当轴承振动值突破安全阈值时,制造企业损失的远非维修费用。某重型装备制造厂的案例揭示了典型多米诺效应:传动系统突发故障导致36小时停产,触发订单违约金(合约金额的9%&…...

Redis事务详解:原理、使用与注意事项

文章目录 Redis事务详解:原理、使用与注意事项什么是Redis事务Redis事务的基本使用基本事务示例事务执行过程 Redis事务的错误处理1. 入队错误2. 执行错误 WATCH命令:乐观锁实现Redis事务的局限性事务的最佳实践Lua脚本总结 Redis事务详解:原…...

提升 GitHub Stats 的 6 个关键策略

哈哈,GitHub 的 “B-” 评级 其实是个玄学问题,但确实有一些 快速提升的技巧!你的数据看起来 提交数(147)和 PR(9)不算少,但 Stars(21)和贡献项目数ÿ…...