《深入解析UART协议及其硬件实现》-- 第二篇:UART硬件架构设计与FPGA实现

第二篇:UART硬件架构设计与FPGA实现

1. 模块化架构设计

1.1 系统级框图与时钟域划分

-

核心模块划分 :

发送模块(TX) :负责数据帧组装与串行输出。

接收模块(RX) :负责串行数据采样与帧解析。

波特率生成器(Baud Generator) :生成发送/接收时钟。

控制寄存器组(Control Registers) :配置数据位宽、校验模式、波特率等参数。 -

时钟域划分 :

系统时钟域(clk_sys) :主时钟,用于控制逻辑和寄存器访问。

波特率时钟域(clk_baud) :由波特率生成器分频得到,用于发送/接收时序控制。 -

跨时钟域同步策略 :

- 异步信号(如外部中断信号)需通过两级同步器(2-FF)消除亚稳态:

verilog

always @(posedge clk_sys) beginsync_reg <= async_signal; // 第一级同步sync_signal <= sync_reg; // 第二级同步 end - 异步信号(如外部中断信号)需通过两级同步器(2-FF)消除亚稳态:

1.2 波特率生成器设计

-

分频器参数化建模 :

分频系数计算 :分频系数=系统时钟频率/(波特率×过采样倍数)

- 例如:系统时钟50 MHz,波特率115200,16x过采样 → 分频系数 = 50,000,000 / (115200 × 16) ≈ 27.13 → 取整为27。

-

Verilog实现 :

verilog

module baud_generator (input wire clk, // 系统时钟input wire [15:0] div_value, // 分频系数output wire baud_clk // 波特率时钟

);reg [15:0] counter = 0;always @(posedge clk) beginif (counter == div_value) begincounter <= 0;baud_clk <= ~baud_clk;end else begincounter <= counter + 1;endend

endmodule

1.3 过采样技术(16x Oversampling)

-

抗噪声设计原理 :

接收端以波特率的16倍频率采样,通过多数表决过滤瞬时噪声。 -

实现步骤 :

- 在16个采样周期内检测起始位下降沿。

- 对每个数据位取中间3次采样(第7、8、9次)的多数值作为最终值。

-

Verilog代码片段 :

verilog// 起始位检测 always @(posedge clk_16x) beginif (rx_sync == 1'b0 && start_detected == 1'b0) begin // 检测到起始位sample_counter <= 0;start_detected <= 1'b1;end end// 数据位采样 always @(posedge clk_16x) beginif (start_detected) beginsample_counter <= sample_counter + 1;if (sample_counter % 16 == 7) begin // 采样中点data_shift <= {rx_sync, data_shift[7:1]};endend end

2. 发送器(Transmitter)RTL实现

2.1 状态机设计

- 状态定义 :

IDLE :等待发送请求(发送使能信号拉高)。

START :发送起始位(逻辑0)。

DATA :依次发送数据位(LSB优先)。

PARITY :发送校验位(可选)。

STOP :发送停止位(逻辑1)。

RETURN_IDLE :返回IDLE状态,等待下一帧。 - 状态转移图 :

IDLE → (发送使能) → START → (1个波特周期) → DATA → (数据位发送完成) → PARITY → (校验位发送完成) → STOP → (停止位发送完成) → RETURN_IDLE

2.2 数据缓冲与移位寄存器

-

双缓冲设计 :

发送缓冲区(TX Buffer) :存储待发送数据,允许连续写入。

移位寄存器(Shift Register) :从缓冲区加载数据,逐位输出。 -

Verilog实现 :

verilogreg [7:0] tx_buffer; reg [7:0] shift_reg; reg tx_busy;always @(posedge clk_baud) beginif (!tx_busy && tx_enable) beginshift_reg <= tx_buffer; // 加载数据到移位寄存器tx_busy <= 1'b1;end else if (tx_busy) beginshift_reg <= {1'b0, shift_reg[7:1]}; // 右移输出end end

2.3 亚稳态防护

-

同步器链应用 :

外部信号(如发送使能)需跨时钟域同步:

verilogreg tx_enable_sync1, tx_enable_sync2; always @(posedge clk_baud) begintx_enable_sync1 <= tx_enable; // 第一级同步tx_enable_sync2 <= tx_enable_sync1; // 第二级同步 end

3. 接收器(Receiver)关键逻辑

3.1 起始位检测与毛刺滤波

- 滤波算法 :

在16x过采样下,连续3次检测到低电平视为有效起始位。 - Verilog实现 :

verilog

reg [2:0] start_samples;

always @(posedge clk_16x) beginstart_samples <= {start_samples[1:0], rx_sync};if (start_samples == 3'b000) begin // 连续3次低电平start_detected <= 1'b1;end

end

3.2 数据采样点动态校准

- 中点采样策略 :

在16x过采样下,每个数据位在第7、8、9次采样点取中间值。 - 多数表决逻辑 :

verilog

wire [2:0] samples = {sample7, sample8, sample9};

assign data_bit = (samples >= 2) ? 1'b1 : 1'b0; // 至少2个高电平视为1

3.3 错误检测电路

-

帧错误(Frame Error) :

停止位未检测到高电平 → 标志位置1。verilog

always @(posedge clk_baud) beginif (stop_bit_received != 1'b1) beginframe_error <= 1'b1;endend

- 溢出错误(Overrun Error) :

接收缓冲区未读取时新数据到达 → 标志位置1。 - 奇偶校验错误(Parity Error) :

接收校验位与计算值不匹配 → 标志位置1。

4. FPGA验证方法论

4.1 基于SystemVerilog的断言验证

- 协议规则检查 :

systemverilog

// 检查停止位为高电平assert property (@(posedge clk_baud) (tx_state == STOP) |-> (txd == 1'b1)) else $error("Stop bit error!");// 检查奇偶校验位正确性assert property (@(posedge clk_baud) (parity_generated == expected_parity)) else $error("Parity error!");

4.2 自动化测试平台

-

回环测试(Loopback Test) :

将发送端(TXD)直接连接至接收端(RXD),验证数据完整性。verilog

uart_top uut (.clk(clk),.txd(loopback_rxd), // 发送端输出连接至接收端输入.rxd(loopback_txd));

- 随机化测试向量 :

systemverilog

for (int i=0; i<1000; i++) begindata = $urandom(); // 生成随机数据send_data(data);check_received_data(data);end

4.3 时序收敛分析

- 建立/保持时间约束 :

tcl

# XDC约束示例(Xilinx Vivado)create_clock -period 20 [get_ports clk] # 50MHz时钟set_input_delay -clock clk 2 [get_ports rxd]set_output_delay -clock clk 3 [get_ports txd]

- 时序报告分析 :

确保关键路径(如状态机逻辑)满足时序要求。

附录:关键RTL代码与仿真波形

1. 发送状态机Verilog代码

verilog

typedef enum {IDLE, START, DATA, PARITY, STOP} tx_state_t;

tx_state_t current_state = IDLE;always @(posedge clk_baud) begincase (current_state)IDLE: if (tx_enable_sync2) begincurrent_state <= START;txd <= 1'b0; // 发送起始位endSTART: current_state <= DATA;DATA: if (bit_counter == 7) begincurrent_state <= PARITY;endPARITY: current_state <= STOP;STOP: current_state <= RETURN_IDLE;endcase

end

2. 仿真波形

- 起始位(低电平)→ 数据位(LSB优先)→ 停止位(高电平)。

相关文章:

《深入解析UART协议及其硬件实现》-- 第二篇:UART硬件架构设计与FPGA实现

第二篇:UART硬件架构设计与FPGA实现 1. 模块化架构设计 1.1 系统级框图与时钟域划分 核心模块划分 : 发送模块(TX) :负责数据帧组装与串行输出。 接收模块(RX) :负责串行数据采样与…...

java swing 晃动鼠标改变背景颜色

import java.awt.Color; import java.awt.Component; import java.awt.event.MouseEvent; import java.awt.event.MouseMotionListener;import javax.swing.*; public class testA extends JFrame {testA(){super("晃动鼠标改变背景颜色");setBounds(600, 200, 600, …...

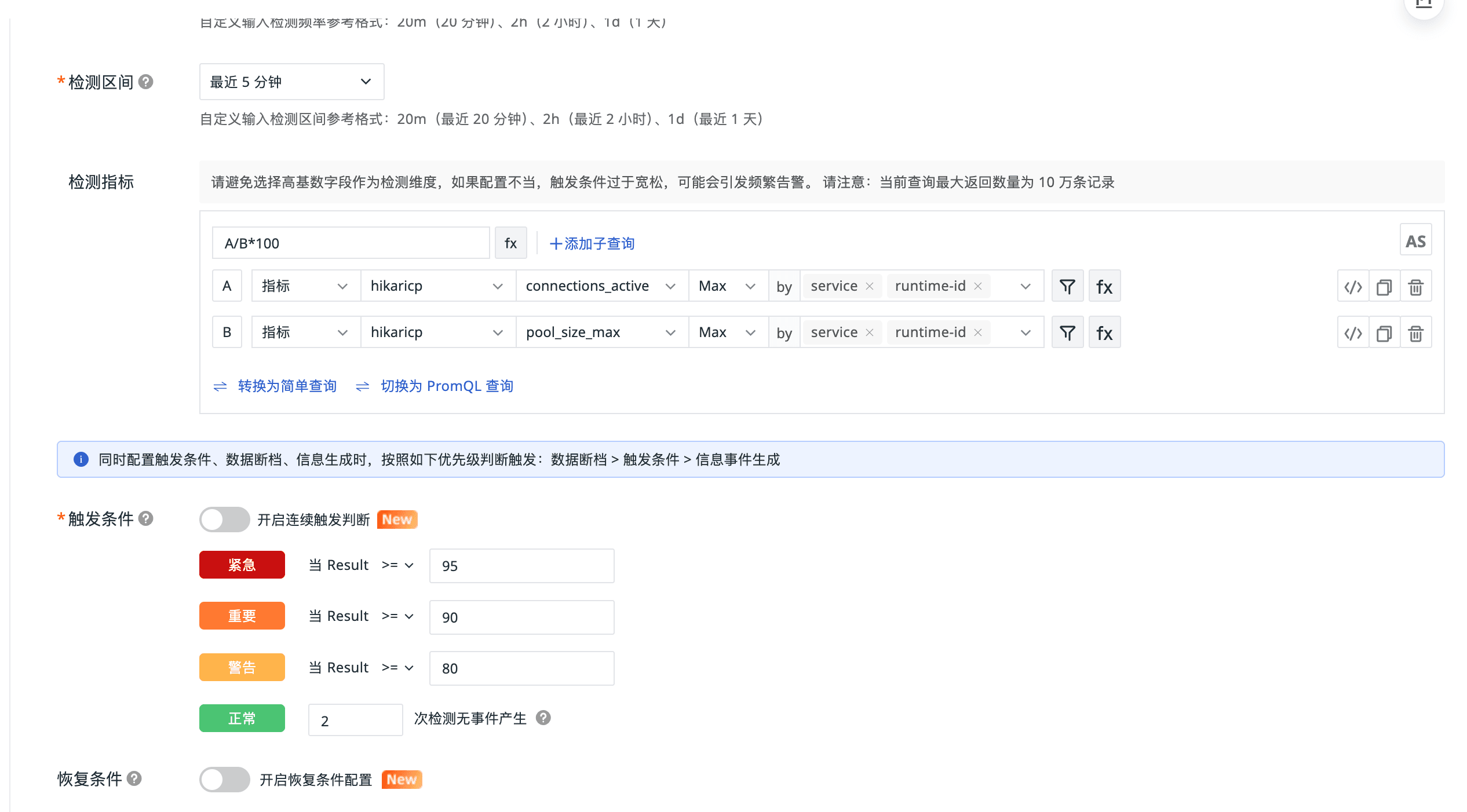

HikariCP 可观测性最佳实践

HikariCP 介绍 HikariCP 是一个高性能、轻量级的 JDBC 连接池,由 Brett Wooldridge 开发。它以“光”命名,象征快速高效。它支持多种数据库,配置简单,通过字节码优化和智能管理,实现低延迟和高并发处理。它还具备自动…...

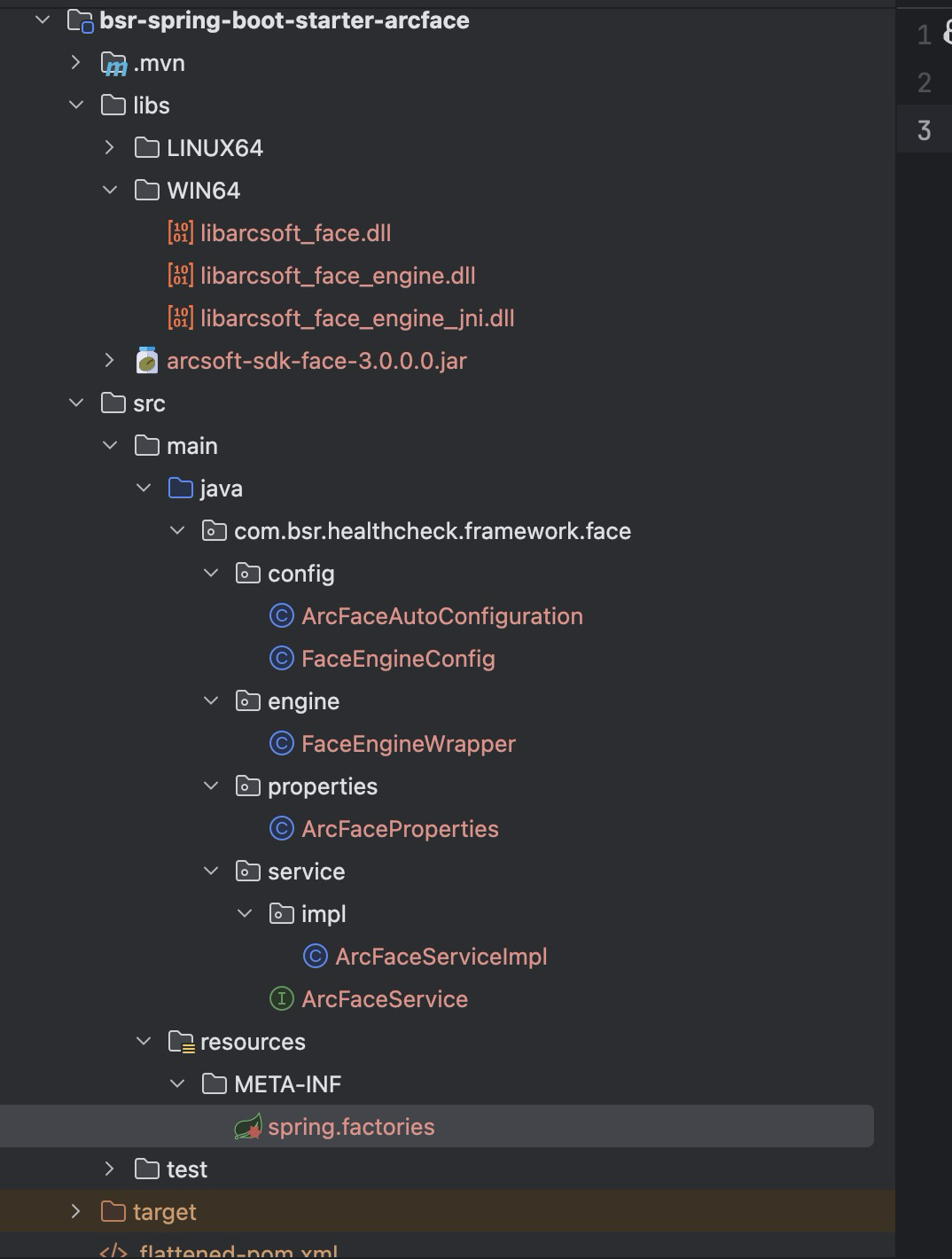

简简单单探讨下starter

前言 今天其实首先想跟大家探讨下:微服务架构,分业务线了,接入第三方服务、包啥的是否自己定义一个stater更好? 一、starter是什么? 在 Spring Boot 中,Starter 是一种特殊的依赖模块,用于快速…...

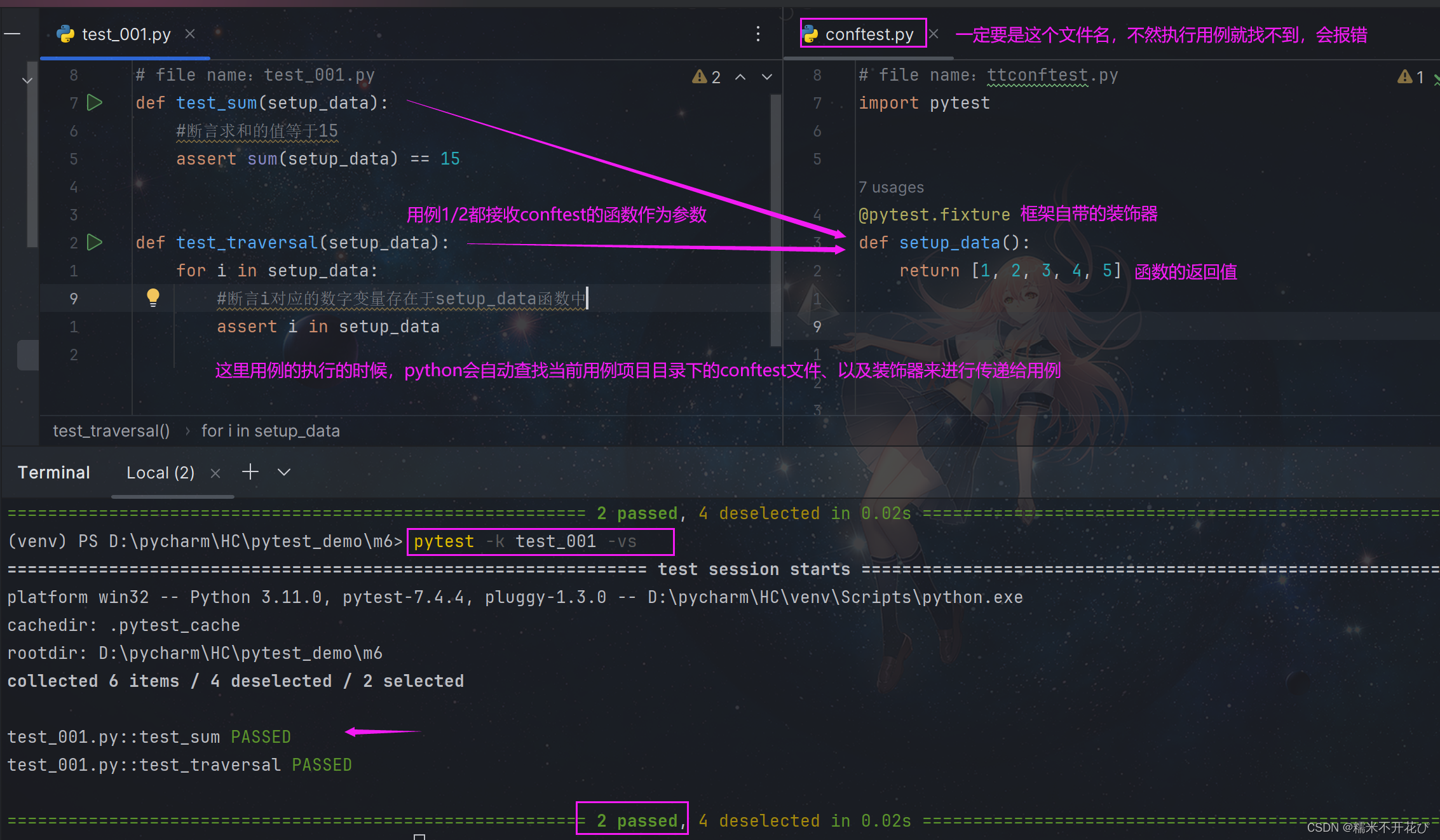

PyTest框架学习

0. 优先查看学习教程 超棒的学习教程 1. yield 语句 yield ptc_udp_clientyield:在 Pytest fixture 中,yield 用于分隔设置和清理代码。yield 之前的代码在测试用例执行前运行,yield 之后的代码在测试用例执行后运行。ptc_udp_client&…...

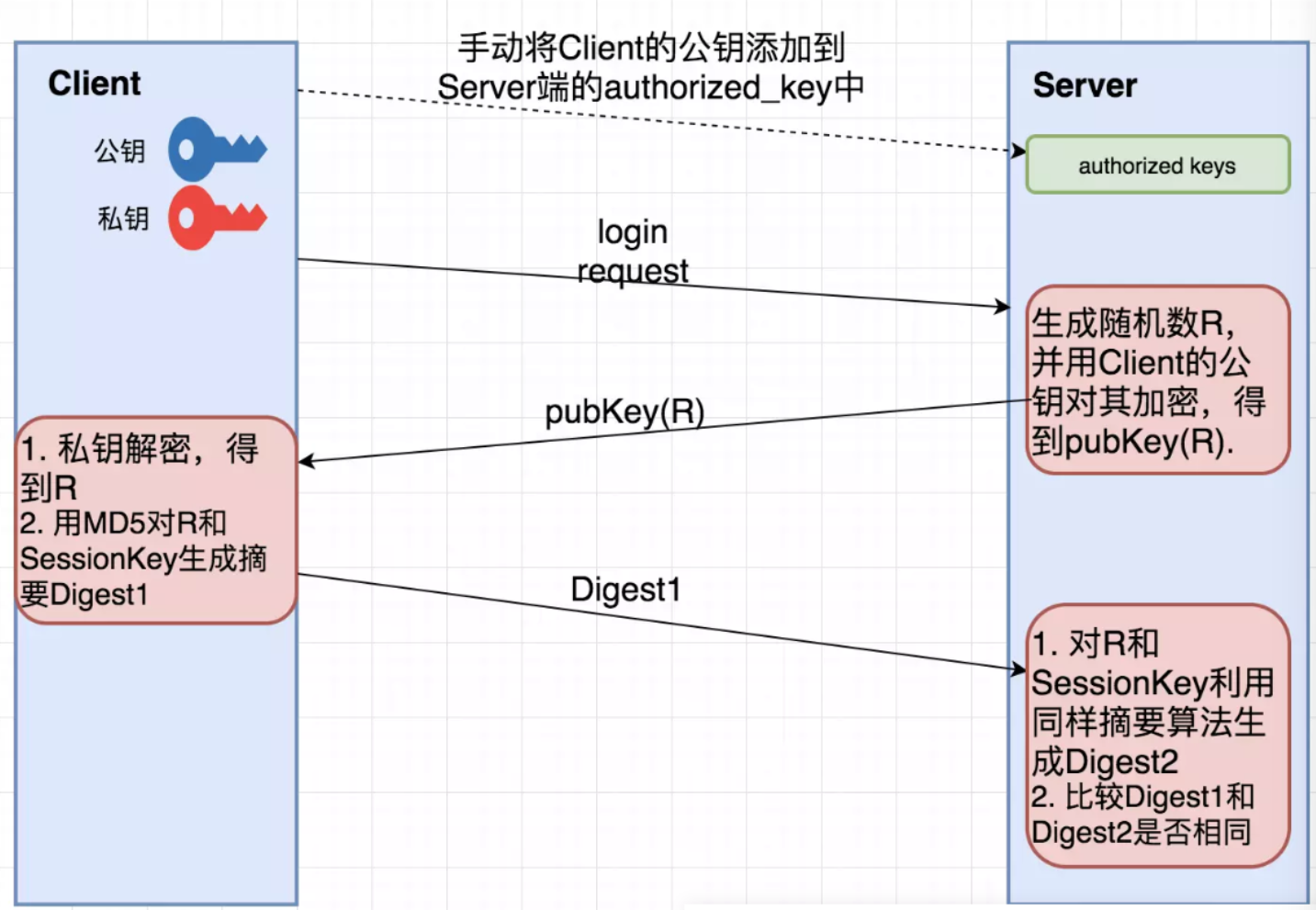

SIP、SAP、SDP、mDNS、SSH、PTP

🌈 一、SIP 会话初始协议 会话初始协议 SIP 是一个在 IP 网络上进行多媒体通信的应用层控制协议,它被用来创建、修改和终结 1 / n 个参加者参加的会话进程。SIP 不能单独完成呼叫功能,需要和 RTP、SDP 和 DNS 配合来完成。 1. SIP 协议的功…...

【AI学习笔记】Coze工作流写入飞书多维表格(即:多维表格飞书官方插件使用教程)

背景前摇: 今天遇到一个需求,需要把Coze平台大模型和用户的对话记录保存进飞书表格,这个思路其实不难,因为官方提供了写入飞书表格和多维表格的插件,但是因为平台教程和案例的资料匮乏,依据现有的官方文档…...

System.Threading.Timer 和 System.Timers.Timer

在 .NET 中,System.Threading.Timer 和 System.Timers.Timer 都是用于定时任务的类,但它们的实现方式、使用场景和特性有所不同。以下是它们的 核心区别 和 使用示例: 1. System.Threading.Timer 特点 轻量级,基于线程池…...

在 Windows 系统下配置 VSCode + CMake + Ninja 进行 C++ 或 Qt 开发

在 Windows 系统下配置 VSCode CMake Ninja 进行 C 或 Qt 开发,是一个轻量级但功能强大的开发环境。下面我将分步骤详细说明如何搭建这个开发环境,支持纯 C 和 Qt 项目。 🧰 所需工具安装 1. 安装 Visual Studio Code(VSCode&…...

`tokenizer.decode` 出现乱码或异常输出,怎么处理

tokenizer.decode 出现乱码或异常输出,怎么处理 在使用 Hugging Face Transformers 库进行大语言模型(LLM)开发时,tokenizer.decode 出现乱码或异常输出,通常和模型输出的 token 序列、分词器对齐逻辑、特殊 token 处理有关。以下从模型侧、分词器侧、后处理环节给出解决…...

几何绘图与三角函数计算应用

几何绘图与三角函数计算应用 设计思路 左侧为绘图控制面板,右侧为绘图区域支持绘制点、线、矩形、圆、多边形等基本几何图形实现三角函数计算器(正弦、余弦、正切等)包含角度/弧度切换和常用数学常数历史记录功能保存用户绘图 完整实现代码…...

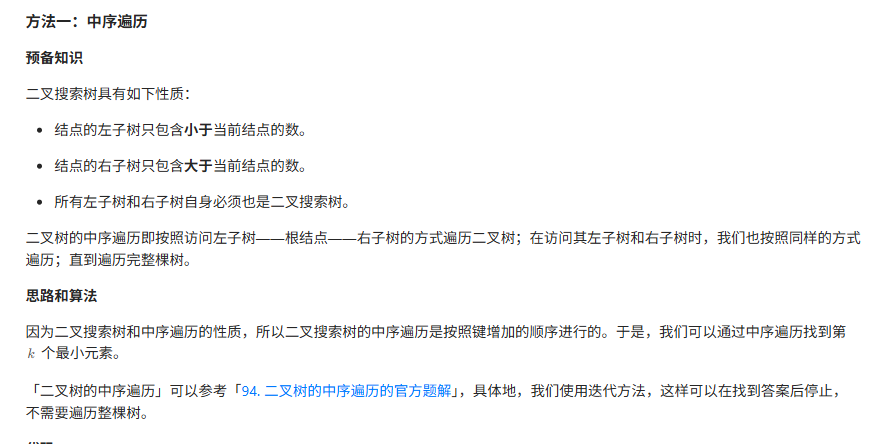

leetcode 二叉搜索树中第k小的元素 java

中序遍历 定义一个栈,用于存取二叉树中的元素 Deque<TreeNode> stack new ArrayDeque<TreeNode>();进入while循环while(! stack.isEmpty()|| root ! null){}将root的左节点入栈,直到rootnull while(rootnull){stack.push(root);root ro…...

5.1 初探大数据流式处理

在本节中,我们深入探讨了大数据流式处理的基础知识和关键技术。首先,我们区分了批式处理和流式处理两种大数据处理方式,了解了它们各自的适用场景和特点。流式处理以其低延迟和高实时性适用于需要快速响应的场景,而批式处理则适用…...

基于 Android 和 JBox2D 的简单小游戏

以下是一个基于 Android 和 JBox2D 的简单小游戏开发示例,实现一个小球在屏幕上弹跳的效果: 1. 添加 JBox2D 依赖 在项目的 build.gradle 文件中添加 JBox2D 的依赖: dependencies {implementation org.jbox2d:jbox2d-library:2.3.1 } 2.…...

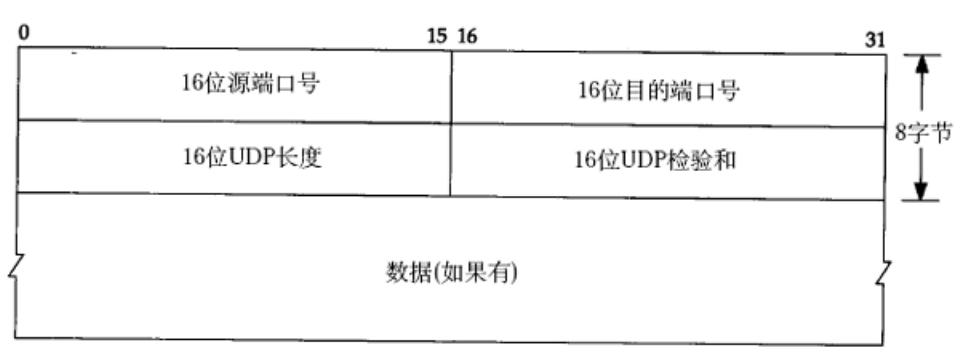

传输层协议 UDP 介绍 -- UDP 协议格式,UDP 的特点,UDP 的缓冲区

目录 1. 再识的端口号 1.1 端口号范围划分 1.2 知名端口号(Well-Know Port Number) 2. UDP 协议 2.1 UDP 协议格式 2.2 UDP 的特点 2.3 UDP 的缓冲区 2.4 一些基于 UDP 的应用层协议 传输层(Transport Layer)是计算机网络…...

Python try-except-else 语句详解

try-except-else 是 Python 中用于异常处理的重要结构,它允许你优雅地处理可能出现的错误,并在没有错误发生时执行特定代码。下面我将详细解释这个结构及其用法。 基本语法 try:# 可能引发异常的代码块 except [ExceptionType]:# 异常处理代码块 else:…...

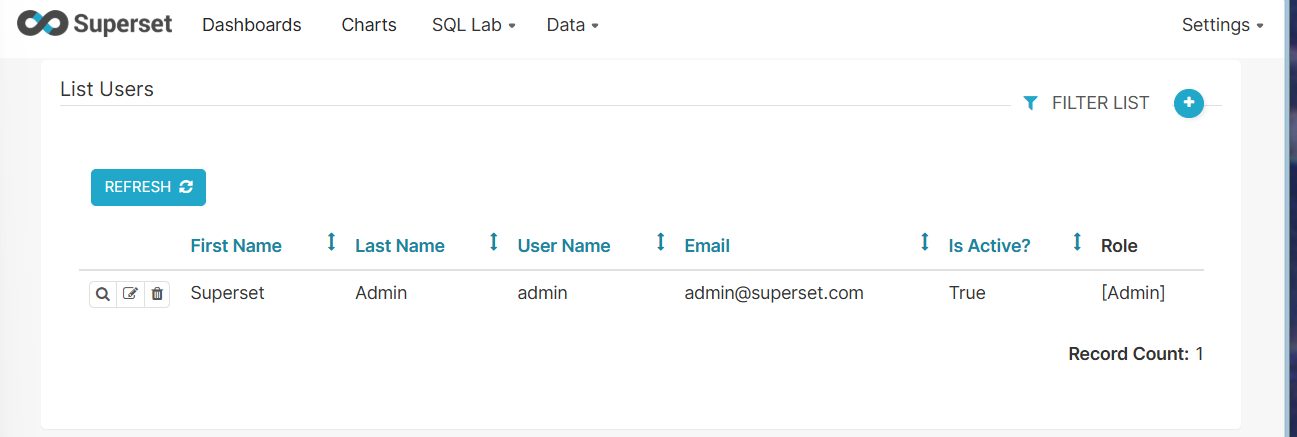

ApacheSuperset CVE-2023-27524

前言:CVE-2023-27524 是一种远程代码执行漏洞,攻击者通过该漏洞可在受影响系统上执行任意代码,从而获得未授权访问权 CVE-2023-27524 GitHubhttps://github.com/horizon3ai/CVE-2023-27524 任务一 代理 | 拉取镜像 vi /etc/proxychains4.conf //最下面修…...

Windows Server部署Vue3+Spring Boot项目

在Windows Server 上部署Vue3 Spring Boot前后端分离项目的详细步骤如下: 一、环境准备 安装JDK 17 下载JDK MSI安装包(如Oracle JDK 或 OpenJDK) 双击安装,配置环境变量: JAVA_HOME:JDK安装路径…...

malloc 是如何分配内存的?——C 语言内存分配详解

文章目录 malloc是如何分配内存的?——C语言内存分配详解一、引言二、内存分配的基本概念1. 虚拟内存与物理内存2. 进程内存布局 三、malloc函数详解1. 函数原型与功能2. 关键特性 四、malloc的底层实现机制1. 内存分配器的角色2. 分配策略3. 内存碎片问题 五、glib…...

Opencl

**OpenCL(Open Computing Language)**是一种用于异构平台(包括CPU、GPU、FPGA、DSP等)上的并行计算框架和编程标准。它由Khronos Group制定,旨在提供一种跨平台、统一的编程接口,使开发者可以利用不同硬件设…...

如何在 HTML 中添加按钮

原文:如何在 HTML 中添加按钮 | w3cschool笔记 (请勿将文章标记为付费!!!!) 在网页开发中,按钮是用户界面中不可或缺的元素之一。无论是用于提交表单、触发动作还是导航࿰…...

【优秀三方库研读】quill 开源库中的命名空间为什么要用宏封装

将命名空间封装成宏的作用与优势 QUILL_BEGIN_NAMESPACE 和 QUILL_END_NAMESPACE 这种宏封装是 C++ 库开发中的常见技巧,主要解决以下问题并提供显著优势: 1. 解决核心问题:命名空间嵌套与版本控制 问题场景: 库需要支持多版本共存(如 quill::v1, quill::v2),但希望默认…...

)

AlphaFold3运行错误及解决方法(1)

1. chemical_component_sets.pickle 运行alphafold3遇到下面的问题: FileNotFoundError: [Errno 2] No such file or directory: /xxx/xxx/anaconda3/envs/alphafold3/lib/python3.11/site-packages/alphafold3/constants/converters/chemical_component_sets.pickle搜索你的系…...

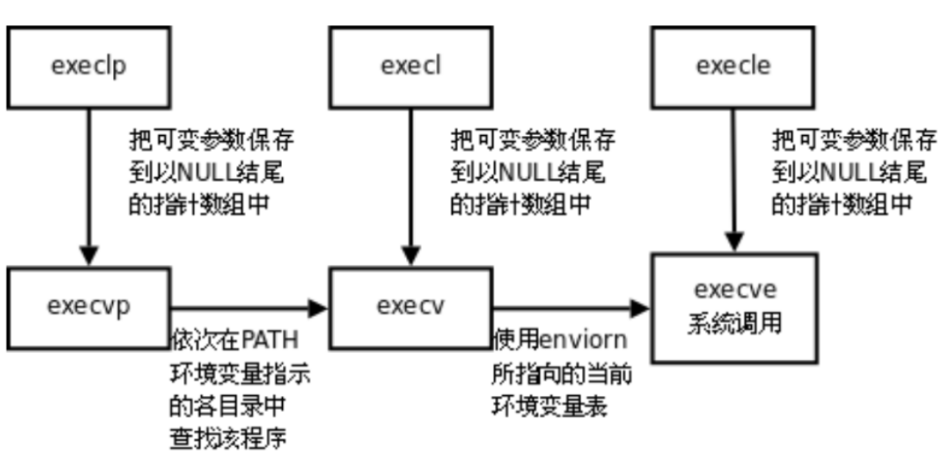

Linux--进程的程序替换

问题导入: 前面我们知道了,fork之后,子进程会继承父进程的代码和“数据”(写实拷贝)。 那么如果我们需要子进程完全去完成一个自己的程序怎么办呢? 进程的程序替换来完成这个功能! 1.替换原理…...

调教 DeepSeek - 输出精致的 HTML MARKDOWN

【序言】 不知道是不是我闲的蛋疼,对百度AI 和 DeepSeek 的回答都不太满意。 DeepSeek 回答句子的引用链接,始终无法准确定位。有时链接只是一个域名,有时它给的链接是搜索串如: baidu.com/?q"搜索内容"。 百度AI 回答句子的引用…...

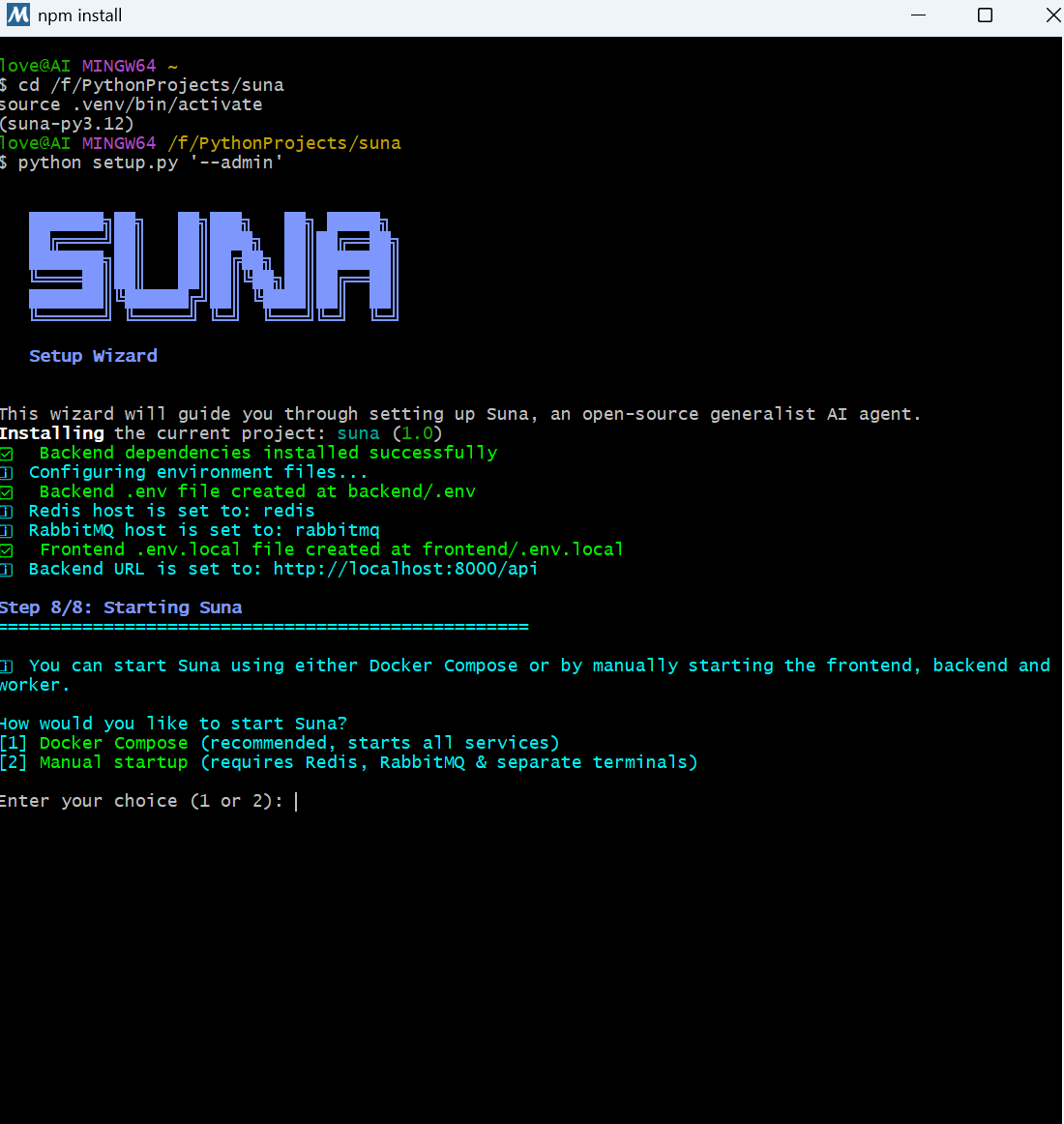

【笔记】Windows系统部署suna基于 MSYS2的Poetry 虚拟环境backedn后端包编译失败处理

基于 MSYS2(MINGW64)中 Python 的 Poetry 虚拟环境包编译失败处理笔记 一、背景 在基于 MSYS2(MINGW64)中 Python 创建的 Poetry 虚拟环境里,安装 Suna 开源项目相关包时编译失败,阻碍项目正常部署。 后端…...

:分组注意力机制的原理与实践《一》)

GQA(Grouped Query Attention):分组注意力机制的原理与实践《一》

GQA(Grouped Query Attention)是近年来在大语言模型中广泛应用的一种注意力机制优化方法,最初由 Google 在 2023 年提出。它是对 Multi-Query Attention (MQA) 的扩展,旨在平衡模型性能与计算效率。 🌟 GQA 是什么&…...

【深度学习优化算法】02:凸性

【作者主页】Francek Chen 【专栏介绍】 ⌈ ⌈ ⌈PyTorch深度学习 ⌋ ⌋ ⌋ 深度学习 (DL, Deep Learning) 特指基于深层神经网络模型和方法的机器学习。它是在统计机器学习、人工神经网络等算法模型基础上,结合当代大数据和大算力的发展而发展出来的。深度学习最重…...

JAVA国际版一对一视频交友视频聊天系统源码支持H5+APP

全球畅连无界社交:JAVA国际版一对一视频交友系统源码(H5APP双端覆盖) 在全球化社交需求激增的今天,构建一个支持多语言、适配国际支付且功能丰富的视频交友平台,成为出海创业者和企业的核心诉求。JAVA国际版一对一视频…...

策略公开了:年化494%,夏普比率5.86,最大回撤7% | 大模型查询akshare,附代码

原创内容第907篇,专注智能量化投资、个人成长与财富自由。 这位兄弟的策略公开了,年化494%,夏普比率5.86,最大回撤7%,欢迎大家前往围观: http://www.ailabx.com/strategy/683ed10bdabe146c4c0b2293 系统代…...