【FPGA零基础学习之旅#10】按键消抖模块设计与验证(一段式状态机实现)

🎉欢迎来到FPGA专栏~按键消抖模块设计与验证

- ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹

- ✨博客主页:小夏与酒的博客

- 🎈该系列文章专栏:FPGA学习之旅

- 文章作者技术和水平有限,如果文中出现错误,希望大家能指正🙏

- 📜 欢迎大家关注! ❤️

🎉 目录-按键消抖模块设计与验证

- 一、效果演示

- 二、模块设计

- 三、仿真测试

- 3.1 常规编写

- 3.2 task编写

- 四、仿真模型

一、效果演示

🥝模块设计:

🥝按键消抖模块的完整代码,可直接使用:

//

//模块:按键消抖模块

//key_state:输出消抖之后按键的状态

//key_flag:按键消抖结束时产生一个时钟周期的高电平脉冲

/

module KeyFilter(input Clk,input Rst_n,input key_in,output reg key_flag,output reg key_state

);//按键的四个状态localparamIDLE = 4'b0001,FILTER1 = 4'b0010,DOWN = 4'b0100,FILTER2 = 4'b1000;//状态寄存器reg [3:0] curr_st;//边沿检测输出上升沿或下降沿wire pedge;wire nedge;//计数寄存器reg [19:0]cnt;//使能计数寄存器reg en_cnt;//计数满标志信号reg cnt_full;//计数满寄存器//------<边沿检测电路的实现>------//边沿检测电路寄存器reg key_tmp0;reg key_tmp1;//边沿检测always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginkey_tmp0 <= 1'b0;key_tmp1 <= 1'b0;endelse beginkey_tmp0 <= key_in;key_tmp1 <= key_tmp0;end endassign nedge = (!key_tmp0) & (key_tmp1);assign pedge = (key_tmp0) & (!key_tmp1);//------<状态机主程序>------ //状态机主程序always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)begincurr_st <= IDLE;en_cnt <= 1'b0;key_flag <= 1'b0;key_state <= 1'b1;endelse begincase(curr_st)IDLE:beginkey_flag <= 1'b0;if(nedge)begincurr_st <= FILTER1;en_cnt <= 1'b1;endelsecurr_st <= IDLE;endFILTER1:beginif(cnt_full)beginkey_flag <= 1'b1;key_state <= 1'b0;curr_st <= DOWN;en_cnt <= 1'b0;end else if(pedge)begincurr_st <= IDLE;en_cnt <= 1'b0;endelsecurr_st <= FILTER1;endDOWN:beginkey_flag <= 1'b0;if(pedge)begincurr_st <= FILTER2;en_cnt <= 1'b1;endelsecurr_st <= DOWN;endFILTER2:beginif(cnt_full)beginkey_flag <= 1'b1;key_state <= 1'b1;curr_st <= IDLE;en_cnt <= 1'b0;end else if(nedge)begincurr_st <= DOWN;en_cnt <= 1'b0;endelsecurr_st <= FILTER2;enddefault:begincurr_st <= IDLE;en_cnt <= 1'b0;key_flag <= 1'b0;key_state <= 1'b1;endendcaseendend//------<20ms计数器>------ //20ms计数器//Clk 50_000_000Hz//一个时钟周期为20ns//需要计数20_000_000 / 20 = 1_000_000次always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)cnt <= 20'd0;else if(en_cnt)cnt <= cnt + 1'b1;elsecnt <= 20'd0;endalways@(posedge Clk or negedge Rst_n)beginif(!Rst_n)cnt_full <= 1'b0;else if(cnt == 999_999)cnt_full <= 1'b1;elsecnt_full <= 1'b0;endendmodule🥝RTL视图:

🥝状态转移:

🥝仿真结果:

二、模块设计

🥝模块设计:

| 信号 | 作用 |

|---|---|

| clk | 时钟信号输入 |

| rst_n | 复位信号输入 |

| key_in | 按键信号输入 |

| key_flag | 消抖结束之后的标志位 |

| key_state | 消抖结束之后按键的状态 |

🥝上升沿检测电路:

🥝下降沿检测电路:

🥝边沿检测电路的实现:

检测到下降沿,nedge输出高电平;检测到上升沿,pedge输出高电平。

//------<边沿检测电路的实现>------

//边沿检测电路寄存器

reg key_tmp0;

reg key_tmp1;//边沿检测

always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginkey_tmp0 <= 1'b0;key_tmp1 <= 1'b0;endelse beginkey_tmp0 <= key_in;key_tmp1 <= key_tmp0;end

endassign nedge = (!key_tmp0) & (key_tmp1);//检测到下降沿,nedge输出高电平

assign pedge = (key_tmp0) & (!key_tmp1);//检测到上升沿,pedge输出高电平

🥝一段式状态机设计:

按键的四种状态:

//按键的四个状态

localparamIDLE = 4'b0001,FILTER1 = 4'b0010,DOWN = 4'b0100,FILTER2 = 4'b1000;

计数器:

//------<20ms计数器>------

//20ms计数器

//Clk 50_000_000Hz

//一个时钟周期为20ns

//需要计数20_000_000 / 20 = 1_000_000次//计数寄存器

reg [19:0]cnt;//使能计数寄存器

reg en_cnt;//计数满标志信号

reg cnt_full;//计数满寄存器always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)cnt <= 20'd0;else if(en_cnt)cnt <= cnt + 1'b1;elsecnt <= 20'd0;

endalways@(posedge Clk or negedge Rst_n)beginif(!Rst_n)cnt_full <= 1'b0;else if(cnt == 999_999)cnt_full <= 1'b1;elsecnt_full <= 1'b0;

end

状态机主程序:

//------<状态机主程序>------

//状态机主程序

always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)begincurr_st <= IDLE;en_cnt <= 1'b0;key_flag <= 1'b0;key_state <= 1'b1;endelse begincase(curr_st)IDLE:beginkey_flag <= 1'b0;if(nedge)begincurr_st <= FILTER1;en_cnt <= 1'b1;endelsecurr_st <= IDLE;endFILTER1:beginif(cnt_full)beginkey_flag <= 1'b1;key_state <= 1'b0;curr_st <= DOWN;en_cnt <= 1'b0;end else if(pedge)begincurr_st <= IDLE;en_cnt <= 1'b0;endelsecurr_st <= FILTER1;endDOWN:beginkey_flag <= 1'b0;if(pedge)begincurr_st <= FILTER2;en_cnt <= 1'b1;endelsecurr_st <= DOWN;endFILTER2:beginif(cnt_full)beginkey_flag <= 1'b1;key_state <= 1'b1;curr_st <= IDLE;en_cnt <= 1'b0;end else if(nedge)begincurr_st <= DOWN;en_cnt <= 1'b0;endelsecurr_st <= FILTER2;enddefault:begincurr_st <= IDLE;en_cnt <= 1'b0;key_flag <= 1'b0;key_state <= 1'b1;endendcaseend

end

三、仿真测试

3.1 常规编写

`timescale 1ns/1ns

`define clock_period 20module KeyFilter_tb;reg Clk;reg Rst_n;reg key_in;wire key_flag;wire key_state;KeyFilter KeyFilter0(.Clk(Clk),.Rst_n(Rst_n),.key_in(key_in),.key_flag(key_flag),.key_state(key_state));initial Clk = 1;always#(`clock_period/2) Clk = ~Clk;initial beginRst_n = 1'b0;key_in = 1'b1;#(`clock_period*10);Rst_n = 1'b1;#(`clock_period*10 + 1);key_in = 0;#1000;key_in = 1;#2000;key_in = 0;#1400;key_in = 1;#2600;key_in = 0;#1300;key_in = 1;#200;key_in = 0;#20000100;#50000000;key_in = 1;#2600;key_in = 0;#1000;key_in = 1;#2000;key_in = 0;#1400;key_in = 1;#2600;key_in = 0;#1300;key_in = 1;#200;key_in = 1;#20000100;#50000000;$stop;endendmodule仿真结果:

3.2 task编写

`timescale 1ns/1ns

`define clock_period 20module KeyFilter_tb;reg Clk;reg Rst_n;reg key_in;wire key_flag;wire key_state;KeyFilter KeyFilter0(.Clk(Clk),.Rst_n(Rst_n),.key_in(key_in),.key_flag(key_flag),.key_state(key_state));initial Clk = 1;always#(`clock_period/2) Clk = ~Clk;initial beginRst_n = 1'b0;key_in = 1'b1;#(`clock_period*10);Rst_n = 1'b1;#(`clock_period*10 + 1);#30000;PressKey; #10000;PressKey; #10000;PressKey; #10000;$stop;endreg [15:0]myrand;task PressKey;begin//50次随机时间按下抖动repeat(50)beginmyrand = {$random}%65536;//0~65535#myrand key_in = ~key_in;endkey_in = 0;#50_000_000;//按下稳定//50次随机时间释放抖动repeat(50)beginmyrand = {$random}%65536;//0~65535#myrand key_in = ~key_in;endkey_in = 1;#50_000_000;//释放稳定endendtaskendmodule注意$random随机函数的用法:

$random这一系统函数可以产生一个有符号的32bit随机整数。一般的用法是$random%b,其中b>0。这样就会生成一个范围在(-b+1):(b-1)中的随机数。如果只得到正数的随机数,可采用{$random}%b来产生。

myrand = {$random}%65536;//0~65535

上述语句的作用即是产生了0~65535之间的随机数。

通过repeat语句循环50次,就产生了50次不同的延时效果:

repeat(50)beginmyrand = {$random}%65536;//0~65535#myrand key_in = ~key_in;

end

仿真结果:

四、仿真模型

编写key_model并添加到测试激励文件中:

`timescale 1ns/1nsmodule key_model(key);output reg key;reg [15:0]myrand;initial beginkey = 1'b1;PressKey; #10000;PressKey; #10000;PressKey; #10000;$stop;endtask PressKey;begin//50次随机时间按下抖动repeat(50)beginmyrand = {$random}%65536;//0~65535#myrand key = ~key;endkey = 0;#50_000_000;//按下稳定//50次随机时间释放抖动repeat(50)beginmyrand = {$random}%65536;//0~65535#myrand key = ~key;endkey = 1;#50_000_000;//释放稳定endendtask endmodule修改KeyFilter_tb:

`timescale 1ns/1ns

`define clock_period 20module KeyFilter_tb;reg Clk;reg Rst_n;wire key_in;wire key_flag;wire key_state;KeyFilter KeyFilter0(.Clk(Clk),.Rst_n(Rst_n),.key_in(key_in),.key_flag(key_flag),.key_state(key_state));key_model key_model0(.key(key_in));initial Clk = 1;always#(`clock_period/2) Clk = ~Clk;initial beginRst_n = 1'b0;#(`clock_period*10);Rst_n = 1'b1;#(`clock_period*10 + 1);endendmodule整个激励文件的内部结构:

仿真结果:

🧸结尾

- ❤️ 感谢您的支持和鼓励! 😊🙏

- 📜您可能感兴趣的内容:

- 【FPGA】串口通信讲解-状态机判断数据值

- 【Python】串口通信-与FPGA、蓝牙模块实现串口通信(Python+FPGA)

- 【Arduino TinyGo】【最新】使用Go语言编写Arduino-环境搭建和点亮LED灯

- 【全网首发开源教程】【Labview机器人仿真与控制】Labview与Solidworks多路支配关系-四足爬行机器人仿真与控制

相关文章:

【FPGA零基础学习之旅#10】按键消抖模块设计与验证(一段式状态机实现)

🎉欢迎来到FPGA专栏~按键消抖模块设计与验证 ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹 ✨博客主页:小夏与酒的博客 🎈该系列文章专栏:FPGA学习之旅 文章作者技术和水平有限,如果文中出现错误,希望大…...

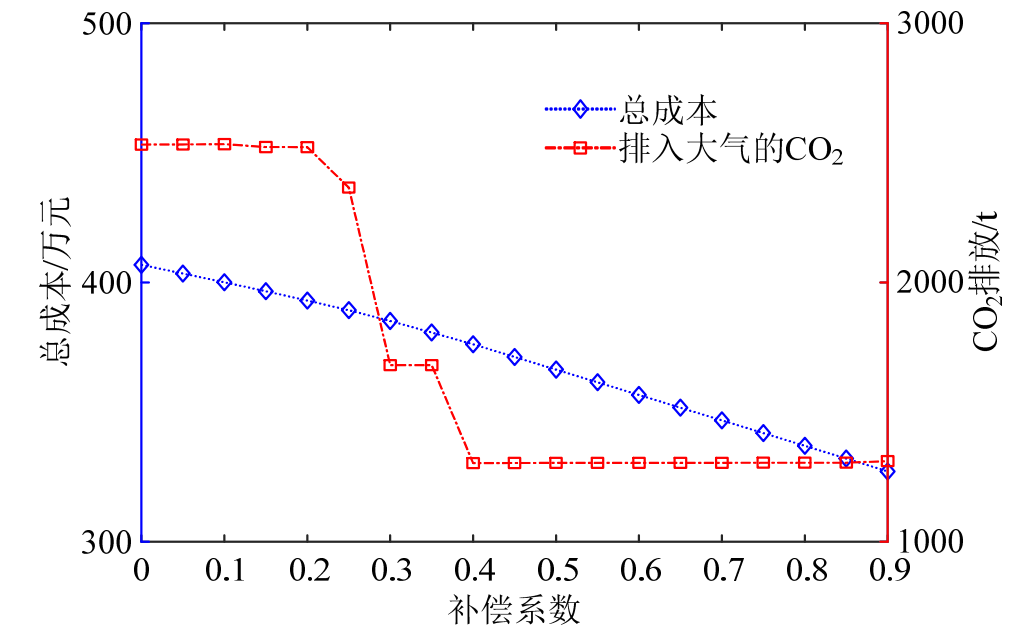

【EI复现】基于阶梯碳交易的含P2G-CCS耦合和燃气掺氢的虚拟电厂优化调度(Matlab代码实现)

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭&a…...

高防cdn和高防服务器有什么不一样?

高防cdn: 相信很多看过我们文章的小伙伴对cdn已经很了解了,cdn的原理很简单,就是构建在网络上的很多个节点,为网站作内容 分发。使用户就近获取所需资源。且分配的cdn节点都是高防节点,每个节点都有防御功能。还…...

ppt怎么压缩?试试这样压缩文件

当PPT文件体积过大时,打开的速度就会很慢,演示的时候刘程度也会受到影响,其次,现在很多平台对于上传的文件是有大小限制的,比如超过100M的文件就无法上传、发送等等,那么,怎么才能压缩PPT文件呢…...

stm32 cubemx ps2无线(有线)手柄

文章目录 前言一、cubemx配置二、代码1.引入库bsp_hal_ps2.cbsp_hal_ps2.h 2.主函数 前言 本文讲解使用cubemx配置PS2手柄实现对手柄的按键和模拟值的读取。 很简单,库已经封装好了,直接就可以了。 文件 一、cubemx配置 这个很简单,不需要…...

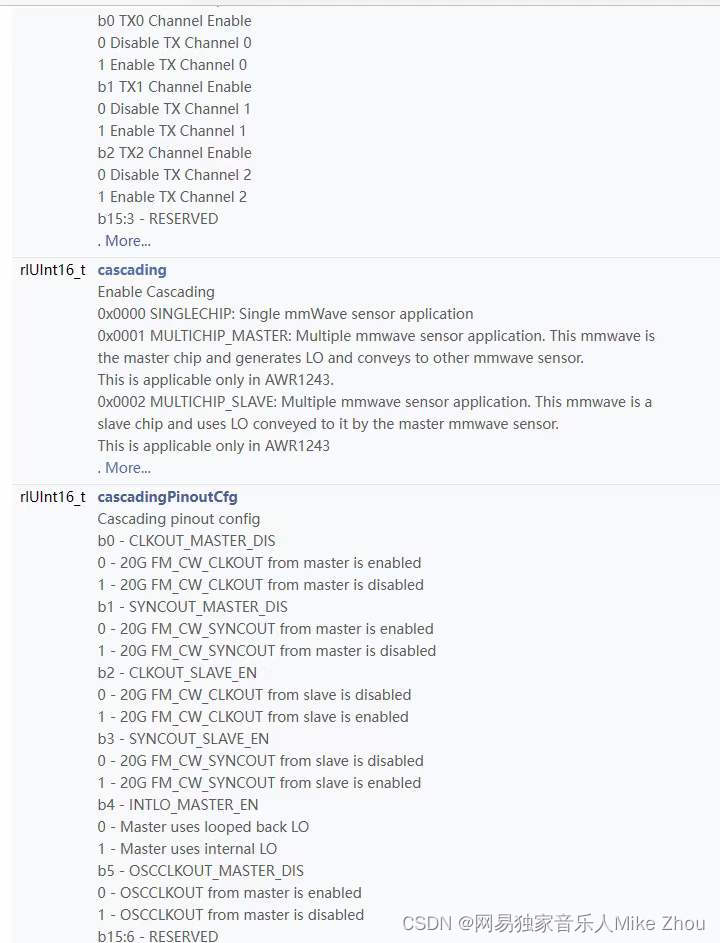

【TI毫米波雷达笔记】sdk传参时的type避坑

【TI毫米波雷达笔记】sdk传参时的type避坑 这个函数要传一个结构体进去 然后结构体里面有个adcoutcfg结构体变量 adcoutcfg结构体里面共有三个变量 一个adcbitformat结构体 另外两保留 点开adcbitformat结构体发现是个32位段 一共四级结构体 那么请问 为什么adcoutcfg变量不直…...

【算法挨揍日记】day02——双指针算法_快乐数、盛最多水的容器

202. 快乐数 202. 快乐数https://leetcode.cn/problems/happy-number/ 题目: 编写一个算法来判断一个数 n 是不是快乐数。 「快乐数」 定义为: 对于一个正整数,每一次将该数替换为它每个位置上的数字的平方和。然后重复这个过程直到这个…...

【Hilog】鸿蒙系统日志源码分析

【Hilog】鸿蒙系统日志源码分析 Hilog采用C/S结构,Hilogd作为服务端提供日志功能。Client端通过API调用(最终通过socket通讯)与HiLogd打交道。简易Block图如下。 这里主要分析一下。Hilog的读、写、压缩落盘,以及higlog与android…...

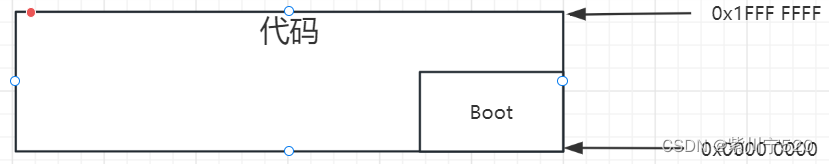

keil下载程序具体过程4:flash下载算法

引言 本篇文章将介绍flash算法文件,阐述从jlink如何下载镜像文件写入到内部的falsh。 一、XIP 在谈flash下载算法文件时,先说明XIP是什么。 芯片的启动方式有很多种:可以从RAM中启动、内部的flash、外部的flash等等(还有从sd卡、…...

如何快速的让自己从月入2000变成月入两万?

从月入2000变成月入两万 前言我们可以这么做:1.提升自己的技能:2.寻找更好的工作机会:寻找更好的工作机会是一个重要的目标,以下是几个建议: 3.开展副业或兼职工作:4.创业或投资:5.构建个人品牌…...

使用 CycleGAN 进行图像到图像转换

介绍 在人工智能和计算机视觉领域,CycleGAN 是一项非凡的创新,它重新定义了我们感知和操作图像的方式。这种尖端技术彻底改变了图像到图像的转换,实现了领域之间的无缝转换,例如将马变成斑马或将夏日风景变成雪景。在本文中,我们将揭开 CycleGAN 的魔力,并探索其在各个领…...

Svg使用和注册components文件夹内部全部为全局组件

1.安装SVG依赖插件 pnpm install vite-plugin-svg-icons -D 2. 封装SvgIcon <template><div><svg :style"{ width: width, height: height }"><use :xlink:href"prefix name" :fill"color"></use></svg>…...

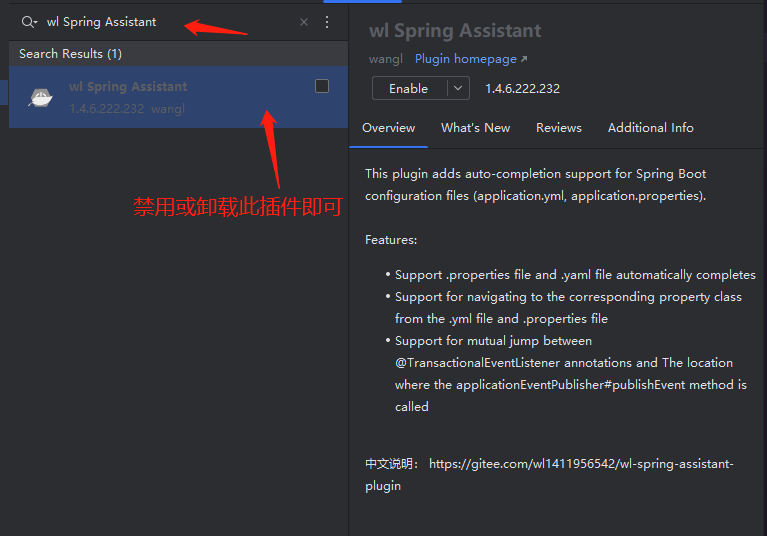

解决idea编辑application.yml文件或properties文件没有提示问题

注意:这里说的没有提示,是针对application.properties和application.yml文件 解决办法:在idea的插件面板中,禁用或卸载 wl Spring Assistant插件即可解决问题。...

前端懒加载

懒加载的概念 懒加载也叫做延迟加载、按需加载,指的是在长网页中延迟加载图片数据,是一种较好的网页性能优化的方式。在比较长的网页或应用中,如果图片很多,所有的图片都被加载出来,而用户只能看到可视窗口的那一部分…...

【手动配置ip地址后,电脑仍自动分配ip的问题】

现象 手动给电脑分配了一个ipv4地址,但是电脑会自动分配一个169开头的ipv4,导致虽然可以上网,但访问不了局域网内其他的设备(我配置的另一个网关,所以可以上网) 原因 ip地址冲突了,把电脑的i…...

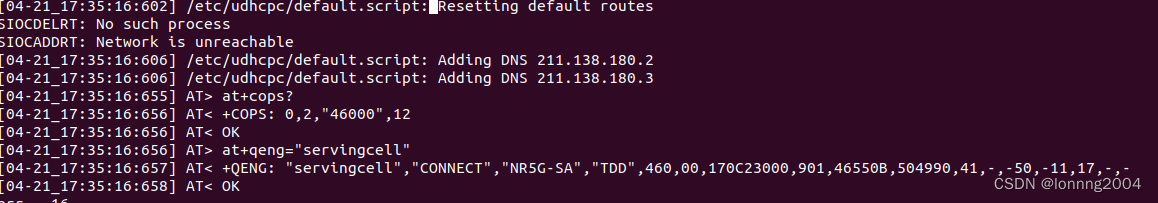

移远RM500U-CN模块直连嵌入式ubuntu实现拨号上网

目录 1 平台: 2 需要准备的资料 3 参考文档 4 编译环境与驱动移植 4.1 内核驱动添加厂家ID和产品ID 4. 2.添加零包处理 4.3 增加复位恢复机制 4.4 增加批量输出 批量输出 URB 的数量和容量 的数量和容量 4.5 内核配置与编译 5 QM500U-CN拨号(在开…...

【JavaWeb】MySQL基础操作

1 通用语法规则 SQL语句可以单行或者多行书写,以分号结尾SQL语句不区分大小写,关键字建议使用大写单行注释 --注释内容(通用) # 注释内容(MySQL独有)多行注释 /* 注释内容 */ 2 语句 数据库 -- 查…...

【Tool】虚拟机安装与调试与设置与主机共享文件

前言 安装了vm17,实现了与主机文件共享, 步骤 下载虚拟机(试用版) Download VMware Workstation Pro 双击安装 暂不激活或者 使用如下激活码 KRNJX-22GXY-HCW46-MWYHY-YWRDB RDHTN-YFFKY-8YVR7-Q996Y-K74X3 N2XRH-GCH84-MV…...

Spring中的接口使用

技术主题 在我们的项目中,经常会使用一些注解,注解带给我们代码简洁,本质是用于在代码中添加元数据信息,从而实现更加灵活、高效和可维护的代码结构。 技术原理 注解一@Target(ElementType.TYPE) 这个注解表示被它修饰的注解可以应用在类、接口、枚举等类型上。换句话说…...

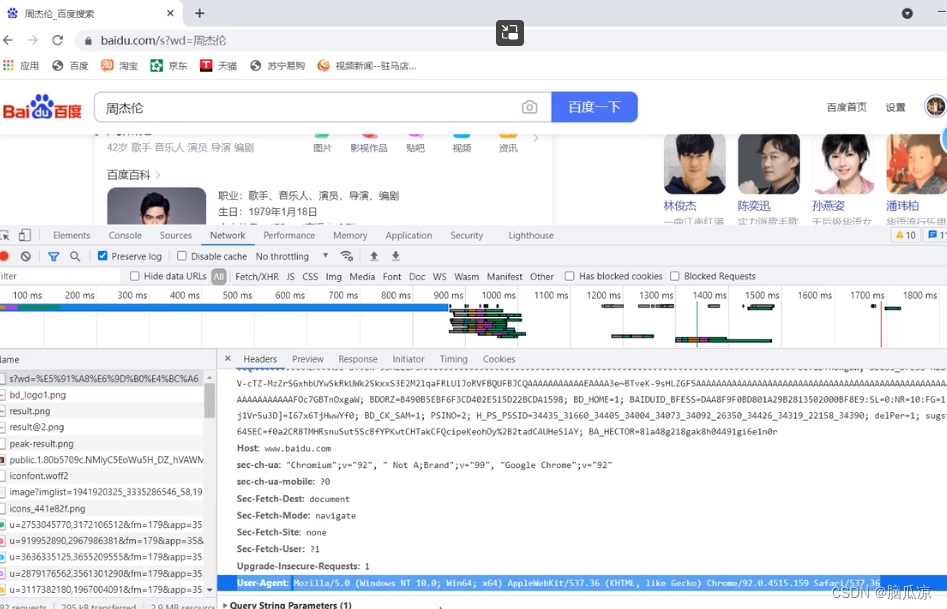

爬虫017_urllib库_get请求的quote方法_urlencode方法_---python工作笔记036

按行来看get请求方式 比如这个地址 上面这个地址复制粘贴过来以后 可以看到周杰伦变成了一堆的Unicode编码了 所以这个时候我们看,我们说https这里,用了UA反爬,所以这里 我们构建一个自定义的Request对象,里面要包含Us...

终极指南:5分钟免费激活Windows和Office的智能解决方案

终极指南:5分钟免费激活Windows和Office的智能解决方案 【免费下载链接】KMS_VL_ALL_AIO Smart Activation Script 项目地址: https://gitcode.com/gh_mirrors/km/KMS_VL_ALL_AIO 还在为Windows系统频繁弹出激活提示而烦恼吗?Office文档突然变成只…...

终极指南:如何用WhisperX实现70倍速离线语音识别与精准时间戳

终极指南:如何用WhisperX实现70倍速离线语音识别与精准时间戳 【免费下载链接】whisperX WhisperX: Automatic Speech Recognition with Word-level Timestamps (& Diarization) 项目地址: https://gitcode.com/gh_mirrors/wh/whisperX 你是否曾面临重要…...

如何快速突破AI编程工具限制:Cursor Pro免费使用的终极解决方案指南

如何快速突破AI编程工具限制:Cursor Pro免费使用的终极解决方案指南 【免费下载链接】cursor-free-vip [Support 0.45](Multi Language 多语言)自动注册 Cursor Ai ,自动重置机器ID , 免费升级使用Pro 功能: Youve rea…...

Qwen3-4B-Thinking部署教程:Ubuntu/CentOS系统vLLM环境适配

Qwen3-4B-Thinking部署教程:Ubuntu/CentOS系统vLLM环境适配 1. 模型简介 Qwen3-4B-Thinking-2507-Gemini-2.5-Flash-Distill是一个基于54.4百万个由Gemini 2.5 Flash生成的token训练而成的文本生成模型。该模型旨在提炼Gemini-2.5 Flash的行为模式、推理轨迹、输出…...

项目解决方案:食堂反浪费AI智能监督系统项目解决方案

目录 第一章 项目背景 1.1 国家粮食节约战略要求 1.2 传统管理模式局限性 1.3 AI技术成熟提供解决方案 1.4 先期成效验证 第二章 需求确认 2.1 实时监测与即时预警需求 2.2 多层级数据管理需求 2.3 AI识别精度与适应性需求 2.4 周期性分析报告需求 第三章 需要解决的…...

终极解决方案:5分钟突破百度网盘限速,实现10倍下载加速

终极解决方案:5分钟突破百度网盘限速,实现10倍下载加速 【免费下载链接】baidu-wangpan-parse 获取百度网盘分享文件的下载地址 项目地址: https://gitcode.com/gh_mirrors/ba/baidu-wangpan-parse 想象一下,当你急需下载一份重要的学…...

终极指南:如何利用MATLAB工具箱进行基因组尺度代谢网络分析

终极指南:如何利用MATLAB工具箱进行基因组尺度代谢网络分析 【免费下载链接】cobratoolbox The COnstraint-Based Reconstruction and Analysis Toolbox. Documentation: 项目地址: https://gitcode.com/gh_mirrors/co/cobratoolbox COBRA工具箱是一个专业的…...

2025最权威的AI辅助写作平台实测分析

Ai论文网站排名(开题报告、文献综述、降aigc率、降重综合对比) TOP1. 千笔AI TOP2. aipasspaper TOP3. 清北论文 TOP4. 豆包 TOP5. kimi TOP6. deepseek 1. 在内容创作里头,降低人工智能生成内容所占比例,也就是降低AIGC率&…...

别再只盯着CNN了!用ViT的cls token搞定图像分类,保姆级原理拆解

从会议主持人到图像分类:ViT中cls token的全局智慧 想象你正在组织一场跨部门会议,每个参会者都带着自己的专业见解。作为主持人,你需要倾听所有人的发言,提炼关键信息,最终形成一份综合报告——这正是Vision Transfor…...

)

BGP负载分担配置避坑指南:如何让流量在eBGP和iBGP链路上真正跑起来(附排错命令)

BGP负载分担实战手册:从原理到排错的深度解析 在数据中心互联和跨国企业组网场景中,BGP协议的负载分担能力直接影响着关键业务的传输质量和链路利用率。许多工程师在配置maximum load-balancing命令后常遇到一个尴尬现象——设备确实学习到了多条等价路由…...