牛客网Verilog刷题 | 入门特别版本

文章目录

- 1、 VL1 输出1

- 2、VL2 wire连线

- 3、 VL3 多wire连接

- 4、VL4 反相器

- 5、VL5 与门

- 6、VL6 NOR 门

- 7、VL7 XOR 门

- 8、VL8 逻辑运算

- 10、VL10 逻辑运算2

- 11、VL11 多位信号

- 12、VL12 信号顺序调整

- 13、VL13 位运算与逻辑运算

- 14、VL14 对信号按位操作

- 15、VL15 信号级联合并

- 16、VL16 信号反转输出

- 17、VL17 三元操作符

1、 VL1 输出1

描述

构建一个没有输入和一个输出常数1的输出的电路

输入描述:

无

输出描述:

输出信号为one

`timescale 1ns/1nsmodule top_module(output one

);assign one = 1;endmodule

2、VL2 wire连线

描述

创建一个具有一个输入和一个输出的模块,其行为类似于电路上的连线。

输入描述:

输入信号in0

输出描述:

输出信号out1

`timescale 1ns/1nsmodule wire0( input in0, output out1);assign out1 = in0;

endmodule

3、 VL3 多wire连接

描述

创建一个具有 2个输入和 3个输出的模块,使用线连接的方式:

a -> z

b -> x

b -> y

输入描述:

input wire a b

输出描述:

output wire x y z

`timescale 1ns/1nsmodule top_module(a, b, x, y, z);input a, b;output x, y, z;assign x = b;assign y = b;assign z = a;endmodule

4、VL4 反相器

描述

输出输入信号的值的相反的值

输入描述:

in

输出描述:

out

`timescale 1ns/1nsmodule top_module(input in,output out

);assign out = ~in;

endmodule

5、VL5 与门

描述

创建实现 AND 门的模块,输入有三个wire,将三个信号(a b c)进行与操作,请思考在实际电路需要几个与门?请写出对应的RTL

输入描述:

a b c

输出描述:

d

`timescale 1ns/1ns

module top_module( input a, input b, input c,output d );assign d = a & b & c;endmodule

6、VL6 NOR 门

描述

创建实现 OR和NOR 的模块,NOR 门是输出反相的 OR 门。

c 是 nor输出,d是or输出

输入描述:

a b

输出描述:

c d

`timescale 1ns/1nsmodule top_module( input a, input b, output c,output d);assign c = a ~| b;assign d = a | b;endmodule

7、VL7 XOR 门

描述

创建一个实现 XOR 门的模块

输入描述:

a b

输出描述:

c

`timescale 1ns/1nsmodule top_module( input a, input b, output c );assign c = a ^ b;endmodule

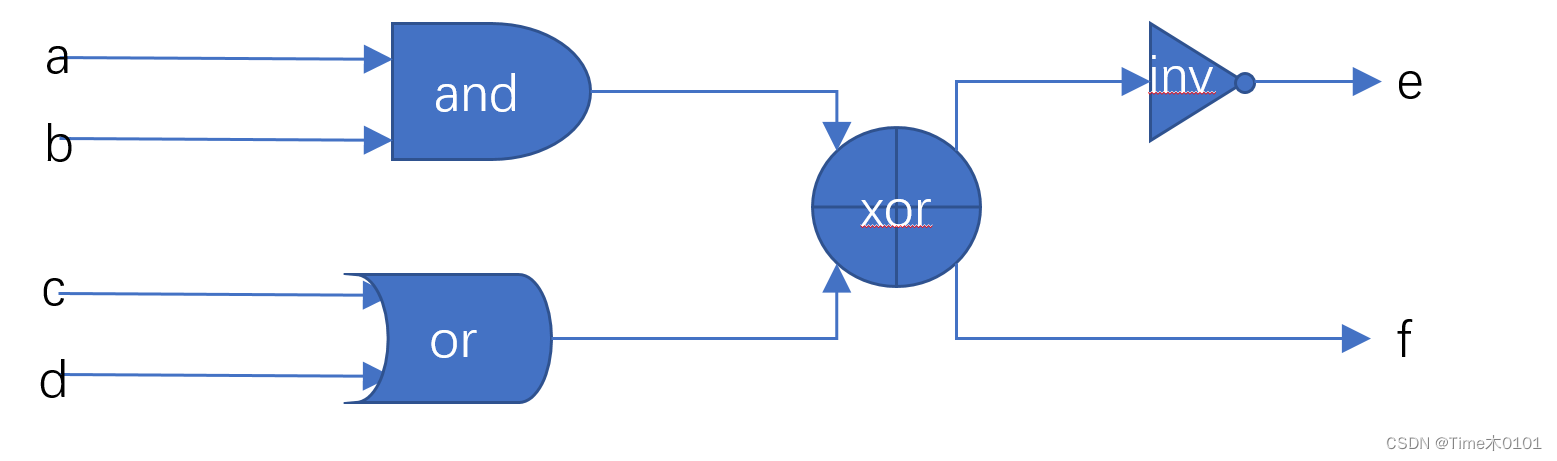

8、VL8 逻辑运算

描述

写出如图的rtl逻辑,限制使用最多四次assign

输入描述:

a b c d

输出描述:

e f

`timescale 1ns/1nsmodule top_module (input a,input b,input c,input d,output e,output f );wire out_xor;assign out_xor = (a & b) ^ (c | d);assign e = ~out_xor;assign f = out_xor;endmodule

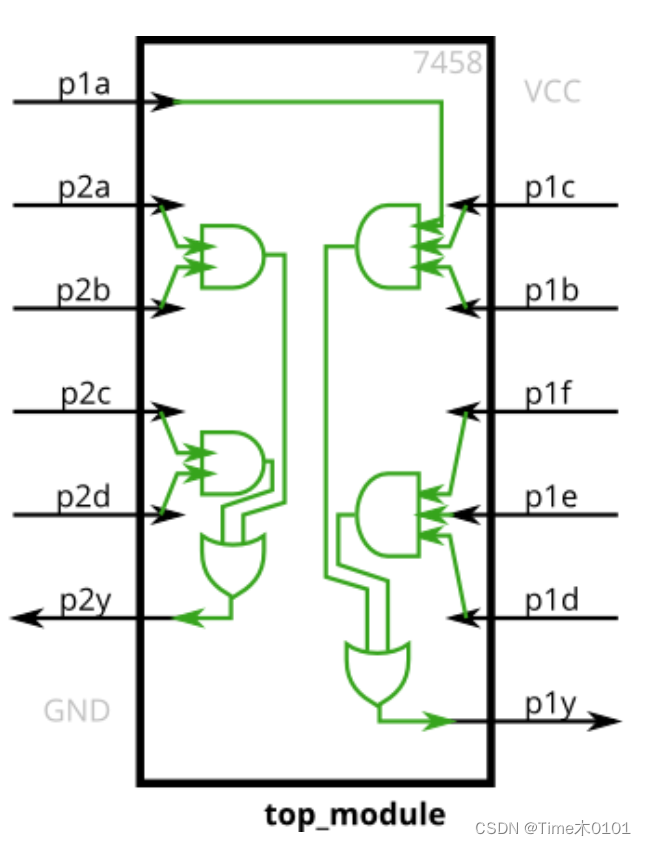

9、VL9 模拟逻辑芯片

描述

下图为某芯片的逻辑,请通过RTL实现它的功能

输入描述:

p1a, p1b, p1c, p1d, p1e, p1f,p2a, p2b, p2c, p2d

输出描述:

p1y,p2y

`timescale 1ns/1nsmodule top_module ( input p1a, p1b, p1c, p1d, p1e, p1f,output p1y,input p2a, p2b, p2c, p2d,output p2y );assign p1y = (p1a & p1b & p1c) | (p1f & p1e & p1d);assign p2y = (p2a & p2b) | (p2c & p2d);

endmodule

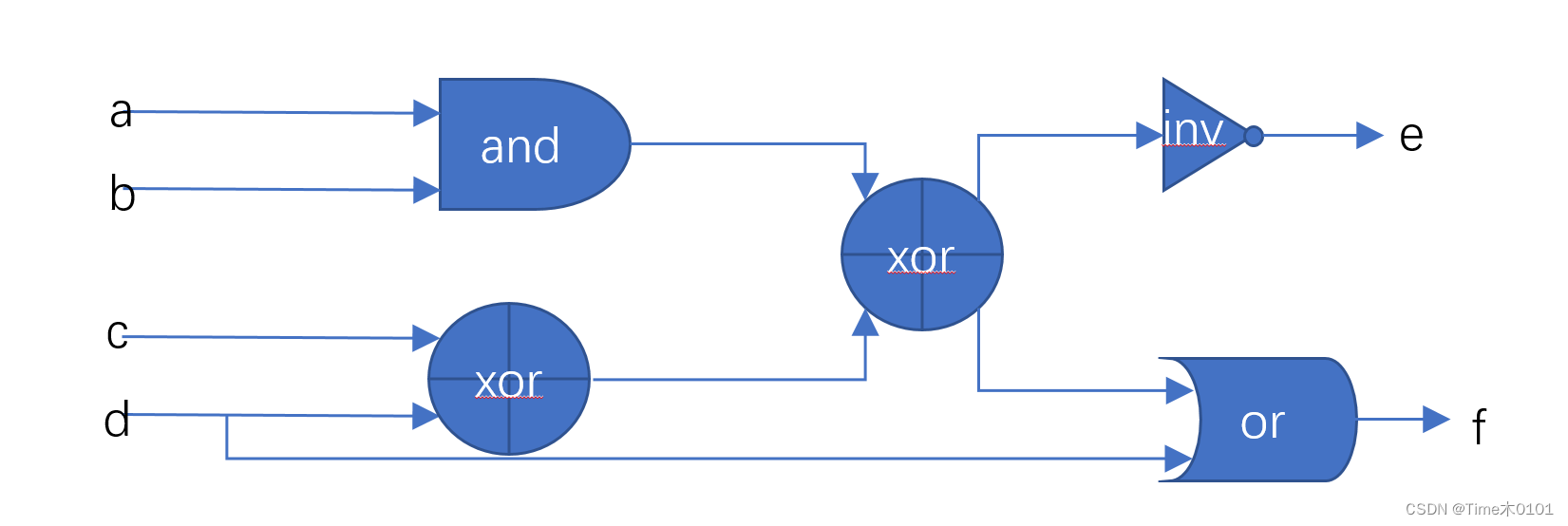

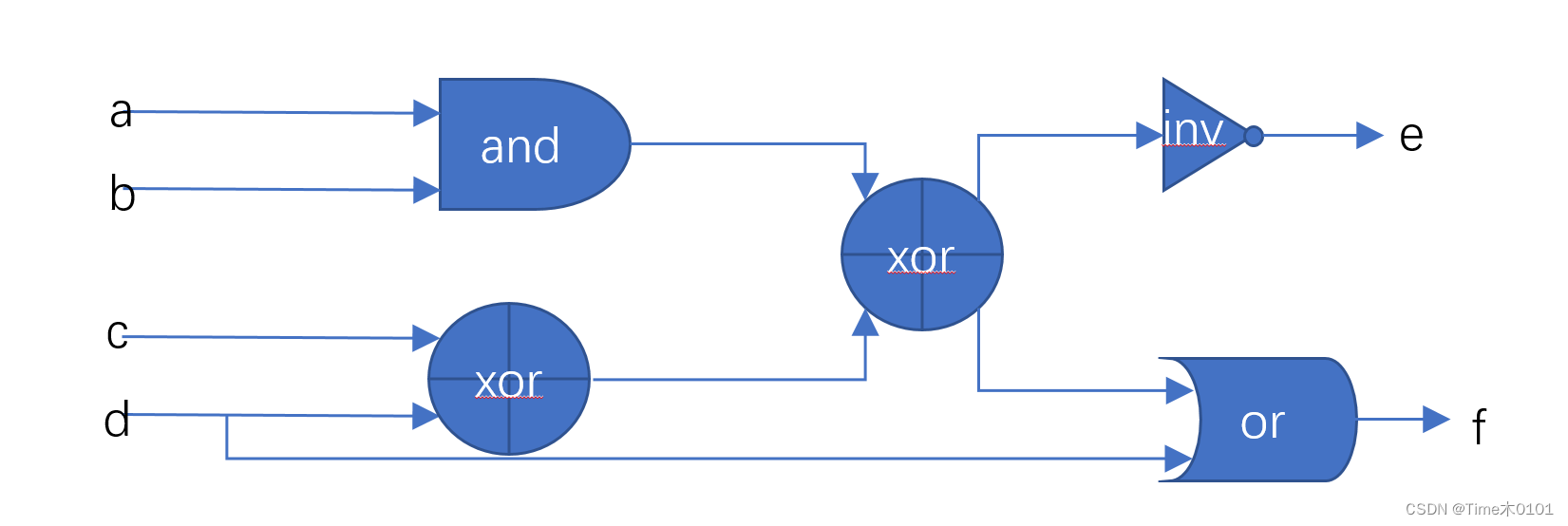

10、VL10 逻辑运算2

描述

根据下述逻辑,给出对应的module设计

输入描述:

a b c d

输出描述:

e f

`timescale 1ns/1nsmodule top_module (input a,input b,input c,input d,output e,output f );wire out_xor;assign out_xor = (a & b) ^ (c ^ d);assign e = ~out_xor;assign f = out_xor | d;

endmodule

11、VL11 多位信号

描述

构建一个具有一个3位输入in的信号[2:0],将其分成三个独立的输出a b c(从2到0)

输入描述:

in

输出描述:

a b c

`timescale 1ns/1nsmodule top_module(in, a, b, c

);input [2:0] in;output a, b, c;assign a = in[2];assign b = in[1];assign c = in[0];endmodule

12、VL12 信号顺序调整

描述

一个16位信号in包含四个四位数[3:0]a[3:0]b[3:0]c[3:0]d,将它们顺序倒置为dcba输出,输出out

输入描述:

in

输出描述:

out

`timescale 1ns/1nsmodule top_module(in, out

);input [15:0] in;output [15:0] out;assign out = { in[3:0], in[7:4], in[11:8], in[15:12] };

endmodule

13、VL13 位运算与逻辑运算

描述

现有一个模块,输入信号为[2:0]a和[2:0]b,请输出信号的按位或[2:0]c和或信号d

输入描述:

[2:0]a [2:0]b

输出描述:

[2:0]c d

`timescale 1ns/1nsmodule top_module(input [2:0] a, input [2:0] b, output [2:0] c,output d

);assign c = a | b;assign d = a || b;

endmodule

14、VL14 对信号按位操作

描述

将一个五输入的信号分别进行的每一位进行: 全部按位与;全部按位或;全部按位异或

输入描述:

[4:0]in

输出描述:

out_and, out_or, out_xor

`timescale 1ns/1nsmodule top_module( input [4:0] in,output out_and,output out_or,output out_xor

);assign out_and = & in;assign out_or = | in;assign out_xor = ^ in;

endmodule

15、VL15 信号级联合并

描述

将6个输入信号串联转为四个信号输出,输入信号为[4:0] a[4:0] b[4:0]c [4:0]d [4:0]e [4:0]f,末尾增加一个宽度为两位的3,形成32位长度后,按照从前到后的顺序输出[7:0]w [7:0]x [7:0]y [7:0]z

输入描述:

[4:0] a[4:0] b[4:0]c [4:0]d [4:0]e [4:0]f

输出描述:

[7:0]w [7:0]x [7:0]y [7:0]z

在`timescale 1ns/1nsmodule top_module(input [4:0] a, b, c, d, e, f,output [7:0] w, x, y, z );assign { w, x, y, z } = {a, b, c, d, e, f, 2'b11};

endmodule

16、VL16 信号反转输出

描述

输入一个16位的信号in,将其从低位到高位输出(即反转顺序输出)为out

输入描述:

[15:0] in

输出描述:

[15:0] out

`timescale 1ns/1nsmodule top_module(input [15:0] in,output [15:0] out

);reg [15:0] out;integer i;always@(*)beginfor(i=0; i<=15; i=i+1) beginout[15-i] = in[i];endend

endmodule

个人完成90%,这里一开始用initial总是不成功

需要搞清楚 always 和initial的用法。

17、VL17 三元操作符

描述

给定四个无符号数字,找到最大值。不使用if进行判断,尽量少使用语句的情况下完成。

输入描述:

[7:0]a b c d

输出描述:

[7:0] max

`timescale 1ns/1nsmodule top_module(input [7:0] a, b, c, d,output [7:0] max);assign max = (((a >= b) ? a:b)>=((c>=d)? c:d)) ?((a >= b) ? a:b):((c>=d) ? c:d);endmodule

注:一开始分开比较测试但就是 不用过,最后干脆就直接一行搞定,既然尽量少使用语句,那就一行。

相关文章:

牛客网Verilog刷题 | 入门特别版本

文章目录 1、 VL1 输出12、VL2 wire连线3、 VL3 多wire连接4、VL4 反相器5、VL5 与门6、VL6 NOR 门7、VL7 XOR 门8、VL8 逻辑运算10、VL10 逻辑运算211、VL11 多位信号12、VL12 信号顺序调整13、VL13 位运算与逻辑运算14、VL14 对信号按位操作15、VL15 信号级联合并16、VL16 信…...

ROS通信机制之话题(Topics)的发布与订阅以及自定义消息的实现

我们知道在ROS中,由很多互不相干的节点组成了一个复杂的系统,单个的节点看起来是没起什么作用,但是节点之间进行了通信之后,相互之间能够交互信息和数据的时候,就变得很有意思了。 节点之间进行通信的一个常用方法就是…...

容灾设备系统组成,容灾备份系统组成包括哪些

随着信息技术的快速发展,企业对数据的需求越来越大,数据已经成为企业的核心财产。但是,数据安全性和完整性面临巨大挑战。在这种环境下,容灾备份系统应运而生,成为保证企业数据安全的关键因素。下面我们就详细介绍容灾…...

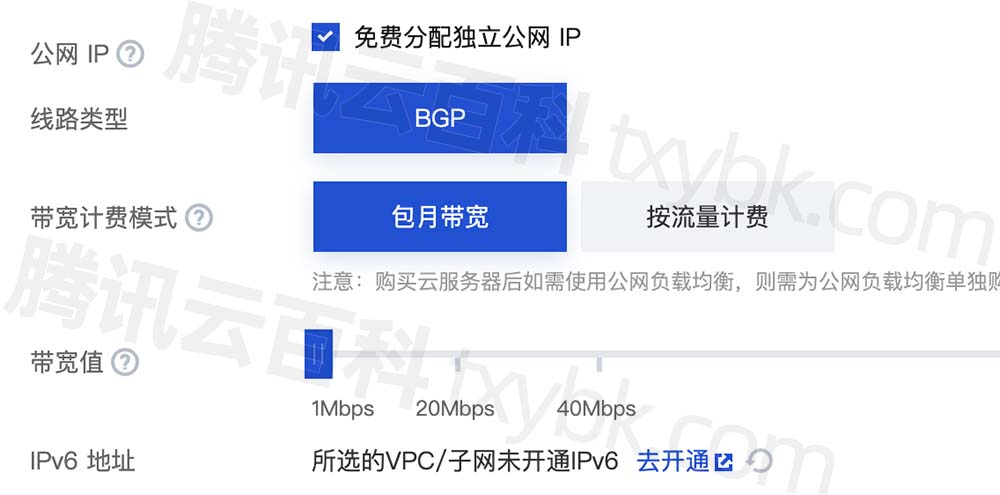

腾讯云服务器租用价格表_一年、1个月和1小时报价明细

腾讯云服务器租用费用表:轻量应用服务器2核2G4M带宽112元一年,540元三年、2核4G5M带宽218元一年,2核4G5M带宽756元三年、云服务器CVM S5实例2核2G配置280.8元一年、GPU服务器GN10Xp实例145元7天,腾讯云服务器网长期更新腾讯云轻量…...

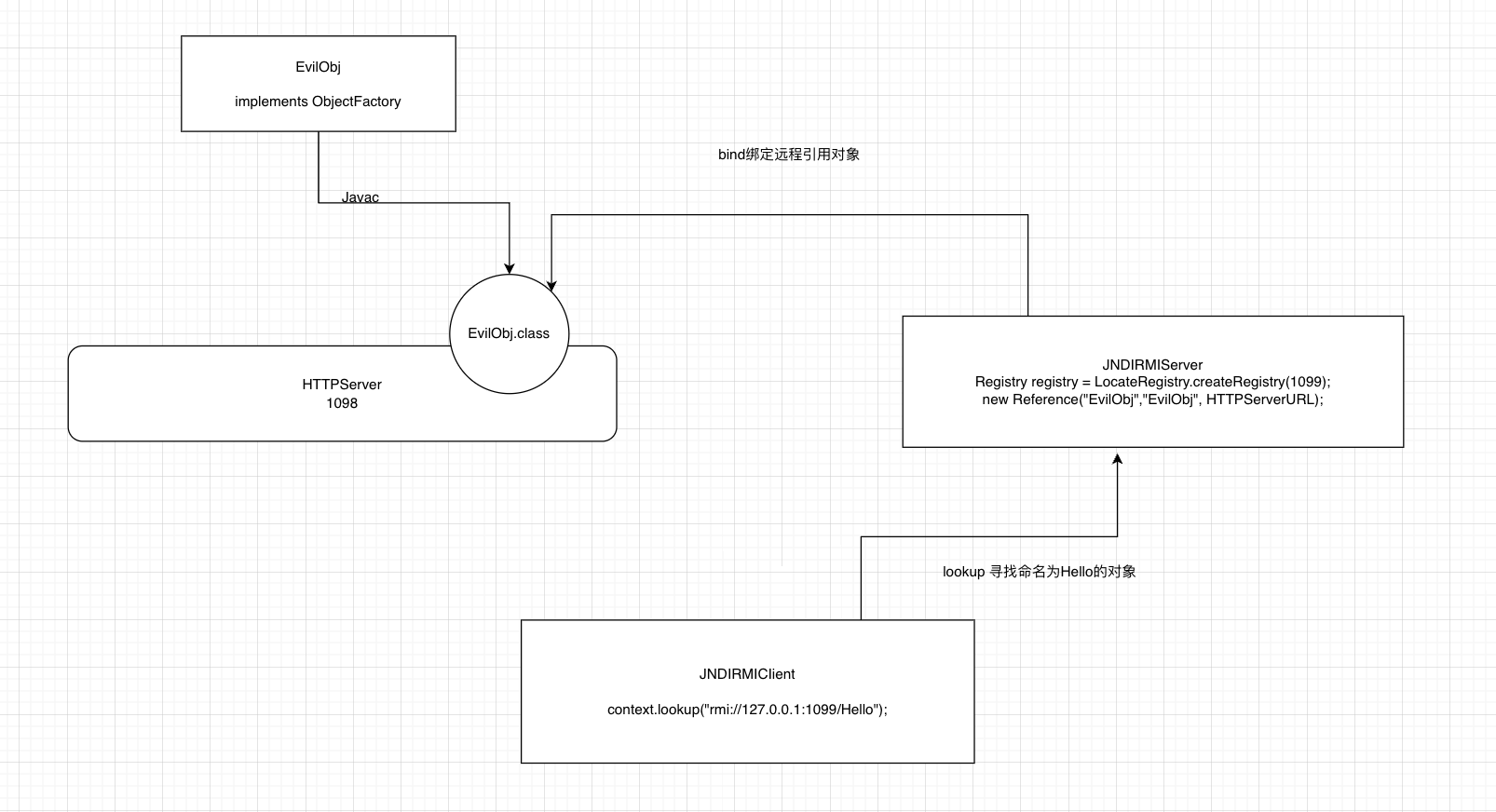

【java安全】JNDI注入概述

文章目录 【java安全】JNDI注入概述什么是JNDI?JDNI的结构InitialContext - 上下文Reference - 引用 JNDI注入JNDI & RMI利用版本:JNDI注入使用Reference 【java安全】JNDI注入概述 什么是JNDI? JNDI(Java Naming and Directory Interf…...

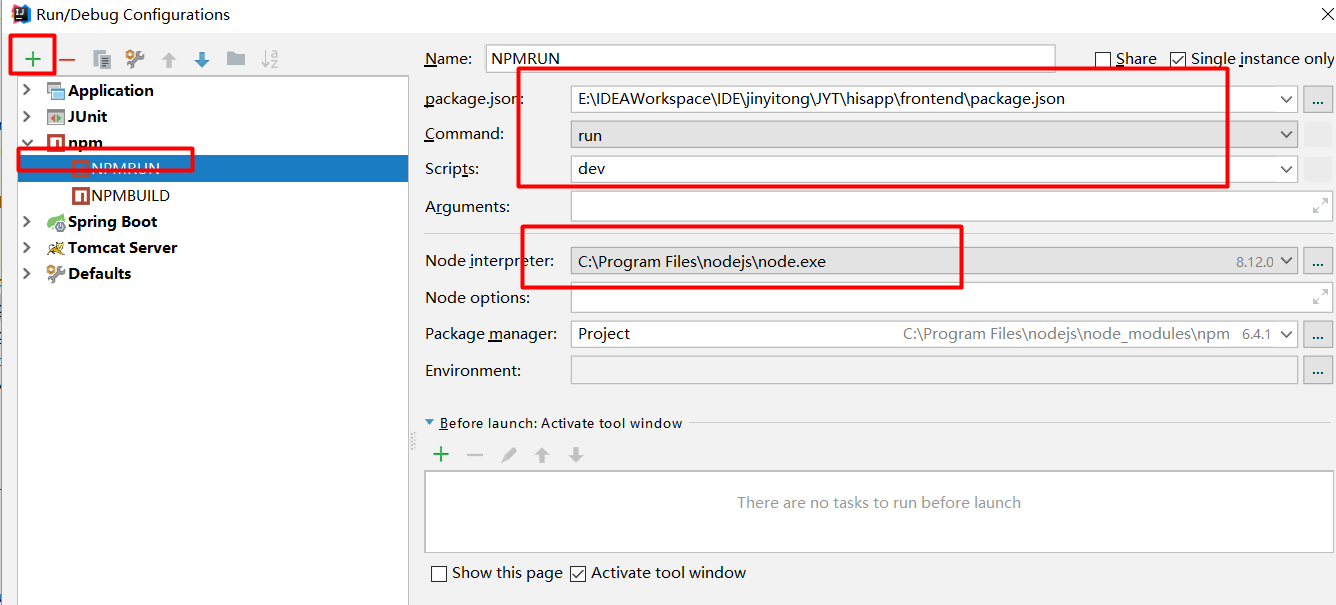

零基础如何使用IDEA启动前后端分离中的前端项目(Vue)?

一、在IDEA中配置vue插件 点击File-->Settings-->Plugins-->搜索vue.js插件进行安装,下面的图中我已经安装好了 二、搭建node.js环境 安装node.js 可以去官网下载:安装过程就很简单,直接下一步就行 测试是否安装成功:要…...

生产者以及消费者)

laravel实现AMQP(rabbitmq)生产者以及消费者

基于php-amqplib/php-amqplib组件适配laravel框架的amqp封装库 支持便捷可配置的队列工作模式 官网详情 在此基础上可支持延迟消息、死信队列等机制。 环境要求: PHP版本: ^7.3|^8.0 需要开启的扩展: socket 其他: 如果需要实现延迟任务需要安装对应版本的ra…...

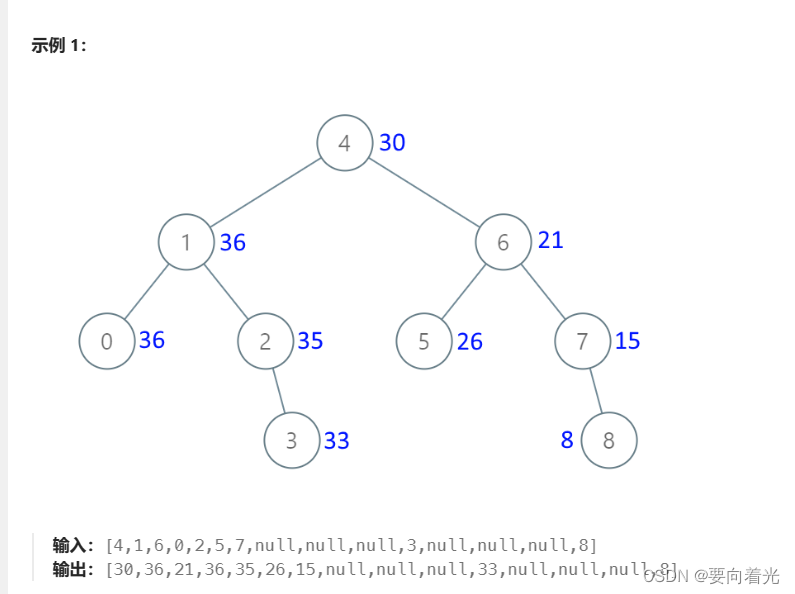

LeetCode——二叉树篇(九)

刷题顺序及思路来源于代码随想录,网站地址:https://programmercarl.com 目录 669. 修剪二叉搜索树 108. 将有序数组转换为二叉搜索树 538. 把二叉搜索树转换为累加树 669. 修剪二叉搜索树 给你二叉搜索树的根节点 root ,同时给定最小边界…...

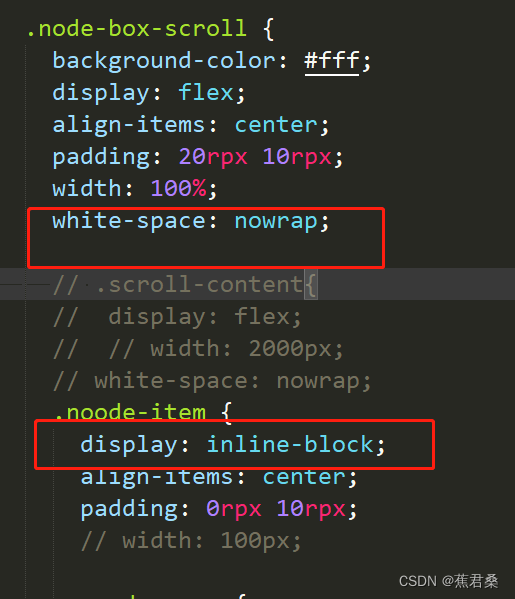

uniapp scroll-view横向滚动无效,scroll-view子元素flex布局不生效

要素排查: 1.scroll-x属性需要开启,官方类型是Boolean,实际字符串也行。 2scroll-view标签需要给予一个固定宽度,可以是百分百也可以是固定宽度或者100vw。 3.子元素需要设置display: inline-block(行内块元素&#x…...

无涯教程-进程 - 简介

进程间通信就是在不同进程之间传播或交换信息,那么不同进程之间存在着什么双方都可以访问的介质呢?进程的用户空间是互相独立的,一般而言是不能互相访问的,唯一的例外是共享内存区。另外,系统空间是“公共场所”,各进…...

HTML番外篇(四)-HTML5新增元素-CSS常见函数-理解浏览器前缀-BFC

一、HTML5新增元素 1.HTML5语义化元素 在HMTL5之前,我们的网站分布层级通常包括哪些部分呢? header、nav、main、footer ◼ 但是这样做有一个弊端: 我们往往过多的使用div, 通过id或class来区分元素;对于浏览器来说这些元素不…...

自适应学习率)

机器学习之Adam(Adaptive Moment Estimation)自适应学习率

Adam(Adaptive Moment Estimation)是一种常用的优化算法,特别适用于训练神经网络和深度学习模型。它是一种自适应学习率的优化算法,可以根据不同参数的梯度信息来动态调整学习率,以提高训练的效率和稳定性。 Adam算法…...

深入理解Linux权限管理:保护系统安全的重要措施

Linux操作系统以其稳定性、可靠性和灵活性而受到广泛使用。其中一个关键特性是其强大的权限管理系统,它可以保护系统资源和用户数据的安全性。本文将深入探讨Linux权限管理的概念、原则和实践,帮助您理解如何正确配置和管理权限,以确保系统的…...

:消费者拦截器的使用)

kafka复习:(20):消费者拦截器的使用

一、定义消费者拦截器(只消费含"sister"的消息) package com.cisdi.dsp.modules.metaAnalysis.rest;import org.apache.kafka.clients.consumer.ConsumerInterceptor; import org.apache.kafka.clients.consumer.ConsumerRecord; import org.…...

水库大坝安全监测的主要内容包括哪些?

在水库大坝的实时监测中,主要任务是通过无线传感网络监测各个监测点的水位、水压、渗流、流量、扬压力等数据,并在计算机上用数据模式或图形模式进行实时反映,以掌握整个水库大坝的各项变化情况。大坝安全监测系统能实现全天候远程自动监测&a…...

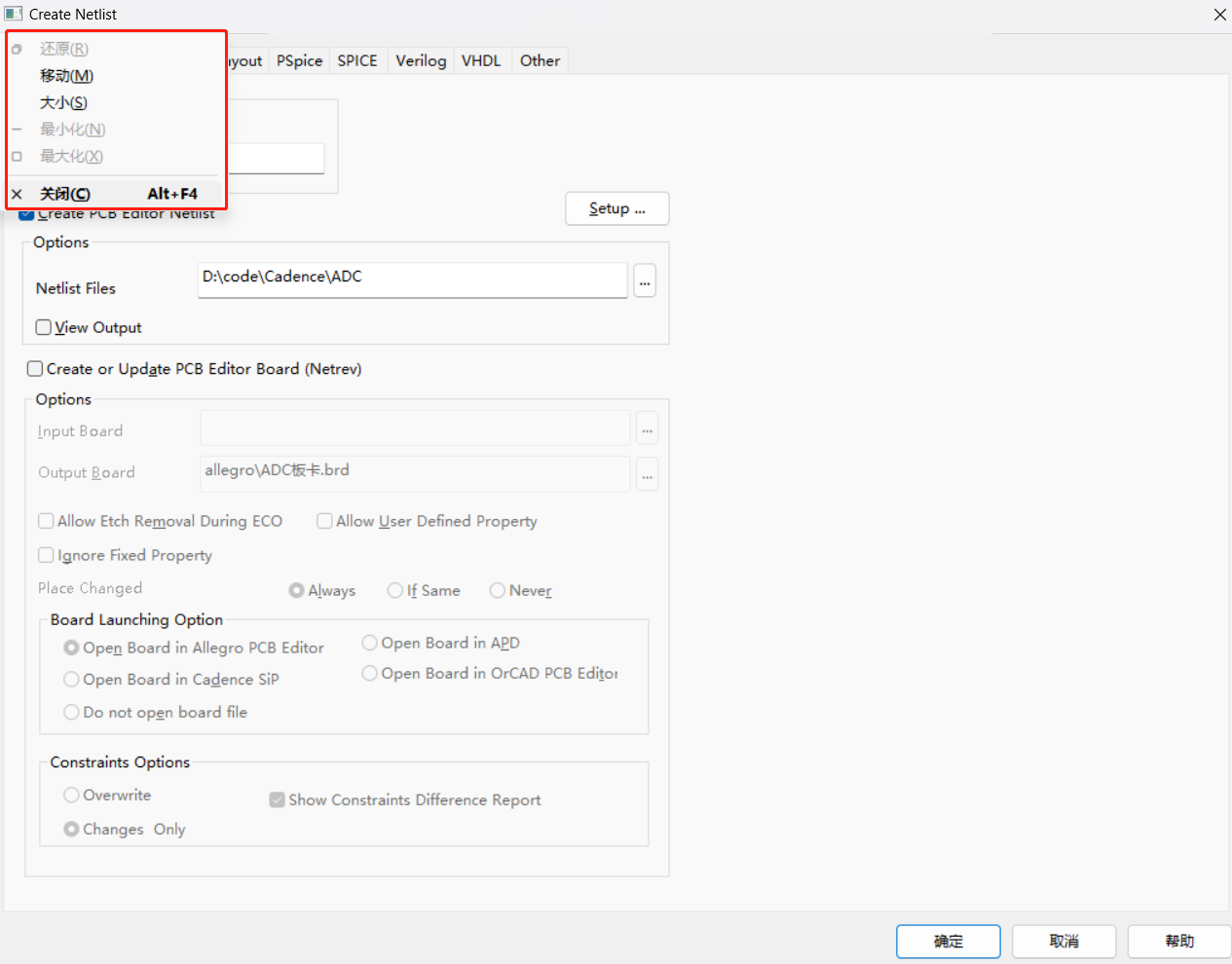

Cadence软件屏幕显示问题

问题 就是今天打开Cadence软件想导出网表看一下,发现没有显示确定按钮什么的,那个窗口也是无语,不能移动,缩放也只能左右缩放,还不能缩小什么的,真的醉了,后面就是调整窗口的分辨率。 因为我最…...

访问服务器快慢的因素

我们在租用服务器的过程中,可能在访问速度方面,会受到某些因素影响,如果您要进行此项业务,进行一些简单的了解 是非常的有必要的,下面壹基比小鑫带大家一起去做个具体的探讨吧。 对于服务器不太了解的都认为࿰…...

vue(element ui安装)

目录 一,element ui安装二,main.js三,使用element ui最后 一,element ui安装 先在盘服中找到你创建的node的位置 如有不懂根据可以看看上一章安装node 然后在终端找到 进入这个位置之后就可以安装了 输入npm i element-ui -S这个…...

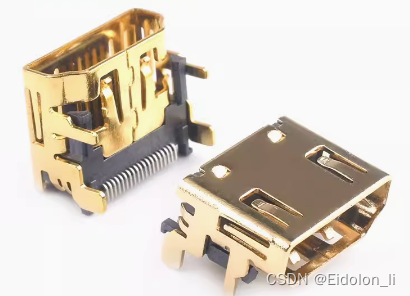

基于FPGA视频接口之HDMI2.0编/解码

简介 为什么要特别说明HDMI的版本,是因为HDMI的版本众多,代表的HDMI速度同样不同,当前版本在HDMI2.1速度达到48Gbps,可以传输4K及以上图像,但我们当前还停留在1080P@60部分,且使用的芯片和硬件结构有很大差别,故将HDMI分为两个部分说明1080@60以下分辨率和4K以上分辨率(…...

Codeforces Round #894 (Div.3)

文章目录 前言A. Gift Carpet题目:输入:输出:思路:代码: B. Sequence Game题目:输入:输出:思路:代码: C. Flower City Fence题目:输入:…...

W5500 TCP客户端实战:从寄存器配置到网络调试助手,一步步打通你的第一个物联网连接

W5500 TCP客户端实战:从寄存器配置到网络调试助手,一步步打通你的第一个物联网连接 在嵌入式物联网开发中,网络通信模块的选择往往决定了项目的稳定性和开发效率。W5500作为一款全硬件TCP/IP协议栈芯片,以其稳定的性能和简单的开发…...

AIGC 检测算法 1.0 到 4.0 升级了什么?嘎嘎降 AI 实测 80% AI 率降到 6% 答辩稳过

AIGC 检测算法 1.0 到 4.0 升级了什么?嘎嘎降 AI 实测 80% AI 率降到 6% 答辩稳过 很多同学不理解——为什么 2024 年用换同义词就能降下 AI 率、2025 年开始这招就半失效了、2026 年完全没用了?真相是——AIGC 检测算法从 1.0 升级到 4.0 经历了 4 次大…...

Perplexity + Obsidian + LlamaIndex三端联动:打造个人知识库响应延迟<800ms的私有化查询方案

更多请点击: https://intelliparadigm.com 第一章:Perplexity技术文档查询 Perplexity 是一种衡量语言模型预测能力的指标,常用于评估模型对给定文本序列的不确定性程度。在技术文档查询场景中,它被用作排序与重排的关键信号——…...

)

Oracle 19c单实例安装后,别忘了做这5个安全与性能基础配置(CentOS 7版)

Oracle 19c单实例安装后的5个关键安全与性能配置指南(CentOS 7环境) 刚完成Oracle 19c的安装只是数据库管理的第一步。许多初级DBA常犯的错误是认为安装成功就意味着工作结束,实际上默认配置往往存在严重的安全漏洞和性能隐患。本文将带您完成…...

)

保姆级教程:用R包MaAsLin2搞定微生物组与临床数据的关联分析(附完整代码)

微生物组与临床数据关联分析实战:MaAsLin2从入门到精通 在微生物组研究中,揭示菌群变化与宿主表型之间的关联是核心科学问题之一。传统统计方法往往难以应对高维稀疏的微生物组数据特性,而专门设计的工具如MaAsLin2(Microbiome Mu…...

Perplexity真实岗位薪资曝光,17城对比+职级换算公式,HR不会告诉你的薪酬锚点

更多请点击: https://codechina.net 第一章:Perplexity真实岗位薪资曝光,17城对比职级换算公式,HR不会告诉你的薪酬锚点 一线数据来源与采样逻辑 本章薪资数据源自2024年Q2匿名技术社区(如Levels.fyi、Blind、脉脉脱…...

声磁同步定点仪怎么选?这份选购经验干货分享

做工厂电缆故障检测、地埋电缆探测的工程人员,多半都踩过定点仪的坑:设备抗干扰差,复杂厂区地下管线密集,找半天定不准点位,开挖错位置不仅耽误工期,额外的开挖成本、停产损失动辄几万到几十万。作为常年跟…...

手持式身份核验测温一体机:从防疫工具到智能终端的深度解析与应用

1. 项目概述:一个被低估的“防疫哨兵”你可能在商场、写字楼、医院或者社区的入口见过它——一个看起来像固定电话机,或者一个带屏幕的扫码盒子,旁边还伸出一个测温探头。这就是我们今天要聊的主角:手持式身份核验测温一体机。很多…...

Adobe-GenP 3.0:5分钟解锁Adobe全家桶的专业方案

Adobe-GenP 3.0:5分钟解锁Adobe全家桶的专业方案 【免费下载链接】Adobe-GenP Adobe CC 2019/2020/2021/2022/2023 GenP Universal Patch 3.0 项目地址: https://gitcode.com/gh_mirrors/ad/Adobe-GenP 还在为高昂的Adobe订阅费用发愁吗?Adobe-Ge…...

)

告别黑盒渲染!用Nvdiffrast手把手教你从零搭建可微渲染管线(PyTorch版)

从零构建可微渲染管线:Nvdiffrast深度实践指南 在计算机图形学与深度学习交叉领域,可微渲染技术正掀起一场革命。传统渲染管线如同黑盒,输入3D场景参数,输出2D图像,但反向路径却被阻断——这正是Nvdiffrast要解决的痛点…...