ASIC-WORLD Verilog(13)状态机FSM

写在前面

在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加点自己的理解)分享给大家。

这是网站原文:Verilog Tutorial

这是系列导航:Verilog教程系列文章导航

有限状态机FSM简介

状态机(FSM)是许多数字设计的核心。计数器就是 FSM 的一种简单形式。当我学习Verilog时,我曾经想知道“如何在Verilog中编码FSM”和“编码它的最佳方法是什么”。接下来我将尝试回答这两个问题。

状态机类型

根据状态机的输出类型分类,有两种类型的状态机。第一种是 Moore 状态机,其输出仅是当前状态的函数;第二种是 Mealy 状态机,其输出是当前状态和输入的函数。

Moore 状态机

Mealy 状态机

状态机还可以根据所使用的状态编码进行分类。编码类型也是决定FSM的速度和复杂度的关键因素。二进制编码、格雷码、独热码是最常见的几种 FSM 状态编码类型。

状态机建模

编码 FSM 时需要记住的一件事:组合逻辑和时序逻辑应该位于两个不同的always块中。在上两图中,下一状态逻辑(next state logic)始终是组合逻辑;而状态逻辑(state logic)和输出逻辑(output logic)则是时序逻辑。任何到下一个状态逻辑的异步信号在馈送到 FSM 之前都必须进行同步化处理。你应该尽量将状态机FSM 保存在单独的 Verilog 文件中。

使用parameter或`define 等常量声明来定义 FSM 的状态可使代码更具可读性,且更易于管理。

示例:仲裁器

接下来将以仲裁器作为案例,看看该如何实现一个完整的FSM。

FSM 代码应包含三个部分:

- 状态编码部分

- 组合逻辑部分

- 时序逻辑部分

状态编码

状态编码有许多方式,其中最常用的是:

- 二进制码(Binary Encoding)

- 独热码(One Hot Encoding)

- 格雷码(Gray Encoding)

独热码(One Hot Encoding)

parameter [4:0] IDLE = 5'b0_0001;

parameter [4:0] GNT0 = 5'b0_0010;

parameter [4:0] GNT1 = 5'b0_0100;

parameter [4:0] GNT2 = 5'b0_1000;

parameter [4:0] GNT3 = 5'b1_0000;二进制码(Binary Encoding)

parameter [2:0] IDLE = 3'b000;

parameter [2:0] GNT0 = 3'b001;

parameter [2:0] GNT1 = 3'b010;

parameter [2:0] GNT2 = 3'b011;

parameter [2:0] GNT3 = 3'b100;格雷码(Gray Encoding)

parameter [2:0] IDLE = 3'b000;

parameter [2:0] GNT0 = 3'b001;

parameter [2:0] GNT1 = 3'b011;

parameter [2:0] GNT2 = 3'b010;

parameter [2:0] GNT3 = 3'b110;组合逻辑部分

这一部分可以使用函数、assign 语句或者always块来实现。

always @ (state or req_0 or req_1 or req_2 or req_3)

begin next_state = 0;case(state)IDLE : if (req_0 == 1'b1) beginnext_state = GNT0;end else if (req_1 == 1'b1) beginnext_state= GNT1;end else if (req_2 == 1'b1) beginnext_state= GNT2;end else if (req_3 == 1'b1) beginnext_state= GNT3;end else beginnext_state = IDLE;end GNT0 : if (req_0 == 1'b0) beginnext_state = IDLE;end else beginnext_state = GNT0;endGNT1 : if (req_1 == 1'b0) beginnext_state = IDLE;end else beginnext_state = GNT1;endGNT2 : if (req_2 == 1'b0) beginnext_state = IDLE;end else beginnext_state = GNT2;endGNT3 : if (req_3 == 1'b0) beginnext_state = IDLE;end else beginnext_state = GNT3;enddefault : next_state = IDLE;endcase

end时序逻辑部分

这一部分只能使用边沿敏感逻辑例如带posedge clock或者negedge clock的always块来实现。

always @ (posedge clock)

begin : OUTPUT_LOGICif (reset == 1'b1) begingnt_0 <= #1 1'b0;gnt_1 <= #1 1'b0;gnt_2 <= #1 1'b0;gnt_3 <= #1 1'b0;state <= #1 IDLE;end else beginstate <= #1 next_state;case(state)IDLE : begingnt_0 <= #1 1'b0;gnt_1 <= #1 1'b0;gnt_2 <= #1 1'b0;gnt_3 <= #1 1'b0;endGNT0 : begingnt_0 <= #1 1'b1;endGNT1 : begingnt_1 <= #1 1'b1;endGNT2 : begingnt_2 <= #1 1'b1;endGNT3 : begingnt_3 <= #1 1'b1;enddefault : beginstate <= #1 IDLE;endendcaseend

end使用二进制编码的完整FSM代码

module fsm_full(

clock , // Clock

reset , // Active high reset

req_0 , // Active high request from agent 0

req_1 , // Active high request from agent 1

req_2 , // Active high request from agent 2

req_3 , // Active high request from agent 3

gnt_0 , // Active high grant to agent 0

gnt_1 , // Active high grant to agent 1

gnt_2 , // Active high grant to agent 2

gnt_3 // Active high grant to agent 3

);

// Port declaration here

input clock ; // Clock

input reset ; // Active high reset

input req_0 ; // Active high request from agent 0

input req_1 ; // Active high request from agent 1

input req_2 ; // Active high request from agent 2

input req_3 ; // Active high request from agent 3

output gnt_0 ; // Active high grant to agent 0

output gnt_1 ; // Active high grant to agent 1

output gnt_2 ; // Active high grant to agent 2

output gnt_3 ; // Active high grant to agent // Internal Variables

reg gnt_0 ; // Active high grant to agent 0

reg gnt_1 ; // Active high grant to agent 1

reg gnt_2 ; // Active high grant to agent 2

reg gnt_3 ; // Active high grant to agent parameter [2:0] IDLE = 3'b000;

parameter [2:0] GNT0 = 3'b001;

parameter [2:0] GNT1 = 3'b010;

parameter [2:0] GNT2 = 3'b011;

parameter [2:0] GNT3 = 3'b100;reg [2:0] state, next_state;always @ (state or req_0 or req_1 or req_2 or req_3)

begin next_state = 0;case(state)IDLE : if (req_0 == 1'b1) beginnext_state = GNT0;end else if (req_1 == 1'b1) beginnext_state= GNT1;end else if (req_2 == 1'b1) beginnext_state= GNT2;end else if (req_3 == 1'b1) beginnext_state= GNT3;end else beginnext_state = IDLE;end GNT0 : if (req_0 == 1'b0) beginnext_state = IDLE;end else beginnext_state = GNT0;endGNT1 : if (req_1 == 1'b0) beginnext_state = IDLE;end else beginnext_state = GNT1;endGNT2 : if (req_2 == 1'b0) beginnext_state = IDLE;end else beginnext_state = GNT2;endGNT3 : if (req_3 == 1'b0) beginnext_state = IDLE;end else beginnext_state = GNT3;enddefault : next_state = IDLE;endcase

endalways @ (posedge clock)

begin : OUTPUT_LOGICif (reset) begingnt_0 <= #1 1'b0;gnt_1 <= #1 1'b0;gnt_2 <= #1 1'b0;gnt_3 <= #1 1'b0;state <= #1 IDLE;end else beginstate <= #1 next_state;case(state)IDLE : begingnt_0 <= #1 1'b0;gnt_1 <= #1 1'b0;gnt_2 <= #1 1'b0;gnt_3 <= #1 1'b0;endGNT0 : begingnt_0 <= #1 1'b1;endGNT1 : begingnt_1 <= #1 1'b1;endGNT2 : begingnt_2 <= #1 1'b1;endGNT3 : begingnt_3 <= #1 1'b1;enddefault : beginstate <= #1 IDLE;endendcaseend

endendmodule测试脚本

`include "fsm_full.v"module fsm_full_tb();

reg clock , reset ;

reg req_0 , req_1 , req_2 , req_3;

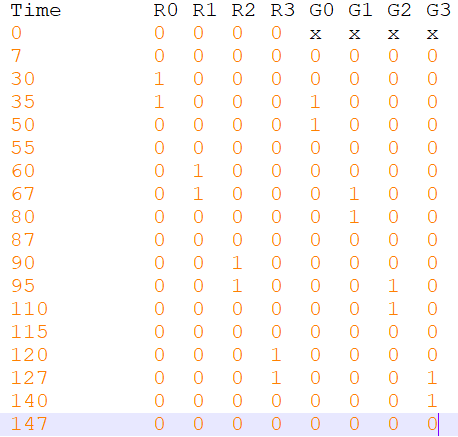

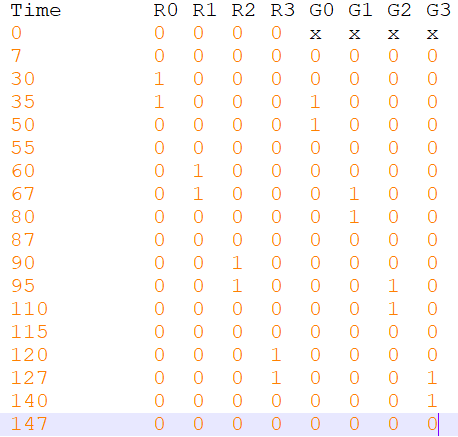

wire gnt_0 , gnt_1 , gnt_2 , gnt_3 ;initial begin$display("Time\t R0 R1 R2 R3 G0 G1 G2 G3");$monitor("%g\t %b %b %b %b %b %b %b %b", $time, req_0, req_1, req_2, req_3, gnt_0, gnt_1, gnt_2, gnt_3);clock = 0;reset = 0;req_0 = 0;req_1 = 0;req_2 = 0;req_3 = 0;#10 reset = 1;#10 reset = 0;#10 req_0 = 1;#20 req_0 = 0;#10 req_1 = 1;#20 req_1 = 0;#10 req_2 = 1;#20 req_2 = 0;#10 req_3 = 1;#20 req_3 = 0;#10 $finish;

endalways#2 clock = ~clock;fsm_full U_fsm_full(

clock , // Clock

reset , // Active high reset

req_0 , // Active high request from agent 0

req_1 , // Active high request from agent 1

req_2 , // Active high request from agent 2

req_3 , // Active high request from agent 3

gnt_0 , // Active high grant to agent 0

gnt_1 , // Active high grant to agent 1

gnt_2 , // Active high grant to agent 2

gnt_3 // Active high grant to agent 3

);endmodule仿真结果

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

相关文章:

ASIC-WORLD Verilog(13)状态机FSM

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加点自己的理解)分享给大家。 这是网站原文&…...

设置微软Edge浏览器主页和新标签页,摆脱扰人和分散注意力的主页

默认情况下,Microsoft Edge会向您显示世界上最令人分心和讨厌的主页(也称为主屏幕)。微软不想只向你展示一个搜索框,也许还有一个漂亮的背景或一些你喜欢的网站的快捷方式,而是想在你面前扔一堆新闻标题和广告。 你可能会打开浏览器阅读电子邮件,结果被Microsoft Edge主…...

视频汇聚平台EasyCVR安防视频监控平台新增经纬度选取功能的详细介绍

视频云存储/安防监控EasyCVR视频汇聚平台基于云边端智能协同,支持海量视频的轻量化接入与汇聚、转码与处理、全网智能分发、视频集中存储等。音视频流媒体视频平台EasyCVR拓展性强,视频能力丰富,具体可实现视频监控直播、视频轮播、视频录像、…...

HCIP-HCS华为私有云的使用

1、概述 HCS(HuaweiCoudStack)华为私有云:6.3 之前叫FusionSphere OpenStack,6.3.1 版本开始叫FusionCloud,6.5.1 版本开始叫HuaweiCloud Stack (HCS)华为私有云软件。 开源openstack,发放云主机的流程&am…...

深度学习1.卷积神经网络-CNN

目录 卷积神经网络 – CNN CNN 解决了什么问题? 需要处理的数据量太大 保留图像特征 人类的视觉原理 卷积神经网络-CNN 的基本原理 卷积——提取特征 池化层(下采样)——数据降维,避免过拟合 全连接层——输出结果 CNN …...

浏览器输入一个URL之后发生了什么?

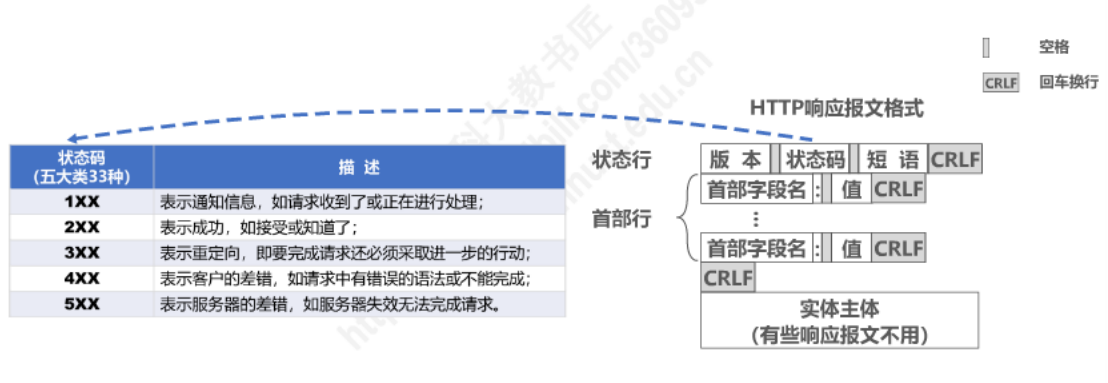

URL解析DNS解析TCP连接TSL连接HTTP请求TCP挥手接收并解析响应 URL 解析 主要分为: 协议,eg http,https域名或者ip地址,eg www.baidu.com 域名相对于ip地址来说,更方便人们记忆,但是实际的网络传输中使用的是ip地址 端…...

uniapp 布局(自定义导航栏加固定高度的主要内容)

不想让整体页面出现滚动条 页面大致分为三部分,导航栏、主题内容、tabbar,不想让整个页面出现滚动条,只想让主要内容滚动。 我这里是直接用了uni.getSystemInfoSync(),整体分为两部分,自定义头部和滚动内容ÿ…...

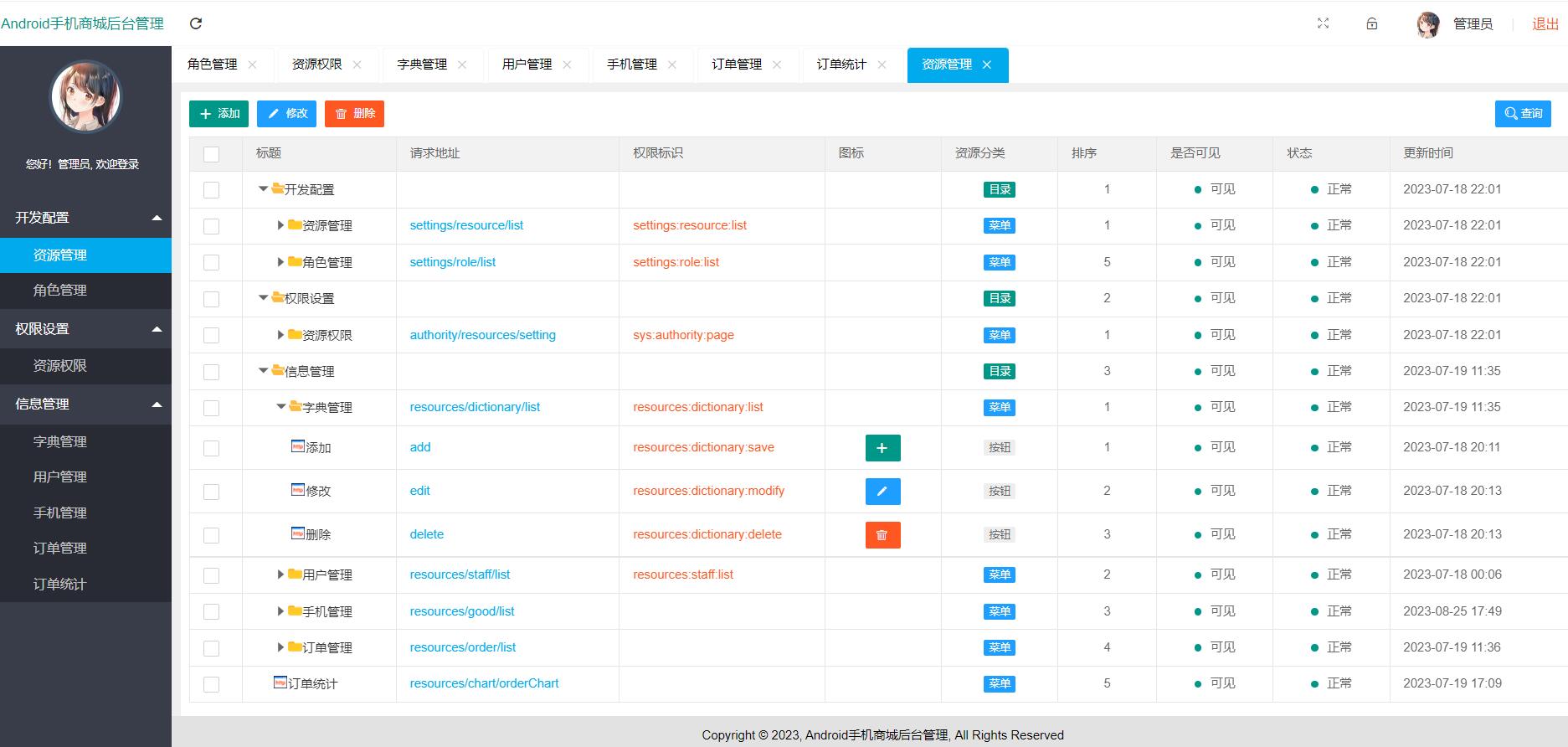

android手机销售app(IDEA,SpringBoot,SSM,MySQL)+支付宝支付+全套视频教程

本项目亮点: 支付宝支付 eCharts柱状图图表数据统计 【项目功能介绍】 本系统包含后台管理和前端app双端系统,后台管理的功能包含: 登录, 退出, 修改管理员信息(基本信息与头像),资源管理,角色管理,资源权限分配,字典管理,用户管理,图书管理,订单管理,订单统计; a…...

的工作原理与优化策略)

深入探讨Java虚拟机(JVM)的工作原理与优化策略

摘要:本文对Java虚拟机(JVM)的工作原理进行深入探讨,包括其内存管理、垃圾回收以及代码执行等方面。同时,文章还通过具体的代码示例,阐述了JVM的优化策略,旨在提高Java程序的性能。 一、引言 …...

WPF数据绑定

数据绑定是一个很强大且优雅的技能,之前用过好多次,但有些地方总不是特别清晰,常常需要重新翻阅资料来回顾,于是这次用了几天时间好好梳理一下,记录一下。 首先数据绑定对数据对象的要求:需要是公有属性&a…...

其他UI控件)

Android学习之路(6) 其他UI控件

ImageView(图像视图) RadioButton(单选按钮)&Checkbox(复选框) 开关按钮ToggleButton和开关Switch ProgressBar(进度条) SeekBar(拖动条) RatingBar(星级评分条) ScrollView(滚动条)...

matlab实现牛顿迭代法求解非线性方程

非线性方程是指含有未知数的方程,且方程中至少有一个未知数的次数大于一或者含有非一次幂的函数(如指数、对数、三角函数等)。例如,$f(x) x^3 - 2x - 5 0$就是一个非线性方程。非线性方程通常没有显式的解析解,因此需…...

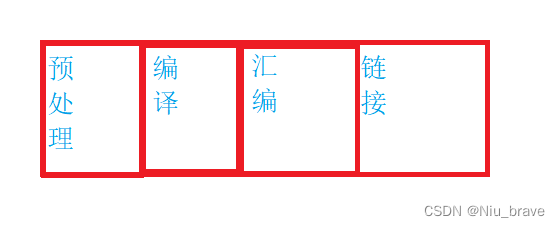

Cpp学习——编译链接

目录 编辑 一,两种环境 二,编译环境下四个部分的 1.预处理 2.编译 3.汇编 4.链接 三,执行环境 一,两种环境 在程序运行时会有两种环境。第一种便是编译环境,第二种则是执行环境。如下图: 在程序运…...

android - fragment 数据丢失?状态丢失?

最佳答案 一些状态丢失的例子: 1. 假设您有一个按钮和一个 TextView 。在代码中,你已经定义了初始值为 0 的整数 i,它通过单击按钮递增 1,并且它的值显示在 TextView 中。假设你已经按下按钮 5 次,那么 textview 将被设置为 0。也…...

Git基本操作

本地仓库 当我们初始化(git init)之后,会在当前目录下生成一个与项目并列的.git文件夹,当我们对项目作出更改之后使用git commit命令,一般是将修改提交到本地仓库,也就是该文件夹下面的文件会对应修改&…...

Nginx配置文件详解

Nginx配置文件详解 1、Nginx配置文件1.1主配置文件详解1.2子配置文件 2、全局配置部分2.1修改启动的工作进程数(worker process) 优化2.2cpu与worker process绑定2.3 PID 路径修改2.4 修改工作进程的优先级2.5调试工作进程打开的文件的个数2.6关闭master-worker工作…...

进程启动原理(1))

【0217】stats collector(统计信息收集器)进程启动原理(1)

文章目录 1. 启动 stats collector进程1.1 stats collector进程启动过程1.1.1 检查套接字 pgStatSock 是否存在1.1.2 重新启动失败的stats collector频率1.1.3 fork() 三种返回值处理1.2 detach所有共享内存段1.3 detach 共享内存段1.4 stats collecotr进程启动的主体相关阅读:…...

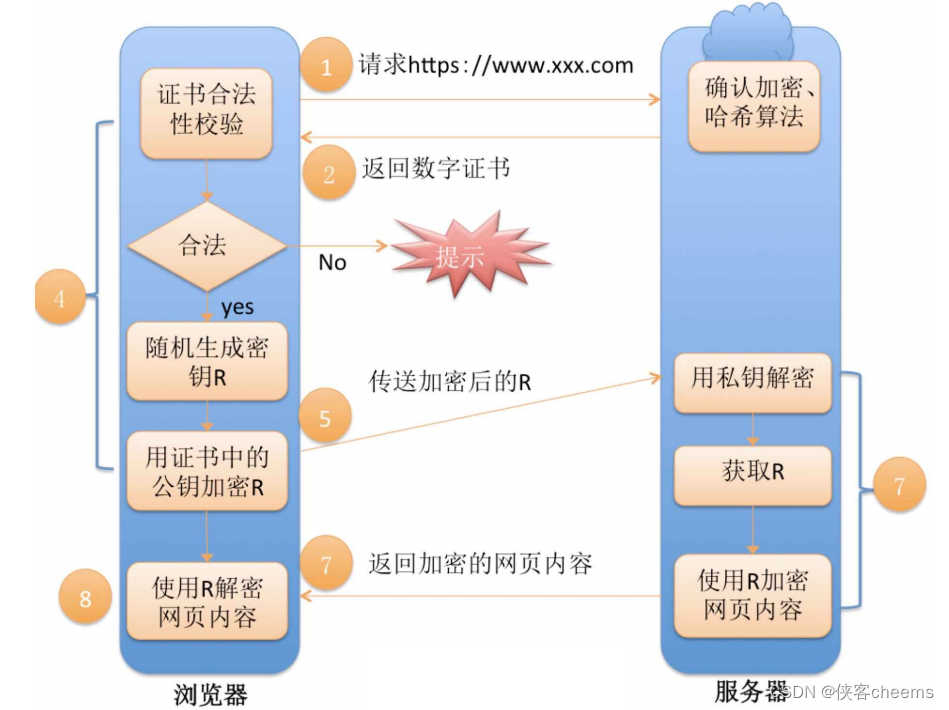

【应用层】网络基础 -- HTTPS协议

HTTPS 协议原理加密为什么要加密常见的加密方式对称加密非对称加密 数据摘要&&数据指纹 HTTPS 的工作过程探究方案1-只使用对称加密方案2-只使用非对称加密方案3-双方都使用非对称加密方案4-非对称加密对称加密中间人攻击-针对上面的场景 CA认证理解数据签名方案5-非对…...

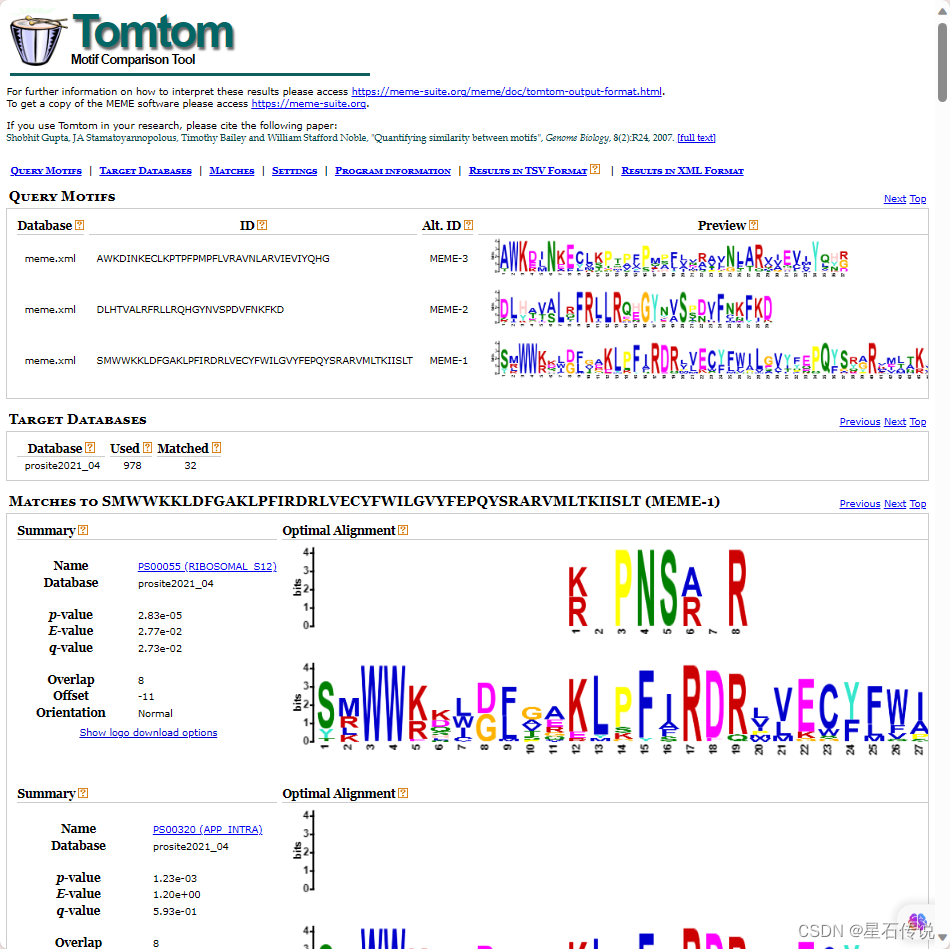

实验篇—— 基因家族Motif 分析

实验篇—— 基因家族Motif 分析 文章目录 前言一、名词解释二、实操1. MEME工具箱2. Motif Discovery(基序发现)1. 结果网页2. 在TBtools中(额外) 2. Motif Enrichment(基序富集分析)3. Motif Search&#…...

Linux拓展之阻止或禁用普通用户登录

禁止指定用户登录 chsh -s /sbin/nologin 指定用户名示例 chsh -s /sbin/nologin testuser恢复指定用户登录 chsh -s /bin/bash 指定用户名示例 chsh -s /bin/bash testuser参考 https://blog.csdn.net/cnds123321/article/details/125232580 https://www.cnblogs.com/cai…...

开源项目脚手架工具:从零到一快速构建标准化项目

1. 项目概述:当开源遇上“锻造”在开源的世界里,我们常常面临一个看似简单实则棘手的问题:如何将一个灵光一现的想法,或者一个内部使用的工具,快速、规范地“锻造”成一个真正意义上的开源项目?这不仅仅是把…...

MonitorControl:终极解决方案!让你的Mac外接显示器亮度调节变得如此简单

MonitorControl:终极解决方案!让你的Mac外接显示器亮度调节变得如此简单 【免费下载链接】MonitorControl 🖥 Control your displays brightness & volume on your Mac as if it was a native Apple Display. Use Apple Keyboard keys or…...

从零构建装饰艺术视觉系统:Midjourney + Figma联动作业流,1小时产出完整海报/包装/UI组件库

更多请点击: https://intelliparadigm.com 第一章:装饰艺术视觉系统的美学内核与技术定位 装饰艺术(Art Deco)视觉系统并非仅关乎复古纹样或金色渐变,其本质是几何秩序、工业节奏与人文表现力的三重耦合。在现代前端架…...

安卓位置伪装的终极指南:3步掌握应用级虚拟定位

安卓位置伪装的终极指南:3步掌握应用级虚拟定位 【免费下载链接】FakeLocation Xposed module to mock locations per app. 项目地址: https://gitcode.com/gh_mirrors/fak/FakeLocation 你是否曾因社交软件暴露真实位置而感到不安?是否需要在不同…...

[Cesium] 数字孪生实践 | 超图插件打通UE4/Unity三维GIS管线全解析

1. 数字孪生与三维GIS技术融合的现状 数字孪生技术正在改变我们理解和构建物理世界的方式。简单来说,数字孪生就是通过数字化手段,在虚拟空间中创建一个与真实世界完全对应的"双胞胎"。这个数字化的双胞胎可以实时反映真实世界的状态ÿ…...

基于Three.js与WebSocket构建虚拟小镇:全栈技术架构与优化实践

1. 项目概述与核心价值最近在折腾一个叫“Alicization-Town”的开源项目,它来自GitHub上的ceresOPA组织。乍一看这个名字,可能会联想到某个动漫或者游戏里的场景,但实际接触后,我发现它远不止于此。这是一个围绕“虚拟小镇”或“数…...

ARM GIC中断控制器架构与寄存器编程详解

1. ARM GIC中断控制器架构概述 中断控制器是现代处理器系统中至关重要的组件,它负责协调和管理来自各种外设的中断请求。ARM架构的通用中断控制器(GIC)经过多代演进,目前GICv3/GICv4已成为主流实现。GIC的核心功能包括中断优先级管理、中断分发、虚拟化支…...

Linux系统变更追踪工具whatdiditdo:实现文件级监控与审计

1. 项目概述:一个追踪系统变更的“时光机”最近在排查一个线上服务故障,问题最终定位到是某个依赖库在几天前的一次静默升级上。为了搞清楚到底是谁、在什么时候、改了什么东西,我不得不翻遍了近一周的服务器操作日志、CI/CD流水线记录和版本…...

掌握这四大趋势,让你的AI Agent真正“能干活”!CSDN收藏必备指南

本文深入探讨了企业级AI Agent的四大核心趋势:MCP协议实现可扩展集成、GraphRAG提升回答一致性、AgentDevOps确保行为质量与推理链路稳定性、RaaS模式实现结果计费。文章指出,这些趋势共同推动AI Agent从“可用”到“好用”的跨越,并提供了实…...

Swift集成飞书开放平台:feishu-swift SDK架构解析与实战指南

1. 项目概述与核心价值最近在折腾一个需要深度集成飞书开放平台的项目,目标是构建一个能与飞书服务端API高效、稳定交互的iOS原生应用。在技术选型阶段,我几乎翻遍了GitHub和各大技术社区,最终锁定了ricsy/feishu-swift这个开源库。简单来说&…...