SystemVerilog interface详细介绍

1. Interface概念

System Verilog中引入了接口定义,接口与module 等价的定义,是要在其他的接口、module中直接定义,不能写在块语句中,跟class是不同的。接口是将一组线捆绑起来,可以将接口传递给module。

2. 接口的优点

一)通过接口在module之间或内部进行信号传递,模块的输入列表就是一个接口,这样简单,避免手动连线的错误。

二)如果需要增加模块的IO,只需要在接口中增加,不需要改变模块的输入列表,防止输入错误、少改了哪个模块的列表。

三)在UVM 中需要在不同的class之间传递信号,用接口的话,传递一组信号只需要uvm_config_db一个接口就可以了,如果不用接口,那么就需要好多条uvm_config_db语句。

四)接口中可以定义一些initial(生成时钟),always块,任务,函数,类的句柄。

3. 定义接口

可以在接口中定义一些信号、函数、任务、class对象,也可以有always,initial语句块。比如可以在initial块中生成时钟clk。

3.1 定义

interface if(input bit clk);logic data;logic valid;logic addr;

endinterface3.2 modport

可以用modport将接口中的信号分组。比如总线接口中,master、slave、arbiter需要的信号是不同的,输入输出也不同。

interface if(input bit clk);logic [7:0] data;logic valid;logic [7:0] addr;logic request;logic grant;logic command;logic ready;modport MASTER(output request,addr,command);modport SLAVE(input request,addr,command,output ready);modport ARBITER(input request,output grant);

endinterface

module Master (if.MASTER if_u);

...

endmodule

module test;if if_u;Master m_u(if_u.MASTER);

endmodule 4. 激励时序

测试平台需要和设计之间的时序密切配合。比如在同一个时间片内,一个信号需要被同时写入和读取,那么采样到新值还是旧值?非阻塞赋值可以解决这个问题,值的计算在active区域,值的更新在NBA区域——采样到的是旧值。

4.1 时钟块控制同步信号的时序

在接口中定义时钟块,时钟块中的任何信号都相对于时钟同步驱动和采样。时钟块大都在测试平台中使用。

interface if(input bit clk);logic [7:0] data;logic valid;logic [7:0] addr;clocking cb@(posedge clk);input valid;input data;input addr;endclockingmodport TEST(clocking cb);modport DUT(input valid ,input data);

endinterface一个接口中可以有多个时钟块,但每个时钟块只有一个时钟表达式。如@(posedge clk)定义了单时钟;@(clk)定义了DDR时钟(双数据率,两个沿)。

4.2 logic还是wire

在测试平台中,如果用过程赋值语句驱动接口中的信号,那么信号要在接口中定义为logic,如果是连续赋值驱动,定义成wire。

定义成logic的一个好处是,如果多个信号驱动logic,那么编译器会报错,这样你就知道写错了,如果是wire,这个错误就隐藏了。

4.3 对测试平台和DUT中事件的调度

如果没有用时钟块,测试平台对DUT的驱动和采样存在竞争,这是因为测试平台的事件和DUT的事件混合在同一个时间片中。

SV中将测试平台中的事件和DUT中的事件分离。

时间片划分:

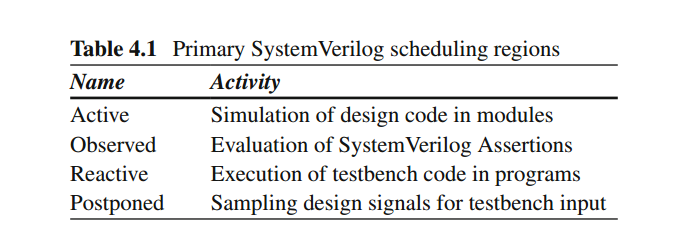

SV的主要调度区域:

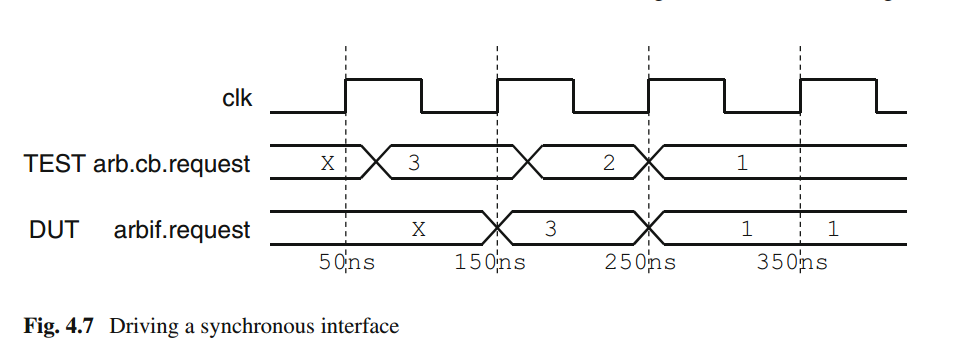

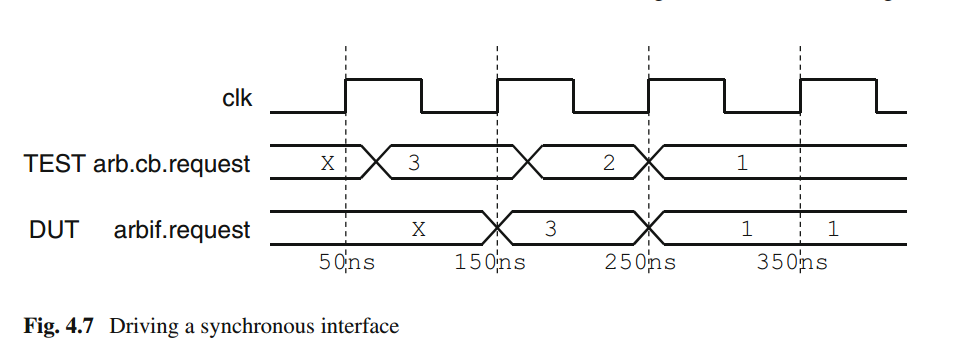

4.4 设计和测试平台之间的时序

时钟块(测试平台)在#1step延时之后采样DUT,也就是采样上一个时间片postponed区域的数据。也就是前面讲的采样旧值。时钟块(测试平台)在#0延时之后驱动DUT信号。0延迟说明还在同一个time slot,DUT能够捕捉到变化。

更细致的时间片划分:

| time slot | |

|---|---|

| active | design |

| inactive | 显示0延迟阻塞赋值; |

| observed | SVA |

| reactive | SV |

| postponed | SV 采样 |

5. 接口采样和驱动信号的时序

为了同步接口中的信号,可以在时钟沿采样或者驱动接口信号。可以在接口中定义时钟块来同步接口信号:

interface if(input bit clk);logic data;logic valid;logic addr;clocking cb@(posedge clk);input valid;input data;input addr;endclockingmodport TEST(clocking cb);modport DUT(input valid ,input data);

endinterface在测试平台中的信号才需要同步。

5.1 接口信号采样时序

如果时钟块中的信号采样DUT中的信号,采样的是上一个时间片(time slot)postponed区域的数据。即如果DUT信号在时钟沿发生0-1跳变,那么采样到0。DUT接口想要驱动TEST接口中时钟块里的信号,需要线给DUT接口信号赋值:

module dut(if.DUT if0);....#10 if0.valid = 1;#10 if0.valid = 2;....

endmodule

5.2 接口信号驱动时序

如果时钟块驱动DUT信号,值会立即传入到设计中。即如果时钟块中的信号在时钟沿发生0-1跳变,则时钟沿之后DUT中为1。

时钟块想要驱动DUT,需要在testbench给时钟块中的信号赋值,在tb中驱动时钟块中的信号需要同步驱动,用“<=”符号。时钟块中的信号驱动采样

program tb(if.TEST if1);...#10 if1.cb.valid <= 1;#10 if1.cb.valid <= 0;...

endprogram

6. 使用虚接口

之前介绍的接口都是跟module一样来描述硬件的;在SV中有面向对象的概念,在class里面使用虚接口——virtual interface。虚接口是一个物理接口的句柄(handler),同这个句柄来访问硬件接口。虚接口是唯一链接动态对象和静态模块、接口的一种机制。

6.1 在测试平台中使用接口

interface inf; //定义接口

...

endinterface

program test(inf if0); // 接口传入测试平台driver drv;initial begindrv = new(if0); // 接口传给driver对象end

endprogram

class driver;virtual vif; // 在class中为虚接口function new(inf i);vif=i;endfunction

endclass

module top;inf inf0(); // 例化接口test t1(inf0);dut d1(inf0);

endmodule也可以在tb中跨模块引用XMR(cross module reference)接口

program test(); //没有接口参数virtual inf if0=top.inf0;//top是顶层模块...

endprogram

module top;inf inf0(); // 例化接口test t1(); // tb无接口列表dut d1(inf0);

endmodule6.2 使用端口传递接口数组

interface inf(input clk);

...

endinterface

parameter NUM=10;

module top;inf xi[NUM](clk); // 顶层例化多个接口,接口名后跟个数test t1(xi);// 接口作为参数dut...

endmodule

program test(inf xi[NUM]); // 接口参数列表virtual inf vxi[NUM];initial beginvxi=xi;end

endprogram也可以用跨模块引用。

7. 接口中的代码

接口中可以定义信号、函数、任务、class对象,也可以有always,initial语句块。下面给一个在《UVMPrimer》中的例子:

interface tinyalu_bfm;import tinyalu_pkg::*;

byte unsigned A;byte unsigned B;bit clk;bit reset_n;wire [2:0] op;bit start;wire done;wire [15:0] result;operation_t op_set;

assign op = op_set;

task reset_alu();reset_n = 1'b0;@(negedge clk);@(negedge clk);reset_n = 1'b1;start = 1'b0;endtask : reset_alutask send_op(input byte iA, input byte iB, input operation_t iop, shortint result);if (iop == rst_op) begin@(posedge clk);reset_n = 1'b0;start = 1'b0;@(posedge clk);#1;reset_n = 1'b1;end else begin@(negedge clk);op_set = iop;A = iA;B = iB;start = 1'b1;if (iop == no_op) begin@(posedge clk);#1;start = 1'b0; end else begindo@(negedge clk);while (done == 0);start = 1'b0;endend // else: !if(iop == rst_op)endtask : send_opcommand_monitor command_monitor_h;

function operation_t op2enum();case(op)3'b000 : return no_op;3'b001 : return add_op;3'b010 : return and_op;3'b011 : return xor_op;3'b100 : return mul_op;default : $fatal("Illegal operation on op bus");endcase // case (op)endfunction : op2enum

always @(posedge clk) begin : op_monitorstatic bit in_command = 0;command_s command;if (start) begin : start_highif (!in_command) begin : new_commandcommand.A = A;command.B = B;command.op = op2enum();command_monitor_h.write_to_monitor(command);in_command = (command.op != no_op);end : new_commandend : start_highelse // start lowin_command = 0;end : op_monitor

always @(negedge reset_n) begin : rst_monitorcommand_s command;command.op = rst_op;command_monitor_h.write_to_monitor(command);end : rst_monitorresult_monitor result_monitor_h;

initial begin : result_monitor_threadforever begin@(posedge clk) ;if (done) result_monitor_h.write_to_monitor(result);endend : result_monitor_threadinitial beginclk = 0;forever begin#10;clk = ~clk;endend

endinterface : tinyalu_bfm函数使用的时候通过接口对象调用就行了

virtual tinyalu_bfm inf;

initial begininf.send_op(..);

end8. 接口使用注意事项

-

接口不能在package中被`include 。

下面这种写法是会报错的。

package pkg;`include "apb_if.sv"…… endpackage而要放在package外面

`include "apb_if.sv" package pkg;…… endpackage如果要在UVM中要通过hierarchy访问DUT中的信号,最好将这些信号放在interface中,然后将virtual interface传给UVM。

// 在接口中定义信号 interface bfm;bit[7:0 addr; endinterface// 实例化接口 bfm u_bfm();// 将虚接口传给UVM initial beginuvm_config_db#(vitual bfm)::set("", uvm_test_top, "bfm", bfm); end// 在UVM可直接操作虚接口如果不这样的话,当uvm component(driver, monitor, agent等)文件是通过package来管理的话,就不能在UVM中hierarchy引用DUT中的信号。

相关文章:

SystemVerilog interface详细介绍

1. Interface概念 System Verilog中引入了接口定义,接口与module 等价的定义,是要在其他的接口、module中直接定义,不能写在块语句中,跟class是不同的。接口是将一组线捆绑起来,可以将接口传递给module。 2. 接口的优…...

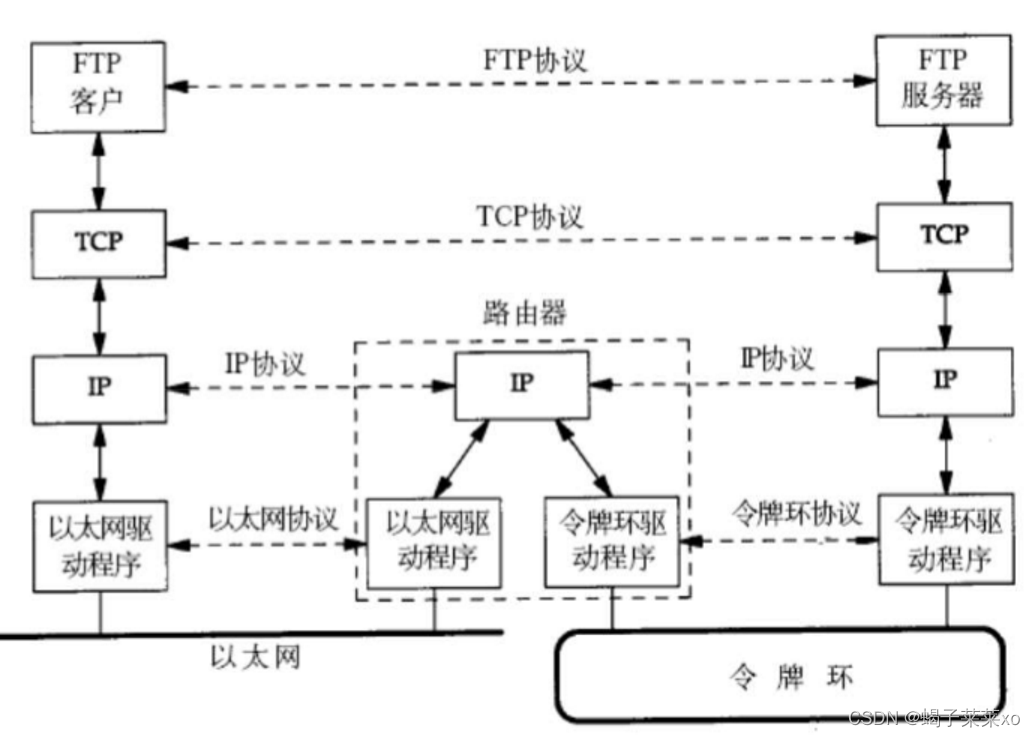

计网第四章(网络层)(三)

IPV4地址的应用规划: 定长的子网掩码FLSM: 使用同一个子网掩码划分子网,每个子网所分配的IP地址数量相同,造成IP地址的浪费。 变长的子网掩码VLSM: 使用不同的子网掩码划分子网,每个子网所分配的IP地址…...

python学习1之安装

前言 目前,Python有两个版本,一个是2.x版,一个是3.x版,这两个版本是不兼容的。由于3.x版越来越普及,我们的教程将以最新的Python 3.9版本为基础。 1、下载 官网地址 https://www.python.org/downloads/ 2、安装 点击…...

Autofac在WebApi,Winform中应用

安装注意事项 使用AOP的时候需要安装Autofac.Extras.DynamicProxy,如果发现VS老是提示报错,需要把VS重启下才可以识别。 WebApi 注意事项:WebApi中多一个ApiController中构造注入功能。 注入和AOP拦截 var siteNameList ClassHelper.GetConstants(typeof(SiteName));//创建…...

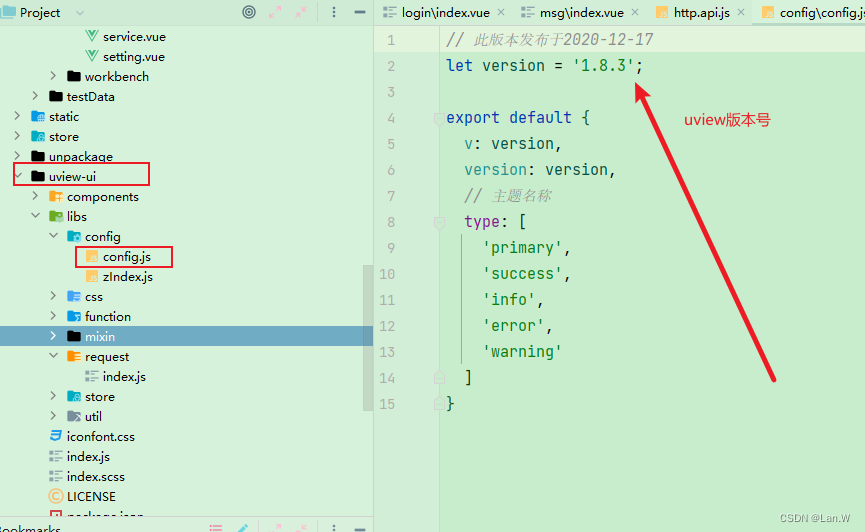

uview ui 查看版号

版本查询2种方式 有两种方式可以查询到正在使用的uView的版本: // 通过console.log打印的形式 console.log(uni.$u.config.v);// 可以查阅uView的配置文件得知当前版本号,具体位置为: /uview-ui/libs/config/config.js...

Python 爬虫网页图片下载到本地

您可以使用Python的requests库来获取网页的源码,使用BeautifulSoup库来解析HTML,并使用urllib库来下载图片到本地。下面是一个示例代码: import requests from bs4 import BeautifulSoup import urllib # 获取网页源码 url https://examp…...

PyQt open3d 加载 显示点云

PyQt加载 显示点云,已经有三种方式,使用 open3d; 使用 vtk; 使用 pcl; 下面是使用 open3d: import sys import open3d as o3d import numpy as np import pyqtgraph.opengl as gl from PyQt5.QtWidgets import QApplication, QVBoxLayout, QWidget, QFi…...

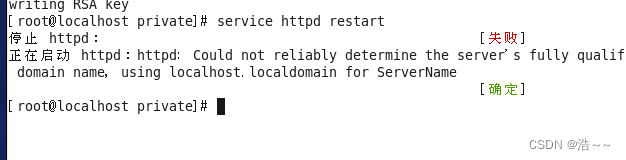

Linux搭建SSLVpn

安装http、ssl服务 编辑http配置文件 修改http的136行,276行以及990行 1、136行将监听端口注释 2、276行和990行修改为自己的域名和要访问的端口 修改http文档最后那部分 新添ssl配置信息,将端口修改为443(截图错了server.key应该放在/etc/…...

Qt5升级到Qt6分步迁移教程

Qt框架的一个新的长期支持版本6.5最近发布。它为以前的版本引入了许多修复、改进和新功能。有些可能对您的应用程序有用(如果不是现在,可能会在将来),因此最好将应用程序迁移到最新版本的框架。 仍然有许多应用程序仍在使用Qt 5&…...

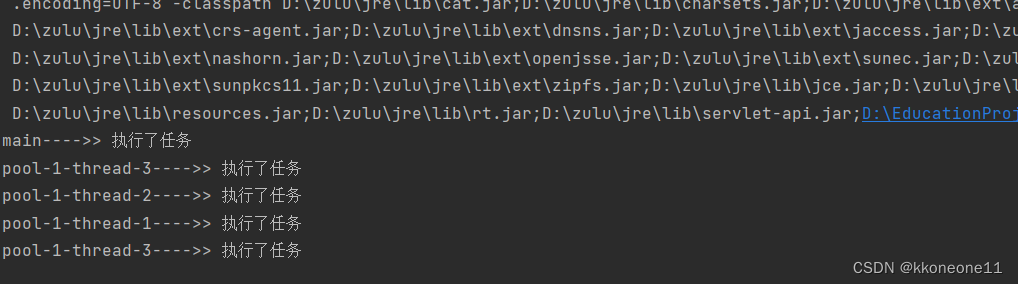

多线程学习之线程池

线程状态 线程状态具体含义NEW一个尚未启动的线程的状态。也称之为初始、开始状态。线程刚被创建,但是并未启动。还没调用start方法。MyThread t new MyThread()只有线程对象,没有线程特征。RUNNABLE当我们调用线程对象的start方法,那么此时…...

Elasticsearch基础

1、简介 Elasticsearch是实时的分布式搜索分析引擎,内部使用Lucene做索引与搜索。 何谓实时?新增到 ES 中的数据在1秒后就可以被检索到,这种新增数据对搜索的可见性称为“准实时搜索”。分布式意味着可以动态调整集群规模,弹性扩…...

论文阅读:Model-Agnostic Meta-Learning for Fast Adaptation of Deep Networks

前言 要弄清MAML怎么做,为什么这么做,就要看懂这两张图。先说MAML**在做什么?**它是打着Mate-Learing的旗号干的是few-shot multi-task Learning的事情。具体而言就是想训练一个模型能够使用很少的新样本,快速适应新的任务。 定…...

基于Web的旅游推荐网站设计与实现(论文+源码)_kaic

【摘 要】 当前,众所周知的旅游产业已慢慢成为全世界经济领域中最具代表影响力和最大领域的产业之一,互联网的蓬勃发展也为旅游业带来了新的机遇。并且旅游网站已经逐渐成为管理旅游信息的主要模式。因此,开发一个稳定性良好、可用性强的旅游…...

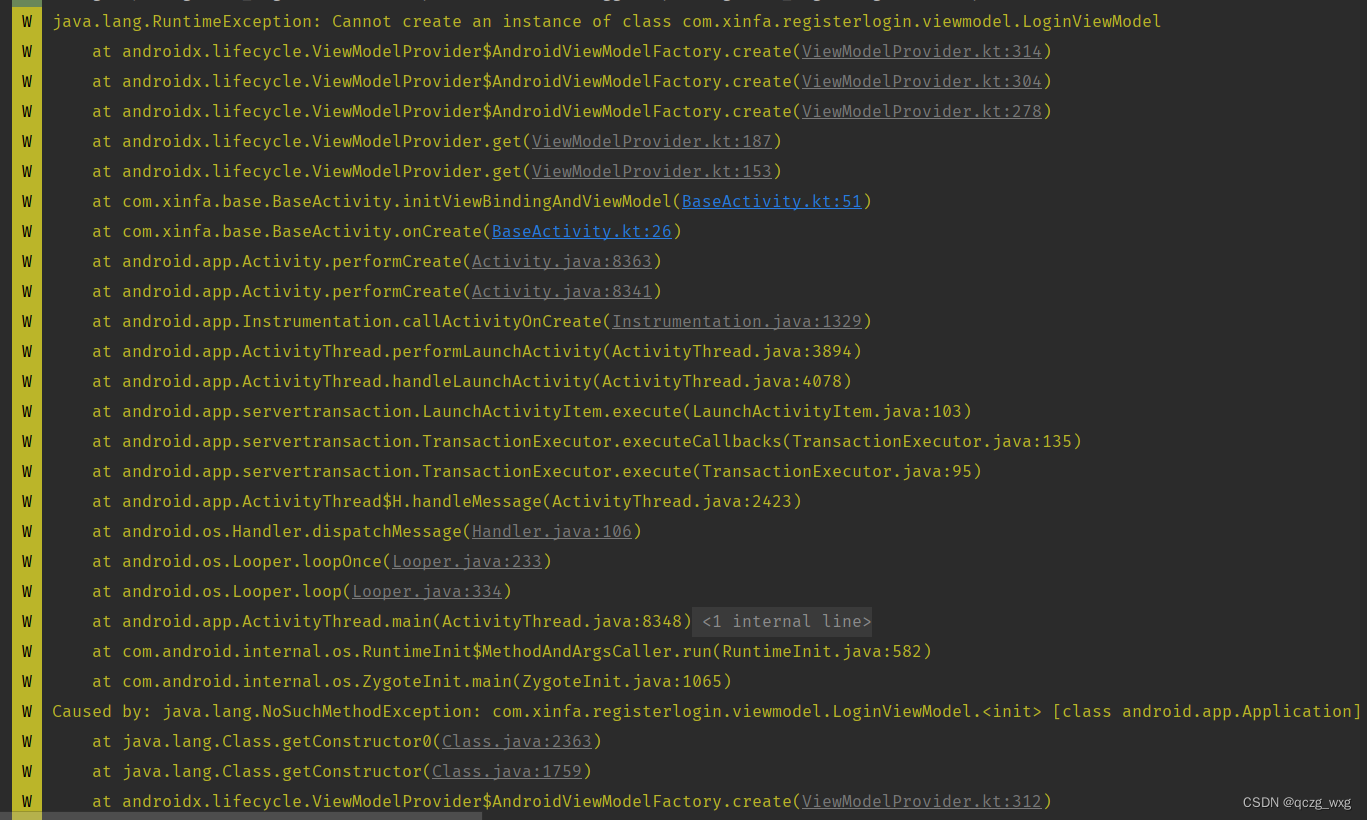

继承AndroidView Model的错误

ViewModelProvider(this)[RegisterViewModel::class.java] 一行简单的代码,总是报这个错误 Caused by: java.lang.NoSuchMethodException: com.xinfa.registerlogin.viewmodel.LoginViewModel. [class android.app.Application] 经过一下午的思索,终于找…...

智慧互联,有序充电--多场景充电

企业微电网能效及充电管理解决方案 安科瑞 崔丽洁 1、企业需求(目的地充电) 站在企业的角度,除了要主动承担碳达峰、碳中和的社会责任,也需要考虑自身的经营和利润,需要结合企业的现状进行改造 企业微电网平台——与…...

yum install libreoffice‘ returned a non-zero

The command ‘/bin/sh -c yum install libreoffice’ returned a non-zero code: 1 1. 异常信息 Is this ok [y/d/N]: Exiting on user command Your transaction was saved, rerun it with:yum load-transaction /tmp/yum_save_tx.2023-08-28.13-42.EftXfl.yumtx The comman…...

Linux知识点 -- 网络基础(一)

Linux知识点 – 网络基础(一) 文章目录 Linux知识点 -- 网络基础(一)一、网络发展二、协议1.OSI七层模型2.TCP/IP五层(或四层)模型 三、网络传输基本流程1.局域网中的两台主机通信流程2.跨网段的两台主机间…...

——分治+排序算法+动态规划)

【leetcode刷题之路】剑指Offer(4)——分治+排序算法+动态规划

文章目录 8 分治算法8.1 【递归】剑指 Offer 07 - 重建二叉树8.2 【递归】【快速幂】剑指 Offer 16 - 数值的整数次方8.3 【递归】剑指 Offer 33 - 二叉搜索树的后序遍历序列8.4 【递归】【分治】剑指 Offer 17 - 打印从1到最大的n位数8.5 【归并排序】【分治】剑指 Offer 51 -…...

美创科技“签”手柠檬文才学堂,共推高校数据安全建设

近日,由柠檬文才学堂联合中国教育在线、东北财经大学网络教育学院共同主办的“三教统筹下高校继续教育数字化转型研讨”顺利召开。 国内高等院校(高职院校)继续教育分管领导,继续教育学院领导及继续教育信息化、教学教务管理、课程…...

【JAVA基础】数据类型,逻辑控制

❤️ Author: 老九 ☕️ 个人博客:老九的CSDN博客 🙏 个人名言:不可控之事 乐观面对 😍 系列专栏: 文章目录 数据类型整型变量 int长整型变量 long单精度浮点数 float双精度浮点数 double字符类型 char字节…...

)

Midjourney订阅决策模型(附2024Q2最新价格与配额表)

更多请点击: https://intelliparadigm.com 第一章:Midjourney订阅决策模型(附2024Q2最新价格与配额表) 选择合适的 Midjourney 订阅计划需综合考量生成频率、图像分辨率、私有化需求及团队协作场景。2024 年第二季度,…...

从零到一:基于Electron与Vue3的现代化桌面应用开发实战

1. 为什么选择ElectronVue3开发桌面应用? 用前端技术开发桌面应用听起来像是"用筷子吃牛排"——看似不搭却意外顺手。我最初接触这个组合是为了快速将一个Vue写的后台管理系统打包成客户端,结果发现开发效率比传统桌面框架高3倍不止。Electron…...

BLDC电机场景化创新:从性能参数到系统解决方案的转型路径

1. 项目概述:在红海中寻找蓝海最近几年,BLDC(无刷直流电机)赛道可以说是热闹非凡。从家里的扫地机器人、空气循环扇,到办公室的静音风扇、电动升降桌,再到路上的两轮电动车、新能源汽车,几乎无处…...

」如何将任务完成率提升至92.7%(实测数据))

为什么头部科技公司已秘密部署ChatGPT 2026预览版?揭秘其「上下文感知决策树(CADT)」如何将任务完成率提升至92.7%(实测数据)

更多请点击: https://intelliparadigm.com 第一章:ChatGPT 2026预览版的演进脉络与战略定位 ChatGPT 2026预览版并非简单的能力叠加,而是OpenAI在可信AI、实时协同与领域自治三大范式下的系统性重构。其核心突破在于将推理过程从黑盒调用转向…...

终极指南:5分钟解锁小爱音箱完整音乐自由

终极指南:5分钟解锁小爱音箱完整音乐自由 【免费下载链接】xiaomusic 使用小爱音箱播放音乐,音乐使用 yt-dlp 下载。 项目地址: https://gitcode.com/GitHub_Trending/xia/xiaomusic 还在为小爱音箱的音乐限制感到困扰?想听什么歌都要…...

开源图书管理系统全栈架构解析:从React前端到Node.js后端实践

1. 项目概述:一个开源图书管理系统的诞生在数字内容日益丰富的今天,无论是个人知识库的整理,还是小型团队、社区的资料共享,一个轻量、灵活且完全自主可控的图书(或广义上的文档)管理系统,始终是…...

如何在Windows上使用iperf3进行专业级网络性能测试:完整指南

如何在Windows上使用iperf3进行专业级网络性能测试:完整指南 【免费下载链接】iperf3-win-builds iperf3 binaries for Windows. Benchmark your network limits. 项目地址: https://gitcode.com/gh_mirrors/ip/iperf3-win-builds iperf3作为专业的网络性能基…...

光栅散射光与仪器杂散光:成因、测量与系统级抑制策略

1. 项目概述:从“完美”光栅到现实噪声在光谱分析、激光系统乃至精密光学测量的世界里,我们常常把衍射光栅想象成一个完美的“光之指挥家”,它能将不同波长的光精准地分离开来,指向各自该去的方向。然而,任何一位有实际…...

别再瞎配了!STM32 GPIO的8种模式到底怎么选?从按键到LED,实战场景帮你一次搞懂

STM32 GPIO模式实战指南:从按键到LED的精准配置策略 在嵌入式开发领域,GPIO(通用输入输出)作为最基础却至关重要的接口,其配置模式的选择往往决定了整个系统的稳定性和响应效率。许多初学者在理论学习阶段能够清晰区分…...

别傻傻手敲了!用C++文件读写自动生成OpenJudge NOI 1.1超级玛丽游戏代码

用C文件操作自动化生成OpenJudge NOI超级玛丽游戏代码 在信息学竞赛中,我们经常会遇到需要输出固定字符图案的题目,比如OpenJudge NOI 1.1中的超级玛丽游戏题目。手动编写这些图案的打印代码不仅耗时耗力,还容易出错。本文将介绍如何利用C的文…...