FPGA原理与结构——FIFO IP核的使用与测试

一、前言

本文介绍FIFO Generator v13.2 IP核的具体使用与例化,在学习一个IP核的使用之前,首先需要对于IP核的具体参数和原理有一个基本的了解,具体可以参考:

FPGA原理与结构——FIFO IP核原理学习![]() https://blog.csdn.net/apple_53311083/article/details/132378996?spm=1001.2014.3001.5501

https://blog.csdn.net/apple_53311083/article/details/132378996?spm=1001.2014.3001.5501

二、FIFO IP核定制

1、FIFO IP核

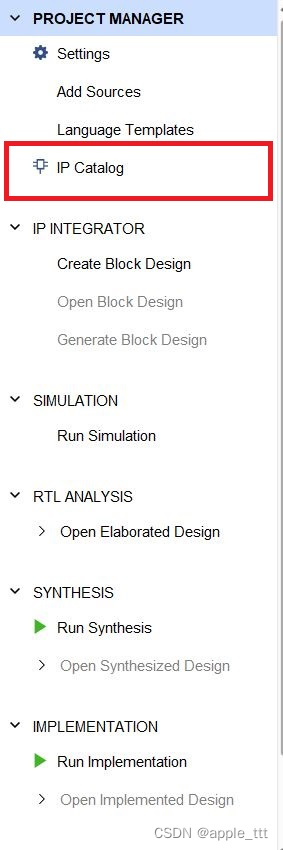

step1 打开vivado工程,点击左侧栏中的IP Catalog

step2 在搜索栏搜索FIFO,找到FIFO Generator核

2、IP核定制

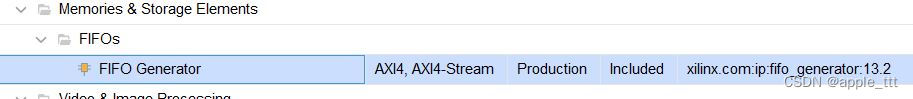

step3 Basic 界面定制

①Component Name :自定义FIFO的名称

②Interface Type :接口类型,我们知道FIFO可以支持Native接口和AXI接口,其中AXI接口包括AXI3,AXI4,AXI Stream类型,这里我们选择Native。

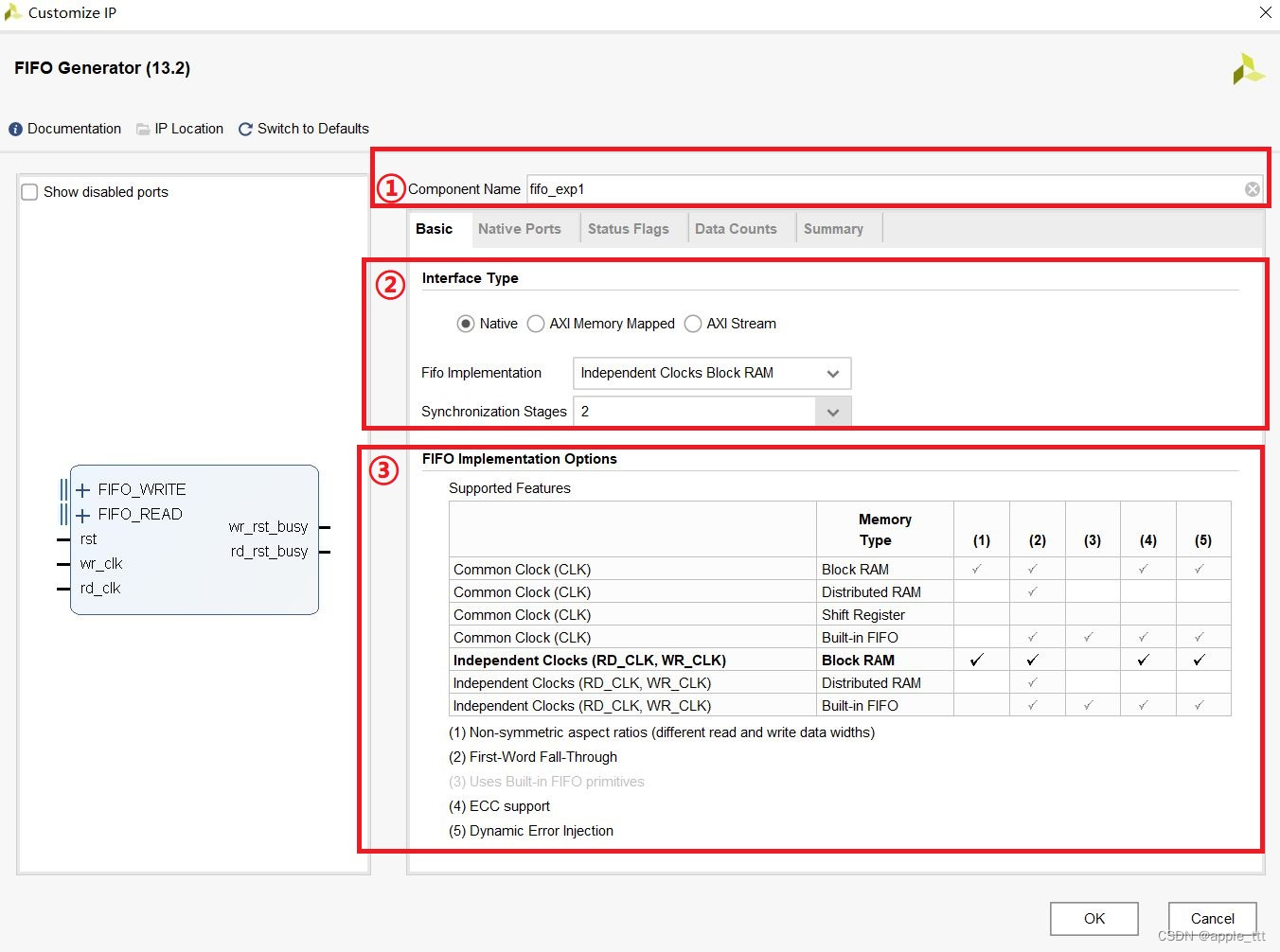

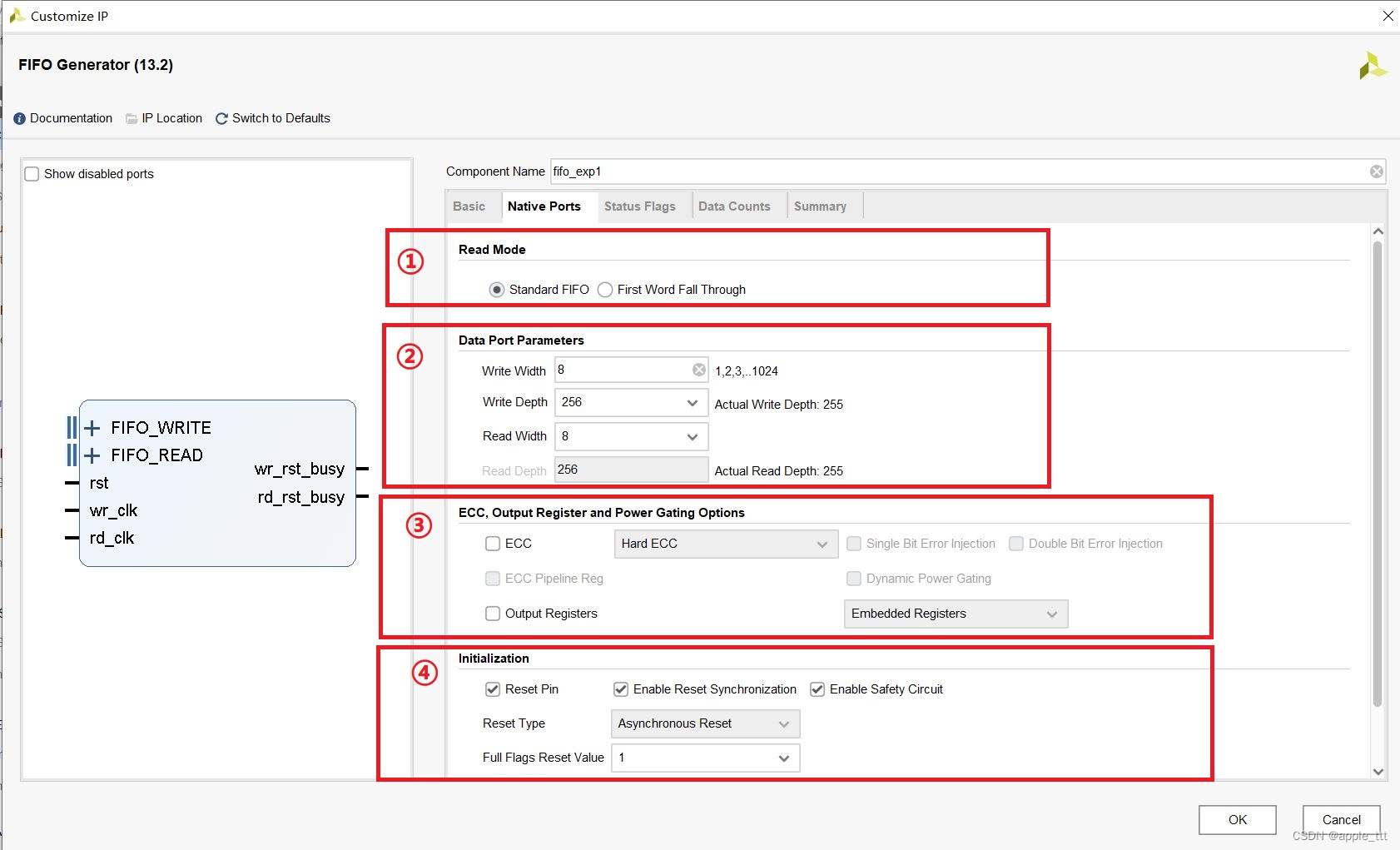

step4 Native Ports 界面设计

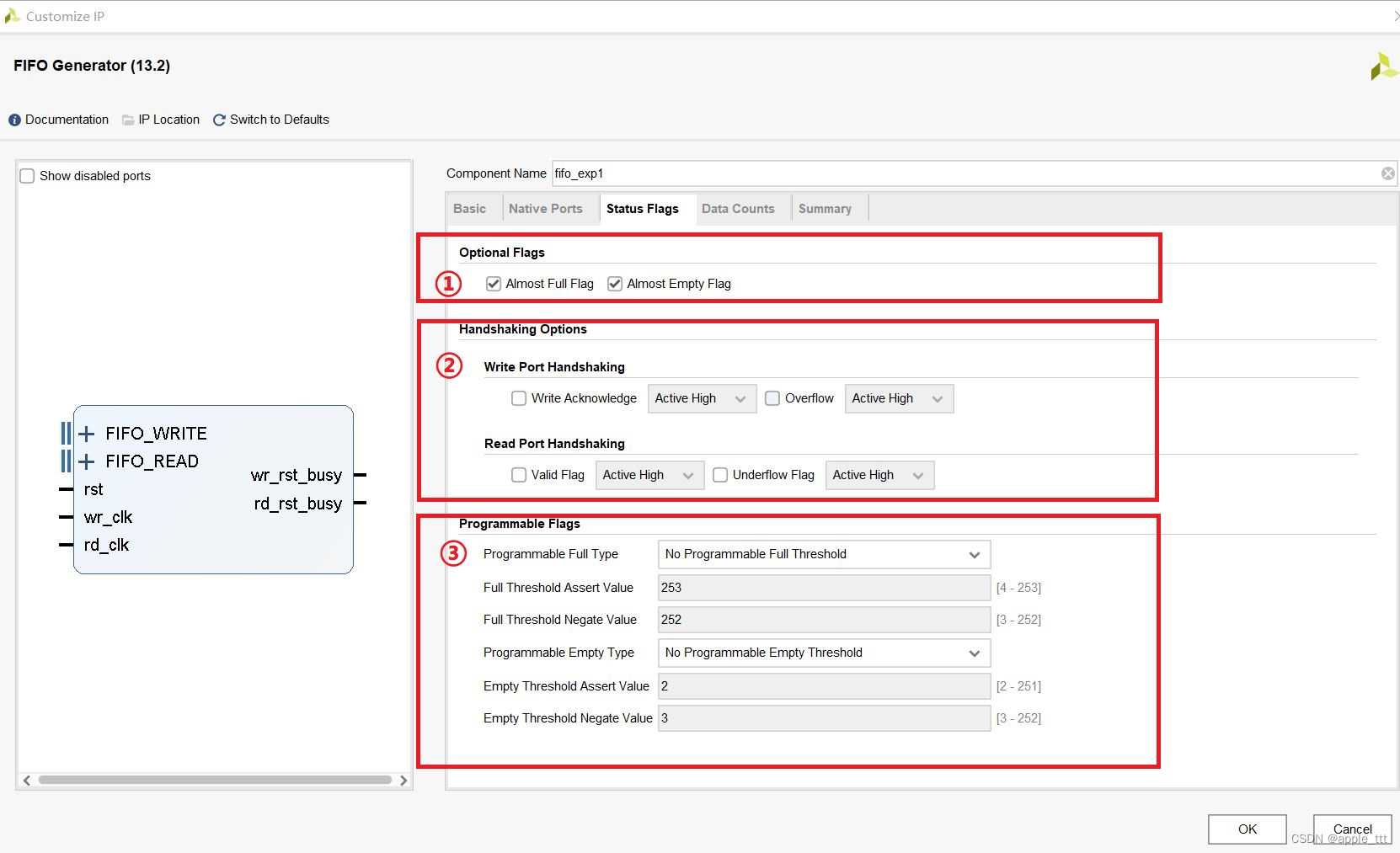

step5 Status Flags 界面定制

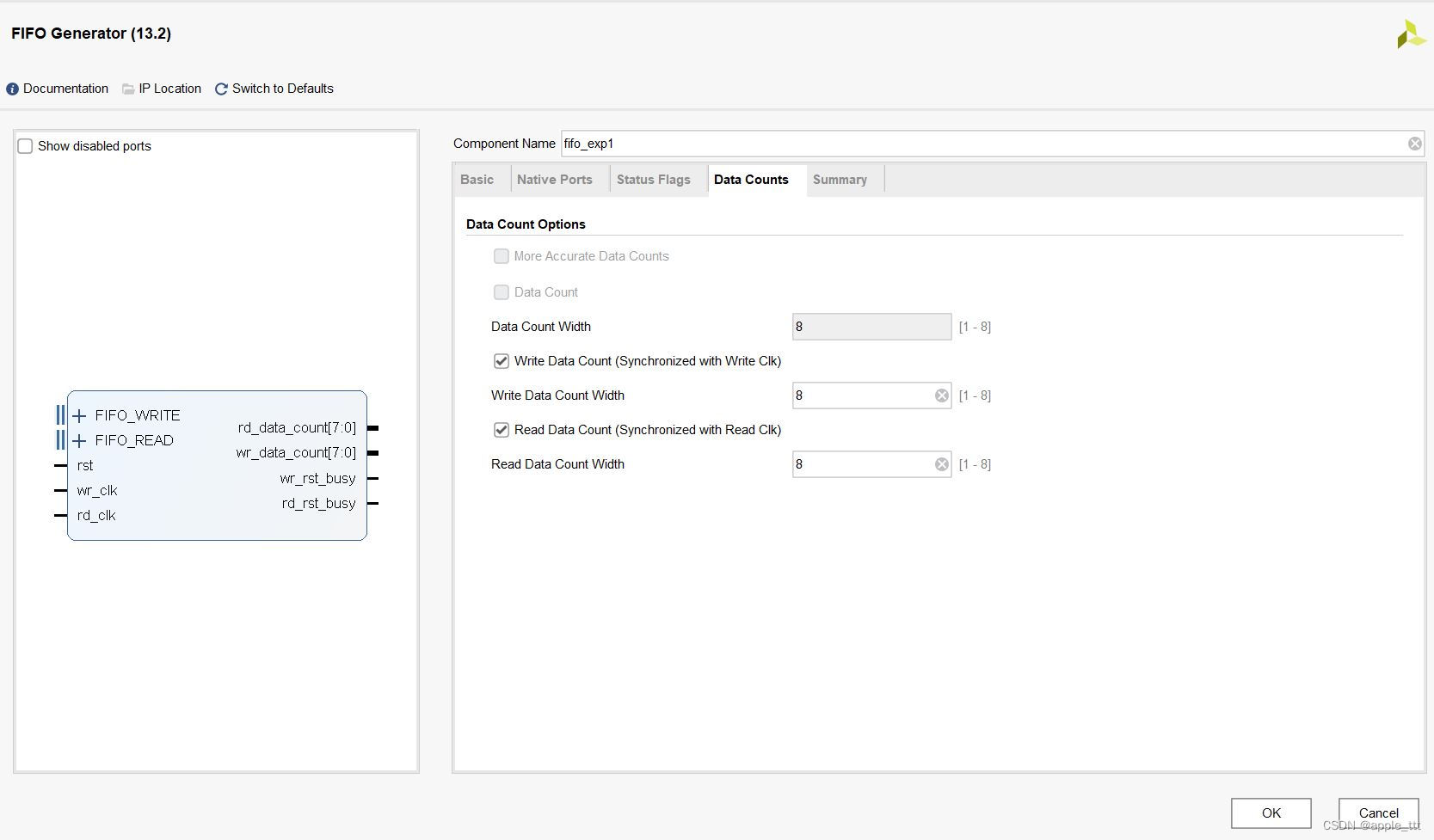

step6 Data Counts

step7 Summary

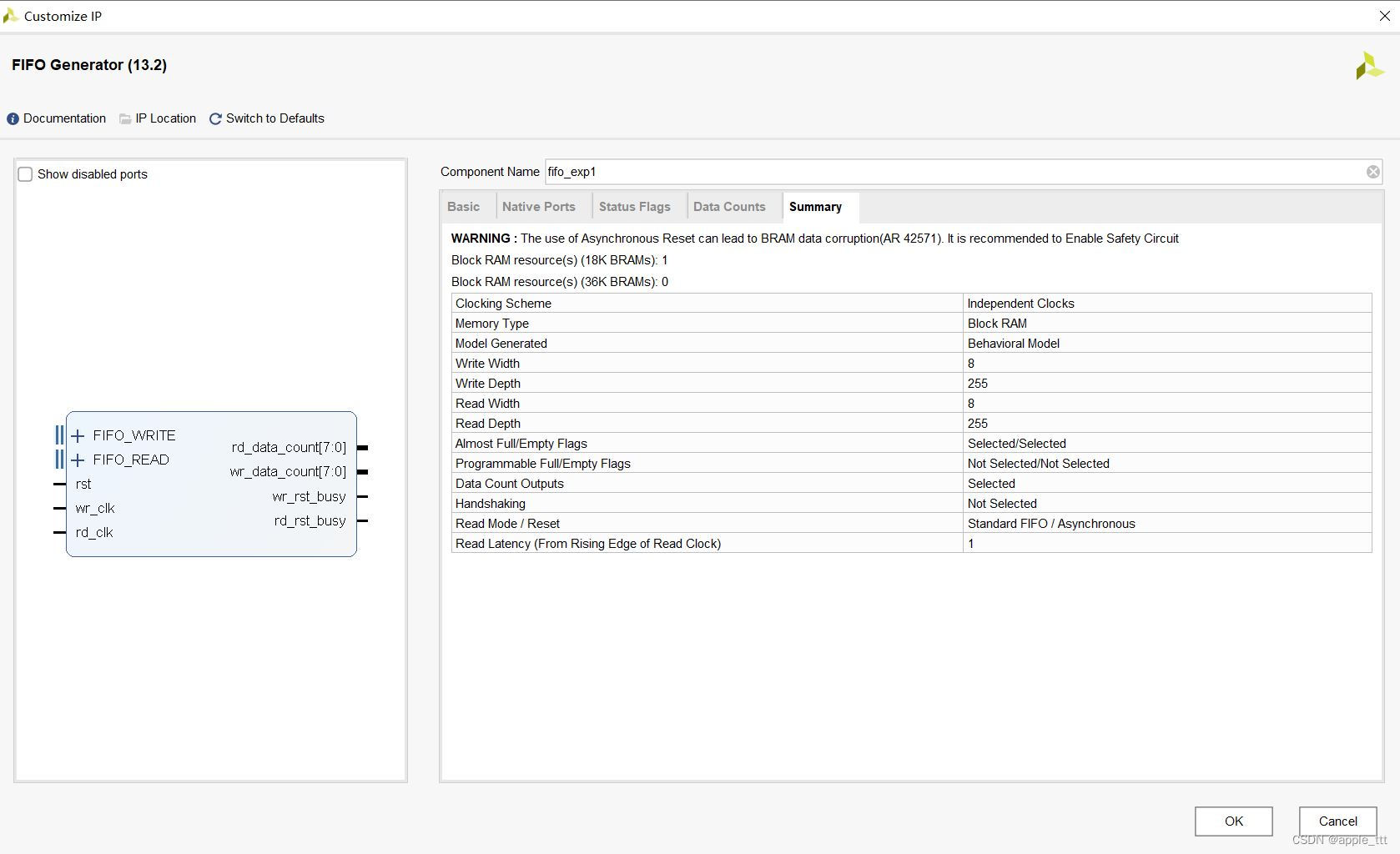

IP核定制的最后一面永远是Summary界面,帮助我们进行一个回顾和检查。

三、IP核测试

首先设计了写FIFO模块和读FIFO模块:

3.1 写fifo模块

//-------------------------------------<写fifo模块>--------------------------------

module fifo_wr(

//-------------------<信号输入>-----------------------input clk, //系统时钟input rst, //复位信号input almost_empty, //FIFO将空信号input almost_full , //FIFO将满信号//-------------------<信号输出>----------------------- output reg fifo_wr_en, //FIFO写使能output reg [7:0] fifo_wr_data //写入FIFO的数据

);//reg define

reg [1:0] state ; //动作状态

reg almost_empty_d0 ; //almost_empty 延迟一拍

reg almost_empty_syn ; //almost_empty 延迟两拍

reg [3:0] dly_cnt ; //延迟计数器//因为 almost_empty 信号是属于FIFO读时钟域的

//所以要将其同步到写时钟域中

always@( posedge clk ) beginif( rst ) beginalmost_empty_d0 <= 1'b0 ;almost_empty_syn <= 1'b0 ;endelse beginalmost_empty_d0 <= almost_empty ;almost_empty_syn <= almost_empty_d0 ;end

end//向FIFO中写入数据

always @(posedge clk ) beginif(rst) beginfifo_wr_en <= 1'b0;fifo_wr_data <= 8'd0;state <= 2'd0;dly_cnt <= 4'd0;endelse begincase(state)2'd0: begin if(almost_empty_syn) begin //如果检测到FIFO将被读空state <= 2'd1; //就进入延时状态end elsestate <= state;end 2'd1: beginif(dly_cnt == 4'd10) begin //延时10拍//原因是FIFO IP核内部状态信号的更新存在延时//延迟10拍以等待状态信号更新完毕 dly_cnt <= 4'd0;state <= 2'd2; //开始写操作fifo_wr_en <= 1'b1; //打开写使能endelsedly_cnt <= dly_cnt + 4'd1;end 2'd2: beginif(almost_full) begin //等待FIFO将被写满fifo_wr_en <= 1'b0; //关闭写使能fifo_wr_data <= 8'd0;state <= 2'd0; //回到第一个状态endelse begin //如果FIFO没有被写满fifo_wr_en <= 1'b1; //则持续打开写使能fifo_wr_data <= fifo_wr_data + 1'd1; //且写数据值持续累加endend default : state <= 2'd0;endcaseend

endendmodule3.2 读FIFO模块

//-------------------------------------<读fifo模块>--------------------------------

module fifo_rd(

//-------------------<信号输入>-----------------------input clk , // 时钟信号input rst , // 复位信号input [7:0] fifo_dout , // 从FIFO读出的数据input almost_full ,// FIFO将满信号input almost_empty,// FIFO将空信号//-------------------<信号输出>----------------------- output reg fifo_rd_en // FIFO读使能

);//reg define

reg [1:0] state ; // 动作状态

reg almost_full_d0 ; // fifo_full 延迟一拍

reg almost_full_syn ; // fifo_full 延迟两拍

reg [3:0] dly_cnt ; // 延迟计数器//因为 fifo_full 信号是属于FIFO写时钟域的

//所以要将其同步到读时钟域中

always@( posedge clk ) beginif( rst ) beginalmost_full_d0 <= 1'b0 ;almost_full_syn <= 1'b0 ;endelse beginalmost_full_d0 <= almost_full ;almost_full_syn <= almost_full_d0 ;end

end//读出FIFO的数据

always @(posedge clk ) beginif(rst) beginfifo_rd_en <= 1'b0;state <= 2'd0;dly_cnt <= 4'd0;endelse begincase(state)2'd0: beginif(almost_full_syn) //如果检测到FIFO将被写满state <= 2'd1; //就进入延时状态elsestate <= state;end 2'd1: beginif(dly_cnt == 4'd10) begin //延时10拍//原因是FIFO IP核内部状态信号的更新存在延时//延迟10拍以等待状态信号更新完毕dly_cnt <= 4'd0;state <= 2'd2; //开始读操作endelsedly_cnt <= dly_cnt + 4'd1;end2'd2: beginif(almost_empty) begin //等待FIFO将被读空fifo_rd_en <= 1'b0; //关闭读使能state <= 2'd0; //回到第一个状态endelse //如果FIFO没有被读空fifo_rd_en <= 1'b1; //则持续打开读使能end default : state <= 2'd0;endcaseend

endendmodule3.3 顶层模块

module fifo_top(

//-------------------<信号输入>-----------------------input sys_clk, //系统时钟input rst //复位信号

);wire [7:0] din; //fifo的输入数据(写入的数据)wire wr_en; //写使能wire rd_en; //读使能wire [7:0] dout; //fifo的输出数据(读出的数据)wire full; //fifo满信号wire almost_full; //fifo将满标志wire empty; //fifo空标志wire almost_empty; //fifo将空标志wire [7:0]rd_data_count; //fifo写时钟域的数据计数wire [7:0]wr_data_count; //fifo读时钟域的数据计数wire wr_rst_busy;wire rd_data_count; //-------------------<IP核例化>-----------------------

fifo_exp1 fifo1 (.rst (rst), // input wire rst.wr_clk (sys_clk), // input wire wr_clk.rd_clk (sys_clk), // input wire rd_clk.din (din), // input wire [7 : 0] din.wr_en (wr_en), // input wire wr_en.rd_en (rd_en), // input wire rd_en.dout (dout), // output wire [7 : 0] dout.full (full), // output wire full.almost_full (almost_full), // output wire almost_full.empty (empty), // output wire empty.almost_empty (almost_empty), // output wire almost_empty.rd_data_count (rd_data_count), // output wire [7 : 0] rd_data_count.wr_data_count (wr_data_count), // output wire [7 : 0] wr_data_count.wr_rst_busy (wr_rst_busy), // output wire wr_rst_busy.rd_rst_busy (rd_rst_busy) // output wire rd_rst_busy

);//例化写FIFO模块

fifo_wr fifo_wr_u1(.clk ( sys_clk ), // 写时钟.rst ( rst ), // 复位信号.fifo_wr_en ( wr_en ) , // fifo写请求.fifo_wr_data ( din ) , // 写入FIFO的数据.almost_empty ( almost_empty ), // fifo空信号.almost_full ( almost_full ) // fifo满信号

);//例化读FIFO模块

fifo_rd fifo_rd_u1(.clk ( sys_clk ), // 读时钟.rst ( rst ), // 复位信号.fifo_rd_en ( rd_en ), // fifo读请求.fifo_dout ( dout ), // 从FIFO输出的数据.almost_empty ( almost_empty ), // fifo空信号.almost_full ( almost_full ) // fifo满信号

);endmodule

3.4 测试模块

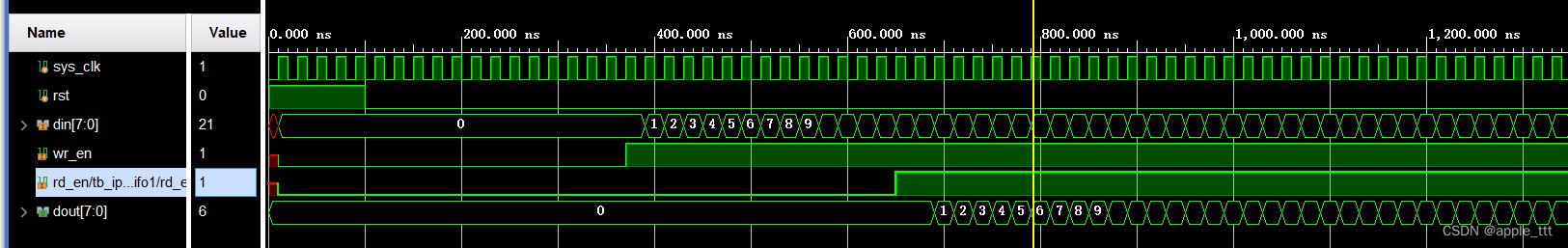

`timescale 1ns / 1psmodule tb_ip_fifo( );// Inputsreg sys_clk;reg rst;// Instantiate the Unit Under Test (UUT)fifo_top tb1_fifo_top (.sys_clk (sys_clk), .rst (rst));//Genarate the clkparameter PERIOD = 20;always beginsys_clk = 1'b0;#(PERIOD/2) sys_clk = 1'b1;#(PERIOD/2);end initial begin// Initialize Inputsrst = 1;// Wait 100 ns for global reset to finish#100 ;rst = 0;// Add stimulus hereendendmodule3.4 测试结果

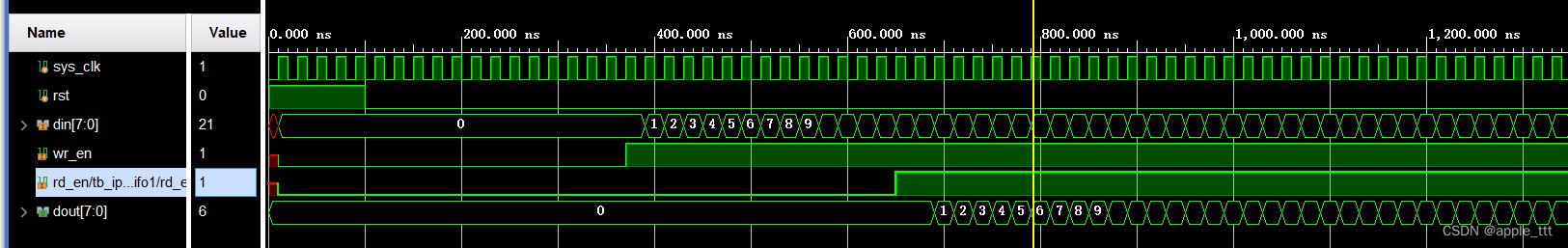

通过看到FIFO如我们预期的写入和读出数据,读出的数据满足先入先出的原则。

四、总结

本文总结了FIFO IP核的使用方法,给出了各个配置参数的具体含义及配置方式,并对相关的设计进行了测试。

相关文章:

FPGA原理与结构——FIFO IP核的使用与测试

一、前言 本文介绍FIFO Generator v13.2 IP核的具体使用与例化,在学习一个IP核的使用之前,首先需要对于IP核的具体参数和原理有一个基本的了解,具体可以参考: FPGA原理与结构——FIFO IP核原理学习https://blog.csdn.net/apple_5…...

ABB CMA120 3DDE300400面板

人机界面:ABB CMA120 3DDE300400 面板通常具有用户友好的人机界面,可用于监视和控制连接设备和系统的操作。 图形显示:该面板通常具有高分辨率的液晶显示屏,用于显示图形界面和实时数据,以便操作员更容易理解和管理工…...

【代码随想录day25】动态规划:01背包理论基础

题目 有n件物品和一个最多能背重量为w 的背包。第i件物品的重量是weight[i],得到的价值是value[i] 。每件物品只能用一次,求解将哪些物品装入背包里物品价值总和最大。 代码 dp[i][j]: 表示从0~i个物品中选物品放到容量为j的背包中所能获得的最大价值 …...

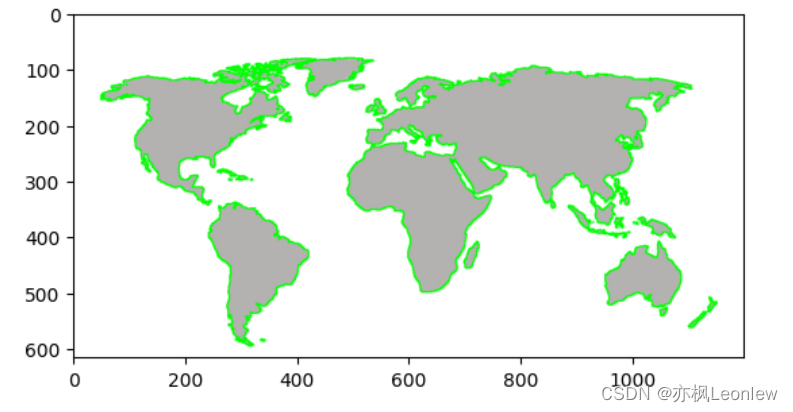

Python Opencv实践 - 轮廓检测

import cv2 as cv import numpy as np import matplotlib.pyplot as pltimg cv.imread("../SampleImages/map.jpg") print(img.shape) plt.imshow(img[:,:,::-1])#Canny边缘检测 edges cv.Canny(img, 127, 255, 0) plt.imshow(edges, cmapplt.cm.gray)#查找轮廓 #c…...

c#保留两位小数

1.使用ToString()方法和格式字符串 double number 3.1415926; string result number.ToString(“F2”); // 将number转换为字符串,并保留两位小数 Console.WriteLine(result); // 输出结果为 “3.14” 2.使用字符串插值和格式字符串 double number 3.1415926;…...

[machineLearning]非监督学习unsupervised learning

1.什么是非监督学习 常见的神经网络是一种监督学习,监督学习的主要特征即为根据输入来对输出进行预测,最终会得到一个输出数值.而非监督学习的目的不在于输出,而是在于对读入的数据进行归类,选取特征,打标签,通过对于数据结构的分析来完成这些操作, 很少有最后的输出操作. 从…...

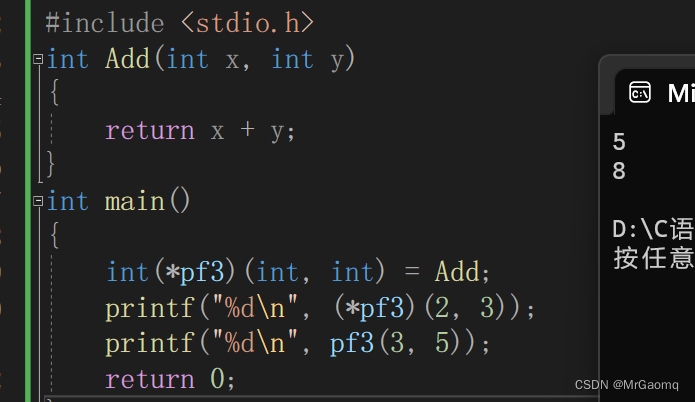

C语言深入理解指针(非常详细)(四)

目录 字符指针变量数组指针变量数组指针变量是什么数组指针变量怎么初始化 二维数组传参的本质函数指针变量函数指针变量的创建函数指针变量的使用代码typedef关键字 函数指针数组转移表 字符指针变量 字符指针在之前我们有提到过,(字符)&am…...

知识库建设:从0到1搞定知识库建设的方法论分享

如果我们想要搭建一个知识库,前提是我们要明确知道这个知识库是干什么用的,只有了解知识库的应用场景才能知道如何去建设知识库。 知识库建设 以常见的电商客服为例,客户会经常咨询什么时候发货,怎么退货,怎么换货………...

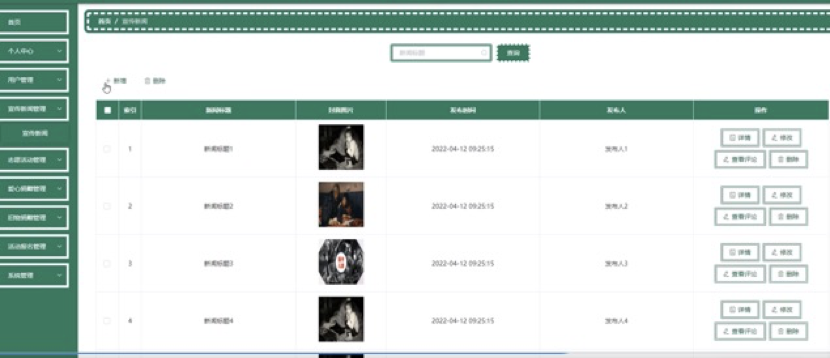

SpringBoot+Vue 的留守儿童系统的研究与实现,2.0 版本,附数据库、教程

博主介绍:✌程序员徐师兄、7年大厂程序员经历。全网粉丝30W,Csdn博客专家、掘金/华为云/阿里云/InfoQ等平台优质作者、专注于Java技术领域和毕业项目实战✌ 文章目录 1.研究背景2. 技术栈3.系统分析4系统设计5系统的详细设计与实现5.1系统功能模块5.2管理员功能模块…...

28.考试

Description 小学期马上就要结束了,为了检验大家的学习成果,老师进行了一次考试。然而小徐前两周半都忙于练习篮球,几乎没有学习,因此考试时很可能做不完所有题目。 但小徐仍然想要拿到尽可能高的分数,因此在做题时需要…...

浏览器窗口间的通信

一、汇总 二、同源策略 三、webSocket (无跨域限制) 优点:无跨域限制 缺点:成本高 四、客户端存储 1、localStorage onStorage 例子: 2、定时器 客户端存储 例子: 缺点: 五、postMessage (无跨域…...

MATLAB 的 plot 绘图

文章目录 SyntaxDescriptionplot(X,Y)plot(X,Y,LineSpec)plot(X1,Y1,…,Xn,Yn)plot(X1,Y1,LineSpec1,...,Xn,Yn,LineSpecn)plot(Y)plot(Y,LineSpec)plot(tbl,xvar,yvar)plot(tbl,yvar)plot(ax,___)plot(___,Name,Value)p plot(___) plot: 2-D line plot Syntax plot(X,Y)plo…...

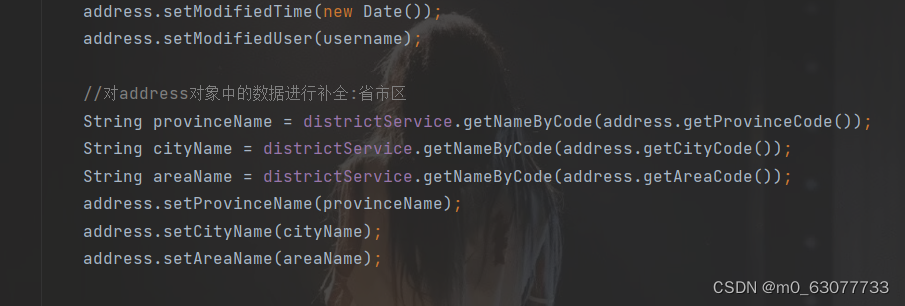

SpringBoot项目--电脑商城【获取省市区列表】

1.易错点 1.错误做法 新增收货地址页面的三个下拉列表的内容展示没有和数据库进行交互,而是通过前端实现的(将代码逻辑放在了distpicker.data.js文件中),实现方法是在加载新增收货地址页面时加载该js文件,这种做法不可取 2.正确做法 把这些数据保存到数据库中,用户点击下拉…...

使用git把本地项目关联远程代码仓库,并推送到远程仓库

你在本地新建了一个项目,写好了代码,但是没有关联远程仓库,怎么关联并上传呢? 你要先去gitee创建一个代码仓库,然后复制http地址。 首次提交项目代码到一个新建的远程仓库: 1、通过命令 git init 把这个…...

Spring+MyBatis使用collection标签的两种使用方法

目录 项目场景: 实战操作: 1.创建菜单表 2.创建实体 3.创建Mapper 4.创建xml 属性描述: 效率比较: 项目场景: 本文说明了Spring BootMyBatis使用collection标签的两种使用方法 1. 方法一: 关联查询 2. 方法…...

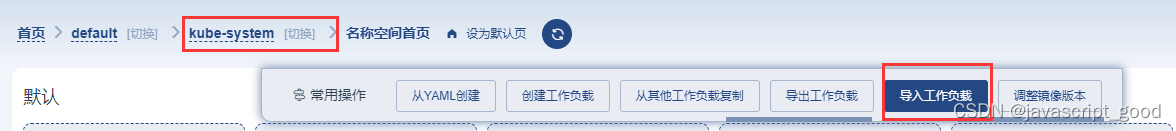

k8s集群中集群方式安装nacos

1、前提条件 一个k8s集群,其中有三个master 节点,这三个节点的标签名称为etcd 三个master节点的ip 分别为:192.165.187.170 、192.165.187.171、192.165.187.172一个mysql 数据库, 数据库的ip 为:192.165.187.180 用户…...

极客时间:数据结构与算法之美【学习笔记+思考实践】

本篇是 《极客时间:数据结构与算法之美》课程的学习笔记和带有自己的一些思考实践。原文学习链接如下:https://time.geekbang.org/column/intro/100017301 开篇词 | 从今天起,跨过“数据结构与算法”这道坎01 | 为什么要学习数据结构和算法&a…...

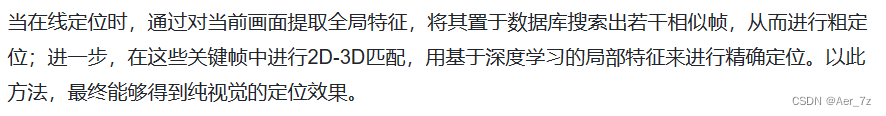

基于视觉重定位的室内AR导航项目思路(2):改进的建图和定位分离的项目思路

文章目录 一、建图二、定位首先是第一种方法:几何方法其次是第二种方法:图像检索方法最后是第三种方法:深度学习方法 前情提要: 是第一次做项目的小白,文章内的资料介绍如有错误,请多包含! 一、…...

nodejs+vue+elementui精品课程网站设计

前端技术:nodejsvueelementui基于nodejs语言、vue.js框架、B/S架构、Mysql数据库设计并实现了精品课程网站设计。系统主要包括首页、个人中心、用户管理、课程信息管理、课程分类管理、学习论坛、在线试题管理、试题管理、系统管理、考试管理等功能模块。 本文首先介…...

40个Linux常用命令组合

1.删除0字节文件 find -type f -size 0 -exec rm -rf {} \; 2.查看进程 按内存从大到小排列 ps -e -o "%C : %p : %z : %a"|sort -k5 -nr 3.按cpu利用率从大到小排列 ps -e -o "%C : %p : %z : %a"|sort -nr 4.打印说cache里的URL grep -r -a jpg …...

基于容器技术的在线代码沙盒:架构设计与安全实践

1. 项目概述:一个开箱即用的在线代码运行沙盒最近在折腾一些需要快速验证代码片段、或者给团队做技术分享的场景,我发现一个痛点:环境配置太麻烦了。你想让新人跑个Python脚本,他可能得先装Python、配环境变量、装依赖库ÿ…...

安卓客户端架构解析:从MVVM到网络通信的完整实践

1. 项目概述:一个面向安卓设备的智能客户端最近在整理手头的开源项目时,发现了一个挺有意思的仓库,名字叫TOM88812/xiaozhi-android-client。光看这个标题,你可能会有点摸不着头脑,这“小智”到底是个啥?是…...

【模拟电路】Circuit JS:从零到一,构建你的首个交互式电路实验

1. 初识Circuit JS:你的虚拟电路实验室 第一次接触Circuit JS时,我正为一个简单的LED电路设计发愁。传统仿真软件要么安装复杂,要么收费昂贵,直到发现这个直接在浏览器里运行的免费工具。打开网页的瞬间,就像走进了中学…...

Linux磁盘挂载与开机自启配置

Linux磁盘挂载与开机自启配置磁盘挂载是 Linux 存储管理中的基础操作。很多线上问题都与挂载配置有关,例如重启后数据盘没挂上、路径指向错误分区、应用因挂载点缺失而启动失败。中级阶段不仅要会临时挂载,更要理解永久挂载的配置方式和风险控制。一、先…...

解密ComfyUI-WanVideoWrapper:在ComfyUI中突破AI视频生成的技术壁垒

解密ComfyUI-WanVideoWrapper:在ComfyUI中突破AI视频生成的技术壁垒 【免费下载链接】ComfyUI-WanVideoWrapper 项目地址: https://gitcode.com/GitHub_Trending/co/ComfyUI-WanVideoWrapper 你是否曾想过将脑海中的创意场景转化为生动的视频内容࿰…...

2025届毕业生推荐的AI学术平台推荐榜单

Ai论文网站排名(开题报告、文献综述、降aigc率、降重综合对比) TOP1. 千笔AI TOP2. aipasspaper TOP3. 清北论文 TOP4. 豆包 TOP5. kimi TOP6. deepseek 在学术写作范畴之内,怎样迅速、精确地给论文确定一个既契合规范又能够切实有效吸…...

【197期】视频一键转图文笔记

这期分享一个自己一直在用的视频转图文笔记工具,把视频文件和对应的字幕文件拖进去,一键就能生成详细的图文笔记。目前自媒体平台上的文章基本都靠这个流程来出,不用另外再写一遍,效率高了很多。使用方式很简单,把视频…...

【Appium 系列】第09节-数据驱动测试 — YAML 数据 + parametrize

对应代码:core/data_driver.py(206行)、testcases/data/login_users.yaml、testcases/yaml/login_test_cases.yaml说明:本节代码示例来自一个真实的移动端自动化测试项目,业务名称和API路径已做模糊化处理。登录测试少…...

常见 PE 启动盘

文章目录常见 PE 启动盘一、强烈推荐 纯净无捆绑类二、功能强大 可选推广类三、老牌经典 捆绑较多类四、官方原版常见 PE 启动盘 这里整理了一份常见的PE启动盘大全,按纯净度和口碑分类,并附上官网或可靠的下载渠道。 一、强烈推荐 纯净无捆绑类 这…...

ARM架构计数器与定时器虚拟化技术详解

1. ARM架构中的计数器-定时器虚拟化技术概述在现代虚拟化环境中,精确的时间管理是确保虚拟机性能和功能完整性的关键要素。ARMv8/v9架构通过一系列精心设计的系统寄存器和硬件特性,为hypervisor提供了强大的计数器与定时器虚拟化能力。这项技术允许每个虚…...