一起学习用Verilog在FPGA上实现CNN----(八)integrationFC设计

1 integrationFC设计

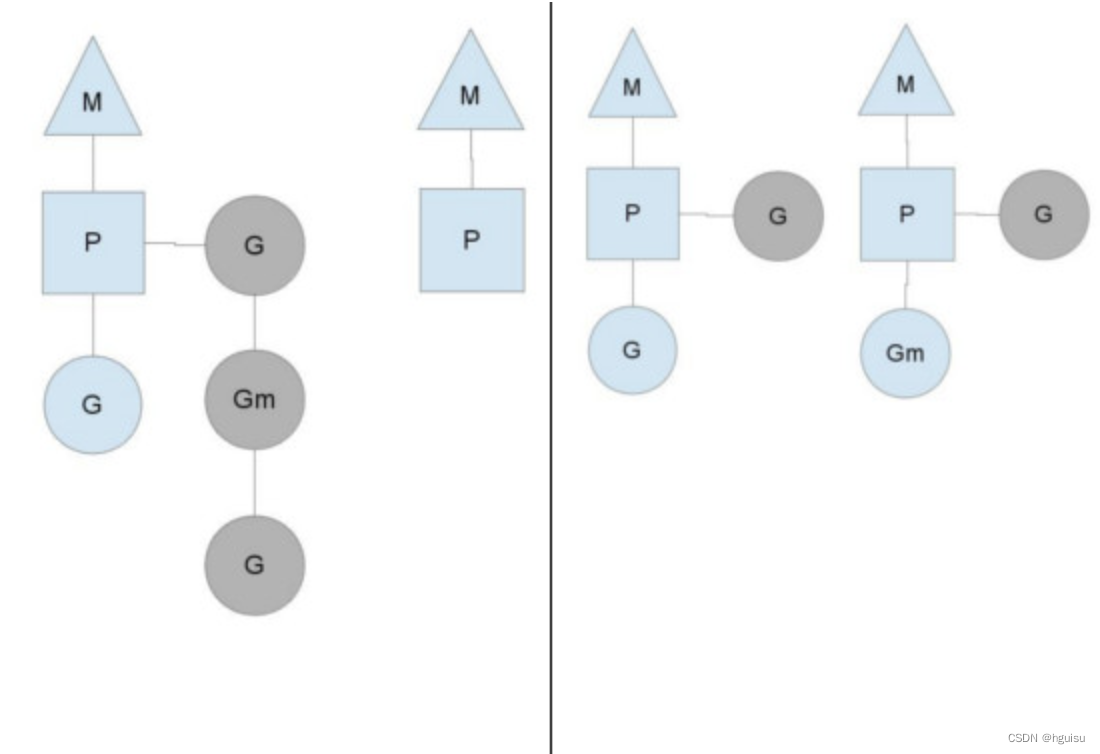

LeNet-5网络结构全连接部分如图所示,该部分有2个全连接层,1个TanH激活层,1个SoftMax激活层:

图片来自附带的技术文档《Hardware Documentation》

integrationFC部分原理图,如图所示,图中W1和W2分别是存储全连接层FC1和全连接层FC2的权重:

全连接层FC1输入神经元个数为3840/32=120个,输出神经元个数为2688/32=84个,原理图如图所示:

Tanh激活层的输入输出位宽均为32位,原理图如图所示:

全连接层FC2输入神经元个数为2688/32=84个,输出神经元个数为320/32=10个,原理图如图所示:

SMax激活层的输入输出位宽均为32位,原理图如图所示:

2 integrationFC程序

创建UsingTheTanh文件:

输入文件名:

双击打开,输入代码:

module UsingTheTanh(x,clk,Output,resetExternal,FinishedTanh);

parameter DATA_WIDTH=32;

parameter nofinputs=784;// deterimining the no of inputs entering the function

input resetExternal;// controlling this layer

input signed [nofinputs*DATA_WIDTH-1:0] x;

input clk;

output reg FinishedTanh;

reg reset;// for the inner tanh

output reg [nofinputs*DATA_WIDTH-1:0]Output;

wire [DATA_WIDTH-1:0]OutputTemp;

reg [7:0]counter=0;

wire Finished;

reg [7:0]i;

// the inner tanh taking inputs in 32 bits and then increment using the i operator

HyperBolicTangent TanhArray (x[DATA_WIDTH*i+:DATA_WIDTH],reset,clk,OutputTemp,Finished);always@(posedge clk)

begin

// if the external reset =1 then make everything to 0

if(resetExternal==1) begin reset=1;i=0;FinishedTanh=0; end

//checking if the tanh is not finished so continue your operation and low down the reset to continueelse if(FinishedTanh==0) begin if(reset==1)begin reset=0; end // if it is finished then store the output of the tanh and increment the input forwardelse if (Finished==1)begin Output[DATA_WIDTH*i+:DATA_WIDTH]=OutputTemp;reset=1;i=i+1;end

// check if all the inputs are finished then the layer is OK

if(i==nofinputs)begin FinishedTanh=1;end

end end

endmodule 如图所示:

创建HyperBolicTangent文件:

双击打开,输入代码:

module HyperBolicTangent (x,reset,clk,OutputFinal,Finished);

parameter DATA_WIDTH=32;

localparam taylor_iter=4;//I chose 5 Taylor Coefficients to undergo my tanh operation

input signed [DATA_WIDTH-1:0] x;input clk;

input reset;

output reg Finished;

output reg[DATA_WIDTH-1:0] OutputFinal;

reg [DATA_WIDTH*taylor_iter-1:0] Coefficients ; //-17/315 2/15 -1/3 1

wire [DATA_WIDTH-1:0] Xsquared; //To always generate a squared version of the input to increment the power by 2 always.

reg [DATA_WIDTH-1:0] ForXSqOrOne; //For Multiplying The power of X(1 or X^2)

reg [DATA_WIDTH-1:0] ForMultPrevious; //output of the first multiplication which is either with 1 or x(X or Output1)

wire [DATA_WIDTH-1:0] OutputOne; //the output of Mulitplying the X term with its corresponding power coeff.

wire [DATA_WIDTH-1:0] OutOfCoeffMult; //the output of Mulitplying the X term with its corresponding power coeff.

reg [DATA_WIDTH-1:0] OutputAdditionInAlways;

wire [DATA_WIDTH-1:0] OutputAddition; //the output of the Addition each cycle floatMult MSquaring (x,x,Xsquared);//Generating x^2

floatMult MGeneratingXterm (ForXSqOrOne,ForMultPrevious,OutputOne); //Generating the X term [x,x^3,x^5,...]

floatMult MTheCoefficientTerm (OutputOne,Coefficients[DATA_WIDTH-1:0],OutOfCoeffMult); //Multiplying the X term by its corresponding coeff.

floatAdd FADD1 (OutOfCoeffMult,OutputAdditionInAlways,OutputAddition); //Adding the new term to the previous one ex: x-1/3*(x^3)

reg [DATA_WIDTH-1:0] AbsFloat; //To generate an absolute value of the input[For Checking the convergence]always @ (posedge clk) begin

AbsFloat=x;//Here i hold the input then i make it positive whatever its sign to be able to compare to implement the rule |x|>pi/2 which is the convergence rule

AbsFloat[31]=0;

if(AbsFloat>32'sb00111111110010001111010111000011)begin //The Finished bit is for letting the bigger module know that the tanh is finishedif (x[31]==0)begin OutputFinal= 32'b00111111100000000000000000000000;Finished =1'b 1;//here i assign it an immediate value of Positive Floating oneend if (x[31]==1)begin OutputFinal= 32'b10111111100000000000000000000000;Finished =1'b 1;//here i assign it an immediate value of Negative Floating oneend

end

//here i handle the case of it equals +- pi/2 so i got the exact value and handle it also immediately

else if (AbsFloat==32'sb00111111110010001111010111000011)begin if (x[31]==0)begin OutputFinal=32'b00111111110010001111010111000011;Finished=1'b 1;endelse begin OutputFinal=32'b10111111110010001111010111000011;Finished=1'b 1;endend

else begin //First instance of the tanhif(reset==1'b1)begin Coefficients=128'b10111101010111010000110111010001_00111110000010001000100010001001_10111110101010101010101010101011_00111111100000000000000000000000;//the 4 coefficients of taylor expansionForXSqOrOne=32'b00111111100000000000000000000000; //initially 1OutputAdditionInAlways=32'b00000000000000000000000000000000; //initially 0ForMultPrevious=x;

Finished=0;

end

else beginForXSqOrOne=Xsquared;ForMultPrevious=OutputOne; //get the output of the second multiplication to multiply with xCoefficients=Coefficients>>32; //shift 32 bit to divide the out_m1 with the new number to compute the factorialOutputAdditionInAlways=OutputAddition;Finished=0;

end

// the end of the tanh

if(Coefficients==128'b00000000000000000000000000000000_00000000000000000000000000000000_00000000000000000000000000000000_00000000000000000000000000000000)begin OutputFinal=OutputAddition;Finished =1'b 1;

end

end

end

endmodule

如图所示:

双击打开integrationFC,修改代码如下:

module integrationFC (clk,reset,iFCinput,CNNoutput);parameter DATA_WIDTH = 32;

parameter IntIn = 120;

parameter FC_1_out = 84;

parameter FC_2_out = 10;input clk, reset;

input [IntIn*DATA_WIDTH-1:0] iFCinput;

output [FC_2_out*DATA_WIDTH-1:0] CNNoutput;wire [FC_1_out*DATA_WIDTH-1:0] fc1Out;

wire [FC_1_out*DATA_WIDTH-1:0] fc1OutTanh;wire [FC_2_out*DATA_WIDTH-1:0] fc2Out;

wire [FC_2_out*DATA_WIDTH-1:0] fc2OutSMax;wire [DATA_WIDTH*FC_1_out-1:0] wFC1;

wire [DATA_WIDTH*FC_2_out-1:0] wFC2;reg FC1reset;

reg FC2reset;

reg TanhReset;

wire TanhFlag;

reg SMaxEnable;

wire DoneFlag;integer counter;

reg [7:0] address1;

reg [7:0] address2;weightMemory

#(.INPUT_NODES(IntIn),.OUTPUT_NODES(FC_1_out),.file("E:/FPGA_Learn/FPGA/Day1211/Weight/weightsdense_1_IEEE.txt"))W1(.clk(clk),.address(address1),.weights(wFC1));weightMemory

#(.INPUT_NODES(FC_1_out),.OUTPUT_NODES(FC_2_out),.file("E:/FPGA_Learn/FPGA/Day1211/Weight/weightsdense_2_IEEE.txt"))W2(.clk(clk),.address(address2),.weights(wFC2)); layer

#(.INPUT_NODES(IntIn),.OUTPUT_NODES(FC_1_out))FC1(.clk(clk),.reset(FC1reset),.input_fc(iFCinput),.weights(wFC1),.output_fc(fc1Out));layer

#(.INPUT_NODES(FC_1_out),.OUTPUT_NODES(FC_2_out))FC2(.clk(clk),.reset(FC2reset),.input_fc(fc1OutTanh),.weights(wFC2),.output_fc(fc2Out));UsingTheTanh

#(.nofinputs(FC_1_out))

Tanh1(.x(fc1Out),.clk(clk),.Output(fc1OutTanh),.resetExternal(TanhReset),.FinishedTanh(TanhFlag));softmax SMax(.inputs(fc2Out),.clk(clk),.enable(SMaxEnable),.outputs(CNNoutput),.ackSoft(DoneFlag));always @(posedge clk or posedge reset) beginif (reset == 1'b1) beginFC1reset = 1'b1;FC2reset = 1'b1;TanhReset = 1'b1;SMaxEnable = 1'b0;counter = 0;address1 = -1;address2 = -1;endelse begincounter = counter + 1;if (counter > 0 && counter < IntIn + 10) beginFC1reset = 1'b0;endelse if (counter > IntIn + 10 && counter < IntIn + 12 + FC_1_out*6) beginTanhReset = 1'b0;address2 = -3;endelse if (counter > IntIn + 12 + FC_1_out*6 && counter < IntIn + 12 + FC_1_out*6 + FC_1_out + 10) beginFC2reset = 1'b0;endelse if (counter > IntIn + 12 + FC_1_out*6 + FC_1_out + 10) beginSMaxEnable = 1'b1;endif (address1 != 8'hfe) beginaddress1 = address1 + 1;endelseaddress1 = 8'hfe;address2 = address2 + 1;end

endendmodule

如图所示:

对设计进行分析,操作如图:

分析后的设计,Vivado自动生成原理图,如图:

对设计进行综合,操作如图:

综合完成,关闭即可:

希望本文对大家有帮助,上文若有不妥之处,欢迎指正

分享决定高度,学习拉开差距

相关文章:

一起学习用Verilog在FPGA上实现CNN----(八)integrationFC设计

1 integrationFC设计 LeNet-5网络结构全连接部分如图所示,该部分有2个全连接层,1个TanH激活层,1个SoftMax激活层: 图片来自附带的技术文档《Hardware Documentation》 integrationFC部分原理图,如图所示,…...

面试题总结

1.js的数据类型 分为基本数据类型和引用数据类型。 基本数据类型 ES5的5种:Null,undefined,Boolean,Number,String, ES6新增:Symbol表示独一无二的值 ES10新增:BigInt 表示任意大的…...

go进阶(1) -深入理解goroutine并发运行机制

并发指的是同时进行多个任务的程序,Web处理请求,读写处理操作,I/O操作都可以充分利用并发增长处理速度,随着网络的普及,并发操作逐渐不可或缺 一、goroutine简述 在Golang中一个goroutines就是一个执行单元ÿ…...

mongodb 操作记录

#启动服务 net start MongoDB #停止服务 net stop MongoDB #进入mongo shell 方式 mongo db #查看当前数据库是那个 #插入一条数据 db.runoob.insert({x:10}) #查找数据 db.runoob.find() 查询所有的数据库 show dbs #连接mongodb mongodb://[username:password]host1[:po…...

JDBC简单的示例

JDBC 编程步骤 加载驱动程序: Class.forName(driverClass) //加载MySql驱动 Class.forName("com.mysql.jdbc.Driver") //加载Oracle驱动 Class.forName("oracle.jdbc.driver.OracleDriver")获得数据库连接: DriverManager.getCon…...

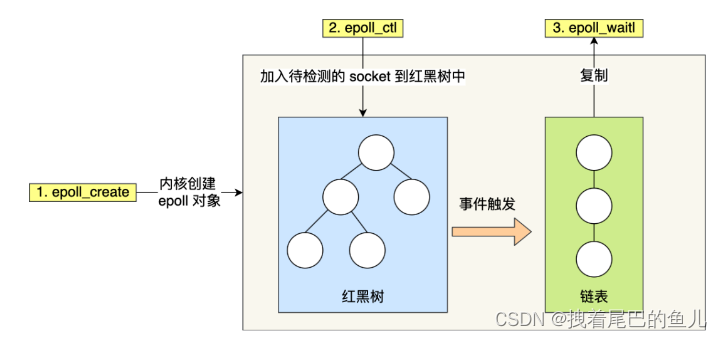

Spring架构篇--2.3 远程通信基础--IO多路复用select,poll,epoll模型

前言:对于传统的BIO(同步阻塞)模型,当有客户端连接达到服务端,服务端在对改连接进行连接建立,和数据传输过程中,是无法响应其他客户端的,只有当服务端完成对一个客户端处理后&#x…...

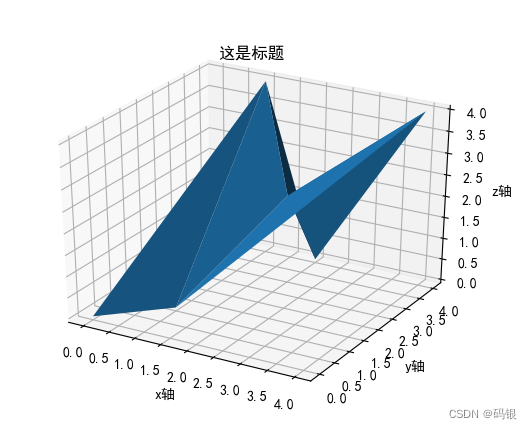

python--matplotlib(4)

前言 Matplotlib画图工具的官网地址是 http://matplotlib.org/ Python环境下实现Matlab制图功能的第三方库,需要numpy库的支持,支持用户方便设计出二维、三维数据的图形显示,制作的图形达到出版级的标准。 其他matplotlib文章 python--matpl…...

)

【项目精选】城市公交查询系统(论文+视频+源码)

点击下载源码 1.1 选题背景 随着低碳生活的普及,人们更倾向于低碳环保的出行方式,完善公交系统无疑具有重要意义。公交是居民日常生活中最常使用的交通工具之一,伴随着我国经济繁荣和城市人口增长,出行工具的选择也变得越来越重要…...

less、sass、webpack(前端工程化)

目录 一、Less 1.配置less环境 1.先要安装node:在cmd中:node -v检查是否安装node 2.安装less :cnpm install -g less 3.检查less是否安装成功:lessc -v 4.安装成功后,在工作区创建xx.less文件 5.在控制台编译less,命令&…...

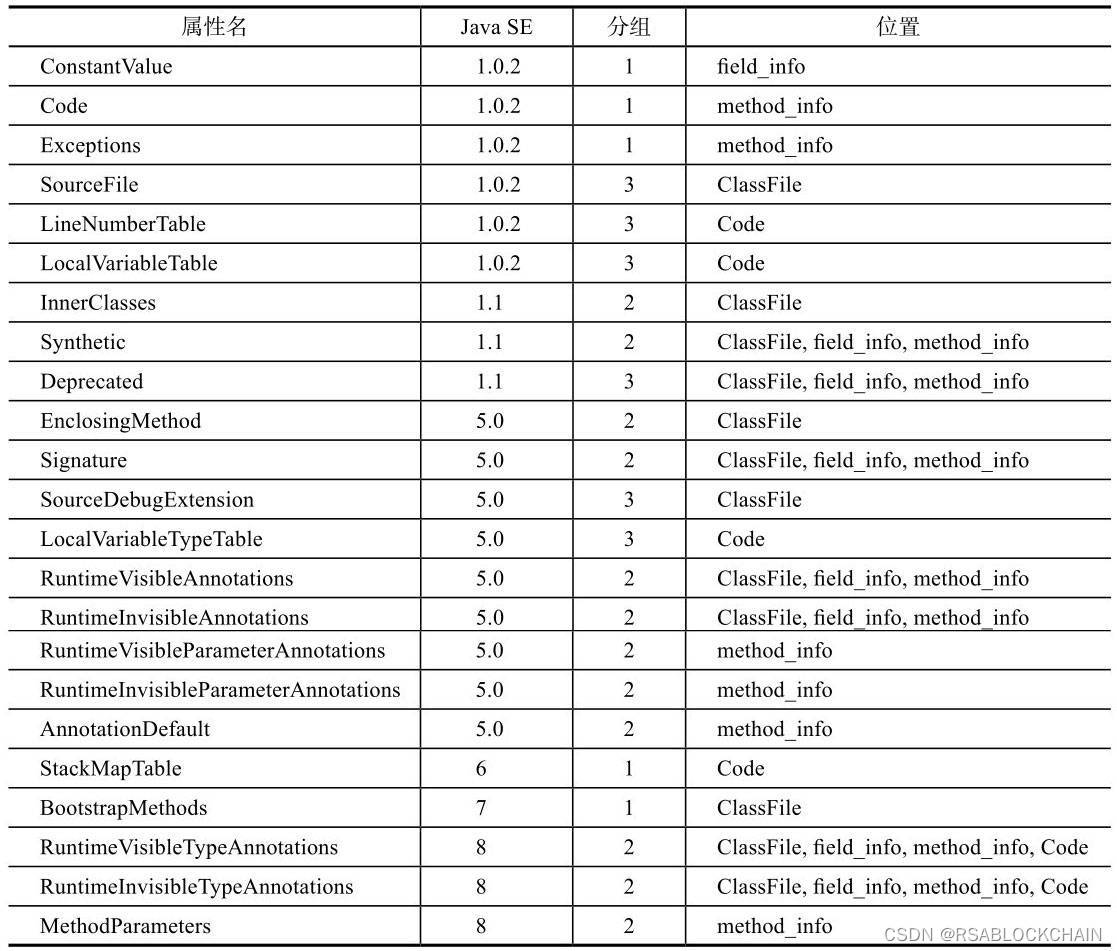

解析Java中的class文件

解析class文件需要把class文件当成文件流来处理,定义ClassReader结构体 type ClassReader struct {data []byte }go语言中的reslice语法可以跳过已经读过的数据。 同时定义了ClassFile数据结构来描述class文件的各个部分,该数据结构如下所示࿱…...

直播预告 | 企业如何轻松完成数据治理?火山引擎 DataLeap 给你一份实战攻略!

更多技术交流、求职机会,欢迎关注字节跳动数据平台微信公众号,回复【1】进入官方交流群 企业数字化转型正席卷全球,这不仅是趋势所在,也是企业发展必然面对的考题,也是企业最关心、最难决策的难题,数字化不…...

)

华为OD机试真题Python实现【 磁盘容量】真题+解题思路+代码(20222023)

磁盘容量 题目 磁盘的容量单位常用的有M、G、T 他们之间的换算关系为1T =1024G,1G=1024M 现在给定n块磁盘的容量,请对他们按从小到大的顺序进行稳定排序 例如给定5块盘的容量 5 1T 20M 3G 10G6T 3M12G9M 排序后的结果为 20M 3G 3M12G9M 1T 10G6T 注意单位可以重复出现 上述…...

php调试配置

错误信息输出 错误日志 nginx把对php的请求发给php-fpm fastcgi进程来处理,默认的php-fpm只会输出php-fpm的错误信息,在php-fpm的errors log里也看不到php的errorlog。原因是php-fpm的配置文件php-fpm.conf中默认是关闭worker进程的错误输出࿰…...

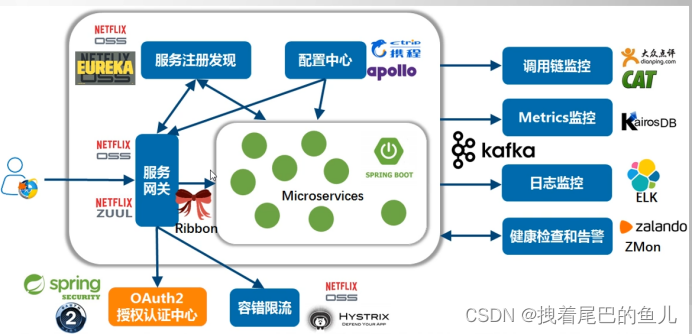

Spring架构篇--1 项目演化过程

前言:如今spring微服务以其灵活开发易于维护已基本占领开发占地,项目从一开始并不是这种服务的拆分,是一步步演变成现在的架构; 项目演化之路: 1 单体架构:开发和运维都较简单: 单体架构&am…...

)

华为OD机试真题Python实现【斗地主 2】真题+解题思路+代码(20222023)

斗地主 2 题目描述 在斗地主扑克牌游戏中,扑克牌由小到大的顺序为3 4 5 6 7 8 9 10 J Q K A 2 玩家可以出的扑克牌阵型有,单张,对子,顺子,飞机,炸弹等 其中顺子的出牌规则为,由至少 5 张由小到大连续递增的扑克牌组成 且不能包含2 例如:{3,4,5,6,7}、{3,4,5,6,7,8,9,1…...

Intel SIMD: AVX2

AVX2 资料: Intel 内部指令 — AVX和AVX2学习笔记Intel Intrinsics — AVX & AVX2 Learning NotesModule x86 AVX 向量寄存器有三种: 128-bit (XMM forms),AVX2 支持,符号 __m128, __m128d, __m128i256-bit (YMM forms)&a…...

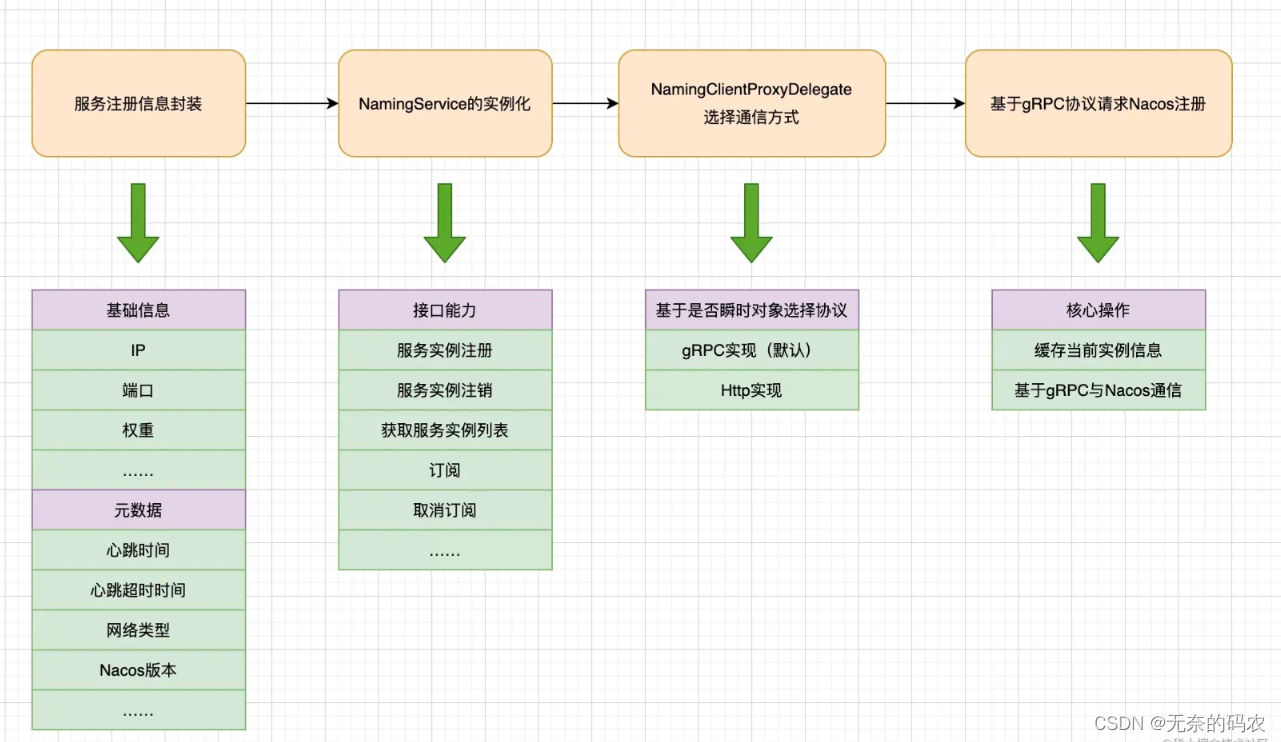

Spring Cloud Nacos源码讲解(二)- Nacos客户端服务注册源码分析

Nacos客户端服务注册源码分析 服务注册信息 我们从Nacos-Client开始说起,那么说到客户端就涉及到服务注册,我们先了解一下Nacos客户端都会将什么信息传递给服务器,我们直接从Nacos Client项目的NamingTest说起 public class NamingTest…...

| 机试题+算法思路+考点+代码解析 【2023】)

华为OD机试 - 停车场最大距离(Python) | 机试题+算法思路+考点+代码解析 【2023】

停车场最大距离 题目 停车场有一横排车位0代表没有停车,1代表有车. 至少停了一辆车在车位上,也至少有一个空位没有停车. 为防止刮蹭,需为停车人找到一个车位 使得停车人的车最近的车辆的距离是最大的 返回此时的最大距离 输入 一个用半角逗号分割的停车标识字符串,停车标识为…...

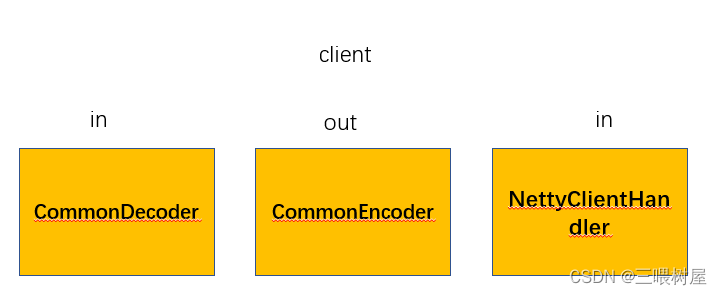

RPC(2)------ Netty(NIO) + 多种序列化协议 + JDK动态代理实现

依赖包解释 Guava 包含了若干被Google的 Java项目广泛依赖 的核心库,例如:集合 [collections] 、缓存 [caching] 、原生类型支持 [primitives support] 、并发库 [concurrency libraries] 、通用注解 [common annotations] 、字符串处理 [string process…...

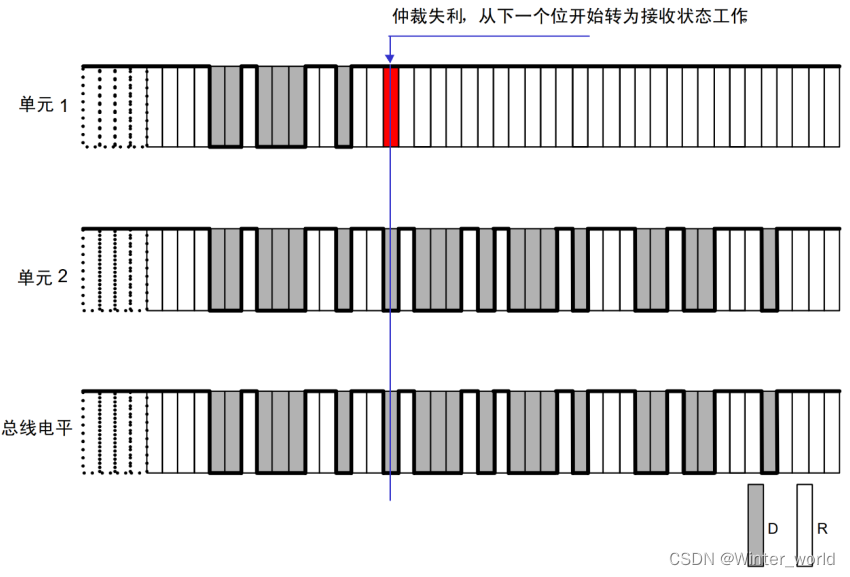

CAN现场总线基础知识总结,看这一篇就理清了(CAN是什么,电气属性,CAN通协议等)

【系列专栏】:博主结合工作实践输出的,解决实际问题的专栏,朋友们看过来! 《QT开发实战》 《嵌入式通用开发实战》 《从0到1学习嵌入式Linux开发》 《Android开发实战》 《实用硬件方案设计》 长期持续带来更多案例与技术文章分享…...

Jellyfin MetaTube插件:5分钟打造专业级媒体库的终极指南

Jellyfin MetaTube插件:5分钟打造专业级媒体库的终极指南 【免费下载链接】jellyfin-plugin-metatube MetaTube Plugin for Jellyfin/Emby 项目地址: https://gitcode.com/gh_mirrors/je/jellyfin-plugin-metatube MetaTube是一款专为Jellyfin和Emby设计的免…...

FLUX.小红书极致真实V2规模化落地:单节点支持10并发请求,QPS达2.1

FLUX.小红书极致真实V2规模化落地:单节点支持10并发请求,QPS达2.1 1. 项目简介 你是否曾经遇到过这样的困扰:想要生成小红书风格的高质量图片,但要么效果不够真实,要么生成速度太慢,要么显存不够用&#…...

Wan2.2-I2V-A14B在微信小程序开发中的应用:实时图片转视频功能实现

Wan2.2-I2V-A14B在微信小程序开发中的应用:实时图片转视频功能实现 1. 引言 "一张照片能变成视频吗?"这是很多社交类小程序用户常有的疑问。想象一下,用户在电商小程序上传商品图片后,系统自动生成一段展示视频&#…...

三相永磁同步电机FOC控制实战:从霍尔传感器配置到SVPWM调参避坑指南

三相永磁同步电机FOC控制实战:从霍尔传感器配置到SVPWM调参避坑指南 当你在深夜的实验室里盯着示波器上跳动的波形,试图让一台三相永磁同步电机平稳启动时,是否经历过这样的场景:明明按照手册配置了所有参数,电机却像喝…...

RSA1 - Writeup by AI

RSA1 - Writeup by AI 1. 题目描述项目内容题目来源Bugku题目类型Crypto (密码学)考点RSA 大数分解、私钥计算题目信息 题目给出了 RSA 加密的三个参数: e 65537 N 1018261336751023520497560395829454421245429586704872293236600679847605951423419167478189648…...

MOOTDX终极指南:Python通达信数据接口让量化分析变得简单高效

MOOTDX终极指南:Python通达信数据接口让量化分析变得简单高效 【免费下载链接】mootdx 通达信数据读取的一个简便使用封装 项目地址: https://gitcode.com/GitHub_Trending/mo/mootdx 你是否曾为获取股票数据而烦恼?面对复杂的API接口和繁琐的数据…...

LoRA训练助手效果展示:动漫风格迁移作品集

LoRA训练助手效果展示:动漫风格迁移作品集 1. 引言 你是否曾经想过,把自己拍摄的普通照片转换成新海诚风格的唯美画面,或者让日常场景拥有吉卜力工作室的梦幻质感?现在,这一切都不再是梦想。通过LoRA训练助手&#x…...

解锁Audacity:5个零成本音频处理功能彻底改变你的创作流程

解锁Audacity:5个零成本音频处理功能彻底改变你的创作流程 【免费下载链接】audacity Audio Editor 项目地址: https://gitcode.com/GitHub_Trending/au/audacity 价值定位:为什么Audacity是音频创作者的必备工具 在音频编辑领域,专…...

实时口罩检测-通用部署教程:Windows WSL2环境下ModelScope模型本地加载

实时口罩检测-通用部署教程:Windows WSL2环境下ModelScope模型本地加载 1. 环境准备与WSL2配置 1.1 WSL2安装与设置 如果你使用的是Windows系统,首先需要安装WSL2(Windows Subsystem for Linux 2)。这是微软提供的Linux兼容层&…...

ColorControl专业调校指南:从问题诊断到显示优化的参数配置全流程

ColorControl专业调校指南:从问题诊断到显示优化的参数配置全流程 【免费下载链接】ColorControl Easily change NVIDIA display settings and/or control LG TVs 项目地址: https://gitcode.com/gh_mirrors/co/ColorControl 一、问题诊断:你的显…...