Verilog零基础入门(边看边练与测试仿真)-时序逻辑-笔记(4-6讲)

文章目录

- 第四讲

- 第五讲

- 第六讲

第四讲

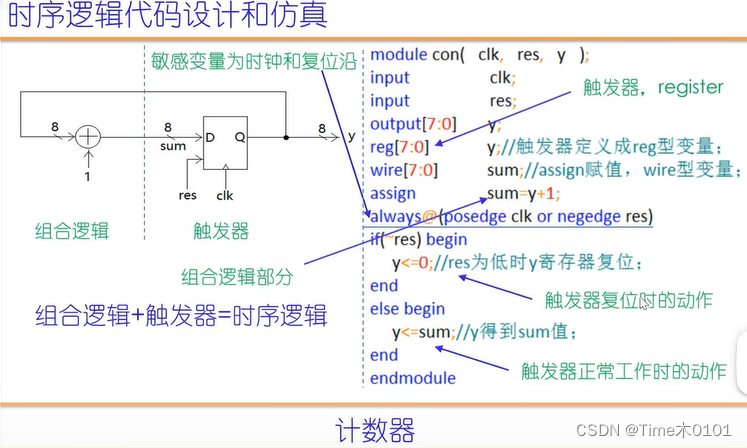

1、计数器

代码:

//计数器

`timescale 1ns/10ps

module counter(clk,res,y);

input clk;

input res;

output[7:0] y;reg[7:0] y;

wire[7:0] sum;//+1运算的结果(1)

assign sum=y+1;//组合逻辑部分(2)always@(posedge clk or negedge res)

if(~res) beginy<=0;

end

else beginy<=sum; //可省略上面(1)(2)语句,y<=y+1;

end

endmodule//--------testbench of counter------

module counter_tb;

reg clk,res;

wire[7:0] y;counter counter(.clk(clk),.res(res),.y(y));initial beginclk<=0;res<=0;#17 res<=1;#6000 $stop;

endalways #5 clk<=~clk;endmodule

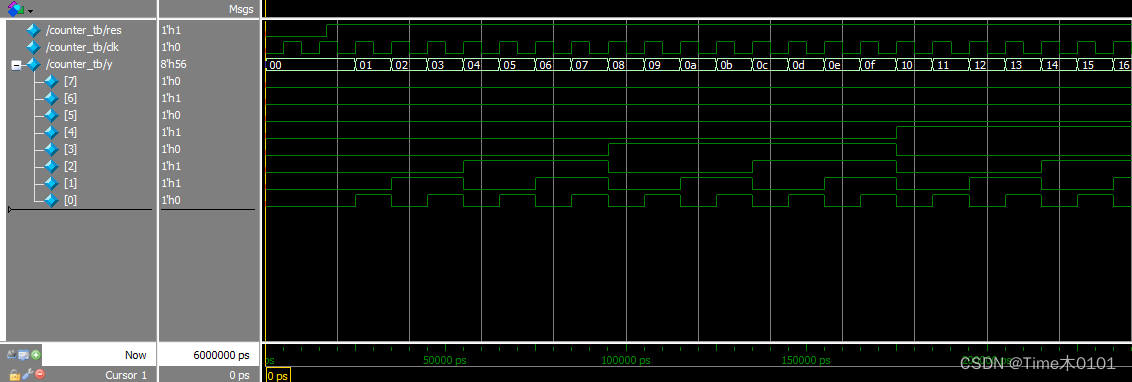

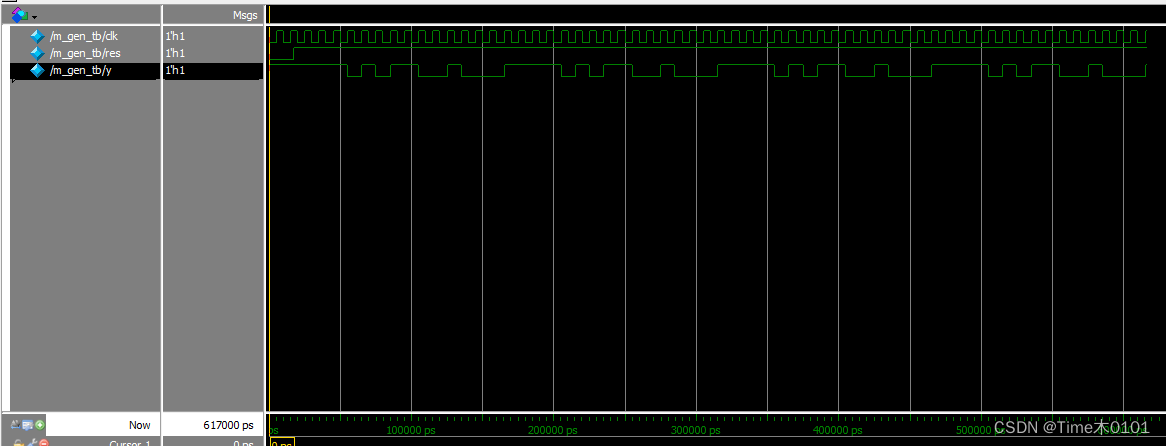

仿真结果:

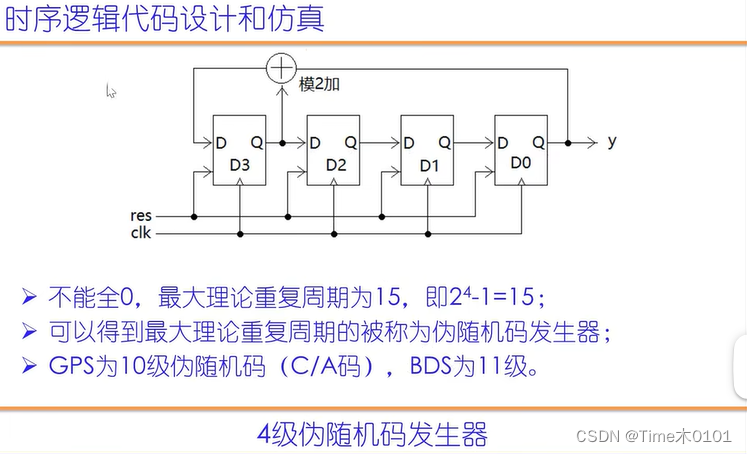

2、4级伪随机码发生器

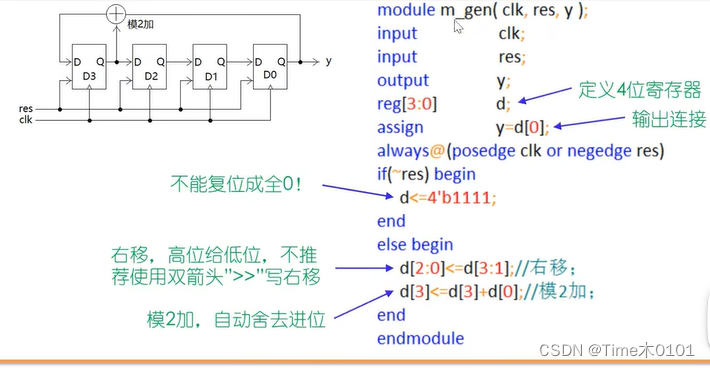

代码:

//四级伪随机码发生器

`timescale 1ns/10ps

module m_gen(clk,res,y);

input clk;

input res;

output y;reg[3:0] d;

assign y=d[0];always@(posedge clk or negedge res)

if(~res)begind<=4'b1111;

end

else begind[2:0]<=d[3:1]; //右移一位d[3]<=d[3]+d[0]; //模二加

endendmodule//-------testbench of m_gen-------

module m_gen_tb;

reg clk,res;

wire y;

m_gen m_gen(.clk(clk),.res(res),.y(y));initial beginclk=0;res=0;#17 res=1;#600 $stop;

end

always #5 clk=~clk;endmodule

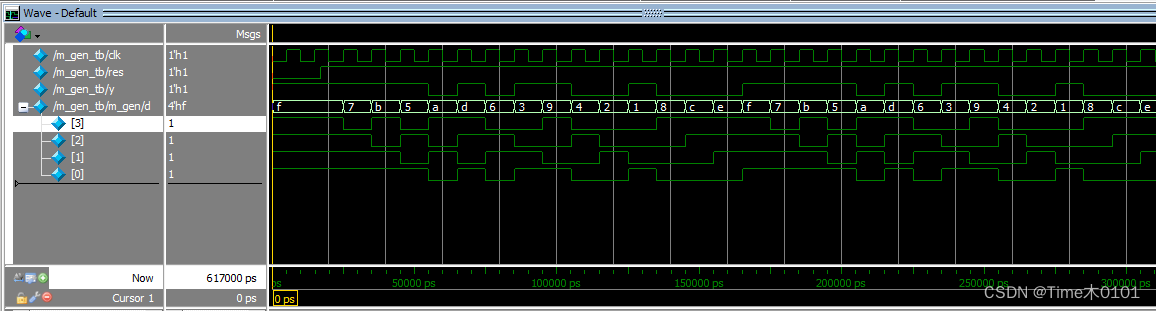

仿真波形图:

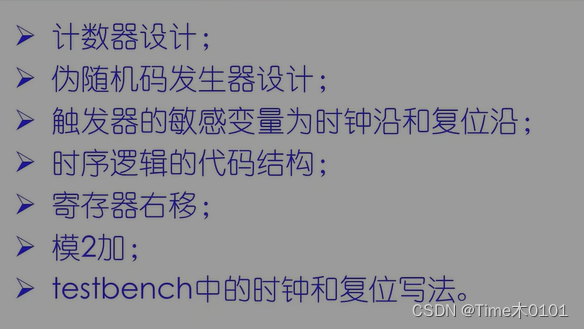

小结:

第五讲

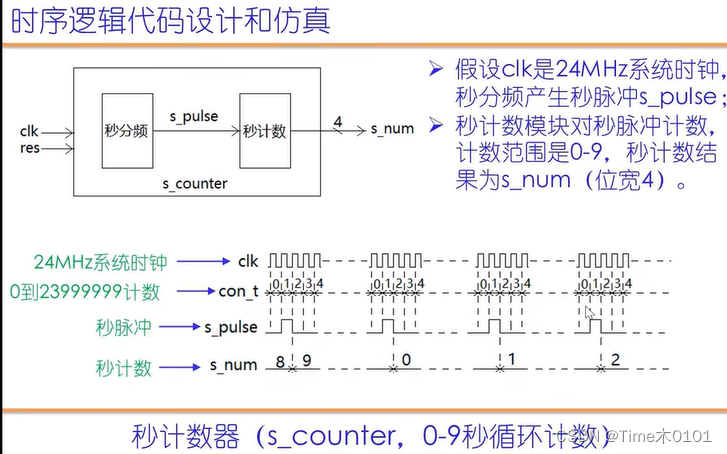

1、秒计数器(s_counter, 0-9秒循环计数)

代码:

//2023-09-07,time

//秒计数器,0-9循环;

`timescale 1ns/10ps

module s_counter(clk,res,s_num);

input clk;

input res;

output[3:0] s_num;parameter frequency_clk=24;//24MHzreg[24:0] con_t; //秒脉冲分频计数器;

reg s_pulse; //秒脉冲尖;

reg[3:0] s_num;

always@(posedge clk or negedge res)

if(~res)begincon_t<=0;s_pulse<=0;s_num<=0;end

else begin//if( con_t==frequency_clk*1000000-1)beginif( con_t==frequency_clk*1000-1)begin//为了仿真方便观察,数值改小了con_t<=0;endelse begincon_t<= con_t+1;endif( con_t==0)begins_pulse<=1;endelse begins_pulse<=0;endif(s_pulse)beginif(s_num==9)begins_num<=0;endelse begins_num<=s_num+1;endend

end

endmodule//-------testbench of s_counter------

module s_counter_tb;

reg clk,res;

wire[3:0] s_num;

s_counter s_counter(.clk(clk),.res(res),.s_num(s_num));initial beginclk<=0;res<=0;#17 res<=1;#300000 $stop;

endalways#5 clk=~clk;endmodule

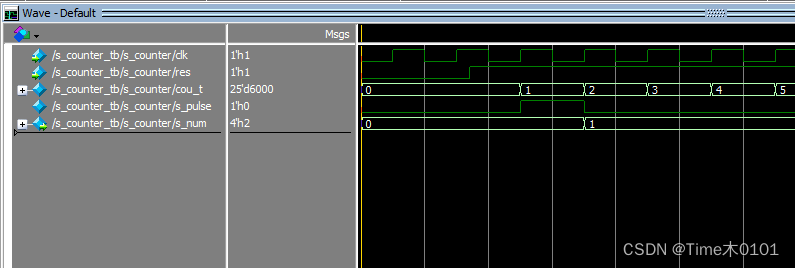

仿真图:

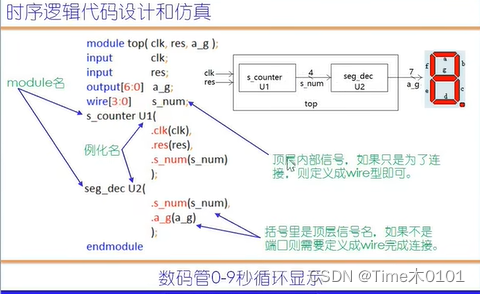

2、秒计数器加数码管显示

2、秒计数器加数码管显示

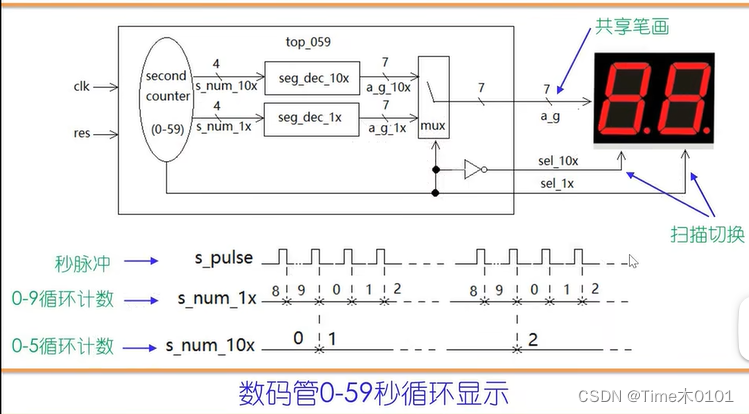

3、0-59秒显示

小结:

第六讲

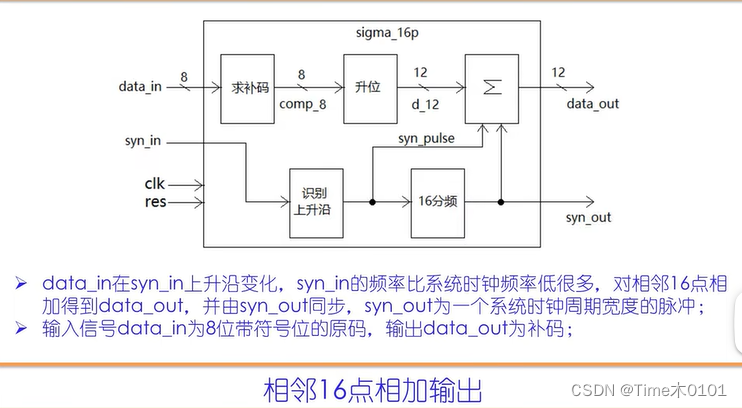

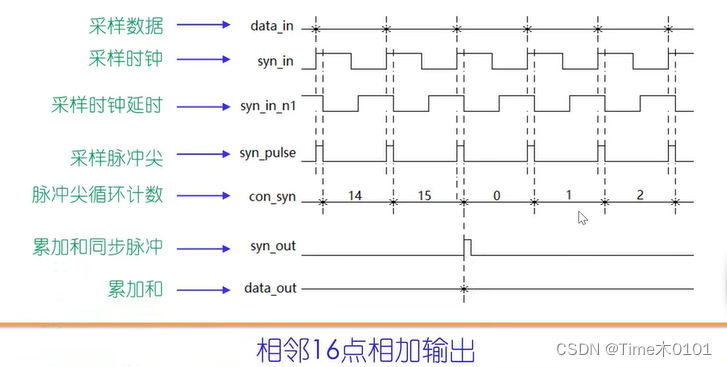

1、相邻点累加

构想:

代码:

//2023-09-11,time

//相邻16点相加;

`timescale 1ns/10ps

module sigma_16p(clk,res,data_in,syn_in,data_out,syn_out);

input clk;

input res;

input[7:0] data_in;//采样信号

input syn_in;//采样时钟

output[11:0] data_out;//累加结果输出

output syn_out;//累加结果同步脉冲reg syn_in_n1;//syn_in的反向延时;

wire syn_pulse;//采样时钟上升沿识别脉冲;

assign syn_pulse=syn_in&syn_in_n1;

reg[3:0] con_syn;//采样时钟循环计数器wire[7:0] comp_8;//补码

wire[11:0] d_12;//升位结果

assign comp_8=data_in[7]?{data_in[7],~data_in[6:0]+1}:data_in;//补码运算;

assign d_12={comp_8[7],comp_8[7],comp_8[7],comp_8[7],comp_8};

reg[11:0] sigma;//累加计算;

reg[11:0] data_out;

reg syn_out;always@(posedge clk or negedge res)

if(~res)beginsyn_in_n1<=0;con_syn<=0;sigma<=0;data_out<=0;syn_out<=0;

end

else beginsyn_in_n1<=~syn_in;if(syn_pulse)begincon_syn<=con_syn+1;endif(syn_pulse)beginif(con_syn==15)beginsigma<=d_12;data_out<=sigma;syn_out<=1;endelse beginsigma<=sigma+d_12;endendelse beginsyn_out<=0;end

endendmodule//---------testbench of sigma_16p_tb-------

module sigma_16p_tb;

reg clk,res;

reg[7:0] data_in;

reg syn_in;

wire[11:0] data_out;

wire syn_out;

sigma_16p sigma_16p(.clk(clk),.res(res),.data_in(data_in),.syn_in(syn_in),.data_out(data_out),.syn_out(syn_out));initial beginclk<=0;res<=0;data_in=1;syn_in<=0;#17 res<=1;#25000 $stop;

endalways #5 clk<=~clk;always #100 syn_in<=~syn_in;endmodule

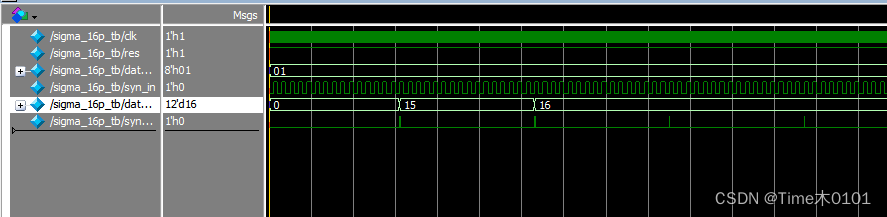

仿真结果:

data_in=1:

data_in=8’b1000_0001 //data_in=-1

小结:

相关文章:

Verilog零基础入门(边看边练与测试仿真)-时序逻辑-笔记(4-6讲)

文章目录 第四讲第五讲第六讲 第四讲 1、计数器 代码: //计数器 timescale 1ns/10ps module counter(clk,res,y); input clk; input res; output[7:0] y;reg[7:0] y; wire[7:0] sum;//1运算的结果(1࿰…...

2023-09-12力扣每日一题

链接: 1462. 课程表 IV 题意 一个pair<int,int>表示a是b的前置 进行n次查询,查询q是否是p的前置(可以不是直接前置) 解: 就是要把01、12、13这种能转换出02、03,弗洛伊德即可 无环无负权 实际…...

)

leetcode面试题:交换和(三种方法实现)

交换和: 给定两个整数数组,请交换一对数值(每个数组中取一个数值),使得两个数组所有元素的和相等。 返回一个数组,第一个元素是第一个数组中要交换的元素,第二个元素是第二个数组中要交换的元…...

前端可视化界面开发技术:实战与优化

引言 在当今的互联网时代,数据可视化已经成为信息展示和交互的重要方式。特别是在前端开发领域,可视化界面的应用越来越广泛,涉及到数据监控、分析和决策等多种场景。本文将深入探讨前端可视化界面开发的关键技术,通过实例解析提…...

Python实现机器学习(下)— 数据预处理、模型训练和模型评估

前言:Hello大家好,我是小哥谈。本门课程将介绍人工智能相关概念,重点讲解机器学习原理机器基本算法(监督学习及非监督学习)。使用python,结合sklearn、Pycharm进行编程,介绍iris(鸢尾…...

树结构处理,list和tree互转

1、实体类 package com.iot.common.test.entity;import lombok.Data;import java.util.List;/*** description:* author:zilong* date:2023/9/8*/ Data public class Node {//idprivate String id;//父节点idprivate String pId;//名称private String name;//编码private Stri…...

可视化大屏设计模板 | 主题皮肤(报表UI设计)

下载使用可视化大屏设计模板,减少重复性操作,提高报表制作效率的同时也确保了报表风格一致,凸显关键数据信息。 软件:奥威BI系统,又称奥威BI数据可视化工具 所属功能板块:主题皮肤上传下载(数…...

Spring Boot + Vue的网上商城之客服系统实现

Spring Boot Vue的网上商城之客服系统实现 在网上商城中,客服系统是非常重要的一部分,它能够为用户提供及时的咨询和解答问题的服务。本文将介绍如何使用Spring Boot和Vue.js构建一个简单的网上商城客服系统。 思路 在本教程中,我们学习了…...

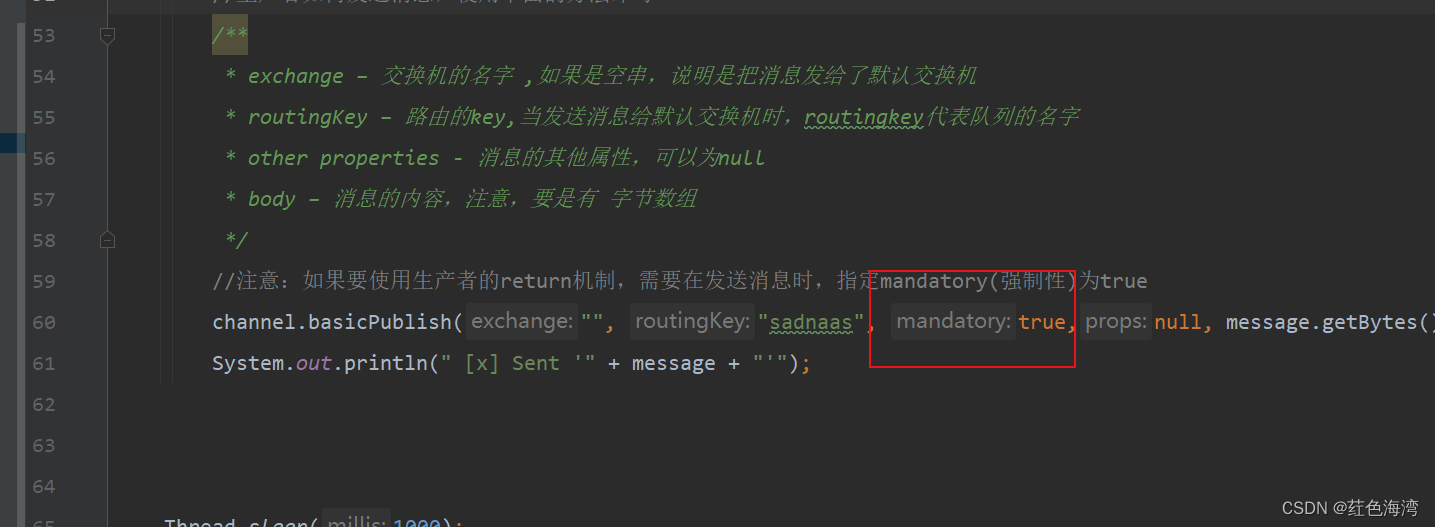

RabbitMQ: return机制

1. Return机制 Confirm只能保证消息到达exchange,无法保证消息可以被exchange分发到指定queue。 而且exchange是不能持久化消息的,queue是可以持久化消息。 采用Return机制来监听消息是否从exchange送到了指定的queue中 2.Java的实现方式 1.导入依赖 &l…...

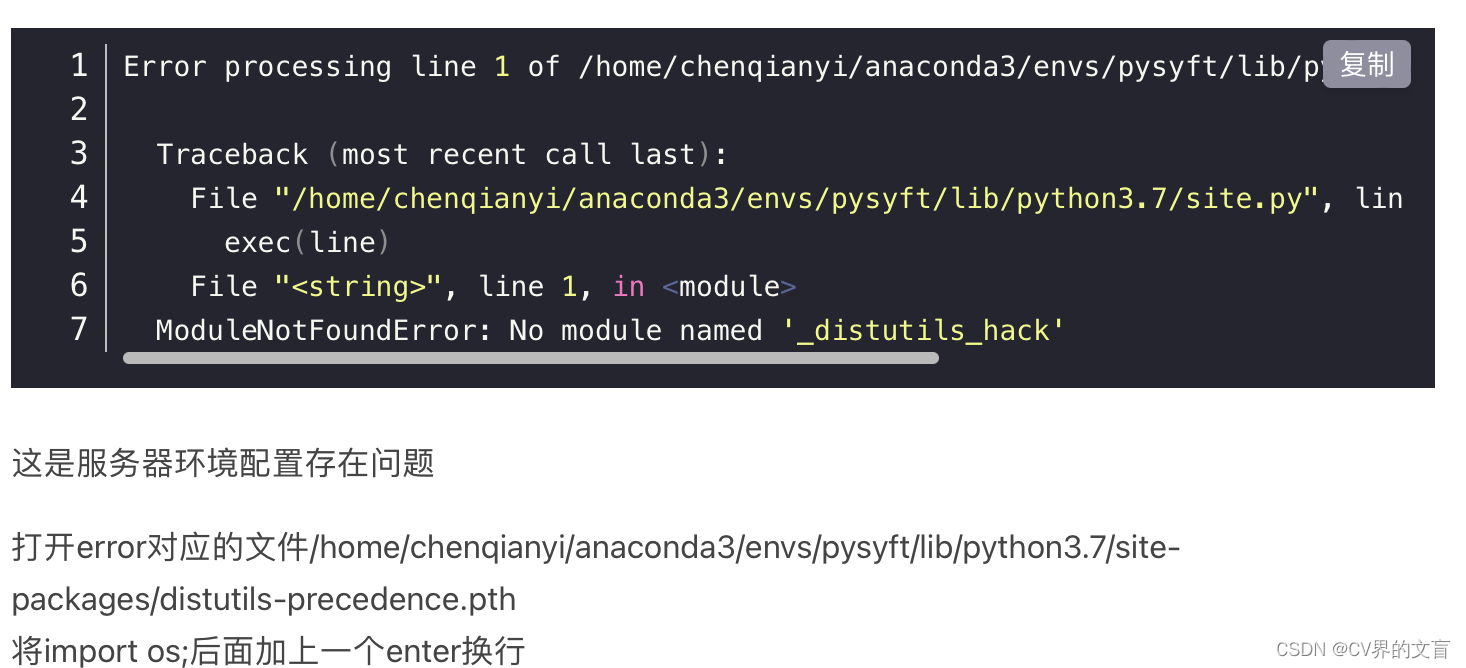

记录一些奇怪的报错

错误:AttributeError: module distutils has no attribute version 解决方案: 第一步:pip uninstall setuptools 第二步:conda install setuptools58.0.4 错误:ModuleNotFoundError: No module named _distutils_hac…...

Ubuntu 安装redis数据库,并设置开机自启动

1、下载安装包 wget http://download.redis.io/releases/redis-7.0.9.tar.gz 2、解压 tar -zxvf redis-7.0.9.tar.gz 3、复制到解压缩的包移动到/usr/local/ sudo mv ./redis-7.0.9 /usr/local/ 4、编译 cd /usr/local/redis-7.0.9 sudo make 5、测试: 时间会比较长࿰…...

:人脸跟踪)

基于开源模型搭建实时人脸识别系统(五):人脸跟踪

继续填坑,之前已经讲了人脸检测,人脸识别实战之基于开源模型搭建实时人脸识别系统(二):人脸检测概览与模型选型_开源人脸识别模型_CodingInCV的博客-CSDN博客,人脸检测是定位出画面中人脸的位置,…...

VUE | 配置环境变量

本篇目录 1. 创建开发环境配置文件2. 创建正式环境配置文件3. 在代码中访问环境变量4. 加载环境变量 在 Vue 项目中是使用 .env 文件来定义和使用不同的环境变量,这些文件在 Vue 项目根目录下创建。推荐有几种环境就创建几个 .env 文件,下面就开发环境和…...

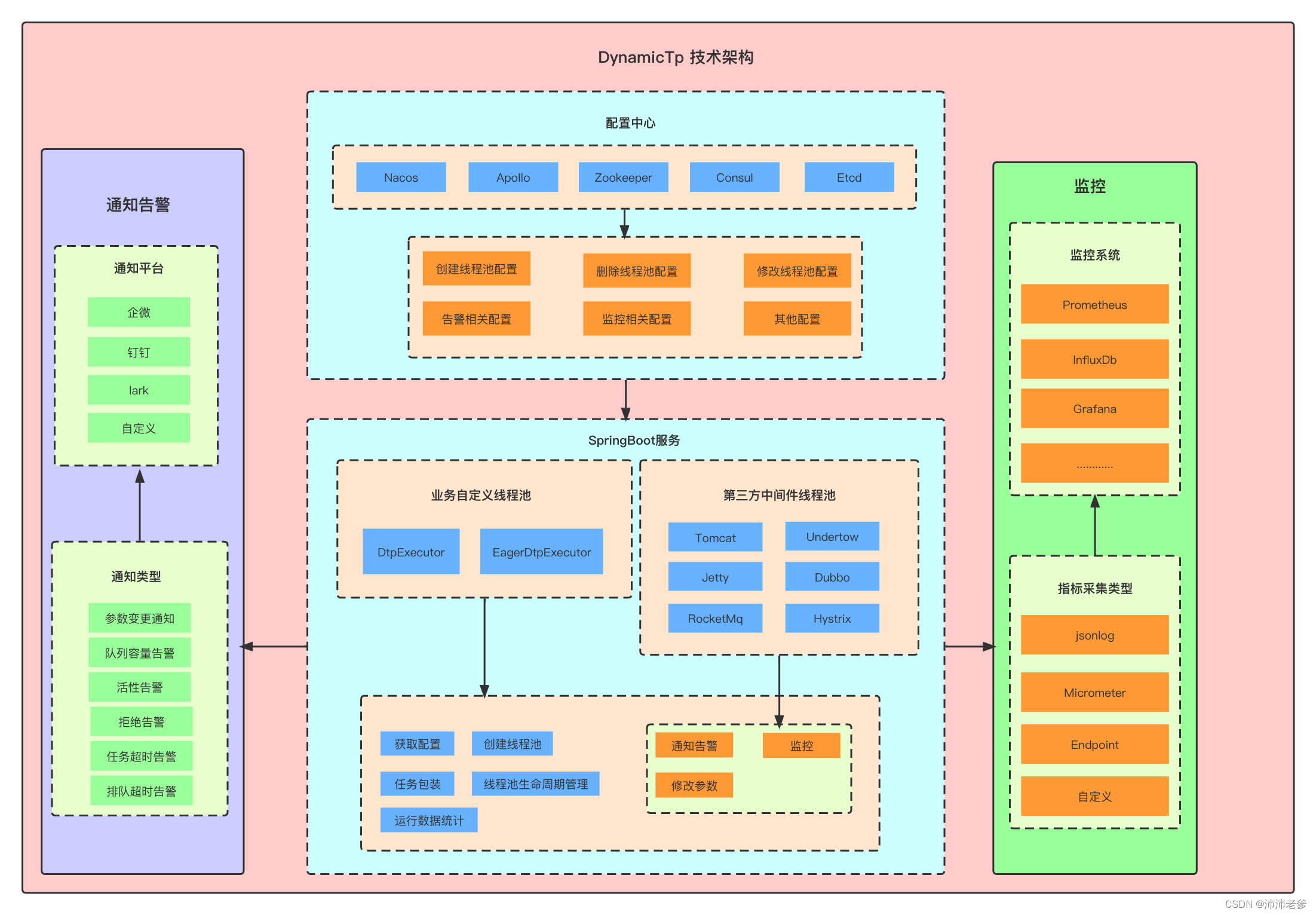

Dynamic-TP入门初探

背景 在使用线程池的过程中,会出现一些痛点: 代码中创建了一个线程池,但是不知道那几个核心参数设置多少比较合适。凭经验设置参数值,上线后发现需要调整,改代码重新发布服务,非常麻烦。线程池相对开发人…...

Git的基本操作:远程操作

7 Git的远程操作 远程操作主要是指,在不同的仓库之间进行提交和代码更改。是一个明显的对等的分布式系统。其中本地个仓库与远程仓库,不同的远程仓库之间都可以建立这种关系。这种关系之间的操作主要有pull和push。 远程仓库 创建SSH key远程仓库和本…...

【IOC,AOP】spring的基础概念

IOC 控制反转 对象的创建控制权转交给外部实体,就是控制反转。外部实体便是IOC容器。其实就是以前创建java对象都是我们new一下,现在我们可以把这个new交给IOC容器来做,new出来的对象也会交由IOC容器来管理。这个new出来的对象则称为Bean。 …...

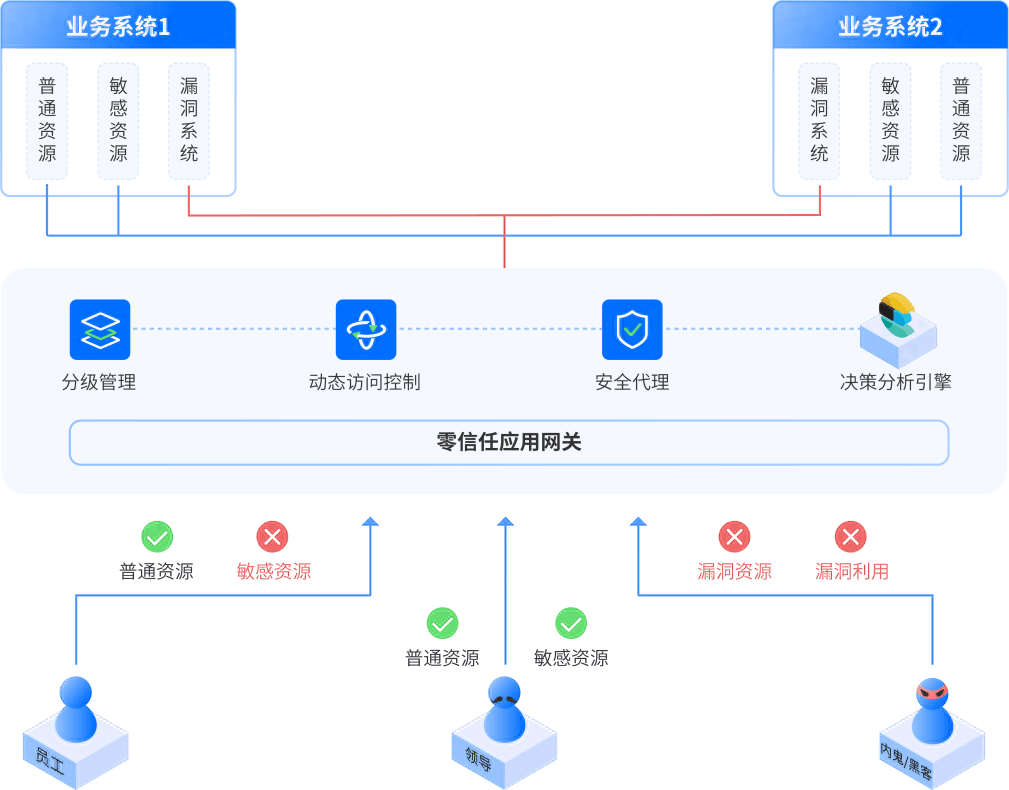

安全实战 | 怎么用零信任防范弱密码?

防范弱密码,不仅需要提升安全性,更需要提升用户体验。 比如在登录各类业务系统时,我们希望员工登录不同系统不再频繁切换账号密码,不再需要3-5个月更换一次密码,也不再需要频繁的输入、记录、找回密码。 员工所有的办…...

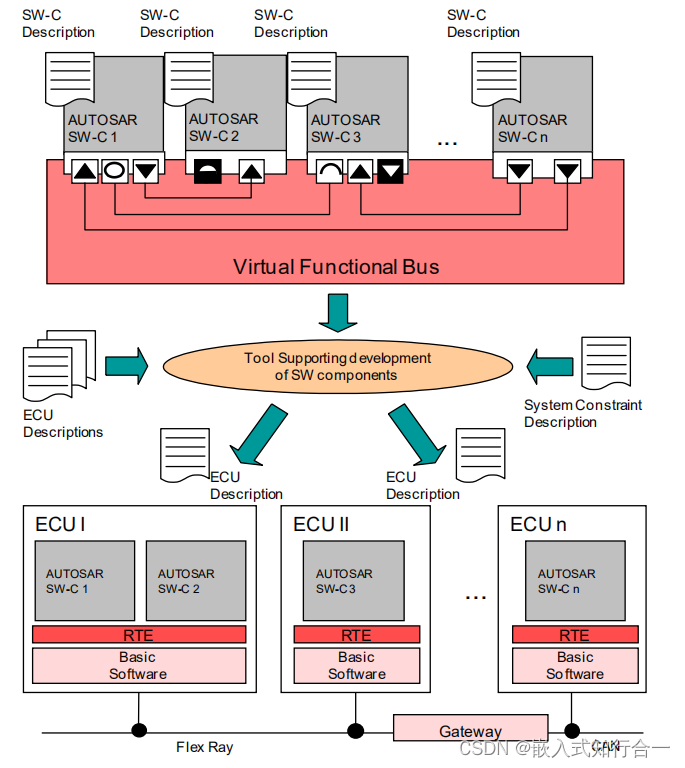

1-4 AUTOSAR方法论

总目录——AUTOSAR入门详解AUTOSAR入门详解目录汇总:待续中。。。https://xianfan.blog.csdn.net/article/details/132818463 目录 一、前言 二、方法论 三、单个ECU开发流程 一、前言 汽车生产供应链上有以下角色:OEM、TIER1、TIER2,其主…...

MFC C++ 数据结构及相互转化 CString char * char[] byte PCSTR DWORE unsigned

CString: char * char [] BYTE BYTE [] unsigned char DWORD CHAR:单字节字符8bit WCHAR为Unicode字符:typedef unsigned short wchar_t TCHAR : 如果当前编译方式为ANSI(默认)方式,TCHAR等价于CHAR,如果为Unicode方式,…...

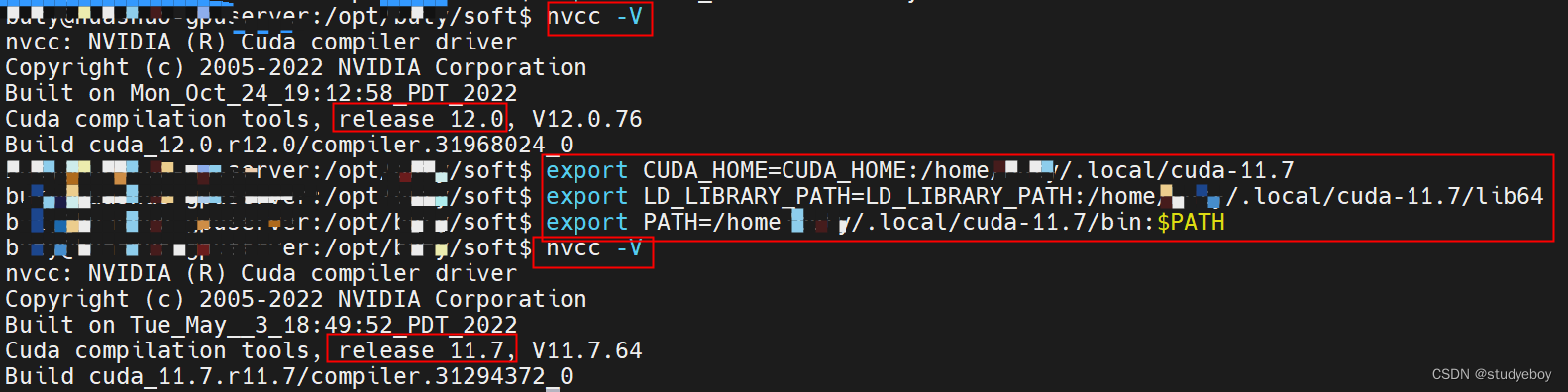

多版本CUDA安装切换

系统中默认的安装CUDA为12.0,现在需要在个人用户下安装CUDA11.7。 CUDA 下载 CUDA官网下载 安装 Log file not open.Segmentation fault (core dumped)错误 将/tmp/cuda-installer.log删除即可。重新安装,去掉驱动的安装,设置Toolkit的安装…...

一图定胜负|虎贲等考 AI 科研绘图:零代码画出期刊级学术图,让论文颜值与专业度双在线

据 Nature 统计,超 90% 的审稿人先看图表,65% 的初审意见直接来自图表质量,一张规范、清晰、专业的学术图,直接影响论文录用与答辩评分。可现实是:Origin、Visio 难学难精通,PPT 做图粗糙不规范,…...

Atlas机器人:人形设计、液压驱动与救灾场景下的技术权衡

1. 项目概述:Atlas,一个充满争议的工程里程碑2013年,当波士顿动力公司为DARPA(美国国防高级研究计划局)打造的Atlas机器人首次公开亮相时,它在工程技术社区引发的震动,远不止于其令人惊叹的行走…...

2026年搜索引擎大变革:生成式优化服务如何引领未来趋势

随着AI技术的不断进步,搜索引擎领域正在经历一场前所未有的变革。2026年,我们见证了从传统SEO到生成式引擎优化(GEO)的重大转变。这场变革不仅改变了用户获取信息的方式,也为企业带来了全新的营销机遇。本文将深入探讨…...

如何轻松解锁QQ音乐加密文件:qmcdump实战指南

如何轻松解锁QQ音乐加密文件:qmcdump实战指南 【免费下载链接】qmcdump 一个简单的QQ音乐解码(qmcflac/qmc0/qmc3 转 flac/mp3),仅为个人学习参考用。 项目地址: https://gitcode.com/gh_mirrors/qm/qmcdump 你是否曾经下载…...

龙为权,凰为心:凰标守住文化最柔软的底线@凤凰标志

龙为权凰为心 中国文艺生态的双轨平衡宣言秩序权力与创作初心,一刚一柔, 如日月轮值,缺一不可。 龙标掌「权」,凰标守「心」, 双轨并行,方可让文化既筋骨强健,又血肉温润。一、龙标:…...

Unitree Go2 ROS2 SDK架构设计指南:实现企业级机器人性能优化的5大策略

Unitree Go2 ROS2 SDK架构设计指南:实现企业级机器人性能优化的5大策略 【免费下载链接】go2_ros2_sdk Unofficial ROS2 SDK support for Unitree GO2 AIR/PRO/EDU 项目地址: https://gitcode.com/gh_mirrors/go/go2_ros2_sdk Unitree Go2 ROS2 SDK是一个为宇…...

从平面到立体:基于OpenLayers与Cesium的无缝地图维度切换实践

1. 二维与三维地图融合的必要性 在现代WebGIS开发中,单纯依赖二维地图已经难以满足用户对空间数据展示的需求。想象一下,当你查看一个城市规划系统时,平面地图能告诉你道路走向,但只有切换到三维视图才能直观看到建筑高度、地形起…...

RapidIO多播技术原理与应用实践

1. RapidIO多播技术概述 在分布式计算和高速互连系统中,多播(Multicast)技术扮演着至关重要的角色。简单来说,多播就像是在会议室里用广播系统发布通知——只需说一次,所有打开扬声器的房间都能同时听到。RapidIO作为高…...

3分钟掌握SRWE:打破屏幕分辨率限制的终极窗口编辑神器

3分钟掌握SRWE:打破屏幕分辨率限制的终极窗口编辑神器 【免费下载链接】SRWE Simple Runtime Window Editor 项目地址: https://gitcode.com/gh_mirrors/sr/SRWE SRWE(Simple Runtime Window Editor)是一款革命性的实时窗口编辑器&…...

如何零成本测试ZPL标签?Virtual ZPL Printer终极解决方案揭秘

如何零成本测试ZPL标签?Virtual ZPL Printer终极解决方案揭秘 【免费下载链接】Virtual-ZPL-Printer An ethernet based virtual Zebra Label Printer that can be used to test applications that produce bar code labels. 项目地址: https://gitcode.com/gh_mi…...