FPGA设计时序约束二、输入延时与输出延时

目录

一、背景

二、set_input_delay

2.1 set_input_delay含义

2.2 set_input_delay参数说明

2.3 使用样例

三、set_output_delay

3.1 set_output_delay含义

3.2 set_output_delay参数说明

3.3 使用样例

四、样例工程

4.1 工程代码

4.2 时序报告

五、参考资料

一、背景

为了在设计中准确的模拟信号从FPGA传输到外部或外部信号进入到FPGA端口的时序,在设计中需要给定输入端口和输出端口的延时信息,因为vivado仅仅能够识别边界内部的时序。

二、set_input_delay

FPGA端口和外部的时延约束命令有两种,输入时延命令set_input_delay和输出时延命令set_output_delay。

2.1 set_input_delay含义

输入时延约束指定了设计中输入时钟端口的输入时延,以应用板为例,输入时延表示在数据从外部芯片通过应用板到达FPGA的输入引脚和应用板的时钟相位存在差异。因此,输入时延值可以是正数也可以是复数,正负值取决于数据信号和时钟信号在外部芯片与FPGA接口处的相对相位。

注:在Ultrascale系列的器件中,输入时延也可以设置到内部的数据引脚上。

2.2 set_input_delay参数说明

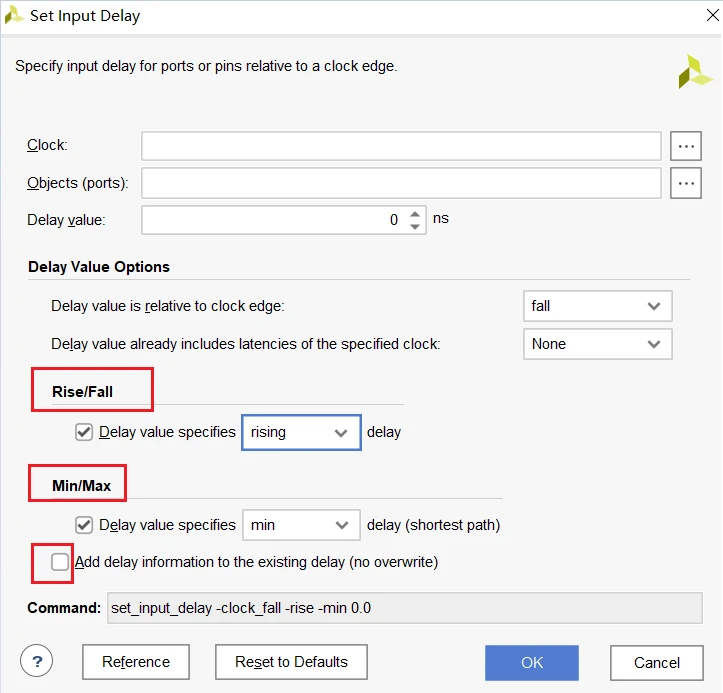

打开vivado中set input delay的设置窗口,有三种可选项:Rise/Fall,Min/Max,Add delay。

Clock:指定约束引脚的同步时钟,必须是事先定义的主时钟或虚拟时钟。

Objects:用于指定约束的目标端口。

Delay value:指定约束的时延值。

Delay value is relative to clock edge:指定输入时延值是相对于同步时钟的边沿,可以是上升沿rise或下降沿fall,默认值为上升沿

Delay value already includes latencies of the specified clock:设置延时值是否包含指定时钟(包括源时钟,网络时钟,源时钟/网络时钟)的潜在因素

Rise/Fall:指定约束信号相对时钟约束的延时边沿,可为上升沿rise或下降沿fall

Min/Max:Min为最小时延值,作用于hold/removal,Max为最大时延值,作用于setup/removal,如果Min/Max都未选择,表示最大时延和最小时延值相等

Add delay information to the existing delay:用于输入端口关联超过一个时钟沿的场景,例如,DDR接口。

2.3 使用样例

a) 设定一个输入延时,相对于时钟sysclk,最大时延和最小时延相等

create_clock -name sysclk -period 10 [get_ports CLK0]

set_input_delay -clock sysclk 2 [get_ports DIN]b)设定一个输入延时,同步时钟为虚拟时钟

create_clock -name clk_port_virt -period 10 #create_clock不指定object时创建的为虚拟时钟

set_input_delay -clock clk_port_virt 2 [get_ports DIN]c)设定一个输入延时,同步时钟为sysclk,最大时延值和最小时延值不同

create_clock -name sysclk -period 10 [get_ports CLK0]

set_input_delay -clock sysclk -max 4 [get_ports DIN]

set_input_delay -clock sysclk -min 1 [get_ports DIN]d)在两个IO端口间是纯组合逻辑,输入端口为DIN,同步时钟为虚拟时钟

create_clock -name sysClk -period 10

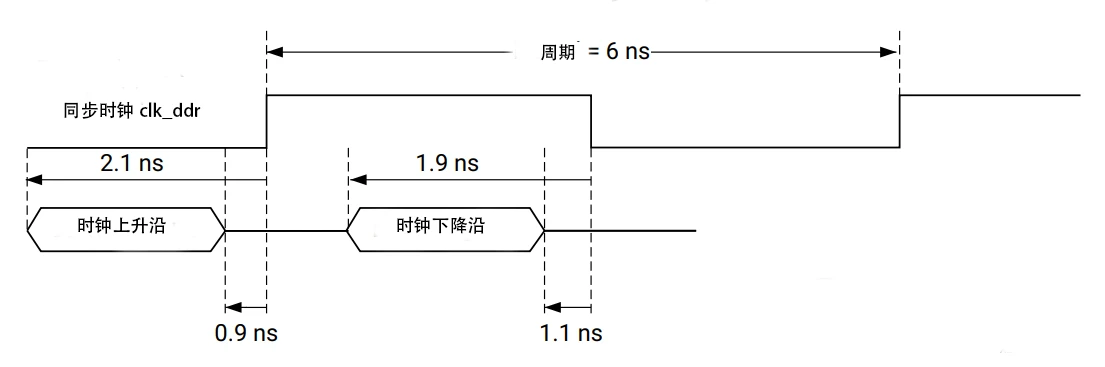

> set_input_delay -clock sysClk 4 [get_ports DIN]e)输入时延设置到DDR的数据输入引脚DDR_IN ,数据被clk_ddr的上升沿和下降沿触发,到FPGA内部FF的数据输入端口,对上升沿和下降沿都敏感

create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_IN]

set_input_delay -clock clk_ddr -max 2.1 [get_ports DDR_IN]

set_input_delay -clock clk_ddr -max 1.9 [get_ports DDR_IN] -clock_fall -

add_delay

set_input_delay -clock clk_ddr -min 0.9 [get_ports DDR_IN]

set_input_delay -clock clk_ddr -min 1.1 [get_ports DDR_IN] -clock_fall -

add_delayf)设置输入时延到startupe3的内部引脚,时延路径从startupe3到组合逻辑单元(针对Ultrascale器件)

create_generated_clock -name clk_sck -source [get_pins -

hierarchical*axi_quad_spi_0/ext_spi_clk] [get_pins STARTUP/CCLK] -edges {3

5 7}

set_input_delay -clock clk_sck -max 7 [get_pins STARTUP/DATA_IN[*]] -

clock_fall

set_input_delay -clock clk_sck -min 1 [get_pins STARTUP/DATA_IN[*]] -

clock_fall三、set_output_delay

3.1 set_output_delay含义

set_output_delay约束指定了关联时钟沿的输出端口的输出路径时延,输出时延可理解为在数据从FPGA的输出端口到达其他芯片和关联的参考时钟间的相位差。输出时延值可以是正数也可以是复数,正负值取决于数据信号和时钟信号在外部芯片与FPGA接口处的相对相位。

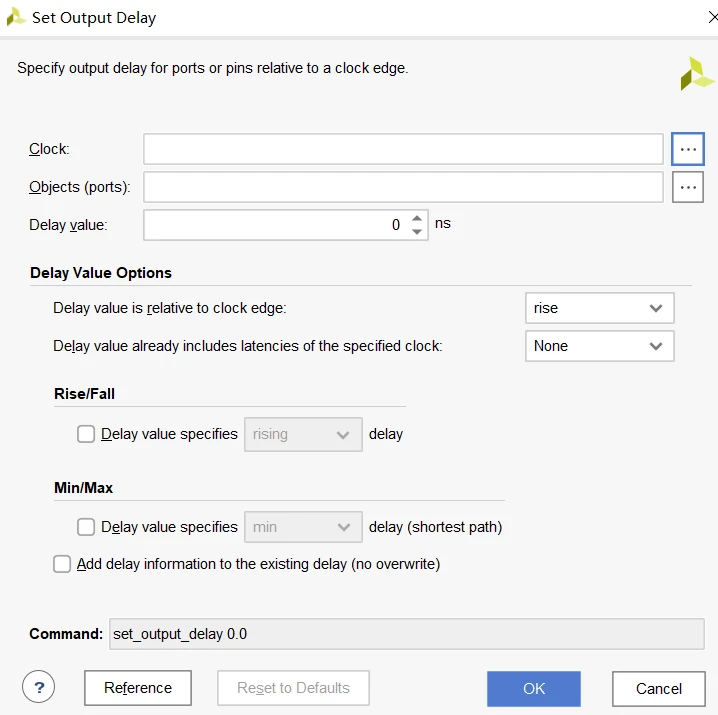

3.2 set_output_delay参数说明

打开set_output_delay窗口,与set_input_delay窗口类似,相关配置项的作用也相同。

3.3 使用样例

a) 设定一个输出时延,同步时钟为sysClk,最大时延和最小时延值相同

create_clock -name sysClk -period 10 [get_ports CLK0]

set_output_delay -clock sysClk 6 [get_ports DOUT]b) 设定输出时延,同步时钟为虚拟时钟

create_clock -name clk_port_virt -period 10 #创建虚拟时钟

set_output_delay -clock clk_port_virt 6 [get_ports DOUT]c)设置输出时延,同步时钟为DDR时钟,最大时延和最小时延值有多个

create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_IN]

set_output_delay -clock clk_ddr -max 2.1 [get_ports DDR_OUT]

set_output_delay -clock clk_ddr -max 1.9 [get_ports DDR_OUT] -clock_fall -add_delay

set_output_delay -clock clk_ddr -min 0.9 [get_ports DDR_OUT]

set_output_delay -clock clk_ddr -min 1.1 [get_ports DDR_OUT] -clock_fall -add_delay上述约束的效果如下图,时钟上升沿的时延范围为0.9-2.1ns,下降沿的时延范围为1.1-1.9ns

d)设置输出时延到STARTUPE3(对于Ultrascale+器件)的pins,从逻辑单元到STARTUPE3

create_generated_clock -name clk_sck -source [get_pins -hierarchical axi_quad_spi_0/ext_spi_clk] [get_pins STARTUP/CCLK] -edges {3 5 7} #创建生成时钟

set_output_delay -clock clk_sck -max 6 [get_pins STARTUP/DATA_OUT[*]] #设置输出时延最大值

set_output_delay -clock clk_sck -min 1 [get_pins STARTUP/DATA_OUT[*]] #设置输出时延最小值四、样例工程

4.1 工程代码

module timing(clk1,clk2,clk3,ce,d1,d2,out );

input clk1,clk2,clk3,ce,d1,d2;

output out;

reg ff1,ff2,ff3;

wire comb;

always@(posedge clk1,negedge ce)

beginif(!ce)ff1<=0;else beginff1<=d1;end

end

always@(posedge clk2,negedge ce)

beginif(!ce)ff2<=0;else beginff2<=d2;end

end

assign comb=ff1*ff2;

always@(posedge clk3,negedge ce)

beginif(!ce)ff3<=0;else beginff3<=comb;end

end

assign out=ff3;

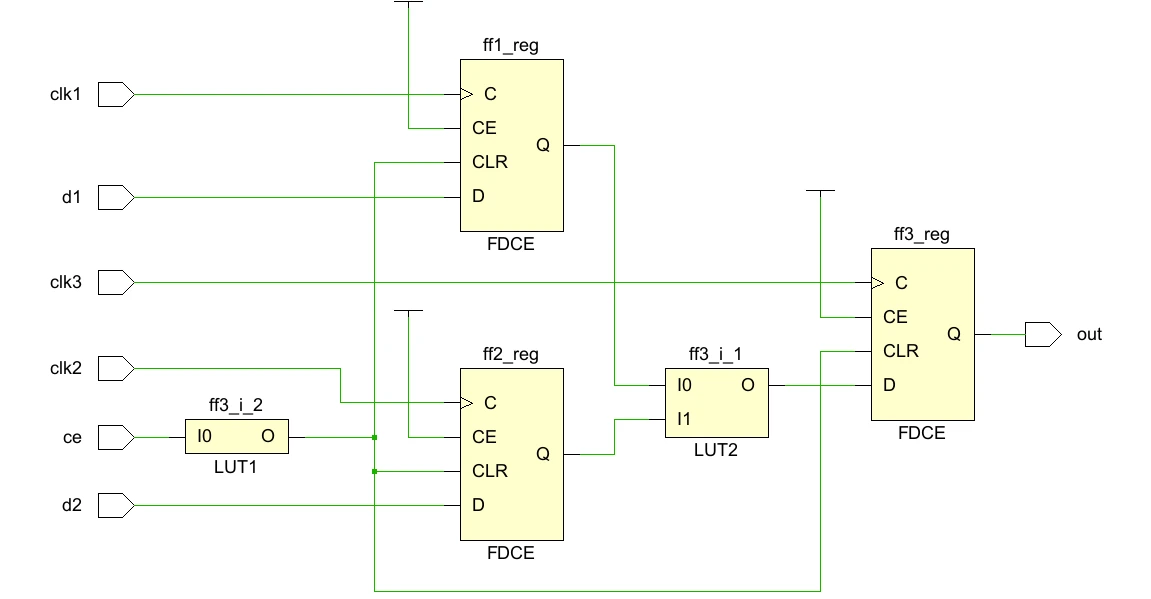

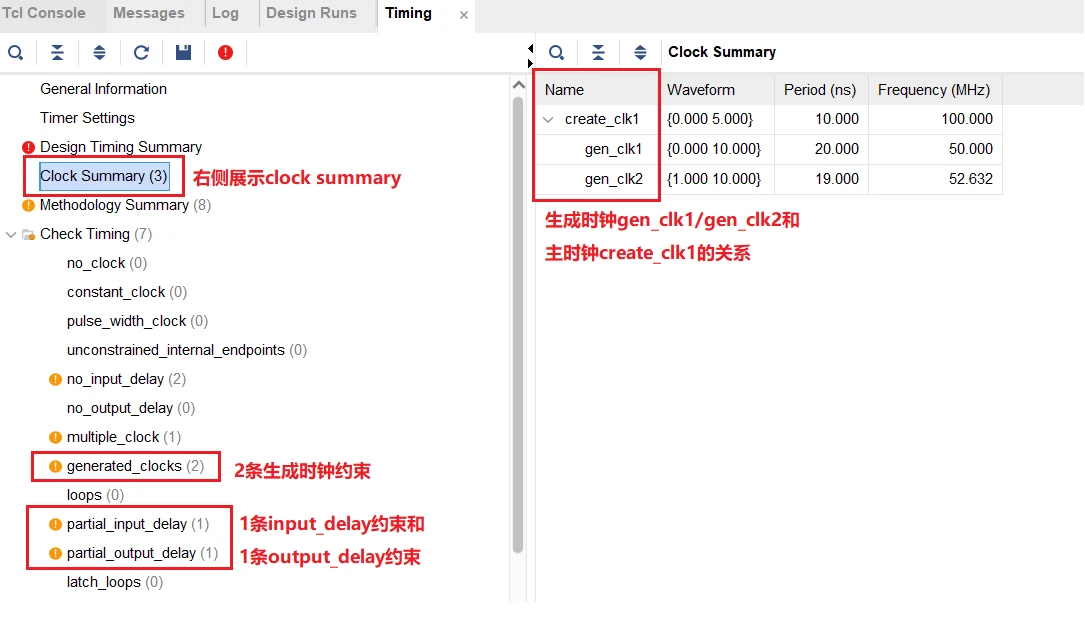

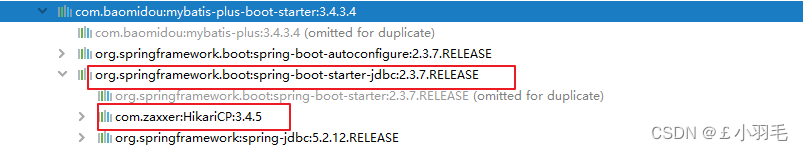

endmodule约束文件,4、5、6为set_input_delay和set_output_delay

1、create_clock -period 10.000 -name create_clk1 -waveform {0.000 5.000} [get_ports clk1] #创建主时钟create_clk1,约束到clk1

2、create_generated_clock -name gen_clk1 -source [get_ports clk1] -divide_by 2 -add -master_clock create_clk1 [get_pins ff2_reg/C] #创建生成时钟gen_clk1,约束到FF2的clk端口

3、create_generated_clock -name gen_clk2 -source [get_ports clk1] -edges {1 3 5} -edge_shift {1.000 0.000 0.000} -add -master_clock create_clk1 [list [get_pins ff2_reg/C] [get_pins ff3_reg/C]] #创建生成时钟gen_clk2,约束到FF3的clk端口

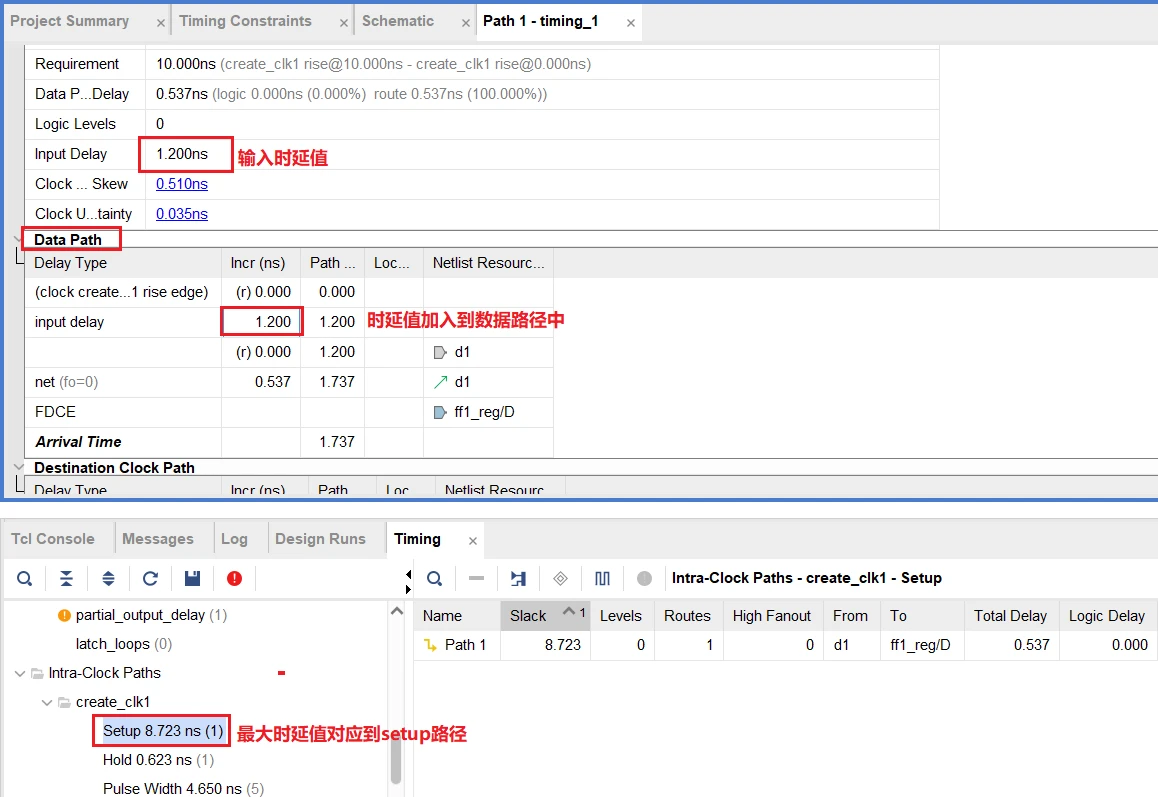

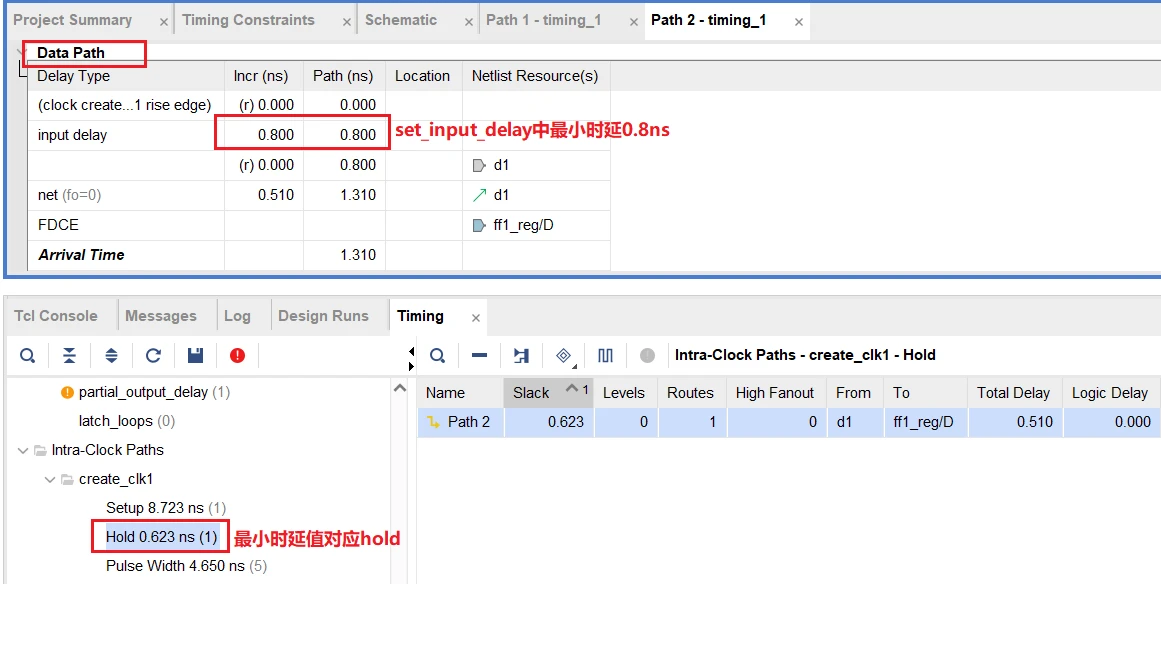

4、set_input_delay -clock [get_clocks create_clk1] -rise -min 0.800 [get_ports d1]

5、set_input_delay -clock [get_clocks create_clk1] -rise -max 1.200 [get_ports d1]#设置输入端口d1的输入时延最大值1.2ns和最小值0.8ns,

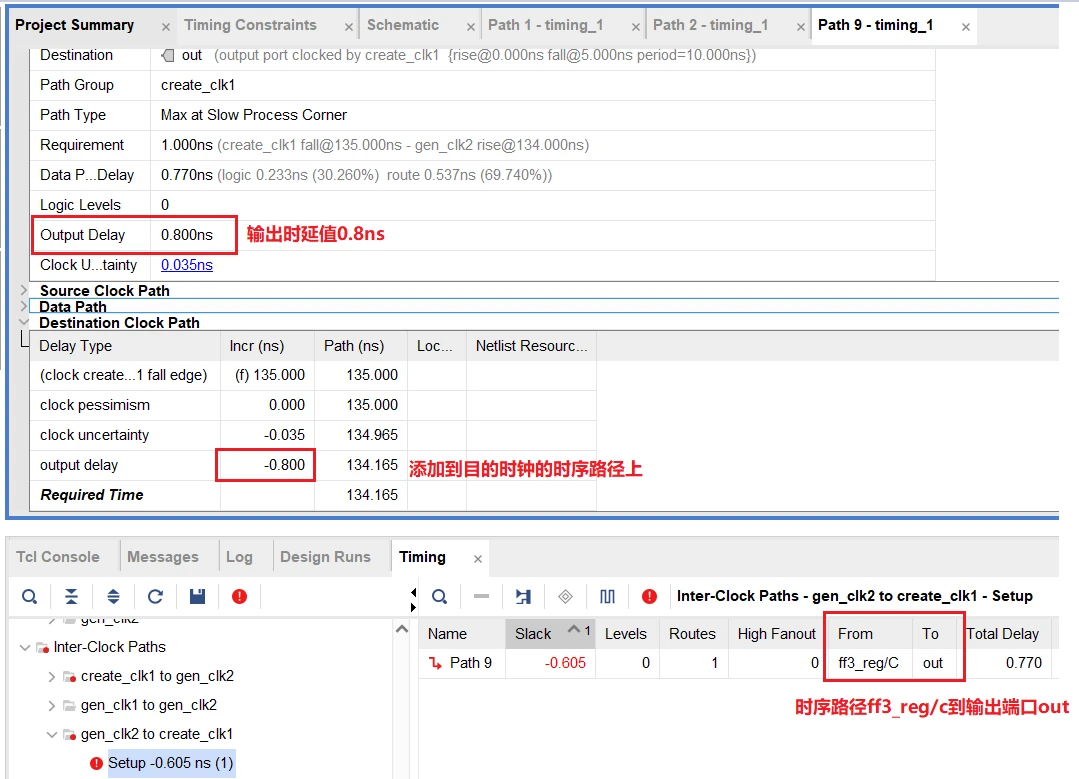

6、set_output_delay -clock [get_clocks create_clk1] -clock_fall -rise -max -add_delay 0.800 [get_ports out] #设置输出时延到输出端口out,同步时钟为create_clk1,输出延时0.8ns网表连接图,FF1_reg和ff2_reg的输出经过LUT2输出到ff3_reg,对应的时钟分别为clk1,clk2,clk3。

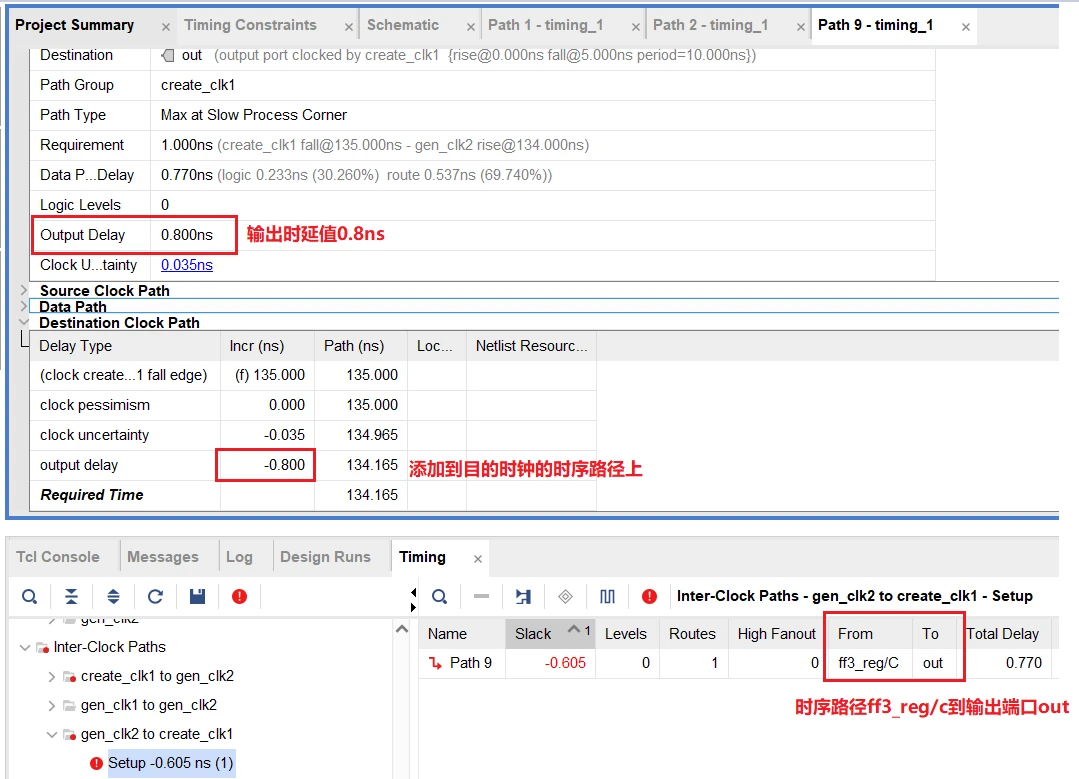

4.2 时序报告

执行Flow Navigator中综合流程下的report timing summary查看时序报告

查看约束到create_clk1的input_delay

input_delay中min时延值对应hold路径

输出时延报告,设置的约束值为0.8ns,符合预期

五、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt

提取码:mylt

相关文章:

FPGA设计时序约束二、输入延时与输出延时

目录 一、背景 二、set_input_delay 2.1 set_input_delay含义 2.2 set_input_delay参数说明 2.3 使用样例 三、set_output_delay 3.1 set_output_delay含义 3.2 set_output_delay参数说明 3.3 使用样例 四、样例工程 4.1 工程代码 4.2 时序报告 五、参考资料 一、…...

电阻的基础与应用

文章目录 电阻的基础与应用电阻的介绍与分类电阻介绍电阻的分类碳膜/金属膜电阻厚膜/薄膜电阻功能性电阻(光敏/热敏/压敏)特殊电阻(绕线电阻/水泥电阻/铝壳电阻) 电阻的主要厂家与介绍国外厂家VISHAY(威世)KOA(兴亚)Kyocera(京瓷)…...

5.html表格

<table><tr><th>列1标题</th><th>列2标题</th><th>列3标题</th></tr><tr><td>行1列1</td><td>行1列2</td><td>行1列3</td></tr><tr><td>行2列1</td>…...

飞桨EasyDL-Mac本地部署离线SDK-Linux集成Python

前言:本文对使用飞桨EasyDL桌面版实现本地部署物体检测做一下说明 一、训练模型 如何使用飞桨EasyDL桌面版这里就不再赘述,直接参照官方文档进行物体检测模型训练。 飞桨EasyDL桌面版-用零代码开发实现物体检测https://ai.baidu.com/ai-doc/EASYDL/Tl2…...

【kubernetes】Kubernetes中的DaemonSet使用

目录 1 为什么需要DaemonSet2 DaemonSet的Yaml的关键字段3 DaemonSet的使用4 一种自行控制Pod更新的方式5 总结 1 为什么需要DaemonSet Deployment可以用于部署无状态的应用,例如系统的接口层或者逻辑层,而多个Pod可以用于负载均衡和容灾。如果有这样一…...

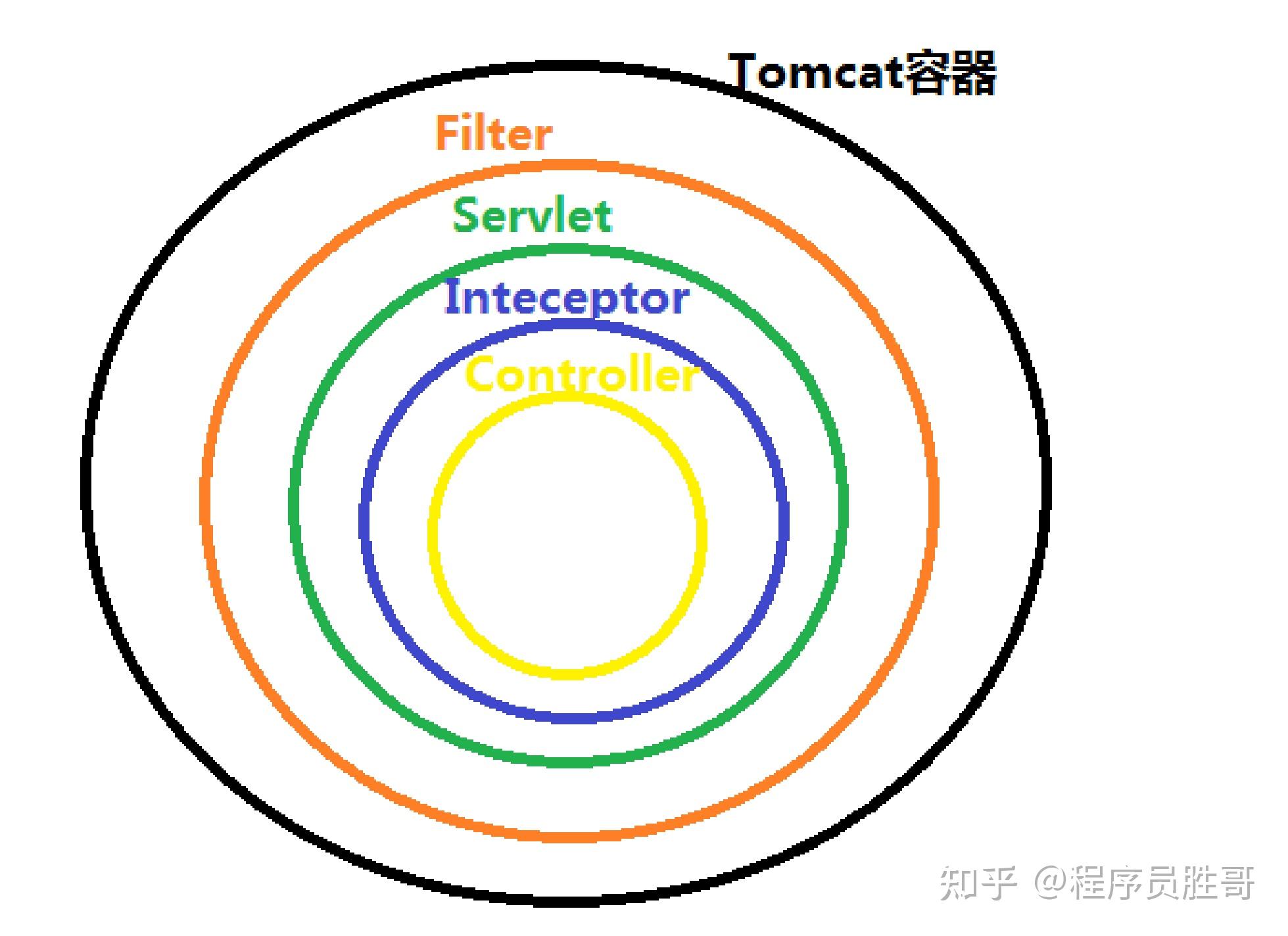

《 新手》web前端(axios)后端(java-springboot)对接简解

文章目录 <font color red>1.何为前后端对接?2.对接中关于http的关键点2.1. 请求方法2.2. 请求参数设置简解: 3.对接中的跨域(CROS)问题**为什么后端处理跨域尽量在业务之前进行?**3.总结 1.何为前后端对接? “前后端对接” 是指前端和后端两个…...

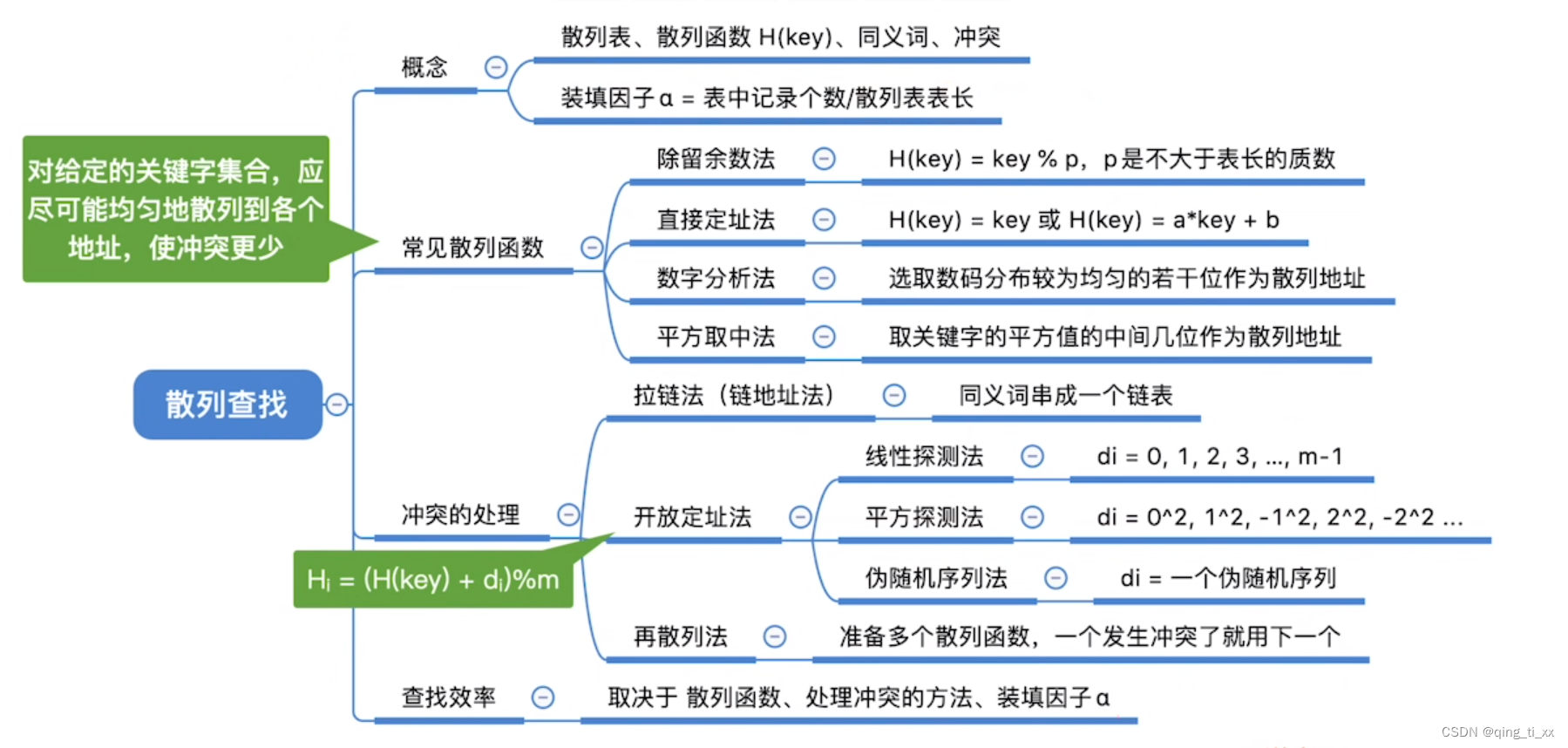

第七章 查找 十、散列查找

一、哈希表(散列表) 哈希表的数据元素的关键字与其存储地址直接相关。 二、解决冲突的方法 三、散列表中元素的查找 总共对比了3个关键字,所以查找长度为3. 四、查找效率计算 (1)成功的概率 需要对比一次的关键字为…...

第一章 C语言知识补充

求字节数运算符:sizeof 强制类型转换运算符:(类型) 下标运算符:[ ] 函数调用运算符:( ) 算术移位指令 算术移位指令有:算术左移SAL和算术右移SAR。算术移位指令的功能描述如下:…...

【Book And Paper 】

【paper Interactive Segmentation of Radiance Fields 算法设计: 电子版...

计算机竞赛 深度学习疲劳检测 驾驶行为检测 - python opencv cnn

文章目录 0 前言1 课题背景2 相关技术2.1 Dlib人脸识别库2.2 疲劳检测算法2.3 YOLOV5算法 3 效果展示3.1 眨眼3.2 打哈欠3.3 使用手机检测3.4 抽烟检测3.5 喝水检测 4 最后 0 前言 🔥 优质竞赛项目系列,今天要分享的是 🚩 **基于深度学习加…...

代码随想录 动态规划 13

300. 最长递增子序列 给你一个整数数组 nums ,找到其中最长严格递增子序列的长度。 子序列 是由数组派生而来的序列,删除(或不删除)数组中的元素而不改变其余元素的顺序。例如,[3,6,2,7] 是数组 [0,3,1,6,2,2,7] 的子…...

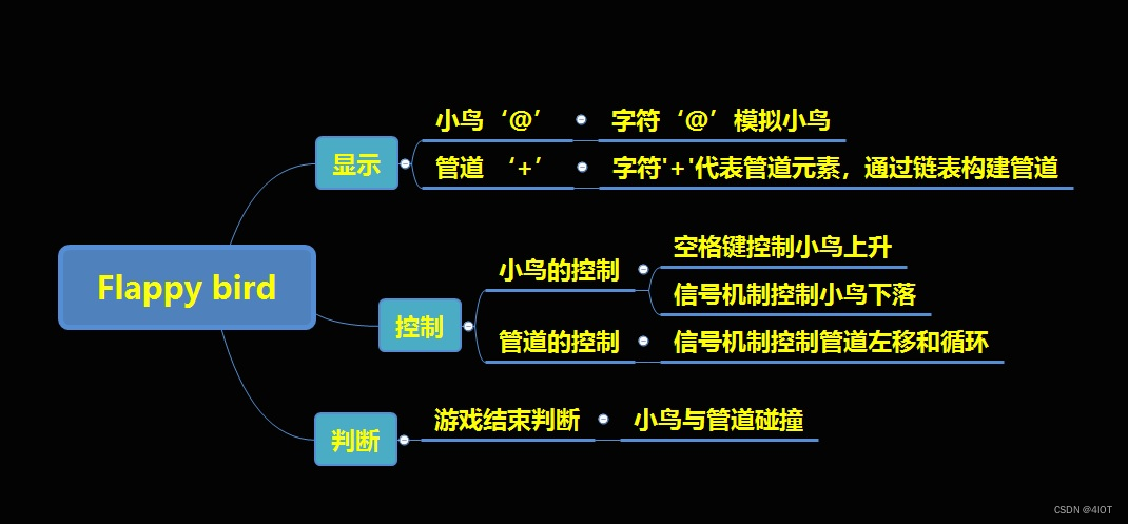

lv6 嵌入式开发-Flappy bird项目

目录 1 项目功能总结 2 知识储备: 3 项目框图 4 Ncurses库介绍 做Flappy bird项目有什么用? 1. 复习、巩固c语言知识 2. 培养做项目的逻辑思维能力 3. 具备开发简单小游戏的能力 学会了Flappy bird项目,贪吃蛇和推房子两款小游戏也可…...

【Java】方法重写

概述 子类中出现了和父类一模一样的方法 当子类需要父类的功能,而功能主体中,子类有自己独特的内容,就可以通过重写父类中的方法,这样即延续了父类的功能,又定义了自己的特有内容 Override 是一个注解,可以…...

艺术表现形式

abstract expressionism 抽象表现主义 20世纪中期的一种艺术运动,包括多种风格和技巧,特别强调艺术家通过非传统和通常非具象的手段表达态度和情感的自由。 抽象表现主义用有力的笔触和滴落的颜料来表达情感和自发性。 简单地结合“abstract expression…...

PHP 反序列化漏洞:手写序列化文本

文章目录 参考环境序列化文本Scalar Type整数浮点数布尔值字符串 Compound Type数组数据结构序列化文本 对象数据结构序列化文本 Special TypeNULL数据结构序列化文本 手写序列化文本过程中的注意事项个数描述须于现实相符序列化文本前缀的大小写变化符号公共属性 参考 项目描…...

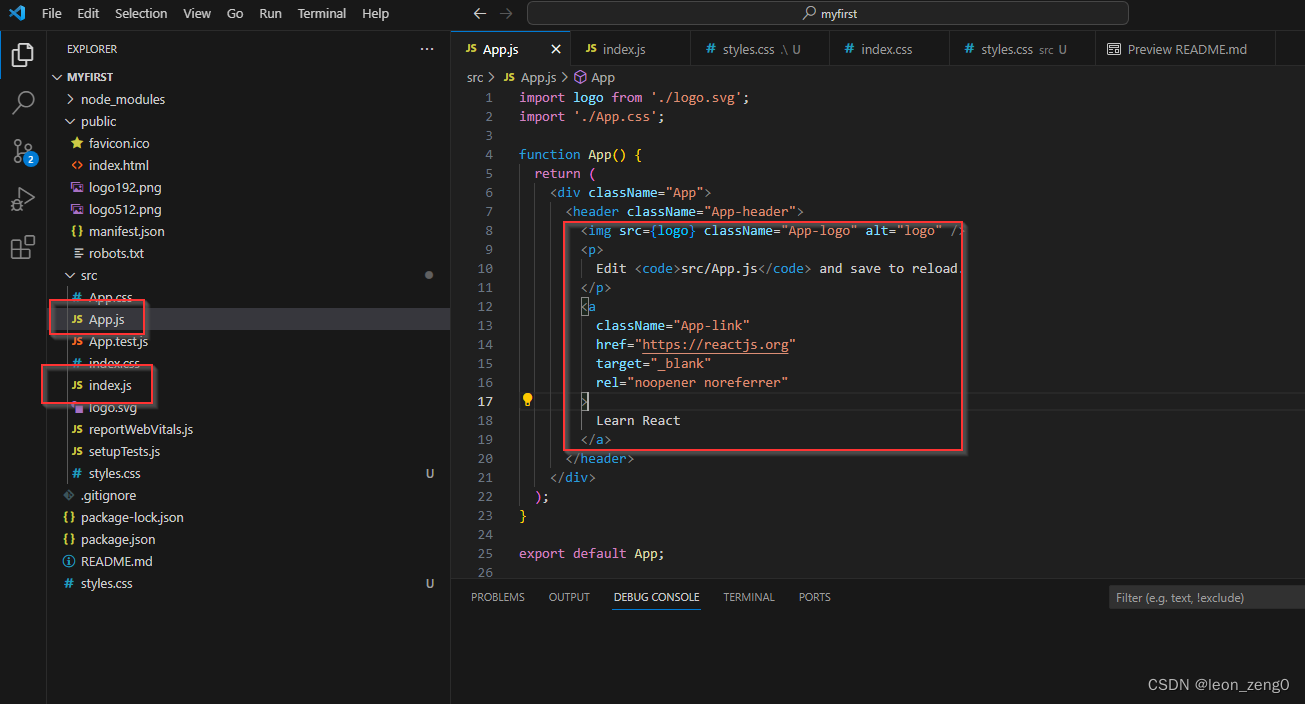

react.js在visual code 下的hello World

想学习reacr.js ,就开始做一个hello world。 我的环境是visual code ,所以我找这个环境下的例子。参照: https://code.visualstudio.com/docs/nodejs/reactjs-tutorial 要学习react.js ,还得先安装node.js,我在visual …...

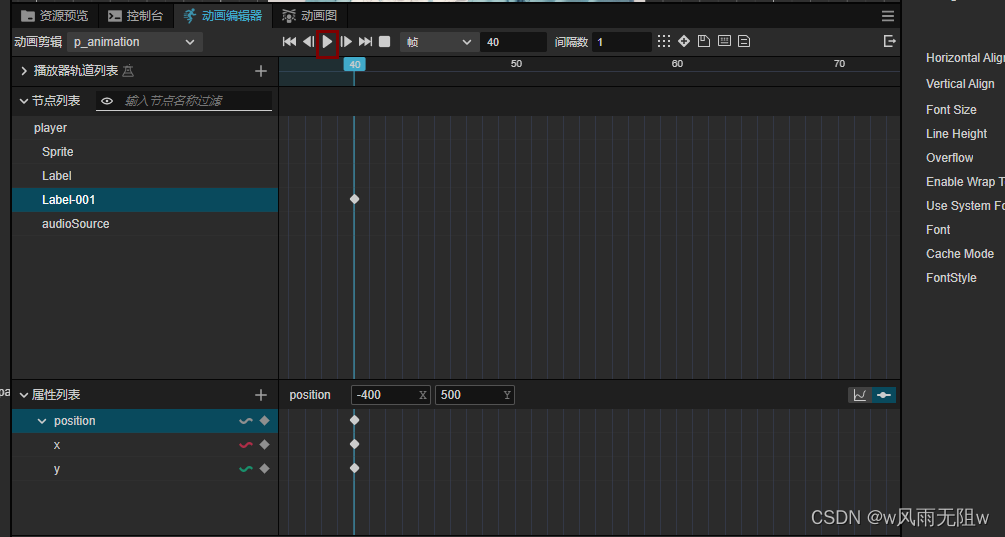

CocosCreator3.8研究笔记(二十四)CocosCreator 动画系统-动画编辑器实操-关键帧实现动态水印动画效果

上一篇,我们介绍了动画编辑器相关功能面板说明,感兴趣的朋友可以前往阅读: CocosCreator3.8研究笔记(二十三)CocosCreator 动画系统-动画编辑器相关功能面板说明。 熟悉了动画编辑器的基础操作,那么再使用动…...

第1篇 目标检测概述 —(3)YOLO系列算法

前言:Hello大家好,我是小哥谈。YOLO(You Only Look Once)系列算法是一种目标检测算法,主要用于实时物体检测。相较于传统的目标检测算法,YOLO具有更快的检测速度和更高的准确率。YOLO系列算法的核心思想是将…...

SpringBoot整合数据库连接

JDBC 1、SQL准备 DROP TABLE IF EXISTS t_book;CREATE TABLE t_book (book_id int(11) NOT NULL,book_name varchar(255) DEFAULT NULL,price int(11) DEFAULT NULL,stock int(11) DEFAULT NULL ) ENGINEInnoDB DEFAULT CHARSETutf8mb4;/*Data for the table t_book */insert…...

uni-app:canvas-绘制图形4(获取画布宽高,根据画布宽高进行图形绘制)

效果 代码 var width ; var height ; const query uni.createSelectorQuery(); //获取宽度 query.select(#firstCanvas).fields({ size: true }, (res) > { width res.width; height res.height; }).exec(); console.log(宽度width); console.log(高…...

STM32F103 IAP实战:从Bootloader设计到远程固件更新

1. 为什么你的STM32需要IAP升级? 第一次接触IAP(In-Application Programming)这个概念时,我正蹲在工厂车间的设备旁边,手里拿着需要升级的STM32板子发愁。产线上30台设备需要更新程序,而每台设备都要拆外壳…...

PICAXE单片机驱动DS18B20温度传感器:从硬件连接到数据处理

1. 项目概述:用PICAXE玩转DS18B20数字温度传感器如果你手头有一块PICAXE单片机,想快速实现一个温度监测项目,那么DS18B20这颗数字温度传感器绝对是你的绝佳拍档。它只需要一根数据线就能和MCU通信,抗干扰能力强,还能通…...

网络安全入门:2026年转行网络安全完整路径图

网络安全入门:2026 年转行网络安全完整路径图 导语:2026 年,网络安全人才缺口达 150 万,平均薪资较传统 IT 岗位高出 30%。但 70% 的转行者因路径不清晰而失败。本文详解 2026 年转行网络安全的完整路径:学习路线、证…...

QQ音乐加密文件解密终极指南:qmcdump实战深度解析

QQ音乐加密文件解密终极指南:qmcdump实战深度解析 【免费下载链接】qmcdump 一个简单的QQ音乐解码(qmcflac/qmc0/qmc3 转 flac/mp3),仅为个人学习参考用。 项目地址: https://gitcode.com/gh_mirrors/qm/qmcdump 你是否遇到…...

Cortex-R52内存管理与实时性优化技术解析

1. Cortex-R52内存管理架构解析Cortex-R52作为Armv8-R架构的旗舰级实时处理器,其内存管理系统针对高可靠性场景进行了深度优化。与传统MMU不同,R52采用了增强型MPU(Memory Protection Unit)设计,通过16-24个可编程保护…...

人工智能的发展历程)

图解人工智能(10)人工智能的发展历程

人工智能自20世纪50年代发展至今,经历了若干次高潮和低谷。每到陷入困境的时候,总有一些科学家勇敢地打破传统思想的束缚,创造出新理论、新方法,使人工智能重现生机。例如,在符号主义陷入危机的时候,费根鲍…...

MatrixFusion™矩阵视频融合,一路画面管全厂,彻底消除车间监控盲区

MatrixFusion™矩阵视频融合,一路画面管全厂,彻底消除车间监控盲区在智能制造全域可视化管控的落地实践中,工业车间因设备密集、产线交错、通道迂回、多区域分割的固有场景特性,成为监控体系搭建的核心难点。传统工业视频监控系统…...

告别SVN提交冲突!手把手教你配置TortoiseSVN 1.10.5的忽略列表与清理功能

告别SVN提交冲突!手把手教你配置TortoiseSVN 1.10.5的忽略列表与清理功能 团队协作开发中,版本控制系统是必不可少的工具。Subversion(SVN)作为一款经典的集中式版本控制系统,至今仍在许多项目中发挥着重要作用。然而&…...

CMS三十年:从“手工建站”到“智能基座”

一个从业者的观察与思考不知不觉,跟CMS打交道已经十几年了。从早期的织梦、帝国,到后来的WordPress,再到现在的各类无头CMS和低代码平台,这个领域的变化比想象中要快得多。写这篇文章,算是对CMS发展历程的一次梳理&…...

欲取全国第一先取北京第一,CSDN 博客排名现在是郑州第一

欲取全国第一先取北京第一,CSDN 博客排名现在是郑州第一 首先,必须得说,郑州第一,太牛了! 这绝对是对你技术输出和持续分享的高度认可,含金量十足。 不过,关于“欲取全国第一先取北京第一”这个…...