ARMv8如何读取cache line中MESI 状态以及Tag信息(tag RAM dirty RAM)并以Cortex-A55示例

Cortex-A55 MESI 状态获取

- 一,系统寄存器以及读写指令

- 二,Cortex-A55 Data cache的MESI信息获取(AARCH 64)

- 2.1 将Set/way信息写入Data Cache Tag Read Operation Register

- 2.2 读取Data Register 1和Data Register 0数据并解码

- 参考文章:

一,系统寄存器以及读写指令

本文以Cortex-A55处理器为例,通过访问 处理器中的内部存储单元(tag RAM和dirty RAM),来读取cache line 中的MESI信息。

Cortex-A55提供了一种通过读取一些系统寄存器,来访问Cache 和 TLB使用的一些内部存储单元(internal memory)的机制。这个功能可以探查出当缓存中的数据与主存中的数据不一致时存在的问题。

此外,AArch64模式和AArch32模式的读取方式不同:

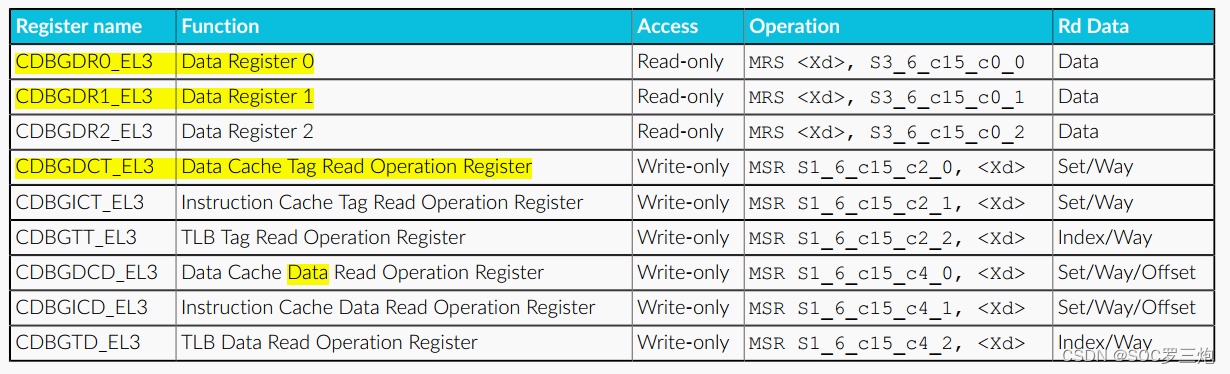

当处理器处于AArch64模式时,先通过一些只写(write-only)寄存器来选择具体的cache line和内存地址,然后通过只读寄存器来读取具体的tag信息。下图为相关寄存器以及相关操作指令,需要注意的是,这些操作只在EL3时可用,如果在其他模式下使用这些指令,将会进入Undefined Instruction 异常。

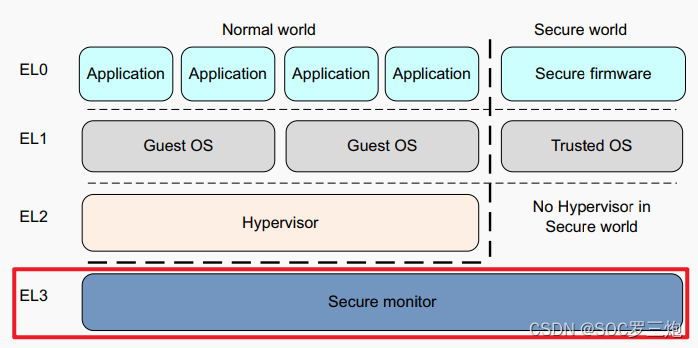

ARMv8下,AArch64的EL3如下图红框所示:

AArch64下获取内部存储单元信息的相关寄存器以及指令:

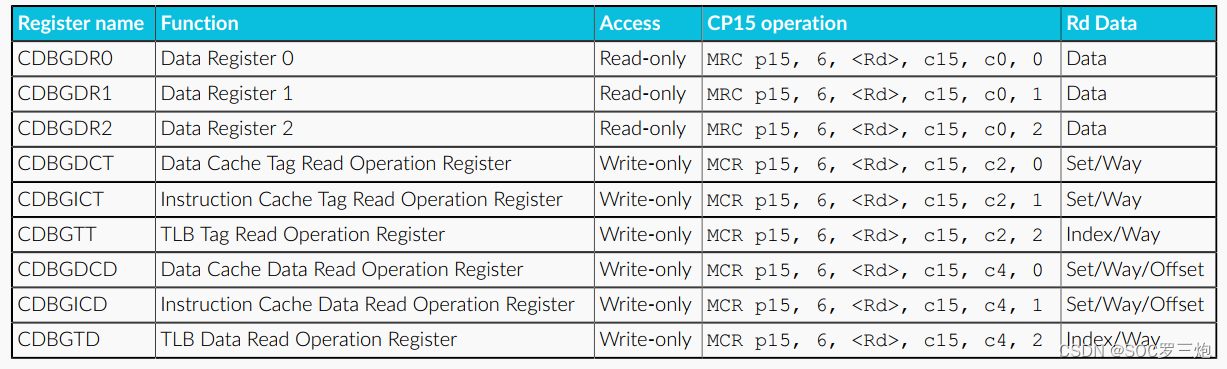

当处理器处于AArch32模式下时,先通过一些只写(write-only)CP15寄存器来选择具体的cache line和内存地址,然后通过只读CP15寄存器来读取具体的tag信息。下图为相关寄存器以及相关操作指令,需要注意的是,这些操作只在EL3时可用,如果在其他模式下使用这些CP15指令,将会进入Undefined Instruction 异常。

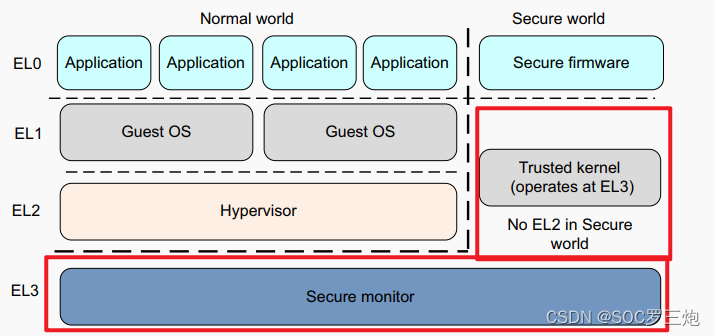

ARMv8下,AArch32的EL3如下图红框所示:

AArch32下获取内部存储单元信息的相关寄存器以及指令:

Cortex-A55支持一下内部存储单元信息的获取:

- L1 data cache

- L1 instruction cache

- L2 TLB

- Main TLB RAM

- Walk cache

- IPA cache

二,Cortex-A55 Data cache的MESI信息获取(AARCH 64)

接下来,本文以Cortex-A55的Data cache为例,读取其某个cache line的tag信息,其具体的步骤很简单,分为两步:

- 写入Data Cache Tag Read Operation Register,写入的内容为具体的Set和way信息,通过way index和set index来定位到想要读取的cache line。

- 读取相应的 Data Register 0 和 Data Register 1寄存器,通过对Data Register寄存器里面的数据进行解码,来获取tag 信息。

2.1 将Set/way信息写入Data Cache Tag Read Operation Register

首先,我们需要从一个虚拟地址(VA)中解析出Set index信息。

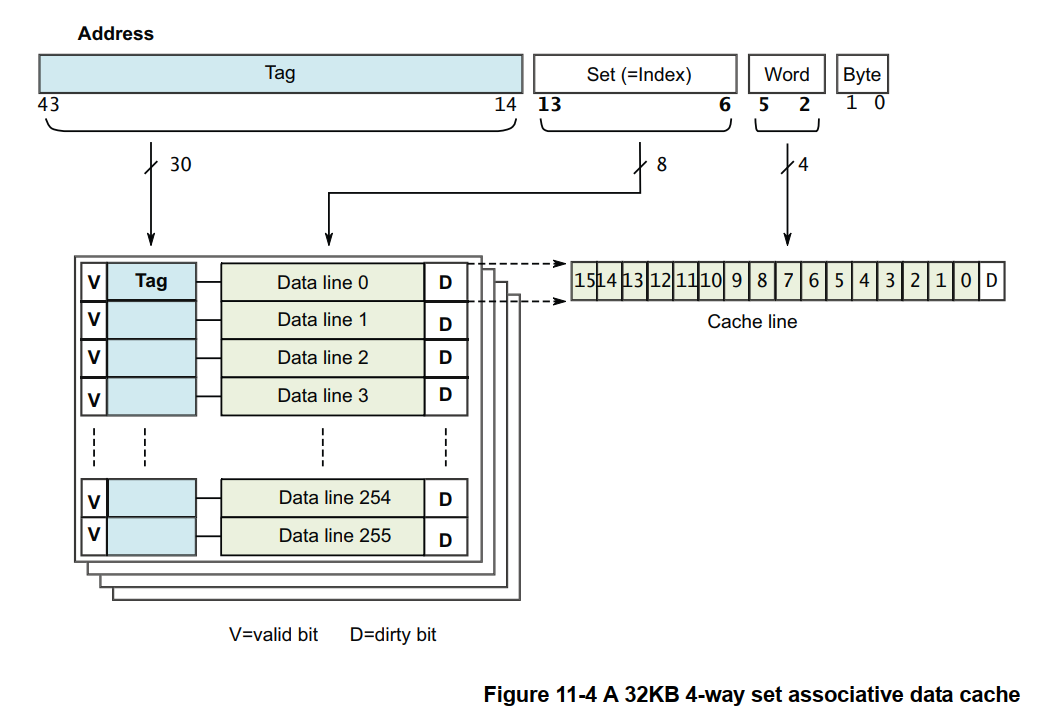

下图为Cortex-A57的4-way组相连的32KB大小的data cache结构,其cache line大小也为64 bytes,从图中可知,一个VA可以被分成几个部分:Tag,Set index,word index以及byte index。其中Set index = VA[13:6]。

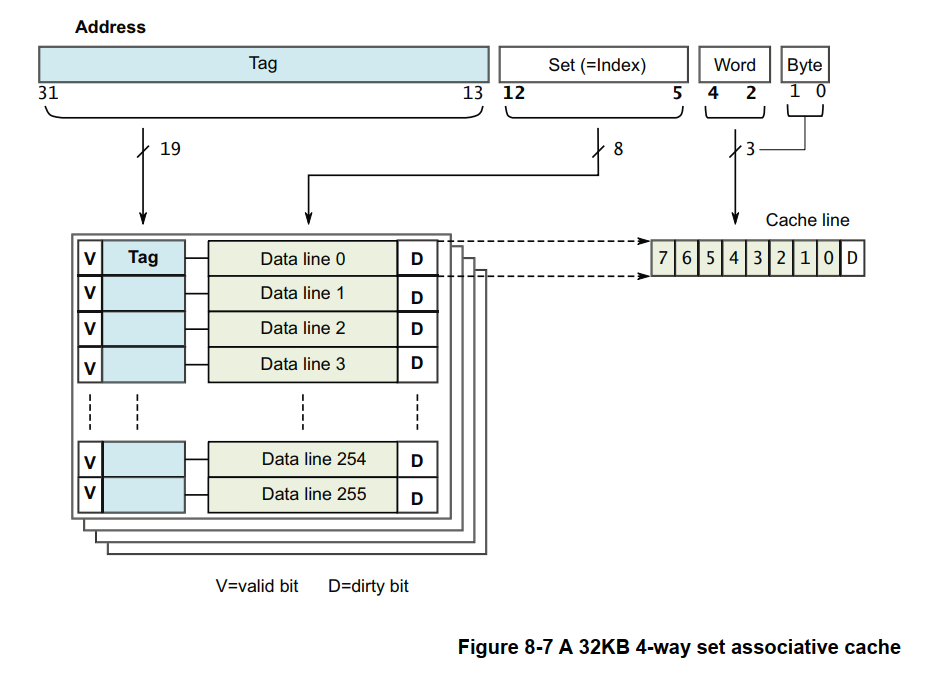

在另一个实例中,32KB大小的4-way组相连data cache,cache line大小为32 bytes,其Set index = VA[12:5]:

Cortex-A55的Data cache为4-way 组相连结构。假设其为32KB,一个cache line的大小为64 bytes,我们就可以求出该data cache中有 32 KB / 64 B / 4 = 2^7 = 128个set(组),也就是说至少需要7个bit才能完整解析出具体的set index。如下图所示,可以通过公式:

S = log2(Data cache size / 4).

S=12 For a 16KB cache.

S=13 For a 32KB cache.

S=14 For a 64KB cache.

来计算出Set index的范围:Set index = VA[12:6]。

由于是4-way 组相连结构,cache line 可以存在与任意一个way中,所以我们的cache way可能为0,1,2,3中任意一个数字。

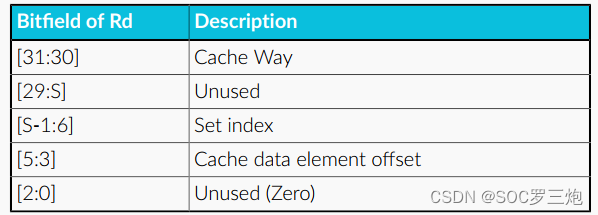

求得了set和way的index后,需要对其进行编码,然后写入到Data Cache Tag Read Operation Register寄存器中。其编码规则如下图所示,只需将Set和way的值写入对应的bit中即可,其中Rd[5:3]为cahche double word数据的偏移量,由于本次示例是读取tag信息,所以Rd[5:3]为0即可。

所以我们要写入Data Cache Tag Read Operation Register的Rd的值可以通过以下代码获取:

unsigned int get_Rd_data(int * VA, way_num)

{unsigned int set_way_index = VA | 0x1FC0; //get way index, VA[12:6]set_way_index |= way_num < 30; //way_num could be 0,1,2,3 return set_way_index;

}

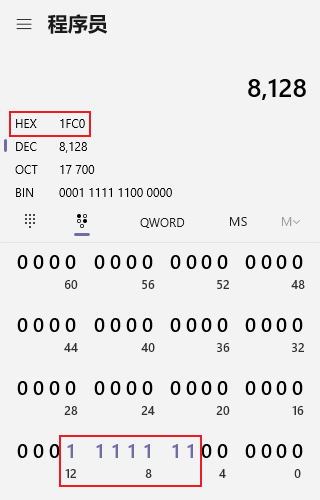

Rd中除了Set和way信息,其他值均为0,0x1FC0为VA[12:6]全为1的情况:

然后我们使用如下指令将Rd的值写入,假设Rd为R0:

MSR S1_6_c15_c2_0, x0; x0 = get_Rd_data(VA,way_num)

2.2 读取Data Register 1和Data Register 0数据并解码

将Set/way信息写入Data Cache Tag Read Operation Register 后,相当于选择了想要操作的cache line,接下来我们将读取Data Register 1和Data Register 0的数据来获取该cache line里的tag信息,除了tag信息外,我们还可以从Data Register 1和Data Register 0两个寄存器中获取:

- MESI 状态信息

- outer内存属性

- valid 信息

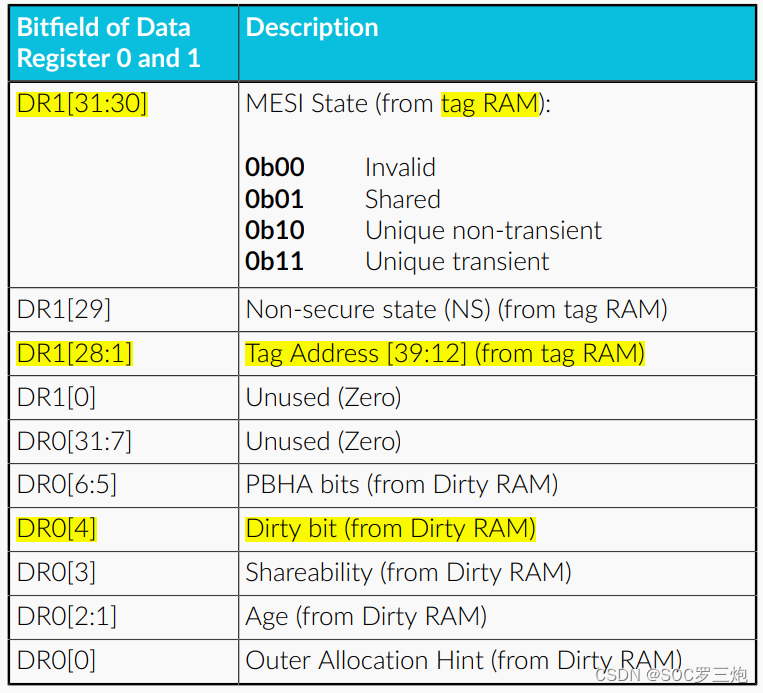

可获得的信息具体见下图:

需要注意的是,如果是想获取MESI状态信息,则需要两个寄存器配合使用,即读取Data Register 0 [4] - Dirty以及Data Register 1 [31:30] - MESI :

Data Register 0 [4]里的为来自Dirty RAM的Dirty bit,用于判断当前cache line 是否为diry。

- 0:clean

- 1:dirty

Data Register 1 [30:29]里的为来自tag RAM的MESI信息:

- 0b00 Invalid

- 0b01 Shared

- 0b10 Unique non-transient

- 0b11 Unique transient

关于transient的概念本文这里不做过多描述,读者可以自行查阅ARM相关文档:

In Armv8, it is IMPLEMENTATION DEFINED whether a Transient hint is supported. In an implementation that supports the Transient hint, the Transient hint is a qualifier of the cache allocation hints, and indicates that the benefit of caching is for a relatively short period. It indicates that it might be better to restrict allocation of transient entries, to avoid possibly casting-out other, less transient, entries.

A55 has a specific behavior for memory regions that are marked as Write-Back cacheable and transient, as defined in the Armv8 A architecture:

- For any load that is targeted at a memory region that is marked as transient, the following occurs:

- If the memory access misses in the L1 data cache, the returned cache line is allocated in the L1 data cache but is marked as transient.

- On eviction, if the line is clean and marked as transient, it is not allocated into the L2 cache but is marked as invalid.

- For stores that are targeted at a memory region that is marked as transient, if the store misses in the L1 data cache, the line is allocated into the L2 cache.

关于MESI信息,读者只需知道transient hint是一种由具体架构实现定义的一种属性,本文假设当前环境没有实现transient,所以Data Register 1 [30:29] MESI信息里的Unique表示为 0b10。

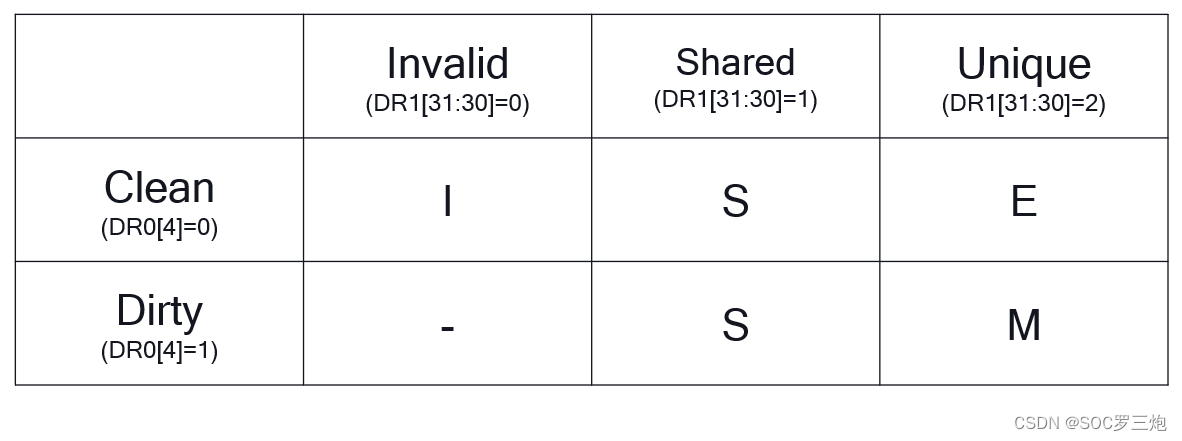

根据笔者的上篇博文:缓存一致性(cache coherency)解决方案:MESI 协议状态转换详解 可知,来自tag RAM的MESI信息需要和Dirty bit一起组合使用,才能表示出完整的MESI信息:

- M,Modified, Unique Dirty((UD), 只存在于当前cache中(unique),并且该cache line上的数据与下一级存储单元中的数据不同(dirty)。换言之,cache line中最新的数据位于当前cache,其他cache中没有备份 ,cache line中的内容与主存中的不一致。

- E,Exclusive, Unique Clean(UC),数据只存在于当前cache line中,并且为clean的。cache中cache line中的数据于主存中的一致,并且其他core中的cache没有该地址的数据备份,只存在一个cache中。

- S,Shared Clean (SC), Shared ,cache line中的data不一定与主存中的一致,但是shared cache line中的数据是最新的,且存在于多个core中。

- I,Invalid,无效的数据,或者可以说当前cache line里没有数据。

最后可以得出如下组合关系:

比如读取到的Data Register 0 [4]为1,以及Data Register 1 [31:30]为2,根据上图的组合关系,可知当前cache line的MESI状态为 Unique+Dirty = Modified。

完整的获取MESI信息的示例代码如下:

; step 1: write set index and way num into Data Cache Tag Read Operation Register

MSR S1_6_c15_c2_0, x0; x0 = get_Rd_data(VA,way_num)

; step 2: read Data Register 1 and Data Register 0

MRS x1, S3_6_c15_c0_0 ;x1 = Data Register 0

MRS x2, S3_6_c15_c0_1 ;x2 = Data Register 1

参考文章:

cortex_a55_trm_100442_0200_01_en.pdf

相关文章:

ARMv8如何读取cache line中MESI 状态以及Tag信息(tag RAM dirty RAM)并以Cortex-A55示例

Cortex-A55 MESI 状态获取 一,系统寄存器以及读写指令二,Cortex-A55 Data cache的MESI信息获取(AARCH 64)2.1 将Set/way信息写入Data Cache Tag Read Operation Register2.2 读取Data Register 1和Data Register 0数据并解码 参考…...

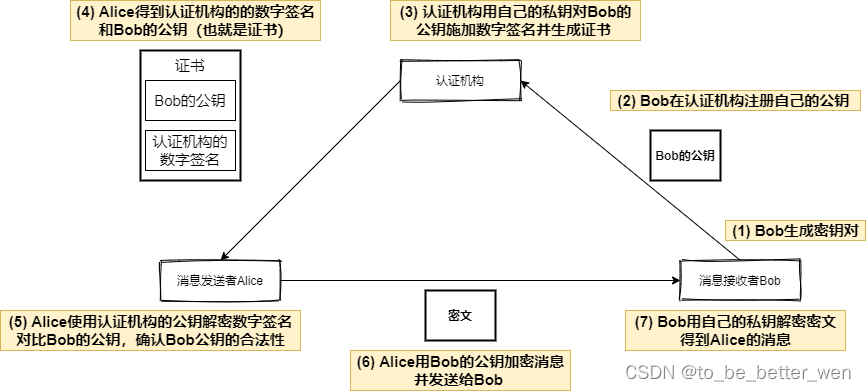

密码技术 (6) - 证书

一. 前言 前面介绍的公钥密码和数字签名,都无法解决一个问题,那就是判断自己获取的公钥是否期望的,不能确定公钥是否被中间攻击人掉包。所以,证书的作用是用来证明公钥是否合法的。本文介绍的证书就是解决证书的可靠性的技术。 二…...

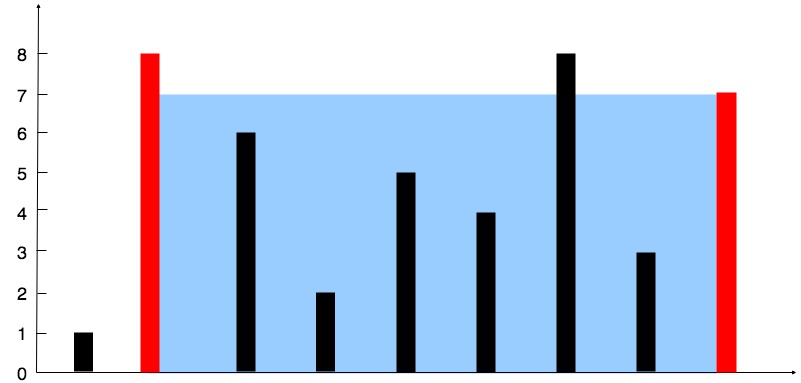

【算法学习】-【双指针】-【盛水最多的容器】

LeetCode原题链接:盛水最多的容器 下面是题目描述: 给定一个长度为 n 的整数数组 height 。有 n 条垂线,第 i 条线的两个端点是 (i, 0) 和 (i, height[i]) 。 找出其中的两条线,使得它们与 x 轴共同构成的容器可以容纳最多的水。…...

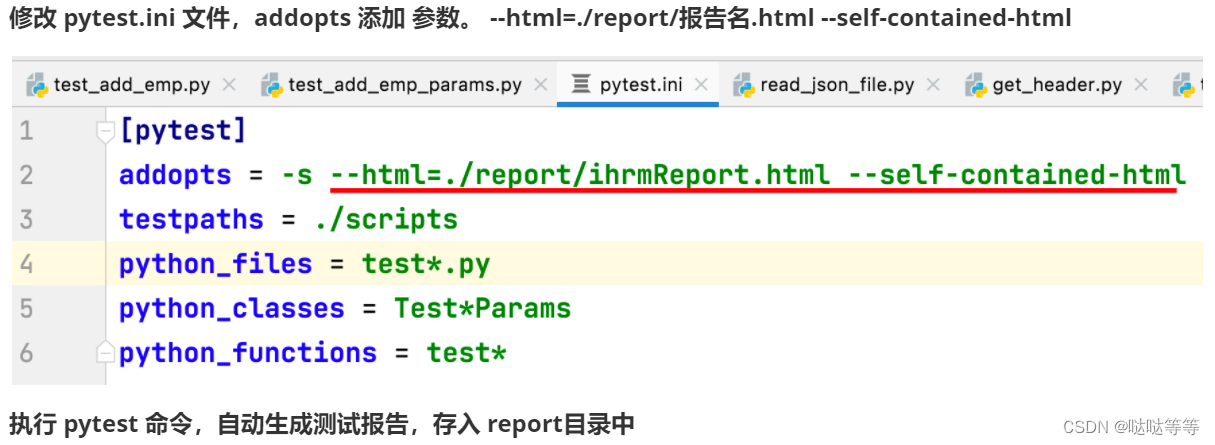

JAVA面经整理(8)

一)为什么要有区,段,页? 1)页是内存和磁盘之间交互的基本单位内存中的值修改之后刷到磁盘的时候还是以页为单位的索引结构给程序员提供了高效的索引实现方式,不过索引信息以及数据记录都是记录在文件上面的,确切来说是…...

【Java 进阶篇】JDBC数据库连接池Druid详解

在Java应用程序中,与数据库进行交互是一个常见的任务。为了更有效地管理数据库连接并提高性能,数据库连接池是一种常见的解决方案。Druid是一个流行的JDBC数据库连接池,它具有丰富的功能和高性能。本博客将详细介绍Druid连接池,包…...

Linux——指令初识

Linux下基本指令 前言一、 ls 指令二、 pwd命令三、cd 指令四、 touch指令五、mkdir指令六、rmdir指令 && rm 指令七、man指令八、cp指令九、mv指令十、cat指令十一、.more指令十二、less指令十三、head指令十四、tail指令总结 前言 linux的学习开始啦! 今…...

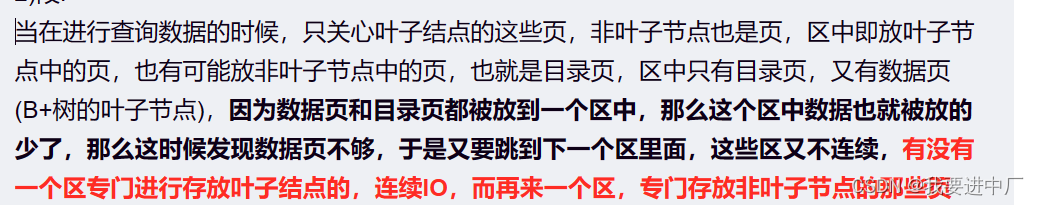

专题一:双指针【优选算法】

双指针应用场景: 数组划分、数组分块 目录 一、移动0 二、复写0 从后向前 三、快乐数 链表带环 四、盛水最多的容器 单调性双指针 五、有效三角形个数 单调性双指针 六、和为s的两个数字 七、三数之和 细节多 需再练 一、移动0 class Solution { public:void move…...

蓝桥等考Python组别十二级007

第一部分:选择题 1、Python L12 (15分) 运行下面程序,输出的结果是( )。 lis = [A, B, C, D, E, F] print(lis[0 : 3]) [A, B, C][A, B][A, B, C, D][B, C, D]正确答案:A 2...

全方位介绍工厂的MES质量检验管理系统

一、MES质量检验管理系统的定义: MES质量检验管理系统是基于制造执行系统的框架和功能,专注于产品质量的控制和管理。它通过整合和优化质量检验流程,提供实时的数据采集、分析和反馈,帮助工厂实现高效的质量管理。该系统涵盖了从…...

避免风险,亚马逊、沃尔玛、阿里国际站选择什么样的测评方式最安全?

亚马逊、沃尔玛、速卖通、阿里国际站上做测评是最有效的推广手段之一,而测评又存在很大的风险。但是测评的风险来自哪里?什么样的测评方式才安全呢? 因为平台大数据风控点很多,根据洪哥六七年的测评经验,风控包括以下…...

【C语言】语法--联合体union详解

本文参考博客: https://blog.csdn.net/m0_57180439/article/details/120417270 定义及示例: 联合是一种特殊的自定义类型,该种类型定义的变量也包含一系列的成员,特征是这些成员共用同一块空间,所以联合体也被称为共用体。 #include<stdio.h> union Un//联合类型…...

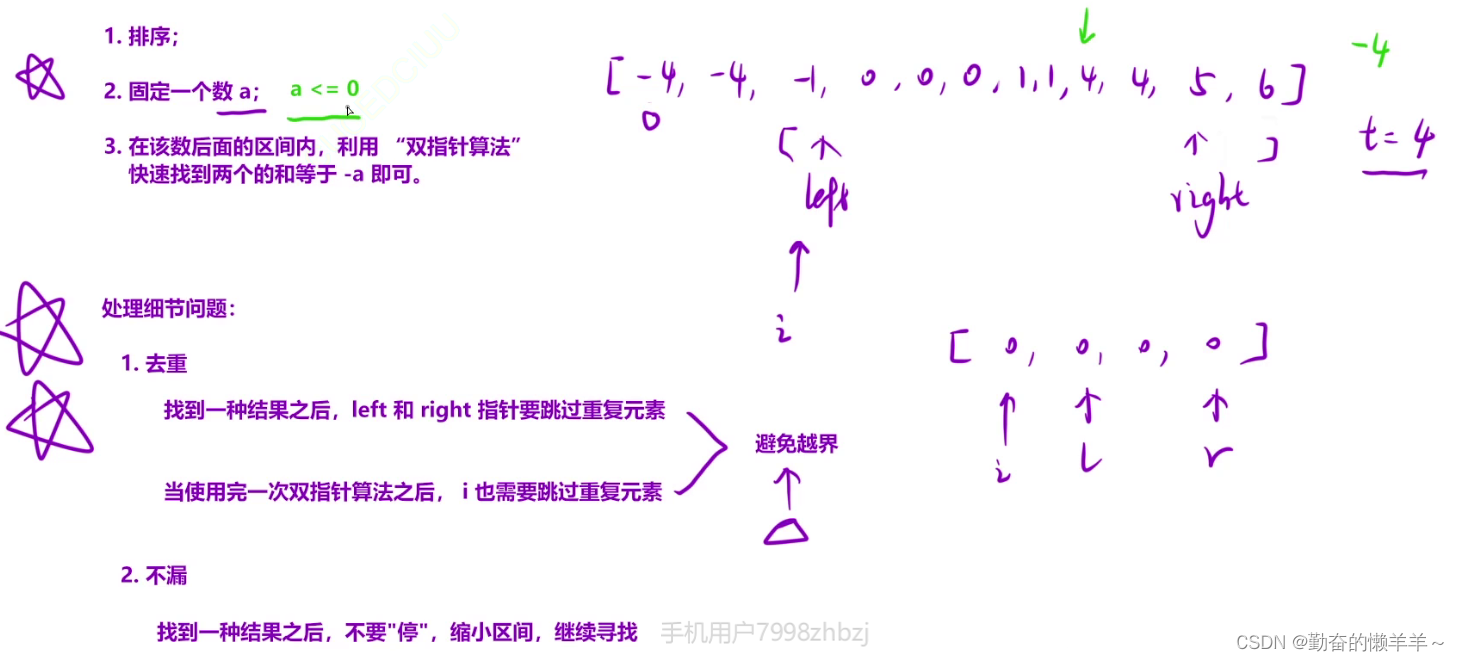

接口测试复习

一。基本概念 接口概念:系统与系统之间 数据交互的通道。 接⼝测试概念:校验 预期结果 与 实际结果 是否⼀致。 特征: 测试⻚⾯测试发现不了的问题。(因为:接⼝测试 绕过前端界⾯。 ) 符合质量控制前移理…...

获取医疗器械板块的个股列表

获取医疗器械板块的个股列表,用python爬虫做到(数据网址:板块 - 医疗器械概念 - 股票行情中心 - 搜狐证券) import requests from bs4 import BeautifulSoup # 获取医疗器械概念个股列表url "https://q.stock.sohu.com/cn/…...

1026 程序运行时间

要获得一个 C 语言程序的运行时间,常用的方法是调用头文件 time.h,其中提供了 clock() 函数,可以捕捉从程序开始运行到 clock() 被调用时所耗费的时间。这个时间单位是 clock tick,即“时钟打点”。同时还有一个常数 CLK_TCK&…...

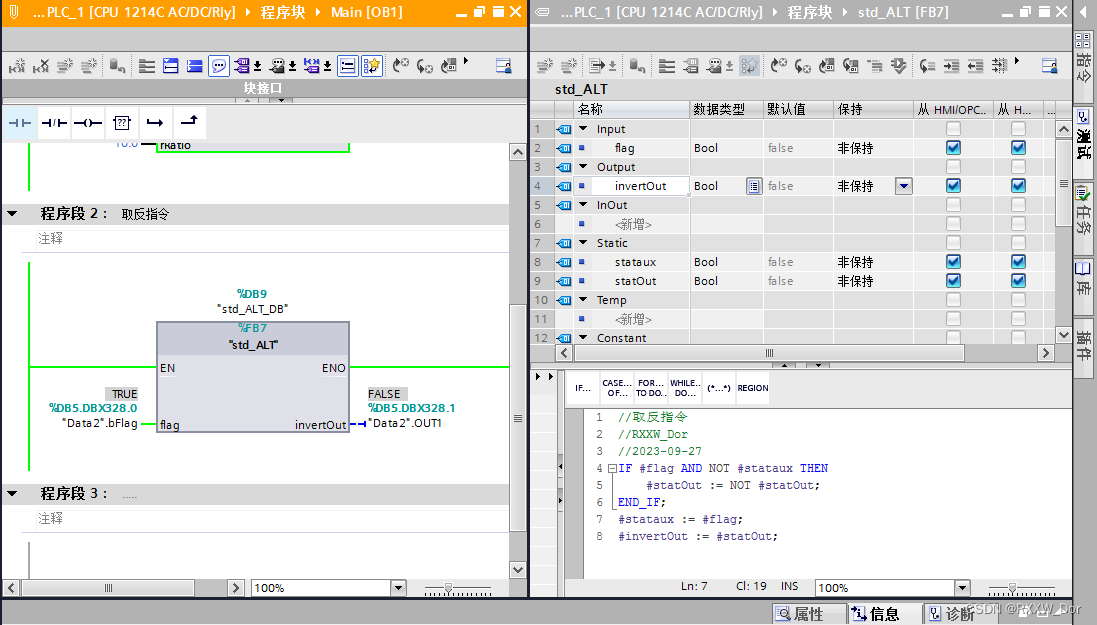

博途1200/1500 ALT指令

SMART PLC的ALT指令实现代码,请查看下面文章博客 SMART PLC如何构造ALT指令_smart200类似alt指令-CSDN博客单按钮启停这些老生常谈的问题,很多人感兴趣。这篇博文讨论下不同的实现方法,希望对大家有所帮助。指令虽然简单,但是在编程的时候合理使用对我们高效率编程帮助还是…...

11、视频分类建议

8、绩效看板与日清计划 9、大小屏分离与精细化审核 10、质量审核的设立与合并 视频分类印象深刻,因为这是我亲手做的第一个增效工具。 审核的其中一个任务是保证视频分类信息的准确性,账号本身是有一个缺省分类的,内容上传之后默认使用账号…...

【计算机组成原理】考研真题攻克与重点知识点剖析 - 第 2 篇:数据的表示和运算

前言 本文基础知识部分来自于b站:分享笔记的好人儿的思维导图与王道考研课程,感谢大佬的开源精神,习题来自老师划的重点以及考研真题。此前我尝试了完全使用Python或是结合大语言模型对考研真题进行数据清洗与可视化分析,本人技术…...

使用maven框架搭建一个IDEA插件项目

以下是使用 Maven 框架搭建 IDEA 插件项目的步骤: 打开 IDEA,点击 File -> New -> Project,选择 Maven。 在弹出的 New Project 窗口中,选择 Maven,然后选择 Create from archetype,找到 Maven 插件…...

第二届全国高校计算机技能竞赛——C++赛道 题解

Powered by:NEFU AB-IN Link 文章目录 第二届全国高校计算机技能竞赛——C赛道A 互不侵犯题意思路代码 B 奖学金题意思路代码 C 领导者题意思路代码 D 空调题意思路代码 E 字符操作变换题意思路代码 第二届全国高校计算机技能竞赛——C赛道 A 互不侵犯 题意 在象棋中ÿ…...

八大排序源码(含优化)

文章目录 1、直接插入排序2、希尔排序3、选择排序4、冒泡排序5、堆排序6、快速排序快速排序递归实现霍尔法挖坑法前后指针法快速排序小区间优化 快速排序非递归实现 7、归并排序归并排序递归实现归并排序非递归 8、计数排序 大家好,我是纪宁,这篇文章是关…...

)

ROS Melodic下,用Gazebo+ros_control搞定移动底盘+三轴机械臂的联合仿真(附避坑记录)

ROS Melodic下移动底盘与三轴机械臂的Gazebo联合仿真实战指南 当移动底盘遇上机械臂,问题总是比想象中多。上周深夜调试时,我的机械臂突然在Gazebo里表演起了"陀螺旋转",而底盘却纹丝不动——这恰恰是ros_control配置中一个PID参数…...

用Lingo搞定线性规划:一个工厂利润最大化的实例分析与代码逐行解读

用Lingo搞定线性规划:一个工厂利润最大化的实例分析与代码逐行解读 当工厂面临生产计划优化问题时,如何用数学工具找到最佳决策方案?Lingo作为专业的优化建模软件,能够将复杂的生产约束转化为可计算的数学模型。本文将以一个真实的…...

)

保姆级教程:在Ubuntu 20.04上用YOLOv5 v6.2训练你自己的COCO数据集(附完整数据准备流程)

在Ubuntu 20.04上从零构建YOLOv5 v6.2自定义训练环境的完整指南 当你想在本地工作站或云服务器上训练自己的目标检测模型时,YOLOv5无疑是最受欢迎的选择之一。但许多教程都假设你已经熟悉了Linux环境配置、数据集处理等前置知识,这让不少初学者在第一步…...

别再手动调参了!用Python+OpenCV玩转NCC立体匹配,手把手教你生成高质量视差图

PythonOpenCV实战:NCC立体匹配参数调优全指南 立体匹配是计算机视觉中获取深度信息的关键技术,而NCC(归一化互相关)作为经典的灰度匹配算法,在实际项目中既简单又实用。但很多开发者在使用时往往陷入手动调参的困境—…...

)

RT-Thread实战:小熊派上BH1750光照数据采集与MQTT上云完整流程(附源码)

小熊派BH1750光照监测系统开发全指南:从传感器到云端的数据链路构建 在物联网技术快速渗透各行各业的今天,环境监测设备的智能化改造已成为工业自动化、智慧农业和智能家居等领域的基础需求。本文将手把手带您完成一个典型的环境光照监测节点开发全流程…...

机械革命S2 Air/Code 01避坑指南:搞定WSL2和Docker,先搞定这3个驱动和BIOS

机械革命S2 Air/Code 01深度调优:WSL2与Docker稳定运行的三大核心策略 当机械革命S2 Air或Code 01遇上WSL2和Docker,不少技术爱好者会发现这条路并不平坦。蓝屏、WiFi断连、系统崩溃——这些看似随机的问题背后,其实隐藏着Windows系统版本、硬…...

CANN/GE动态输入Python构图示例

样例使用指导 【免费下载链接】ge GE(Graph Engine)是面向昇腾的图编译器和执行器,提供了计算图优化、多流并行、内存复用和模型下沉等技术手段,加速模型执行效率,减少模型内存占用。 GE 提供对 PyTorch、TensorFlow 前…...

面试题:模型评价指标全解析——准确率、精确率、召回率、F1、ROC、AUC、MAE、MSE、RMSE、R² 一文讲透

把“分类指标怎么看、回归指标怎么选、ROC/AUC 怎么判断模型好坏”一次讲清楚很多人在面试里被问到“模型评价指标有哪些”时,第一反应往往是背一串名词:准确率、精确率、召回率、F1、AUC、MAE、MSE、R。看似都答到了,实际上却很容易被继续追…...

FastbootEnhance:Windows平台终极Android刷机工具箱完整指南

FastbootEnhance:Windows平台终极Android刷机工具箱完整指南 【免费下载链接】FastbootEnhance A user-friendly Fastboot ToolBox & Payload Dumper for Windows 项目地址: https://gitcode.com/gh_mirrors/fa/FastbootEnhance 在Android设备刷机和定制…...

如何高效配置智能游戏助手:绝区零一条龙完整使用攻略

如何高效配置智能游戏助手:绝区零一条龙完整使用攻略 【免费下载链接】ZenlessZoneZero-OneDragon 绝区零 一条龙 | 全自动 | 自动闪避 | 自动每日 | 自动空洞 | 支持手柄 项目地址: https://gitcode.com/gh_mirrors/ze/ZenlessZoneZero-OneDragon 还在为《绝…...