FPGA实现HDMI输入转SDI视频输出,提供4套工程源码和技术支持

目录

- 1、前言

- 免责声明

- 2、我目前已有的SDI编解码方案

- 3、设计思路框架核模块解析

- 设计框图

- IT6802解码芯片配置及采集

- ADV7611解码芯片配置及采集

- silicon9011解码芯片配置及采集

- 纯verilog的HDMI 解码模块

- RGB888转YUV422

- SPMTE编码

- SDI模式

- 图像缓存

- SPMTE SDI

- GTX

- GV8500

- 4、vivado工程1-->IT6802采集SDI输出

- 5、vivado工程2-->ADV7611采集SDI输出

- 6、vivado工程3-->silicon9011采集SDI输出

- 7、vivado工程4-->HDMI RTL解码SDI输出

- 8、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 9、上板调试验证并演示

- 准备工作

- 输出演示

- 10、福利:工程代码的获取

FPGA实现HDMI输入转SDI视频输出,提供4套工程源码和技术支持

1、前言

FPGA实现SDI视频编解码目前有两种方案:

一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCRCB,GS2972发送器直接将并行的YCRCB编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA实现编解码,利用FPGA的GTP/GTX资源实现解串,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA水平要求较高。

没玩过SDI都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。本文使用Xilinx的Kintex7 FPGA实现HDMI转SDI视频输出;提供3套vivado2019.1版本的工程源码,4套工程的不同点在于输入HDMI视频解码方式的不同,以适应不同的FPGA开发板。第一套工程使用IT6802解码输入的HDMI视频,适应板载IT6802解码芯片的FPGA开发板;第二套工程使用ADV7611解码输入的HDMI视频,适应板载ADV7611解码芯片的FPGA开发板;第三套工程使用silicon9011解码输入的HDMI视频,适应板载silicon9011解码芯片的FPGA开发板;第四套工程使用纯verilog实现的HDMI解码模块解码输入的HDMI视频,适应没有板载HDMI解码芯片只有HDMI输入接口的FPGA开发板;四套工程列表如下:

_______________________________________________________________

|vivado工程 | 第一套工程 | 第二套工程 | 第三套工程 | 第四套工程 |

|vivado版本 | 2019.1 | 2019.1 | 2019.1 | 2019.1 |

|HDMI解码芯片 | IT6802 | ADV7611 |silicon9011| 无 |

|HDMI解码方式 | 硬件解码 | 硬件解码 | 硬件解码 | RTL模块解码 |

|输入视频 | HDMI | HDMI | HDMI | HDMI |

|HDMI解码后视频| RGB888 | RGB888 | RGB888 | RGB888 |

|输出视频 | SDI | SDI | SDI | SDI |

_______________________________________________________________

使用笔记本电脑模拟HDMI输入视频,分辨率为1920X1080@60Hz,FPGA首先用纯verilog实现的i2c控制器配置HDMI解码芯片(第四套工程除外),FPGA采集HDMI输入解码后的RGB888数据,经过RGB888转YUV422模块输出YUV422视频,再经过SPMTE编码模块将YUV422视频数据加上SDI数据帧头、帧尾以及控制信息等组成数据包,此时,原有的视频时序已经被打乱,需要将视频缓存致DDR3中,所以先将视频写入DDR3,然后读出送入Xilinx官方的SPMTE SDI IP核做SDI数据编码,同时需要输入SDI模式,该模块也包含在代码中,从SPMTE SDI IP核输出的已是标准SDI并行视频,最后调用GTX原语将SDI并行视频进行高速串行编码发送,为了保证数据的可靠性,在FPGA开发板需配套一颗GV8500以增强驱动,当然换其他IC也可以做到,最后通过板载的BNC接口将SDI视频发送出去。

本文详细描述了FPGA实现HDMI转SDI视频输出的实现设计方案,工程代码编译通过后上板调试验证,文章末尾有演示视频,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

关于SDI的理论知识部分,可自行搜索一下,很多大佬讲得很详细,也可以参考我之前写的文章点击查看:SDI理论

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、我目前已有的SDI编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;专栏地址链接:点击直接前往

3、设计思路框架核模块解析

提供3套vivado2019.1版本的工程源码,4套工程的不同点在于输入HDMI视频解码方式的不同,以适应不同的FPGA开发板。第一套工程使用IT6802解码输入的HDMI视频,适应板载IT6802解码芯片的FPGA开发板;第二套工程使用ADV7611解码输入的HDMI视频,适应板载ADV7611解码芯片的FPGA开发板;第三套工程使用silicon9011解码输入的HDMI视频,适应板载silicon9011解码芯片的FPGA开发板;第四套工程使用纯verilog实现的HDMI解码模块解码输入的HDMI视频,适应没有板载HDMI解码芯片只有HDMI输入接口的FPGA开发板;四套工程列表如下:

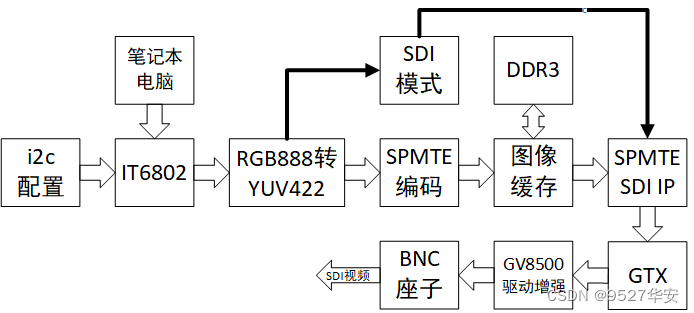

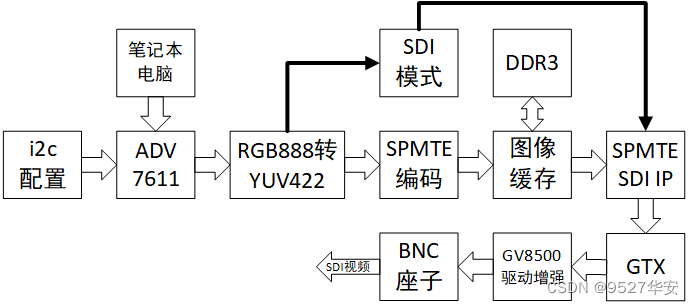

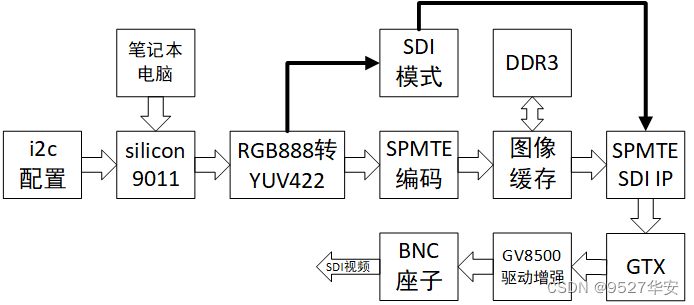

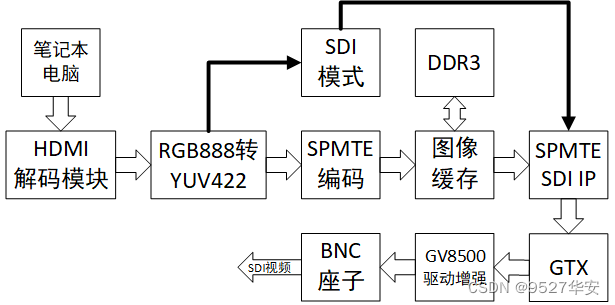

设计框图

第一套工程设计框架如下:

第二套工程设计框架如下:

第三套工程设计框架如下:

第四套工程设计框架如下:

IT6802解码芯片配置及采集

第一套工程使用IT6802解码输入的HDMI视频,适应板载IT6802解码芯片的FPGA开发板;IT6802解码芯片需要i2c配置才能使用,关于IT6802解码芯片的配置和使用,请参考我往期的博客,博客地址:点击直接前往

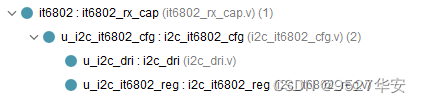

IT6802解码芯片配置及采集这两部分均用verilog代码模块实现,代码中配置为1920x1080分辨率;代码位置如下:

ADV7611解码芯片配置及采集

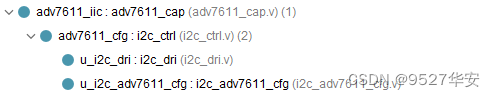

第二套工程使用ADV7611解码输入的HDMI视频,适应板载ADV7611解码芯片的FPGA开发板;ADV7611解码芯片需要i2c配置才能使用,ADV7611解码芯片配置及采集这两部分均用verilog代码模块实现,代码中配置为1920x1080分辨率;代码位置如下:

silicon9011解码芯片配置及采集

第三套工程使用silicon9011解码输入的HDMI视频,适应板载silicon9011解码芯片的FPGA开发板;silicon9011解码芯片需要i2c配置才能使用,关于silicon9011解码芯片的配置和使用,请参考我往期的博客,博客地址:点击直接前往

silicon9011解码芯片配置及采集这两部分均用verilog代码模块实现,代码位置如下:

纯verilog的HDMI 解码模块

第四套工程使用纯verilog实现的HDMI解码模块解码输入的HDMI视频,适应没有板载HDMI解码芯片只有HDMI输入接口的FPGA开发板;模块输入为差分HDMI视频,输出为RGB888的VGA视频,并伴随解码的像素时钟、行同步信号、场同步信号以及数据有效信号;此外,该模块还有配套的EDID模块,负责和输入源协商视频分辨率等基本信息,通过i2c接口与外接通信,IDED信息是固定的十六进制文件,例化了ROM用来存储,上电自动加载;该模块最高只支持1920x1080@60Hz分辨率的输入视频解码,更高的2K、4K暂不支持;代码位置如下:

RGB888转YUV422

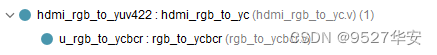

这个模块很简单, RGB888进YUV422出,十几行代码的事儿,不必多讲,采用纯verilog代码实现,代码位置如下:

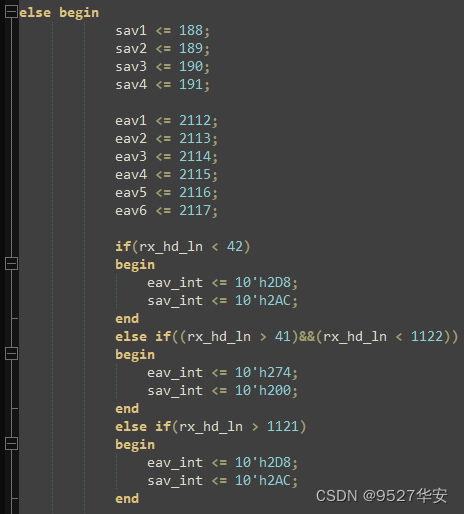

SPMTE编码

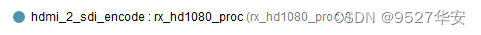

SPMTE编码模块将YUV422视频数据加上SDI数据帧头、帧尾以及控制信息等组成数据包,此时,原有的视频时序已经被打乱,代码位置和核心代码部分如下:

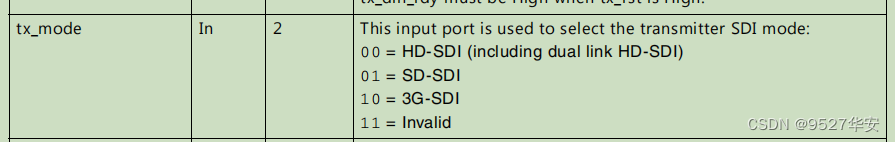

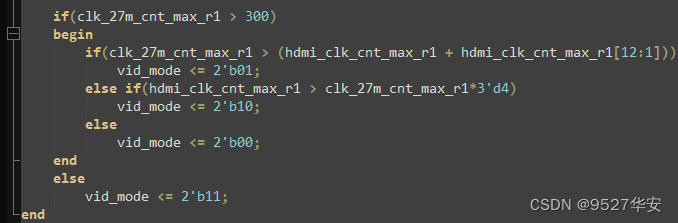

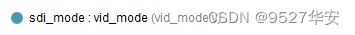

SDI模式

这个模块根据输入的HDMI视频分辨率来选择不同的SDI模式,这个信号会给到后面的Xilinx官方的SPMTE SDI IP核使用,根据Xilinx官方手册,SDI发送模式如下:

代码中体现如下:

代码位置如下:

图像缓存

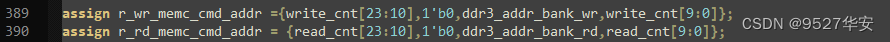

由于原有的输入视频时序已经被打乱,所以输入图像必须经DDR缓存,调用Xilinx官方的MIG 核FIFO IP核,将DDR的用户接口封装为FIFO读写模式,方便用户使用,将图像缓存进DDR3中做4帧缓存,如果你觉得延时太高了,可以改为缓存2帧,DDR3地址读写部分如下:

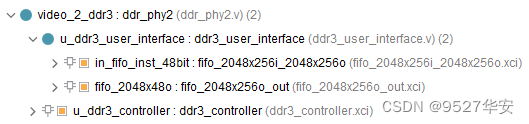

图像缓存代码位置如下:

SPMTE SDI

调用Xilinx官方的SPMTE SDI IP核做SDI数据编码,同时需要输入SDI模式,该模块也包含在代码中,从SPMTE SDI IP核输出的已是标准SDI并行视频,SPMTE SDI IP是Xilinx提供的专门用于SDI视频编解码的IP,可以免费试用,这里调用该IP,并添加了一些用户代码,代码位置如下:

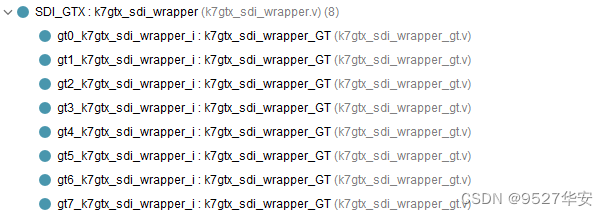

GTX

调用GTX原语将SDI并行视频进行高速串行编码发送,为了达到GTX变速的目的,这里没有调用GTX IP,而是直接调用其原语实现,需要读者对GTX有较深的理解,代码位置如下:

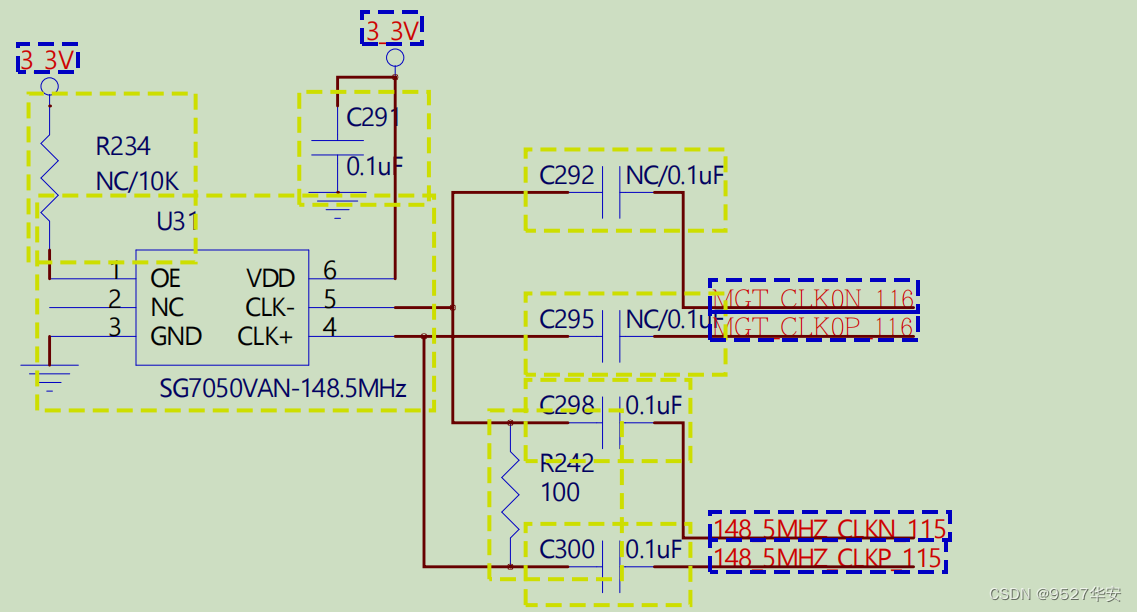

这里对GTX的时钟有严格要求,必须使用一对148.5 MHz和一对148.35 MHz的时钟作为参考时钟,否则运行不了SDI视频解码;原理图如下:

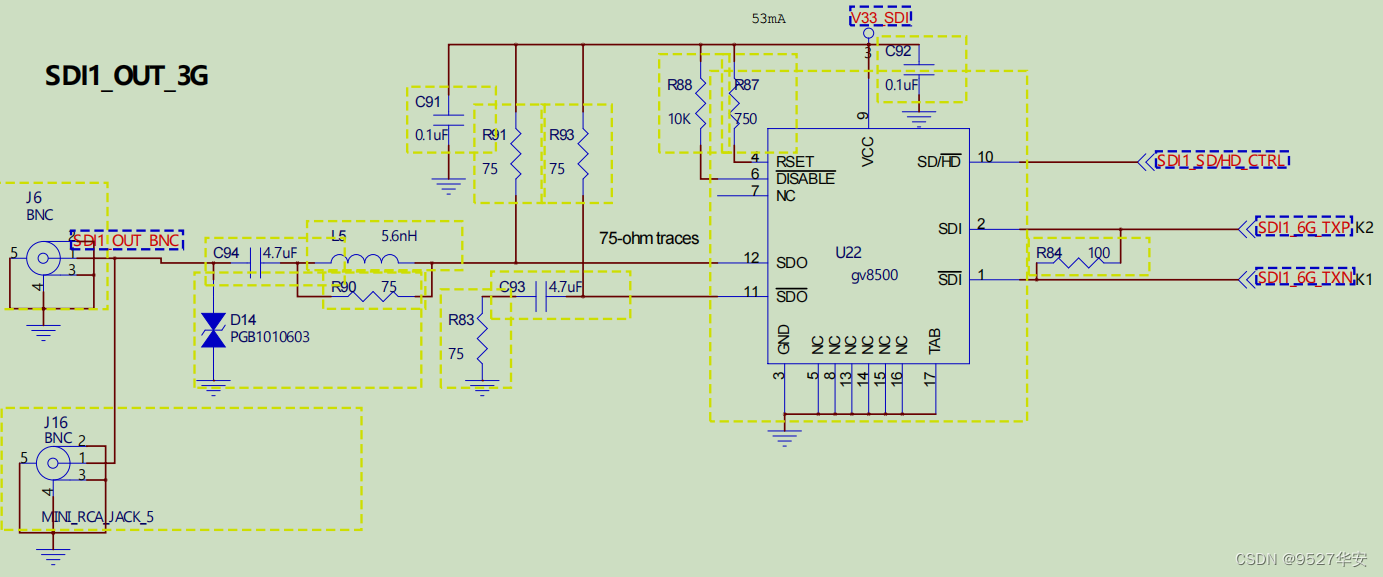

GV8500

为了保证数据的可靠性,在FPGA开发板需配套一颗GV8500以增强驱动,当然换其他IC也可以做到,最后通过板载的BNC接口将SDI视频发送出去。原理图如下:

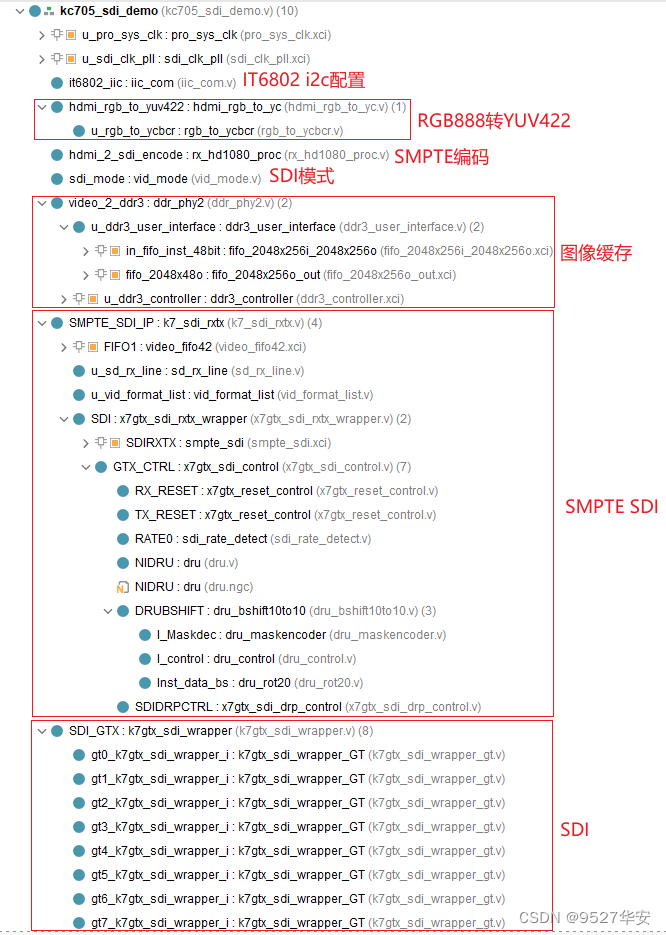

4、vivado工程1–>IT6802采集SDI输出

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:笔记本电脑输出模拟HDMI视频输入,分辨率1920x1080@60Hz,IT6802解码;

输出:SDI;

应用:FPGA实现HDMI转SDI视频输出

工程代码架构如下:

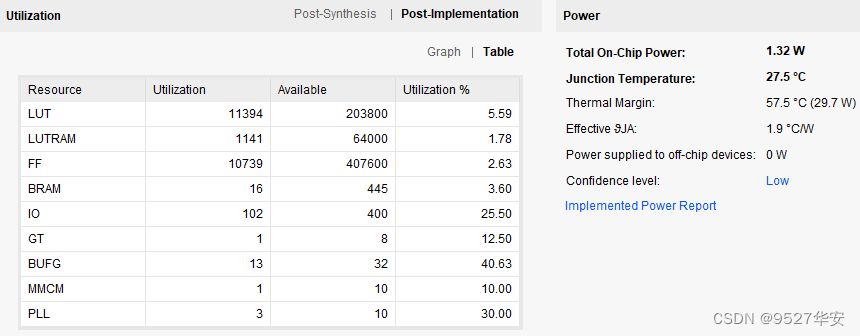

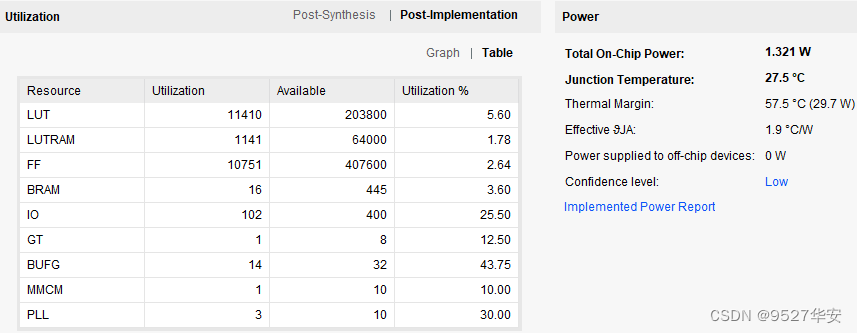

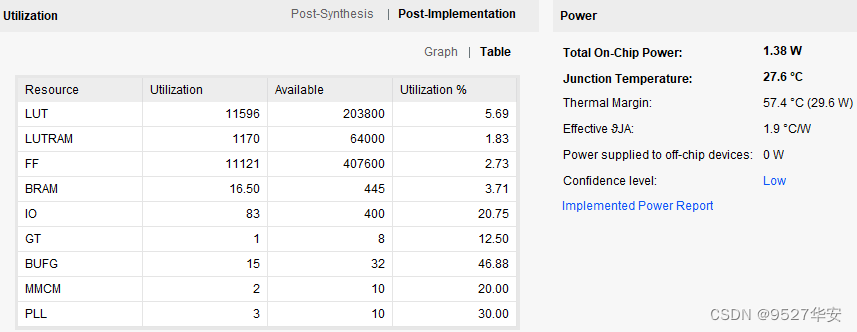

综合编译完成后的FPGA资源消耗和功耗预估如下:

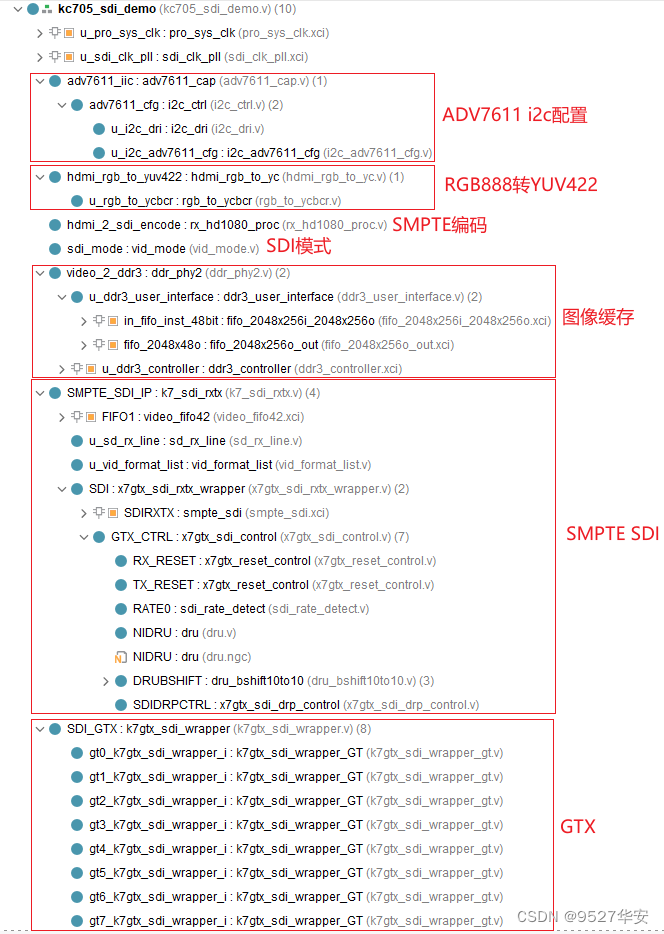

5、vivado工程2–>ADV7611采集SDI输出

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:笔记本电脑输出模拟HDMI视频输入,分辨率1920x1080@60Hz,ADV7611解码;

输出:SDI;

应用:FPGA实现HDMI转SDI视频输出

工程代码架构如下:

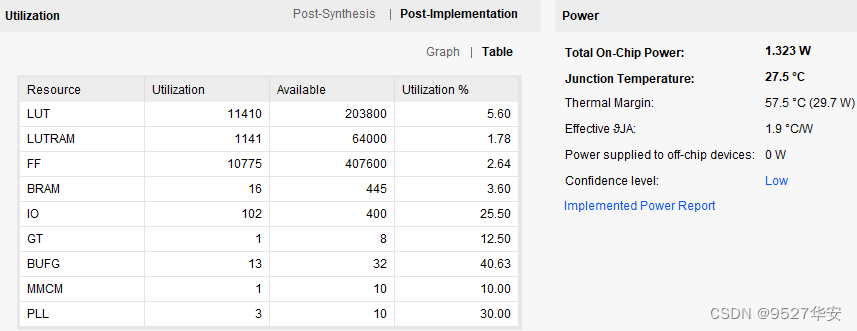

综合编译完成后的FPGA资源消耗和功耗预估如下:

6、vivado工程3–>silicon9011采集SDI输出

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:笔记本电脑输出模拟HDMI视频输入,分辨率1920x1080@60Hz,silicon9011解码;

输出:SDI;

应用:FPGA实现HDMI转SDI视频输出

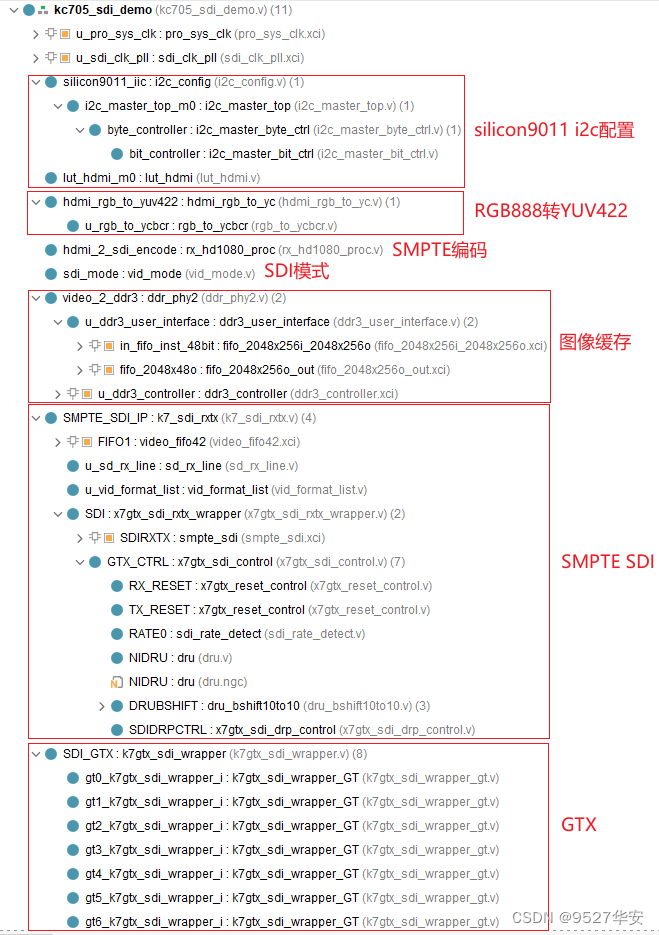

工程代码架构如下:

综合编译完成后的FPGA资源消耗和功耗预估如下:

7、vivado工程4–>HDMI RTL解码SDI输出

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:笔记本电脑输出模拟HDMI视频输入,分辨率1920x1080@60Hz,HDMI RTL模块解码;

输出:SDI;

应用:FPGA实现HDMI转SDI视频输出

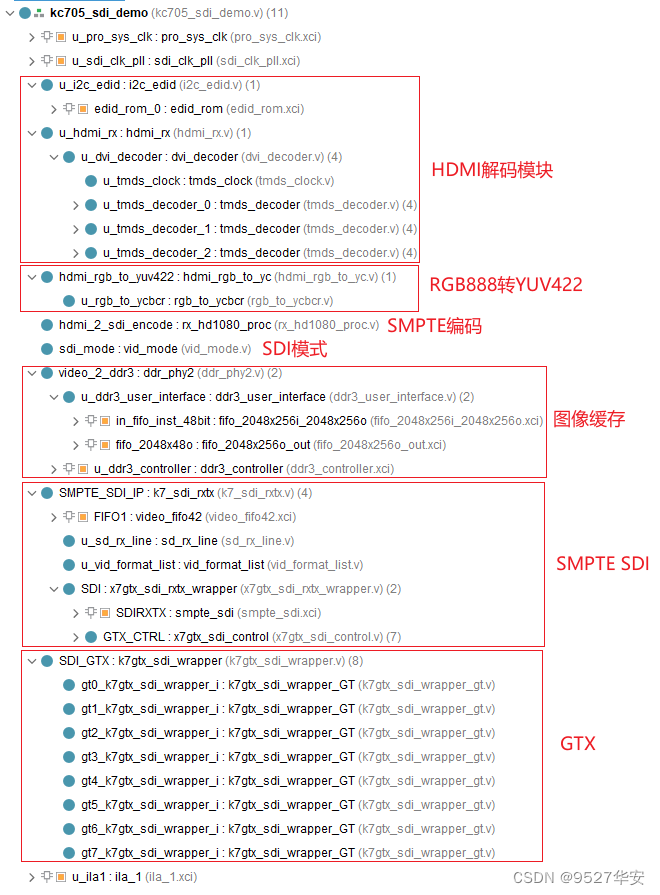

工程代码架构如下:

综合编译完成后的FPGA资源消耗和功耗预估如下:

8、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

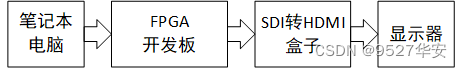

9、上板调试验证并演示

准备工作

你需要有以下装备才能移植并测试该工程代码:

1:笔记本电脑

2:FPGA开发板;

3:板载的HDMI输入接口和SDI输出接口;

4:SDI转HDMI盒子;

5:HDMI显示,要求分辨率支持1920x1080;

测试平台框图如下:

我用的SDI转HDMI盒子如下,某宝有卖:

输出演示

输出演示如下:

10、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA实现HDMI输入转SDI视频输出,提供4套工程源码和技术支持

目录 1、前言免责声明 2、我目前已有的SDI编解码方案3、设计思路框架核模块解析设计框图IT6802解码芯片配置及采集ADV7611解码芯片配置及采集silicon9011解码芯片配置及采集纯verilog的HDMI 解码模块RGB888转YUV422SPMTE编码SDI模式图像缓存SPMTE SDIGTXGV8500 4、vivado工程1-…...

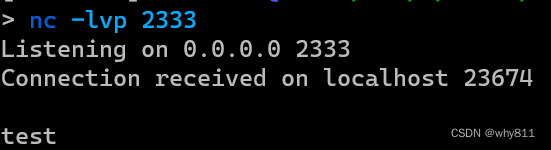

针对FTP的SSRF攻击

前言 ssrf中常用的协议有http,gopher等。但http协议在ssrf中的用处也仅限于访问内网页面,在可以crlf的情况下才有可能扩大攻击范围。gopher协议比较特殊,在部分环境下支持此协议,如:curl。但还有一些环境就不支持了&a…...

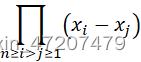

线性代数中涉及到的matlab命令-第一章:行列式

目录 1,逆序数 2,行列式定义和性质 2.1,常用特性及命令 2.2,求行列式 2.3,行列式的性质 2,行列式按行(列)展开 3,范德蒙德行列式 在学习线性代数过程中&#…...

QT编程,QT内存管理、信号与槽、

目录 一、QT工具 二、QT内存管理 三、信号与槽 1、信号与槽特点 2、信号 3、槽函数 4、连接 5、发送信号 6、取消连接 一、QT工具 1、Qt Designer:界面设计编辑工具 2、Qt Assistant: Qt技术文档浏览器 3、Qt Linguist: 国际化语言翻译工具 4、…...

springcloud之项目实战环境准备

写在前面 为了更好的学习springcloud,我们来一起开发一个实战项目,加深理解。 1:项目介绍 在开始项目实战之前先来做一个整体的项目介绍,从而能够让对项目的整体架构和模板有一个比较清晰的认知。 大家都知道双11,…...

Linux 部署 MinIO 分布式对象存储 配置为 typora 图床

前言 MinIO 是一款高性能的对象存储系统,它可以用于大规模的 AI/ML、数据湖和数据库工作负载。它的 API 与Amazon S3 云存储服务完全兼容,可以在任何云或本地基础设施上运行。MinIO 是开源软件,也提供商业许可和支持 MinIO 的特点有&#x…...

)

JVM Optimization Learning(四)

目录 一、调优 1、基础概念 2、什么是调优? 3、调优,从规划开始 4、调优案例 一、调优 1、基础概念 吞吐量:用户代码执行时间 /(用户代码执行时间 垃圾回收时间) 响应时间:STW越短,响应…...

新华三辅导笔记 2023/10/9-2023/10/13

新华三辅导笔记 一、需要用到的软件二、计算机网络概述1、计算机网络的定义和基本功能(1)什么是计算机网络(2)计算机网络的基本功能 2、(1)局域网、城域网和广域网(范围划分)&#x…...

边坡安全监测系统的功能优势

随着科技的进步,边坡安全监测系统在各种工程项目中发挥着越来越重要的作用。这款系统通过实时监测垂直、水平位移数据,以折线图的方式显示在监控平台中,为工程人员提供了直观、便捷的监控工具,从而能够及时掌握边坡稳定状况&#…...

【架构】研发高可用架构和系统设计经验

研发高可用架构和系统设计经验 从研发规范层面、应用服务层面、存储层面、产品层面、运维部署层面、异常应急层面这六大层面去剖析一个高可用的系统需要有哪些关键的设计和考虑。 一、高可用架构和系统设计思想 1.可用性和高可用概念 可用性是一个可以量化的指标,计算的公…...

Linux线程安全

线程安全 Linux线程互斥进程线程间的互斥相关背景概念互斥量mutex互斥量的接口互斥量实现原理探究 可重入VS线程安全概念常见的线程不安全的情况常见的线程安全的情况常见的不可重入的情况常见的可重入的情况可重入与线程安全联系可重入与线程安全区别 常见锁概念死锁死锁的四个…...

Windows安装Node.js

1、Node.js介绍 ①、Node.js简介 Node.js是一个开源的、跨平台的JavaScript运行环境,它允许开发者使用JavaScript语言来构建高性能的网络应用程序和服务器端应用。Node.js的核心特点包括: 1. 事件驱动: Node.js采用了事件驱动的编程模型,通…...

想要开发一款游戏, 需要注意什么?

开发一款游戏是一个复杂而令人兴奋的过程。游戏开发是指创建、设计、制作和发布电子游戏的过程。它涵盖了从最初的概念和创意阶段到最终的游戏发布和维护阶段的各个方面。 以下是一些需要注意的关键事项: 游戏概念和目标: 确定游戏开发的核心概念和目标…...

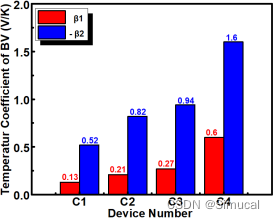

横向AlGaN/GaN基SBD结构及物理模型数据库的开发

GaN基功率器件凭借其临界电场高、电子饱和漂移速度大、热导率高等优良性能在大功率快充、充电桩、新能源汽车等领域具备广泛应用空间。为进一步助推半导体高频、高功率微电子器件的发展进程,天津赛米卡尔科技有限公司技术团队依托先进的半导体TCAD仿真平台成功开发出…...

使用安卓Termux+Hexo,手机也能轻松搭建个人博客网站

文章目录 前言1.安装 Hexo2.安装cpolar3.远程访问4.固定公网地址5.结语 前言 Hexo 是一个用 Nodejs 编写的快速、简洁且高效的博客框架。Hexo 使用 Markdown 解析文章,在几秒内,即可利用靓丽的主题生成静态网页。 下面介绍在Termux中安装个人hexo博客并…...

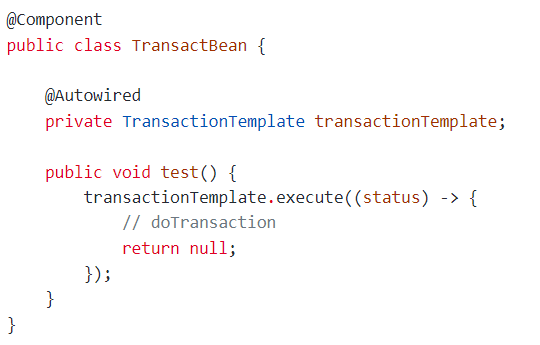

Spring在业务中常见的使用方式

目录 通过IOC实现策略模式 通过AOP实现拦截 通过Event异步解耦 通过Spring管理事务 通过IOC实现策略模式 很多时候,我们需要对不同的场景进行不同的业务逻辑处理举个例子,譬如不同的场景需要不同支付方式,普通的逻辑是使用if-else&#x…...

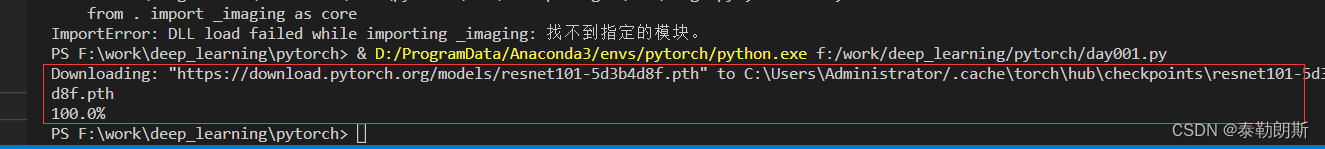

PyTorch 深度学习实战

文章目录 前言1. 环境安装1.Anaconda2.pytorch cuda 环境3.测试 前言 1. 环境安装 1.Anaconda 可以参考这里:Anaconda学习 2.pytorch cuda 环境 我是按照下面的博客一步步完成,亲测有效 Pytorch安装教程(最全最详细版) 我的…...

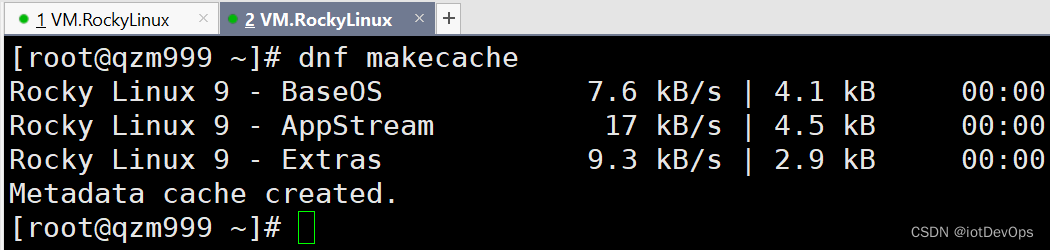

学生用RockyLinux9.2模板虚拟机说明

“RockyLinux9.2”模板虚拟机下载地址 链接:https://pan.baidu.com/s/1xcakszIQ7Kp9Nw_NA9Znlg?pwdqzmm 提取码:qzmm 1.模板机是基于“Rocky-9.2-x86_64-minimal.iso”安装 2.模板机是2023.10.10执行dnf update && dnf upgrade更新和升级软件…...

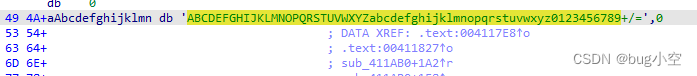

BUUCTF reverse3 1

先运行下 看来是输入正确的flag 使用DIE查看文件 看起来没有壳,直接IDA打开 shift F12查找字符串 一路跟踪 到汇编窗口后F5 这里对Destination和Str2进行比较,Str2有值那么Str2就是经过上面一系列处理之后得到的内容了 继续分析上面的代码 根据…...

关于webWorker未解问题

今天尝试学习webworker,尝试在vue3项目里面使用 使用的就是常规方法,使用worker-loader,加上在vue.config.js内部添加配置 使用完发现问题 如图所见,该worker仅仅配置点击后传输字符串"1",并在worker内部打印,发现打印不出来 但是仅仅只是将引入的文件换个名字 …...

Mac运行CORE Keygen受阻?巧用UPX与brew轻松解包

1. 当Mac遇到CORE Keygen无法运行时该怎么办? 最近有不少朋友在Mac上运行CORE Keygen时遇到了问题,双击应用图标后要么毫无反应,要么直接弹出"无法打开"的提示。这种情况其实很常见,特别是对于一些特殊用途的应用程序。…...

Gitee领跑本土化开发体验:深度解析国内代码托管平台的选择之道

在数字化转型浪潮中,代码托管平台已成为开发者团队不可或缺的基础设施。国内市场经过多年发展,已经从单一的海外平台依赖,逐步形成了多元化的平台选择生态。其中,Gitee凭借其本土化优势脱颖而出,成为众多国内开发团队的…...

支付宝沙箱环境:从零搭建支付测试与调试实战

1. 支付宝沙箱环境入门指南 第一次接触支付宝开放平台的开发者,往往会对支付功能的对接感到头疼。别担心,支付宝沙箱环境就是专为解决这个问题而生的。简单来说,这是一个完全模拟真实支付流程的测试环境,让你可以在不花一分钱的情…...

)

Mac小白必看:手把手教你用终端命令重建丢失的Recovery HD分区(附详细路径解释)

Mac用户自救指南:彻底掌握Recovery HD分区修复全流程 当你发现CommandR组合键失效时,那种无助感我深有体会。去年帮朋友修复一台二手MacBook时,我们花了整整一个下午才搞明白为什么恢复模式无法启动——原来前主人为了腾出空间删除了Recovery…...

高速PCB设计中串扰的成因、影响与实战控制策略

1. 项目概述:高速硬件设计中的“隐形杀手”干了十几年硬件设计,从当年画双面板、用万用表调通就行的年代,一路做到现在动辄几十层、信号速率奔着几十Gbps去的复杂系统,感触最深的一点就是:很多问题,以前可以…...

QtUnblockNeteaseMusic终极指南:跨平台音乐解锁工具的技术实现与应用

QtUnblockNeteaseMusic终极指南:跨平台音乐解锁工具的技术实现与应用 【免费下载链接】QtUnblockNeteaseMusic A desktop client for UnblockNeteaseMusic, made with Qt. 项目地址: https://gitcode.com/gh_mirrors/qt/QtUnblockNeteaseMusic 在数字音乐流媒…...

WeatherBench终极指南:快速构建天气预报AI模型的完整基准平台

WeatherBench终极指南:快速构建天气预报AI模型的完整基准平台 【免费下载链接】WeatherBench A benchmark dataset for data-driven weather forecasting 项目地址: https://gitcode.com/gh_mirrors/we/WeatherBench WeatherBench是一个专为数据驱动天气预报…...

iOS 18.2 Siri大模型升级:从命令响应到意图理解的混合智能架构解析

1. 项目概述:当Siri遇上ChatGPT,一次迟来的“大脑移植”作为一名长期关注移动操作系统与AI交互的从业者,我几乎第一时间就刷到了iOS 18.2 Beta 1的更新包。这次更新的标题——“Siri接入ChatGPT技术”——简单直接,却足以在圈内掀…...

GEE入门实战:从云端概念到首个遥感分析

1. 初识Google Earth Engine(GEE) 第一次接触GEE时,我完全被它的云端处理能力震撼到了。想象一下,你不需要在本地安装任何软件,打开浏览器就能调用PB级别的遥感数据,还能直接在上面跑分析——这简直就是遥感…...

RePKG终极指南:解锁Wallpaper Engine资源包的专业工具

RePKG终极指南:解锁Wallpaper Engine资源包的专业工具 【免费下载链接】repkg Wallpaper engine PKG extractor/TEX to image converter 项目地址: https://gitcode.com/gh_mirrors/re/repkg 你是否曾经对Wallpaper Engine中精美的动态壁纸感到好奇ÿ…...