北邮22级信通院数电:Verilog-FPGA(4)第三周实验:按键消抖、呼吸灯、流水灯 操作流程注意事项

北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

目录

一.注意事项

二.按键消抖

2.1 LED_debounce代码

2.2debounce.v代码

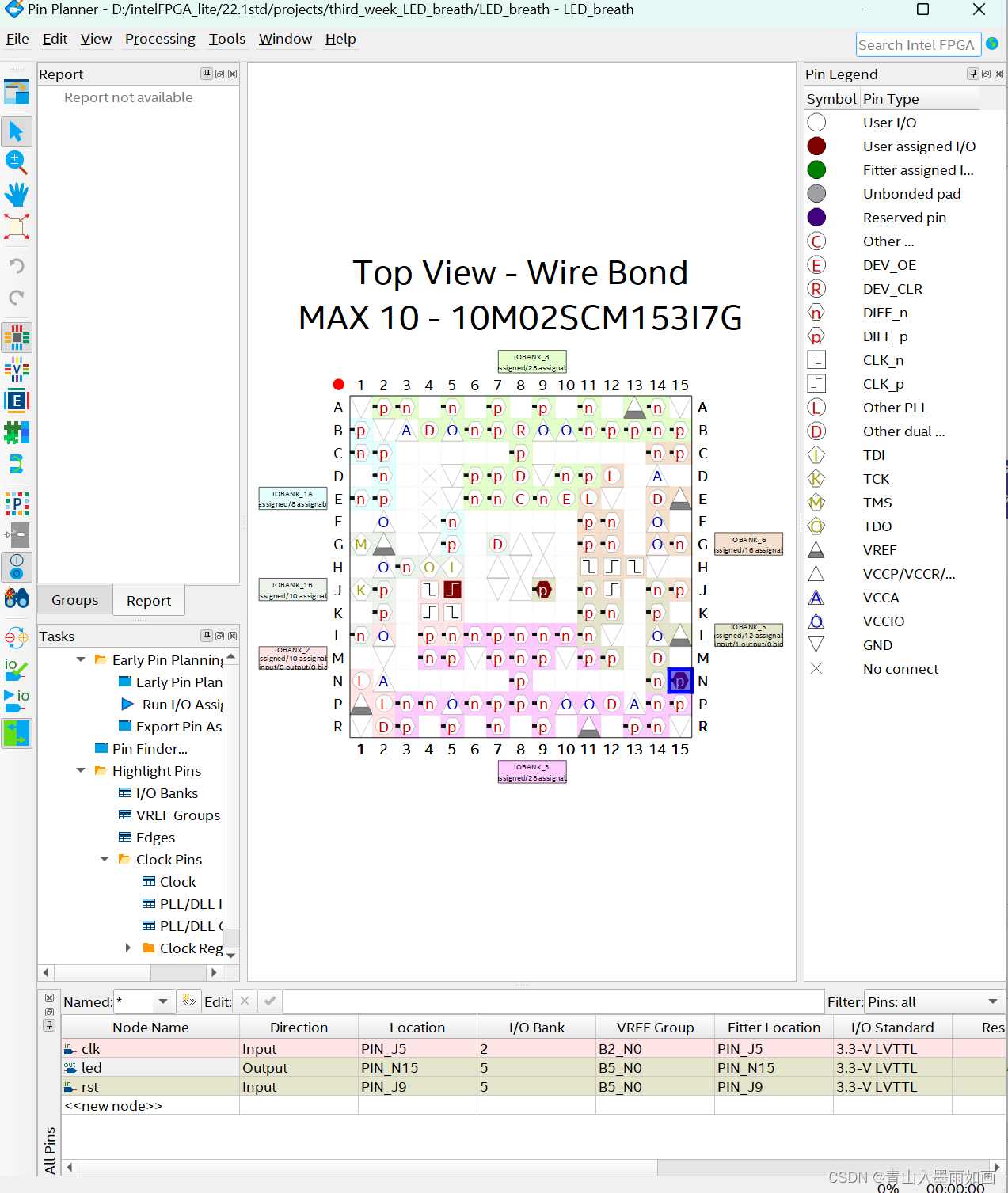

2.3管脚分配

三.流水灯

3.1 LED_flash.v代码

3.2 divide.v代码

3.3decode38.v代码

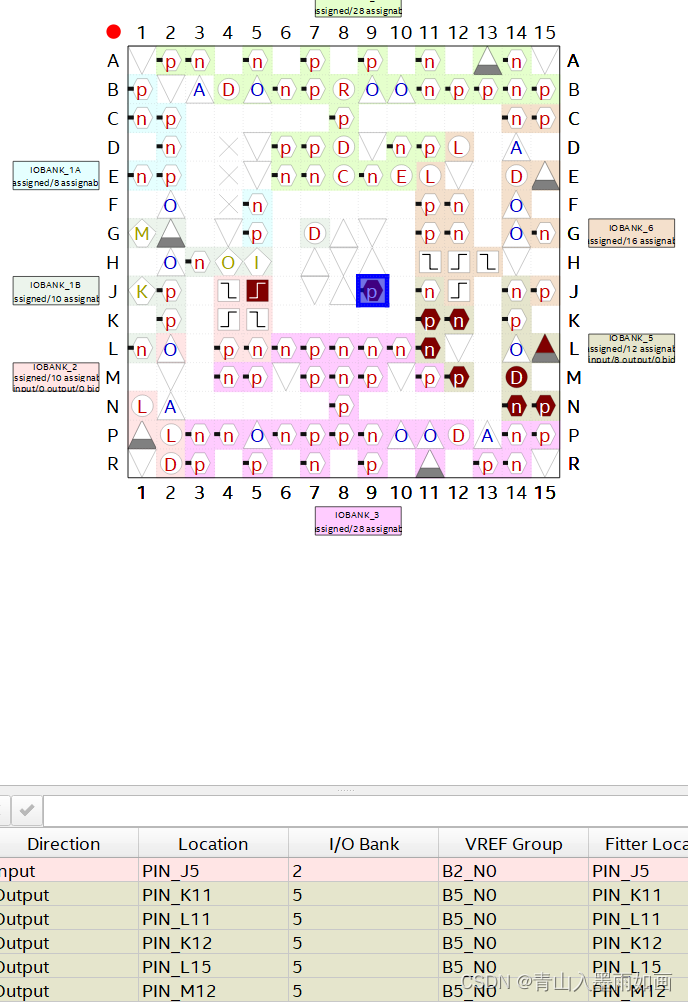

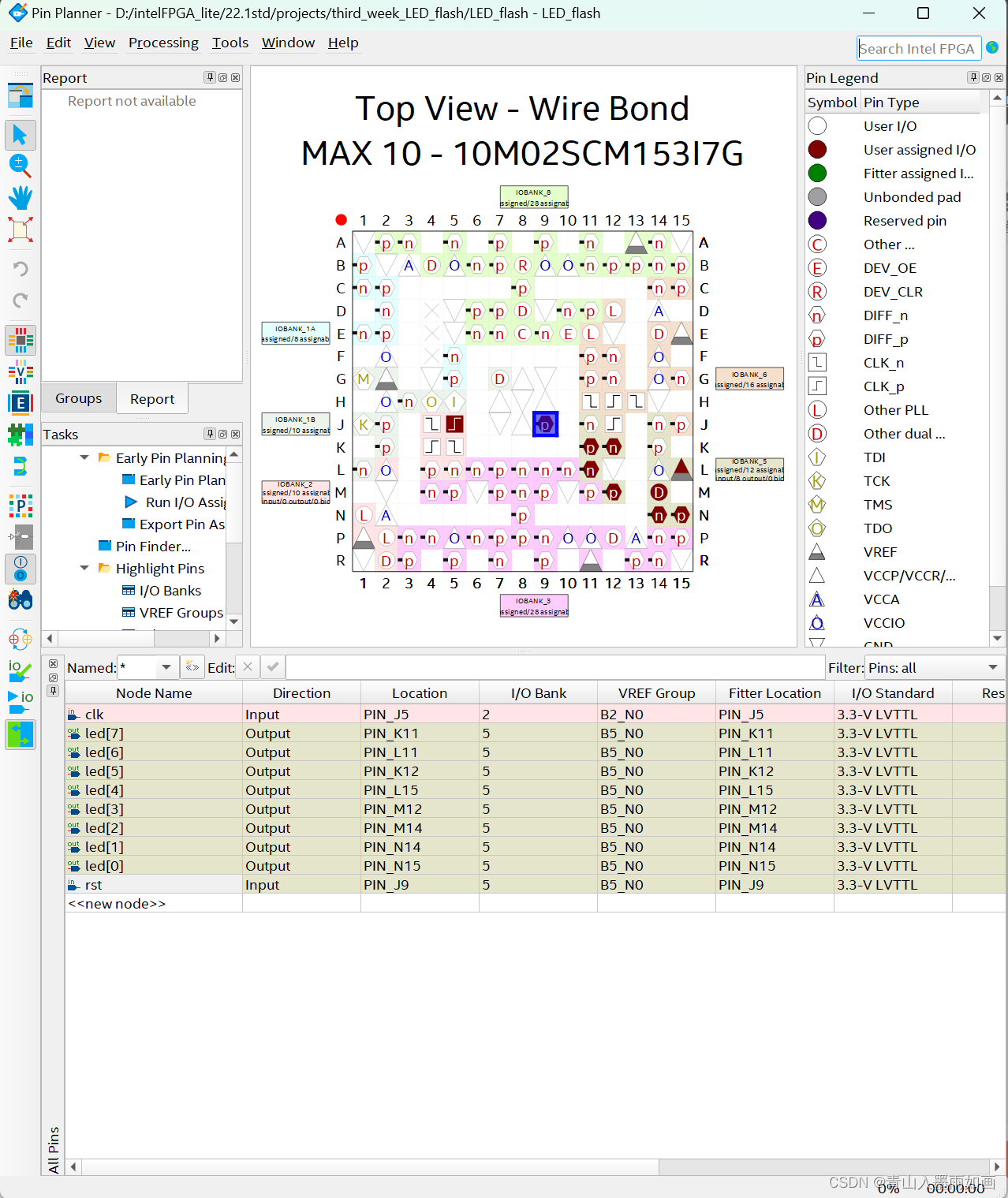

3.4管脚分配

四.呼吸灯

4.1 LED_breath.v代码

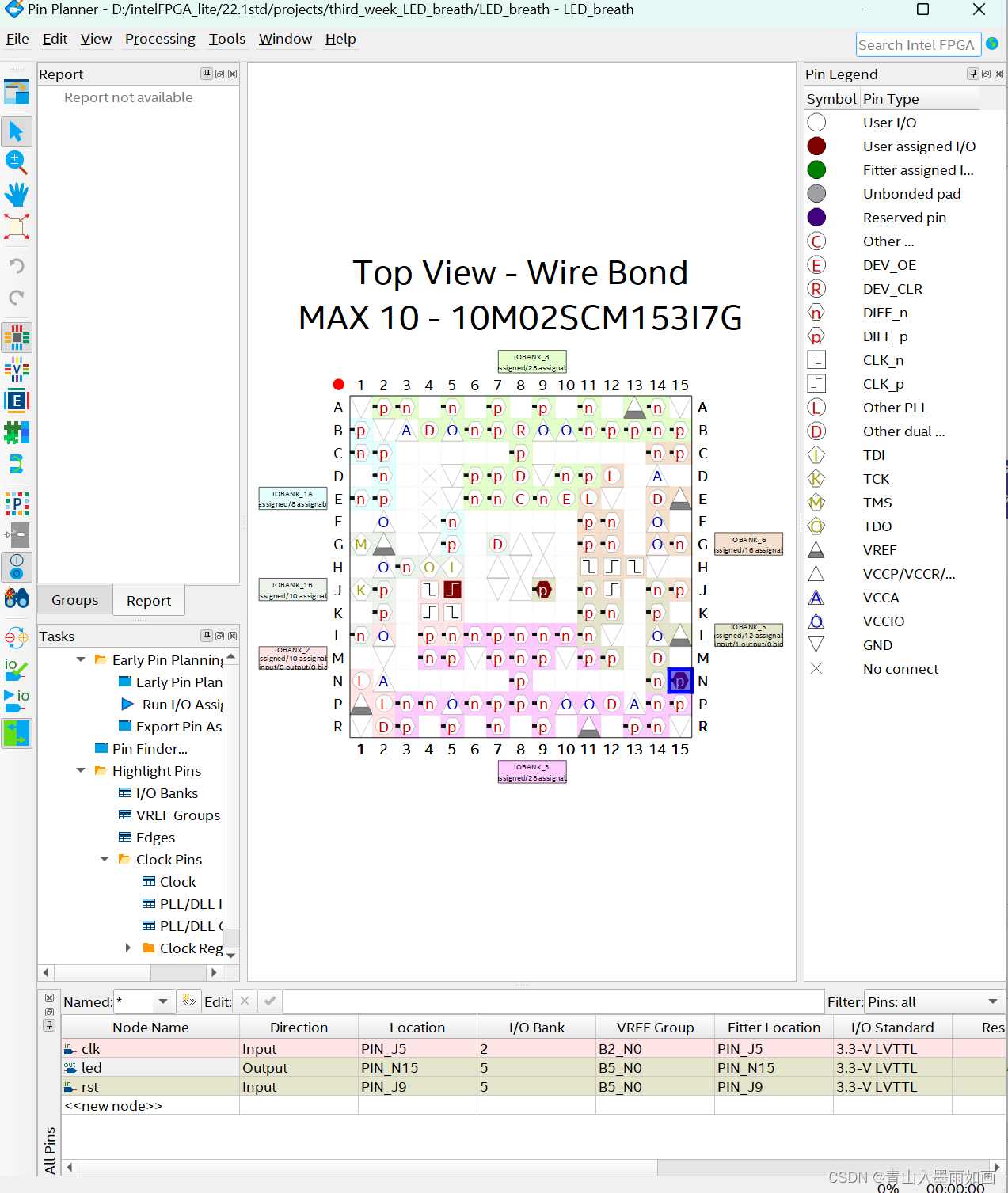

4.2管脚分配

一.注意事项

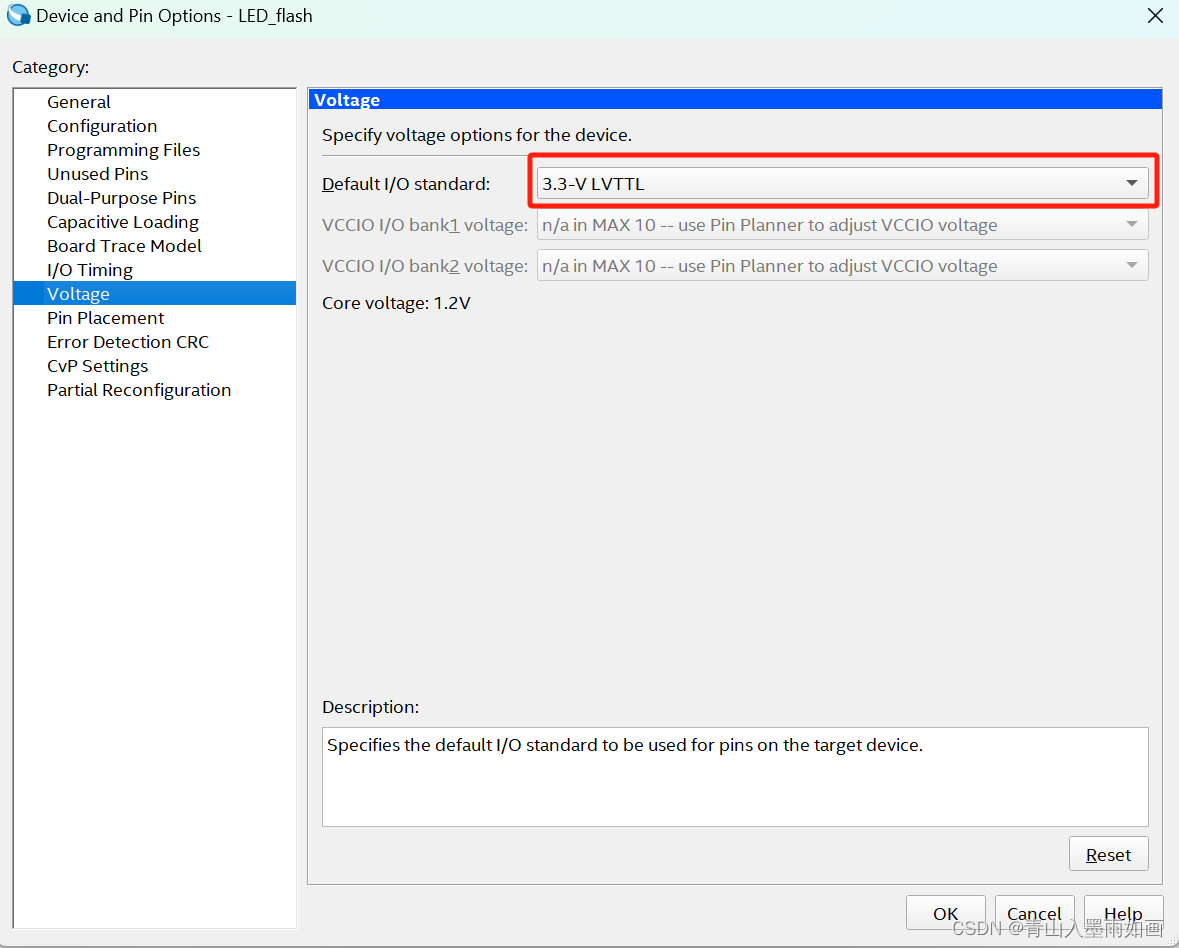

烧录之前首先检查这几个参数是否调整完毕:

没调的赶紧去调!!!

二.按键消抖

2.1 LED_debounce代码

module LED_debounce (clk,rst,key,led);input clk;input rst;input key; output reg led; wire key_pulse;//当按键按下时产生一个高脉冲,翻转一次ledalways @(posedge clk or negedge rst)beginif (!rst) led <= 1'b1;else if (key_pulse)led <= ~led;elseled <= led;end //例化消抖module,这里没有传递参数N,采用了默认的N=1 debounce u1 ( .clk (clk),.rst (rst),.key (key),.key_pulse (key_pulse));endmodule2.2debounce.v代码

module debounce (clk,rst,key,key_pulse);parameter N = 1; //要消除的按键的数量input clk;input rst;input [N-1:0] key; //输入的按键 output [N-1:0] key_pulse; //按键动作产生的脉冲 reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中always @(posedge clk or negedge rst)beginif (!rst) beginkey_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1key_rst_pre <= {N{1'b1}};endelse beginkey_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,//同时key_rst的值赋给key_rst_prekey_rst_pre <= key_rst; //非阻塞赋值。//相当于经过两个时钟触发,//key_rst存储的是当前时刻key的值,//key_rst_pre存储的是前一个时钟的key的值end endassign key_edge = key_rst_pre & (~key_rst);//脉冲边沿检测。//当key检测到下降沿时,//key_edge产生一个时钟周期的高电平reg [17:0] cnt; //产生延时所用的计数器,系统时钟12MHz,//要延时20ms左右时间,至少需要18位计数器 //产生20ms延时,当检测到key_edge有效是计数器清零开始计数always @(posedge clk or negedge rst)beginif(!rst)cnt <= 18'h0;else if(key_edge)cnt <= 18'h0;elsecnt <= cnt + 1'h1;end reg [N-1:0] key_sec_pre; //延时后检测电平寄存器变量reg [N-1:0] key_sec; //延时后检测key,如果按键状态变低产生一个时钟的高脉冲。如果按键状态是高的话说明按键无效always @(posedge clk or negedge rst)beginif (!rst) key_sec <= {N{1'b1}}; else if (cnt==18'h3ffff)key_sec <= key; endalways @(posedge clk or negedge rst)beginif (!rst)key_sec_pre <= {N{1'b1}};else key_sec_pre <= key_sec; end assign key_pulse = key_sec_pre & (~key_sec); endmodule

2.3管脚分配

三.流水灯

3.1 LED_flash.v代码

module LED_flash(clk,rst,led);input clk,rst; output [7:0] led; reg [2:0] cnt ; //定义了一个3位的计数器,输出可以作为3-8译码器的输入wire clk1h; //定义一个中间变量,表示分频得到的时钟,用作计数器的触发 //例化module decode38,相当于调用decode38 u1 ( .sw(cnt), //例化的输入端口连接到cnt,输出端口连接到led .led(led));//例化分频器模块,产生一个1Hz时钟信号 divide #(.WIDTH(32),.N(12000000)) u2 ( //传递参数.clk(clk),.rst_n(rst), //例化的端口信号都连接到定义好的信号.clkout(clk1h)); //1Hz时钟上升沿触发计数器,循环计数 always @(posedge clk1h or negedge rst)if (!rst)cnt <= 0;elsecnt <= cnt +1;endmodule3.2 divide.v代码

module divide ( clk,rst_n,clkout);input clk,rst_n; //输入信号,其中clk连接到FPGA的C1脚,频率为12MHzoutput clkout; //输出信号,可以连接到LED观察分频的时钟//parameter是verilog里常数语句parameter WIDTH = 3; //计数器的位数,计数的最大值为 2**WIDTH-1parameter N = 5; //分频系数,请确保 N < 2**WIDTH-1,否则计数会溢出reg [WIDTH-1:0] cnt_p,cnt_n; //cnt_p为上升沿触发时的计数器,cnt_n为下降沿触发时的计数器reg clk_p,clk_n; //clk_p为上升沿触发时分频时钟,clk_n为下降沿触发时分频时钟//上升沿触发时计数器的控制always @ (posedge clk or negedge rst_n )//posedge和negedge是verilog表示信号上升沿和下降沿//当clk上升沿来临或者rst_n变低的时候执行一次always里的语句beginif(!rst_n)cnt_p<=0;else if (cnt_p==(N-1))cnt_p<=0;else cnt_p<=cnt_p+1;//计数器一直计数,当计数到N-1的时候清零,这是一个模N的计数器end//上升沿触发的分频时钟输出,如果N为奇数得到的时钟占空比不是50%;如果N为偶数得到的时钟占空比为50%always @ (posedge clk or negedge rst_n)beginif(!rst_n)clk_p<=0;else if (cnt_p<(N>>1)) //N>>1表示右移一位,相当于除以2去掉余数clk_p<=0;else clk_p<=1; //得到的分频时钟正周期比负周期多一个clk时钟end//下降沿触发时计数器的控制 always @ (negedge clk or negedge rst_n)beginif(!rst_n)cnt_n<=0;else if (cnt_n==(N-1))cnt_n<=0;else cnt_n<=cnt_n+1;end//下降沿触发的分频时钟输出,和clk_p相差半个时钟always @ (negedge clk)beginif(!rst_n)clk_n<=0;else if (cnt_n<(N>>1)) clk_n<=0;else clk_n<=1; //得到的分频时钟正周期比负周期多一个clk时钟endassign clkout = (N==1)?clk:(N[0])?(clk_p&clk_n):clk_p; //条件判断表达式 //当N=1时,直接输出clk//当N为偶数也就是N的最低位为0,N(0)=0,输出clk_p//当N为奇数也就是N最低位为1,N(0)=1,输出clk_p&clk_n。//正周期多所以是相与

endmodule 3.3decode38.v代码

module decode38 (sw,led);input [2:0] sw; //开关输入信号,利用了其中3个开关作为3-8译码器的输入output [7:0] led; //输出信号控制特定LEDreg [7:0] led; //定义led为reg型变量,在always过程块中只能对reg型变量赋值//always过程块,括号中sw为敏感变量,当sw变化一次执行一次always中所有语句,否则保持不变always @ (sw)begincase(sw) //case语句,一定要跟default语句3'b000: led=8'b0111_1111; //条件跳转,其中“_”下划线只是为了阅读方便,无实际意义 3'b001: led=8'b1011_1111; //位宽'进制+数值是Verilog里常数的表达方法,//进制可以是b、o、d、h(二、八、十、十六进制)3'b010: led=8'b1101_1111;3'b011: led=8'b1110_1111;3'b100: led=8'b1111_0111;3'b101: led=8'b1111_1011;3'b110: led=8'b1111_1101;3'b111: led=8'b1111_1110;default: ;endcaseendendmodule3.4管脚分配

四.呼吸灯

4.1 LED_breath.v代码

module LED_breath(clk,rst,led);input clk; //系统时钟输入input rst; //复位输出output led; //led输出reg [24:0] cnt1; //计数器1reg [24:0] cnt2; //计数器2reg flag; //呼吸灯变亮和变暗的标志位//parameter CNT_NUM = 2400; //计数器的最大值 period = (2400^2)*2 ~= 12000000 = 1s由亮到暗0.5s,由暗到亮0.5sparameter CNT_NUM = 3464; //计数器的最大值 period = (3464^2)*2 ~= 24000000 = 2s由亮到暗1s,由暗到亮1s//产生计数器cnt1always@(posedge clk or negedge rst) begin if(!rst) begincnt1<=13'd0;end else beginif(cnt1>=CNT_NUM-1) cnt1<=1'b0;else cnt1<=cnt1+1'b1; endend//产生计数器cnt2always@(posedge clk or negedge rst) begin if(!rst) begincnt2<=13'd0;flag<=1'b0;end else beginif(cnt1==CNT_NUM-1) begin //当计数器1计满时计数器2开始计数加一或减一if(!flag) begin //当标志位为0时计数器2递增计数,表示呼吸灯效果由暗变亮if(cnt2>=CNT_NUM-1) //计数器2计满时,表示亮度已最大,//标志位变高,之后计数器2开始递减flag<=1'b1;elsecnt2<=cnt2+1'b1;end else begin //当标志位为高时计数器2递减计数if(cnt2<=0) //计数器2级到0,表示亮度已最小,标志位变低,之后计数器2开始递增flag<=1'b0;else cnt2<=cnt2-1'b1;endendelse cnt2<=cnt2;//计数器1在计数过程中计数器2保持不变endend//比较计数器1和计数器2的值产生自动调整占空比输出的信号,输出到led产生呼吸灯效果assign led = (cnt1<cnt2)?1'b0:1'b1;endmodule4.2管脚分配

相关文章:

北邮22级信通院数电:Verilog-FPGA(4)第三周实验:按键消抖、呼吸灯、流水灯 操作流程注意事项

北邮22信通一枚~ 跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章 持续关注作者 迎接数电实验学习~ 获取更多文章,请访问专栏: 北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客 目录 一.注意事项 二.按键消抖 2.1 LED_deboun…...

Ghidra101再入门(上?)-Ghidra架构介绍

Ghidra101再入门(上?)-Ghidra架构介绍 最近有群友问我,说:“用了很多年的IDA,最近想看看Ghidra,这应该怎么进行入门?“这可难到我了。。 我发现,市面上虽然介绍Ghidra怎么用的文章和书籍很多&…...

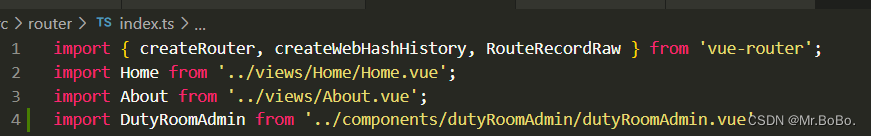

Vue3路由引入报错解决:无法找到模块“xxx.vue”的声明文件 xxx隐式拥有 “any“ 类型。

这类情况应该遇见过吧,这是因为 TypeScript只能理解 .ts 文件,无法理解 .vue 文件。 解决方法:在项目的根目录或者src文件夹下创建一个后辍为 文件名.d.ts 的文件,并写入一下内容: declare module *.vue {import { …...

基于若依ruoyi-nbcio支持flowable流程分类里增加流程应用类型

更多ruoyi-nbcio功能请看演示系统 gitee源代码地址 前后端代码: https://gitee.com/nbacheng/ruoyi-nbcio 演示地址:RuoYi-Nbcio后台管理系统 主要考虑到流程分很多种,普通的是OA流程,还有自定义业务流程,钉钉流程等…...

JS之同步异步promise、async、await

promise异步操作 Promise是异步编程的一种解决方案 JavaScript异步与同步解析 学习promise前我们先来了解下什么是异步? 基本概念: 消息队列中的任务分为宏任务与微任务;调用栈也可以称为主线程 首先我们要知道js是单线程语言,也就是说…...

【OpenCV • c++】自定义直方图 | 灰度直方图均衡 | 彩色直方图均衡

文章目录 一、什么是直方图二、自定义直方图三、灰度直方图均衡四、彩色直方图均衡一、什么是直方图 直方图广泛应用于很多计算机视觉处理当中。通过标记帧与帧之间显著的边缘和颜色的变化,可以检测视频中的场景变化。在每个兴趣点设置一个有相似特征的直方图所构成的“标签”…...

el-tree目录和el-table实现搜索定位高亮方法

需求:el-tree目录实现搜索查询el-table表格项,双击表格项根据yiZhuMLID||muLuID定位el-tree目录,并且高亮展示在可视化区域内,再重新根据el-tree目录的yiZhuMLID搜索刷新el-table表格,定位且高亮展示相对应的yiZhuMLID…...

linux常用指令

基础命令 cd:用于切换目录。例如,要从当前目录切换到/home/user目录,可以使用命令“cd /home/user”。ls:用于列出目录内容。例如,要列出当前目录的内容,可以使用命令“ls”。mkdir:用于创建目…...

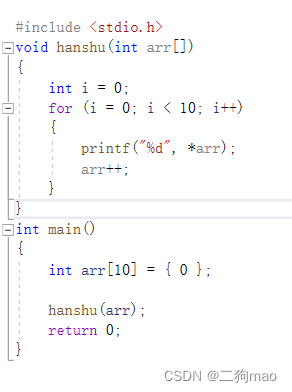

C语言,指针的一些运算

若创建一个数组:int arr[10] 0; 用指针变量来储存数组首元素的地址:int* p arr,这里arr是数组名,表示首元素地址。 若p p 1或者p之后p本来指向数组首元素地址,就变成了指向第二个元素的地址,p n即指向第n 1个地…...

iPhone 如何强制重启

参考iPhone的官方使用手册 传送门 尤其当 iPhone 未响应,也无法将其关机再开机,此方法最有效: 按住调高音量按钮,然后快速松开。按住调低音量按钮,然后快速松开。按住侧边按钮。当 Apple 标志出现时,松开侧…...

数据结构--单链表操作

1.单链表的创建(带头结点) #include<stdlib.h> #define ElemType int typedef struct {//定义一个结点ElemType data;struct STU* next; }STU,*LinkList; bool InitList(LinkList& L) {L (STU*)malloc(sizeof(STU));//创建头结点if (L NUL…...

AlmaLinux (兼容centos)安装Geant4与ROOT

AlmaLinux 介绍 AlmaLinux OS 是一个开源、社区驱动的 Linux 操作系统,它填补了因 CentOS 稳定版本停止维护而留下的空白,同时更加强大。 安装 AlmaLinux 这个我用的是 windows 子系统进行安装 首先打开微软商店,然后搜索AlmaLinux&#…...

)

FPGA面试题(2)

一.同步复位和异步复位 同步复位:当clk有效时,复位才有效。优点:有利于时序分析,防止毛刺现象出现。缺点:复位信号必须大于时钟周期,大部分逻辑器件中D触发器都只有异步复位端口,需要在寄存器数…...

【C++ Primer Plus学习记录】指针——使用new来创建动态数组

目录 1.使用new创建动态数组 2.使用动态数组(如何使用指针访问数组元素) 如果程序只需要一个值,则可能会声明一个简单变量,因为对于管理一个小型数据对象来说,这样做比使用new和指针更简单。通常,对于大型…...

移动app广告变现,对接广告联盟还是选择第三方聚合广告平台?

作为互联网广告的载体,APP天生就比线下传统广告位更具优势,不受地域限制可以辐射到地球上的每一个角落,可以让广告获得更广的覆盖面。通过丰富的广告形式,精准的目标用户画像,也可以更好地实现品牌广告或效果广告的投放…...

ARM 按键控制 LED灯,蜂鸣器,风扇

main.c: #include "uart.h" #include "key_it.h" int main() {all_led_init();uart4_init();//串口初始化//中断初始化key_it_config();key3_it_config();buzzer_init();fan_init();while(1){//保证主程序不结束}return 0; }src/key_it.c: #include"…...

VirtualBox Ubuntu扩展虚拟机磁盘空间

关于Orical VM VirtualBox虚拟机安装了ubuntu linux系统,由于需要,磁盘空间不足,需要扩展磁盘空间,最终找到了一个非常简单的方法,上干货。 1、关闭虚拟机 2、运用VBoxManage命令扩展vdi文件的空间 打开windows的命…...

C#开发的OpenRA游戏之电力系统之二

C#开发的OpenRA游戏之电力系统之二 继续前面的电力系统分析,在OpenRA游戏里,每一个建筑物都会有一个电力描述字段,说明这个建筑物是消耗电力,还是产生电力的。如果这个建筑物是产生电力的,那么这个字段就会是正值,如果这个建筑物是消耗电力的,就会是负值。因此所有电厂…...

Java架构师基础框架设计

目录 1 导学2 理解软件框架3 框架设计里面的框架和设计模式的关系4 基础框架中常见的基本功能4.1 事务处理4.2 微服务网络调用4.3 缓存实现4.4 分布式id4.5 任务调度4.6 工作流5 基础框架的几种基本的使用方式5.1 继承方式5.2 注解或注解加AOP的方式5.3 将基础框架的功能直接当…...

tortoise创建本地仓库

1.安装git和tortoise 推荐 TortoiseGit的安装与配置方法 以及 Git TortoiseGit 配置步骤以及本地版本管理 这里记录一下我遇到的问题 1.右键没有创建本地版本库 2 .创建了但是克隆不了 后续专有 一般选专有网络 注意自行谨慎选择 自行负责...

Diablo Edit2完全指南:掌握暗黑破坏神2存档编辑的艺术

Diablo Edit2完全指南:掌握暗黑破坏神2存档编辑的艺术 【免费下载链接】diablo_edit Diablo II Character editor. 项目地址: https://gitcode.com/gh_mirrors/di/diablo_edit 你是否曾经在暗黑破坏神2中因为技能点分配失误而懊恼?是否因为刷不到…...

在Node.js服务中集成Taotoken实现多模型智能对话

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 在Node.js服务中集成Taotoken实现多模型智能对话 应用场景类,描述一个Node.js后端服务需要集成大模型能力的场景&#…...

如何在Hermes Agent项目中自定义Provider接入Taotoken多模型服务

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 如何在Hermes Agent项目中自定义Provider接入Taotoken多模型服务 Hermes Agent 是一个功能强大的AI代理框架,它允许开发…...

B站成分检测器:5分钟快速上手终极指南,智能识别评论区用户真实身份

B站成分检测器:5分钟快速上手终极指南,智能识别评论区用户真实身份 【免费下载链接】bilibili-comment-checker B站评论区自动标注成分,支持动态和关注识别以及手动输入 UID 识别 项目地址: https://gitcode.com/gh_mirrors/bil/bilibili-c…...

Adobe-GenP 3.0终极指南:三步免费解锁Adobe全家桶的完整教程

Adobe-GenP 3.0终极指南:三步免费解锁Adobe全家桶的完整教程 【免费下载链接】Adobe-GenP Adobe CC 2019/2020/2021/2022/2023 GenP Universal Patch 3.0 项目地址: https://gitcode.com/gh_mirrors/ad/Adobe-GenP 想要免费使用Adobe Creative Cloud专业软件…...

戴尔G15散热控制终极指南:免费开源工具TCC-G15告别过热降频

戴尔G15散热控制终极指南:免费开源工具TCC-G15告别过热降频 【免费下载链接】tcc-g15 Thermal Control Center for Dell G15 - open source alternative to AWCC 项目地址: https://gitcode.com/gh_mirrors/tc/tcc-g15 你是否为戴尔G15笔记本在游戏或高强度工…...

终极Windows与Office智能激活解决方案:KMS_VL_ALL_AIO全面解析与实战指南

终极Windows与Office智能激活解决方案:KMS_VL_ALL_AIO全面解析与实战指南 【免费下载链接】KMS_VL_ALL_AIO Smart Activation Script 项目地址: https://gitcode.com/gh_mirrors/km/KMS_VL_ALL_AIO KMS_VL_ALL_AIO是一款功能强大的Windows与Office智能激活脚…...

3分钟上手ncmdumpGUI:网易云音乐NCM文件轻松转换的完整指南

3分钟上手ncmdumpGUI:网易云音乐NCM文件轻松转换的完整指南 【免费下载链接】ncmdumpGUI C#版本网易云音乐ncm文件格式转换,Windows图形界面版本 项目地址: https://gitcode.com/gh_mirrors/nc/ncmdumpGUI 还在为网易云音乐的NCM格式文件无法在其…...

)

DeepSeek LeetCode 2508.添加边使所有节点度数都为偶数 public boolean isPossible(int n, List<List<Integer>> edges)

问题分析我们需要判断能否添加至多两条边(不能添加重复边,不能添加自环),使得图中所有节点的度数都为偶数。---思路步骤1. 统计每个节点的当前度数遍历给出的边,统计每个节点的度数。 2. 找出度数为奇数的节点设奇数度…...

基于Zynq FPGA的2-FSK基带发射器设计与实现

1. 项目概述与核心思路最近在折腾一个基于Zynq的软件定义无线电(SDR)小项目,核心需求很简单:用硬件逻辑生成一个可调频率的正弦波,并通过DAC输出。这听起来像是数字信号处理的入门练习,但我的目标更具体一点…...