【数字IC设计】DC自动添加门控时钟

简介

数字电路的动态功耗主要是由于寄存器翻转带来的,为了降低芯片内部功耗,门控时钟的方案应运而生。作为低功耗设计的一种方法,门控时钟是指在数据无效时将寄存器的时钟关闭,以此来降低动态功耗。

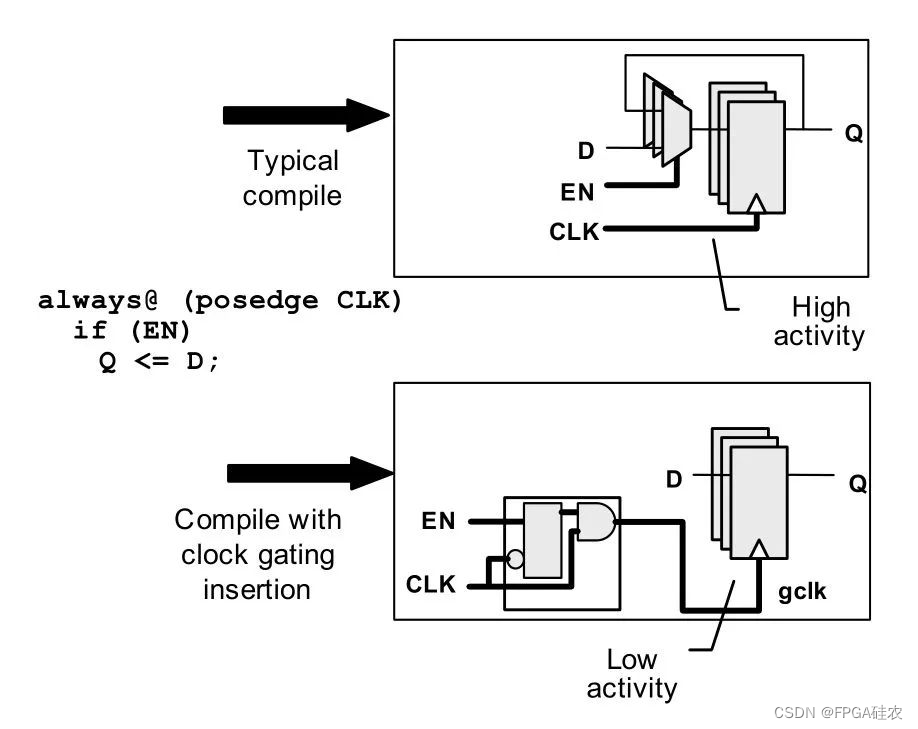

在下图中,展示了加入门控时钟前后电路的变化。由图可知,采取门控时钟技术后,原先的MUX单元消失了(MUX数目和寄存器bit数目有关),但会增加1个额外的门控时钟单元。因此,插入门控时钟并不总是能带来面积上的收益,需要综合数据位宽来考虑。总结一下,就是:

- 插入门控时钟单元后,电路中的MUX就不需要了,如果数据D是多bit的(一般都是如此),插入CG后的面积可能反而会减少;

- 如果D是单bit信号,节省的功耗就比较少,但是如果D是一个32bit的信号,那么插入CG后节省的功耗就比较多了。

这里的决定因素就是D的位宽,若D的位宽很小,那么可能插入的CG面积比原来的MUX大很多,而且节省的功耗又很少,得不偿失。只有当D的位宽超过了一定的bit数后,插入CG的收益才会比较大。

关于这个临界值,不同的工艺可能不同,DC工具给的默认值是3。即,如果D的位宽超过了3bit,那么DC就会默认插入CG。

我们可以通过DC命令:

set_clock_gating_style -minimum_bitwidth 4

来控制芯片中,对不同位宽的寄存器是否自动插入CG。然而,一般情况我们都不会去修改它。

关于门控时钟的详细介绍,在文章中已经给出,这里不再赘述。

DC添加门控时钟

在实际的ASIC设计过程中,门控时钟不需要开发者自己写代码实现,完全可以通过对综合工具进行相应配置,让工具完成对电路添加合适的门控时钟。

下面是一个简单的关于门控时钟的实验:

RTL代码

数据宽度为3bit时:

module cg_top_w3

(input logic clk, input logic rst_n, input logic vld_in, input logic [3-1:0] data_in, output logic vld_out, output logic [3-1:0] data1_out,output logic [3-1:0] data2_out

);always@(posedge clk or negedge rst_n) beginif(!rst_n) beginvld_out <= 1'b0; endelse beginvld_out <= vld_in; end

endalways@(posedge clk or negedge rst_n) beginif(!rst_n) begindata1_out <= 'b0; endelse if(vld_in) begindata1_out <= data_in; end

endalways@(posedge clk or negedge rst_n) beginif(!rst_n) begindata2_out <= 'b0;endelse if(vld_in) begindata2_out <= data_in;endelse begindata2_out <= '0;end

endendmodule

数据宽度为8bit时:

module cg_top_w8

(input logic clk, input logic rst_n, input logic vld_in, input logic [8-1:0] data_in, output logic vld_out, output logic [8-1:0] data1_out, output logic [8-1:0] data2_out

);always@(posedge clk or negedge rst_n) beginif(!rst_n) beginvld_out <= 1'b0; endelse beginvld_out <= vld_in; end

endalways@(posedge clk or negedge rst_n) beginif(!rst_n) begindata1_out <= 'b0; endelse if(vld_in) begindata1_out <= data_in; end

endalways@(posedge clk or negedge rst_n) beginif(!rst_n) begindata2_out <= 'b0;endelse if(vld_in) begindata2_out <= data_in;endelse begindata2_out <= '0;end

endendmodule

两者对应的tcl文件分别为:

set_app_var search_path ./LM

set_app_var target_library sc_max.db

set_app_var link_library sc_max.db

read_file -format sverilog {./cg_top_w3.sv}

check_design

create_clock -period 10 [get_ports clk]

check_design

set_clock_gating_style -minimum_bitwidth 4

compile -gate_clock

report_clock

report_timing

report_area

write_file -format verilog -output cg_top_w3_netlist.v和

set_app_var search_path ./LM

set_app_var target_library sc_max.db

set_app_var link_library sc_max.db

read_file -format sverilog {./cg_top_w8.sv}

check_design

create_clock -period 1 [get_ports clk]

check_design

set_clock_gating_style -minimum_bitwidth 4

compile -gate_clock

report_clock

report_timing

report_power > cg_top_w8.power.rpt

report_area > cg_top_w8.area.rpt

write_file -format verilog -output cg_top_w8_netlist.v其中,set_clock_gating_style -minimum_bitwidth 4用于告诉综合工具数据位宽大于等于多少的时候,开启门控时钟。在进行编译的时候,需要加上-gate_clock选项,即compile -gate_clock。

运行综合

输入dc进入dc shell后,输入source ./xxx.tcl文件运行,可以得到综合后的网表文件。

数据位宽为3bit:

/

// Created by: Synopsys DC Expert(TM) in wire load mode

// Version : L-2016.03-SP1

// Date : Sat Oct 14 10:44:29 2023

/module cg_top_w3 ( clk, rst_n, vld_in, data_in, vld_out, data1_out, data2_out);input [2:0] data_in;output [2:0] data1_out;output [2:0] data2_out;input clk, rst_n, vld_in;output vld_out;wire N4, N5, N6, n1;dfcrq1 vld_out_reg ( .D(vld_in), .CP(clk), .CDN(rst_n), .Q(vld_out) );decrq1 \data1_out_reg[2] ( .D(data_in[2]), .ENN(n1), .CP(clk), .CDN(rst_n), .Q(data1_out[2]) );decrq1 \data1_out_reg[1] ( .D(data_in[1]), .ENN(n1), .CP(clk), .CDN(rst_n), .Q(data1_out[1]) );decrq1 \data1_out_reg[0] ( .D(data_in[0]), .ENN(n1), .CP(clk), .CDN(rst_n), .Q(data1_out[0]) );dfcrq1 \data2_out_reg[2] ( .D(N6), .CP(clk), .CDN(rst_n), .Q(data2_out[2]));dfcrq1 \data2_out_reg[1] ( .D(N5), .CP(clk), .CDN(rst_n), .Q(data2_out[1]));dfcrq1 \data2_out_reg[0] ( .D(N4), .CP(clk), .CDN(rst_n), .Q(data2_out[0]));inv0d1 U3 ( .I(vld_in), .ZN(n1) );an02d1 U4 ( .A1(vld_in), .A2(data_in[2]), .Z(N6) );an02d1 U5 ( .A1(data_in[1]), .A2(vld_in), .Z(N5) );an02d1 U6 ( .A1(data_in[0]), .A2(vld_in), .Z(N4) );

endmodule可以看到,数据位宽为3bit时,网表中没有门控时钟单元。

数据位宽为8bit时:

/

// Created by: Synopsys DC Expert(TM) in wire load mode

// Version : L-2016.03-SP1

// Date : Sat Oct 14 10:44:38 2023

/module cg_top_w8 ( clk, rst_n, vld_in, data_in, vld_out, data1_out, data2_out);input [7:0] data_in;output [7:0] data1_out;output [7:0] data2_out;input clk, rst_n, vld_in;output vld_out;wire N4, N5, N6, N7, N8, N9, N10, N11, net21;SNPS_CLOCK_GATE_HIGH_cg_top_w8 clk_gate_data1_out_reg ( .CLK(clk), .EN(vld_in), .ENCLK(net21) );dfcrq1 vld_out_reg ( .D(vld_in), .CP(clk), .CDN(rst_n), .Q(vld_out) );dfcrq1 \data1_out_reg[7] ( .D(data_in[7]), .CP(net21), .CDN(rst_n), .Q(data1_out[7]) );dfcrq1 \data1_out_reg[6] ( .D(data_in[6]), .CP(net21), .CDN(rst_n), .Q(data1_out[6]) );dfcrq1 \data1_out_reg[5] ( .D(data_in[5]), .CP(net21), .CDN(rst_n), .Q(data1_out[5]) );dfcrq1 \data1_out_reg[4] ( .D(data_in[4]), .CP(net21), .CDN(rst_n), .Q(data1_out[4]) );dfcrq1 \data1_out_reg[3] ( .D(data_in[3]), .CP(net21), .CDN(rst_n), .Q(data1_out[3]) );dfcrq1 \data1_out_reg[2] ( .D(data_in[2]), .CP(net21), .CDN(rst_n), .Q(data1_out[2]) );dfcrq1 \data1_out_reg[1] ( .D(data_in[1]), .CP(net21), .CDN(rst_n), .Q(data1_out[1]) );dfcrq1 \data1_out_reg[0] ( .D(data_in[0]), .CP(net21), .CDN(rst_n), .Q(data1_out[0]) );dfcrq1 \data2_out_reg[7] ( .D(N11), .CP(clk), .CDN(rst_n), .Q(data2_out[7]));dfcrq1 \data2_out_reg[6] ( .D(N10), .CP(clk), .CDN(rst_n), .Q(data2_out[6]));dfcrq1 \data2_out_reg[5] ( .D(N9), .CP(clk), .CDN(rst_n), .Q(data2_out[5]));dfcrq1 \data2_out_reg[4] ( .D(N8), .CP(clk), .CDN(rst_n), .Q(data2_out[4]));dfcrq1 \data2_out_reg[3] ( .D(N7), .CP(clk), .CDN(rst_n), .Q(data2_out[3]));dfcrq1 \data2_out_reg[2] ( .D(N6), .CP(clk), .CDN(rst_n), .Q(data2_out[2]));dfcrq1 \data2_out_reg[1] ( .D(N5), .CP(clk), .CDN(rst_n), .Q(data2_out[1]));dfcrq1 \data2_out_reg[0] ( .D(N4), .CP(clk), .CDN(rst_n), .Q(data2_out[0]));an02d1 U3 ( .A1(vld_in), .A2(data_in[5]), .Z(N9) );an02d1 U4 ( .A1(data_in[4]), .A2(vld_in), .Z(N8) );an02d1 U5 ( .A1(data_in[3]), .A2(vld_in), .Z(N7) );an02d1 U6 ( .A1(data_in[2]), .A2(vld_in), .Z(N6) );an02d1 U7 ( .A1(data_in[1]), .A2(vld_in), .Z(N5) );an02d1 U8 ( .A1(data_in[0]), .A2(vld_in), .Z(N4) );an02d1 U9 ( .A1(data_in[7]), .A2(vld_in), .Z(N11) );an02d1 U10 ( .A1(data_in[6]), .A2(vld_in), .Z(N10) );

endmodule可以看到,数据位宽为8bit时,网表中出现了门控时钟单元,即:

SNPS_CLOCK_GATE_HIGH_cg_top_w8 clk_gate_data1_out_reg ( .CLK(clk), .EN(vld_in), .ENCLK(net21) );

同时,由网表可知,data1_out是被门控了的,而data2_out没有被门控,这是因为data2_out在使能信号无效的时候没有保持自身的值,而是将它赋值为0。

面积比较

为了比较插入门控时钟前后电路的面积,我们进行了一个实验,即采用如下tcl脚本对数据位宽为8bit的设计进行了综合:

set_app_var search_path ./LM

set_app_var target_library sc_max.db

set_app_var link_library sc_max.db

read_file -format sverilog {./cg_top_w8.sv}

check_design

create_clock -period 1 [get_ports clk]

check_design

compile

report_clock

report_timing

report_power > cg_top_w8_nocg.power.rpt

report_area > cg_top_w8_nocg.area.rpt

write_file -format verilog -output cg_top_w8_nocg_netlist.v

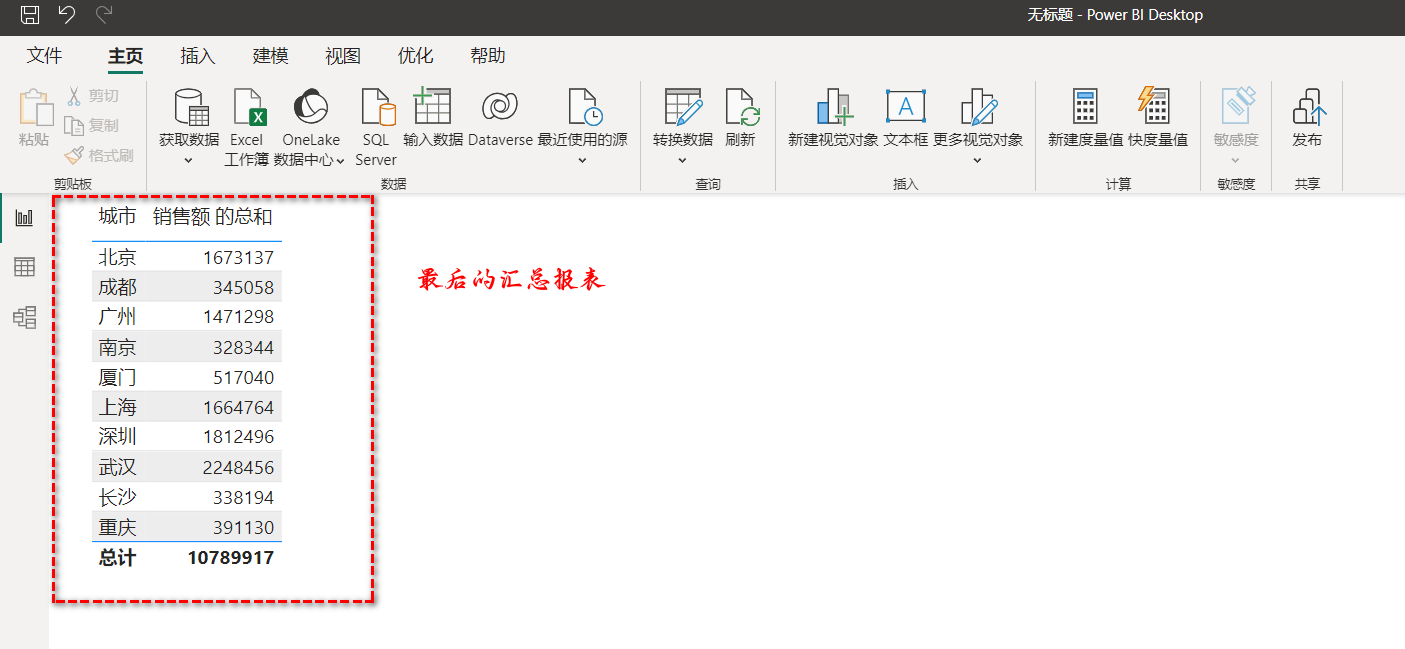

可以看到,该脚本和先前脚本的区别是取消了compile命令的-gate_clock选项。下面是综合报告给出的面积数据:

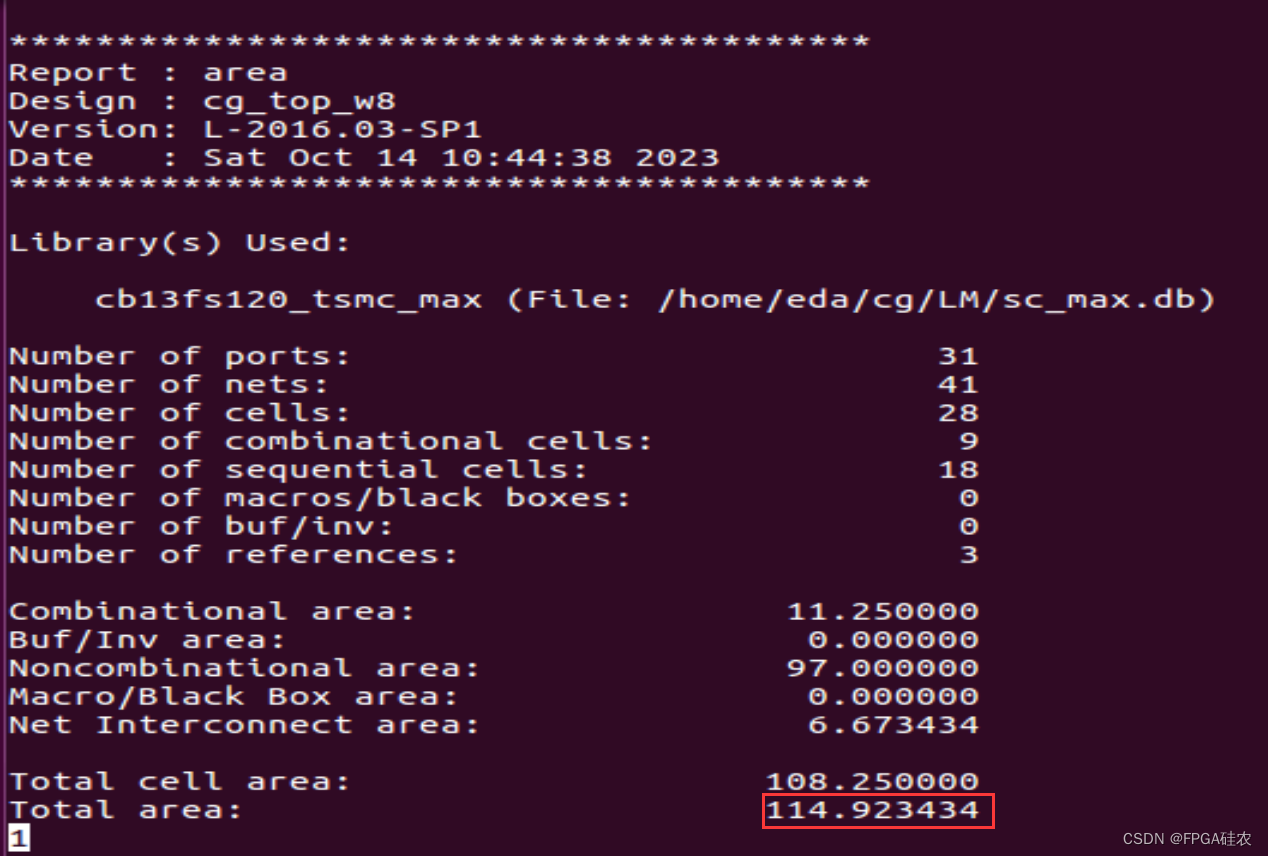

开启门控时钟的,总面积为114.9:

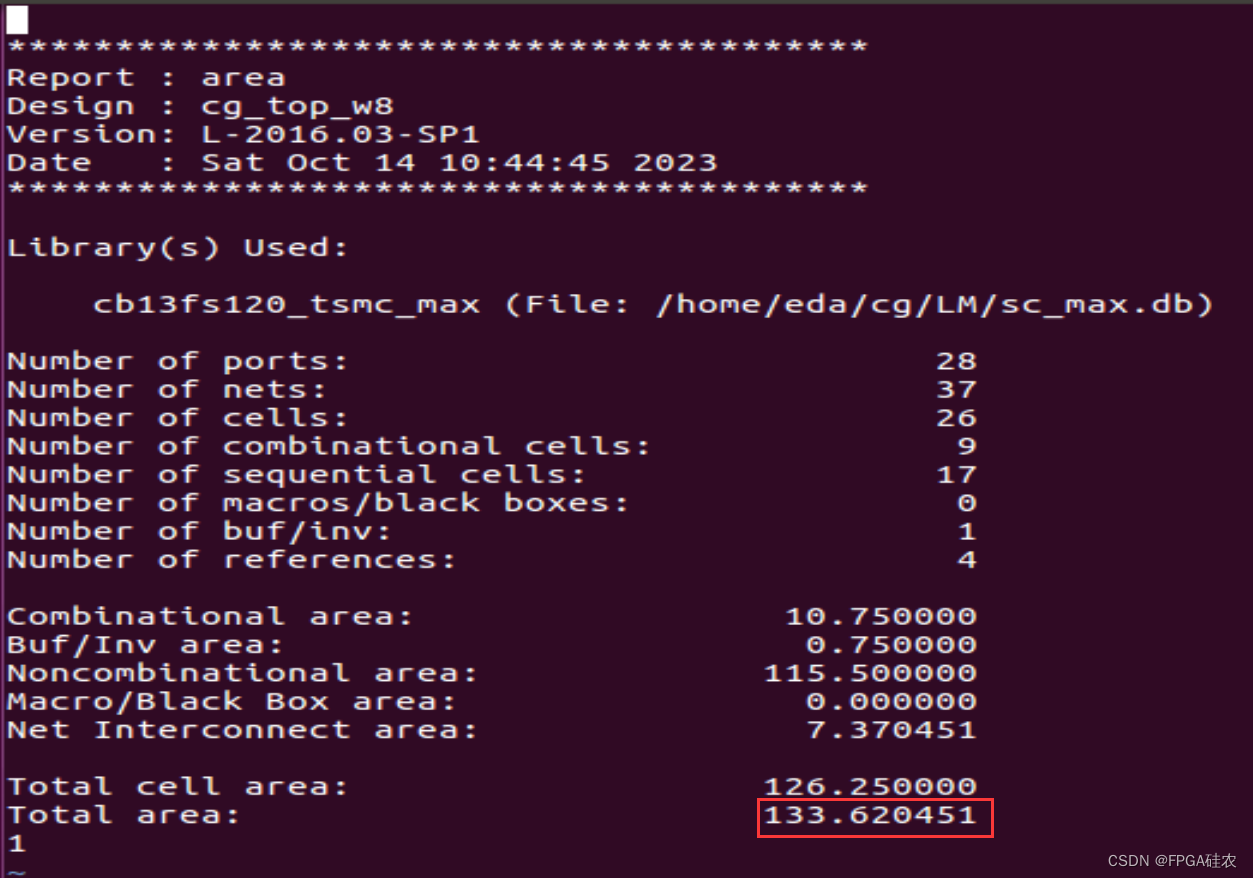

关闭门控时钟的,总面积为133.6:

由此可见,在数据位宽为8bit的情况下,对当前设计开启门控时钟可以节约14%的面积。

相关文章:

【数字IC设计】DC自动添加门控时钟

简介 数字电路的动态功耗主要是由于寄存器翻转带来的,为了降低芯片内部功耗,门控时钟的方案应运而生。作为低功耗设计的一种方法,门控时钟是指在数据无效时将寄存器的时钟关闭,以此来降低动态功耗。 在下图中,展示了…...

前端开发工具vscode

一、下载安装 https://code.visualstudio.com/ 二、安装插件 三、使用 ①、创建一个空目录 ②、利用vscode工具打开该目录 ③、将该目录设置为工作区 在工作区中添加文件,还可以进行浏览器访问(提前安装了Live Server插件) 为工具…...

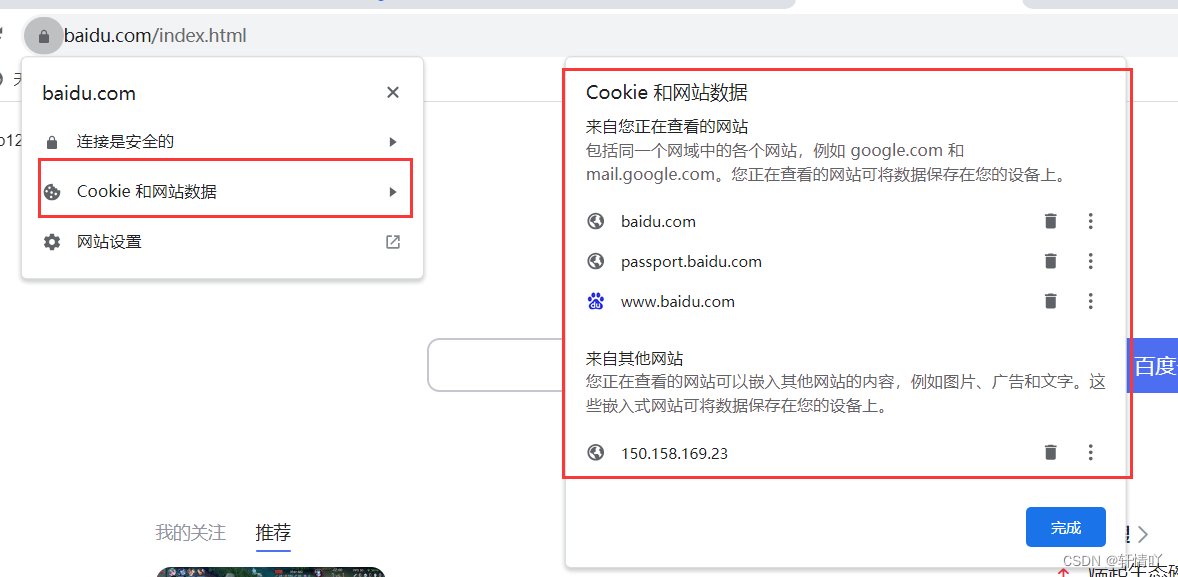

网络基础2(1)

HTTP 1.应用层协议2.send和recv单独使用不安全3.URL4.urlencode和urldecode5.HTTP协议格式6.HTTP中的常见请求方法POST&&GET7.HTTP的状态码8.HTTP常见Header 🌟🌟hello,各位读者大大们你们好呀🌟🌟 Ƕ…...

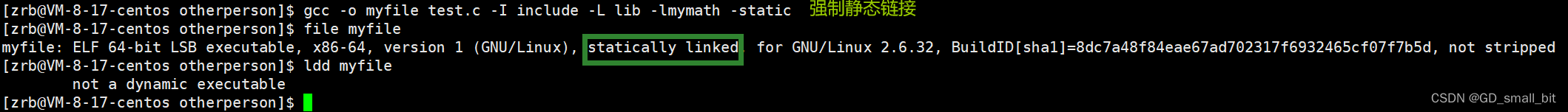

系统文件IO、文件描述符fd、重定向、文件系统、动态库和静态库

目录 C文件接口系统文件I/O系统调用和库函数文件描述符0 & 1 & 2FILE和fd的关系文件描述符的分配规则 重定向重定向的本质输出重定向输入重定向追加重定向 dup2函数 FILE理解文件系统了解磁盘的物理结构逻辑抽象文件系统文件系统的图解和解析通过文件系统来理解ls -al通…...

一、K8S第一步搭建

一、初始化操作 1.1、关闭防火墙 systemctl stop firewalld systemctl disable firewalld关闭交换空间 swapoff -a # 临时 sed -ri s/.*swap.*/#&/ /etc/fstab # 永久重启才能生效 根据规划设置主机名 hostnamectl set-hostname <hostname>映射主机 cat >>…...

pwnable-1-fd

pwn的学习周期确实比较长,需要的前置内容也很多,了解到第一题还算比较简单的,那就先来体验一波~顺带附一波网站链接:👉网站链接 题目 WP 最后一行给出了ssh链接方式,那就先连接一波 第一次连接会有第四行的询问&…...

)

队列的实现(c语言)

队列也是线性表,也是分为两种的:1、顺序队列 2、链队列 顺序队列 #include <stdio.h> #include <stdlib.h>typedef struct {char *base;int front;int erer;int size; }SqQueue;void initSqQueue(SqQueue *queue,int size){queue->base…...

用python实现逆向分析并模拟登陆)

雷电模拟器上使用第一个frida(五)用python实现逆向分析并模拟登陆

上篇通过hook确定了登录代码的位置,参考雷电模拟器上使用第一个frida(四)第一个HOOK之抓包-CSDN博客 接下来逆向分析一下,并用python实现其功能,并模拟登陆。...

基于Linux上MySQL8.*版本的安装-参考官网

本地hadoop环境安装好,并安装好mysql mysql下载地址及选择包 MySQL :: Download MyS的QL Community Server (Archived Versions) mysql安装步骤 下载与上传解压给权限 #mysql安装包上传到/opt下 cd /usr/local/ #解压到此目录 tar -xvf /opt/mysql-8.0.33-linux-glibc2.12-…...

git 项目管理操作

git stash: 保存当前工作进度 git stash save message... : 添加一些注释。 git stash pop : 恢复最新的进度到工作区 git remote prune origin:将本地分支与已删除的远程分支同步 git branch -d <branch-name> :删除分支 git branch -D <branc…...

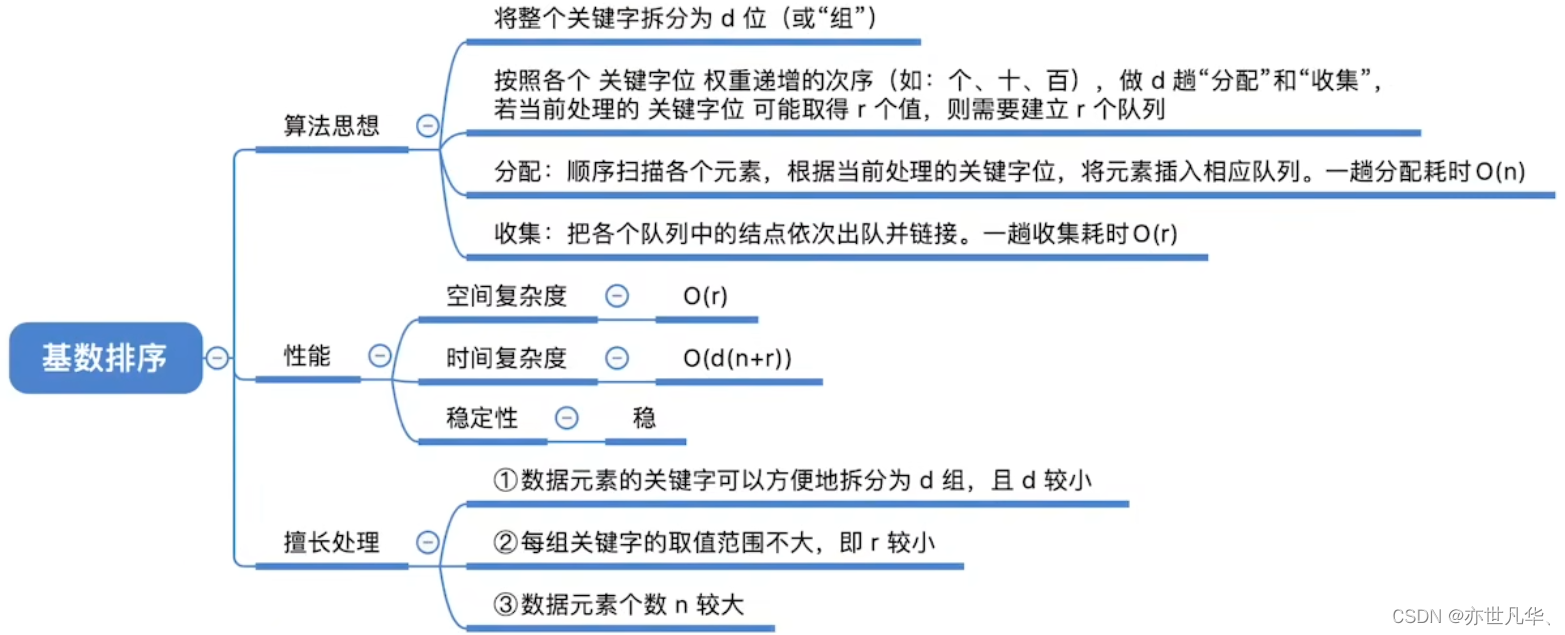

数据结构--》掌握数据结构中的排序算法

当我们面对海量数据时,如何高效地将其排序是数据结构领域中一个重要的问题。排序算法作为其中的关键部分,扮演着至关重要的角色。 无论你是初学者还是进阶者,本文将为你提供简单易懂、实用可行的知识点,帮助你更好地掌握排序算法在…...

-k8s节点设置cpu高于多少就不调度)

Kubernetes实战(三)-k8s节点设置cpu高于多少就不调度

1 k8s节点设置的概念和原理 k8s是Google开源的容器集群管理系统,用于自动化部署、扩展和管理容器化应用程序。在k8s中,Node是指容器运行的物理或虚拟机器。Node可以是一个物理机或一个虚拟机器,k8s通过其调度器将Pod调度到每个Node上。对于一…...

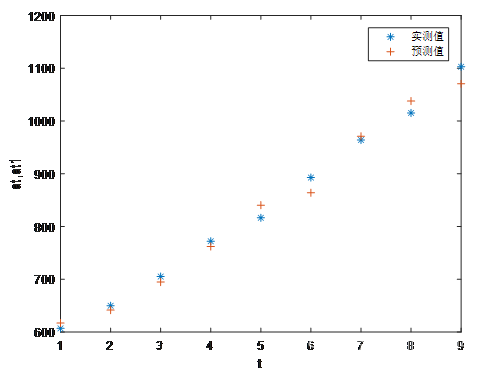

数学建模——平稳时间序列分析方法

目录 1、平稳性的Daniel检验 (1)Spearman相关系数假设检验 (2)时间序列平稳性的Danniel假设检验 案例 【模型分析】 1、原始数据at的平稳性检验 2、一阶差分序列的平稳性检验 3、二阶差分序列的平稳性检验 4、建立AR&#…...

Vuex使用方式及异步问题处理

🎬 艳艳耶✌️:个人主页 🔥 个人专栏 :《Spring与Mybatis集成整合》《Vue.js使用》 ⛺️ 生活的理想,为了不断更新自己 ! 目录 1.Vuex简介: 2.vuex获取值 2.1安装 2.2.菜单栏 2.3.模块 2.4使用 3.改…...

【Vue面试题二十七】、你了解axios的原理吗?有看过它的源码吗?

文章底部有个人公众号:热爱技术的小郑。主要分享开发知识、学习资料、毕业设计指导等。有兴趣的可以关注一下。为何分享? 踩过的坑没必要让别人在再踩,自己复盘也能加深记忆。利己利人、所谓双赢。 面试官:说下你的vue项目的目录结…...

LocalDateTime与时间戳

众所周知,如果想把 LocalDateTime 转为时间戳,需要先指定时区,然后才能转为时间戳,例如: LocalDateTime localDateTime LocalDateTime.now(); ZonedDateTime zonedDateTime localDateTime.atZone(ZoneId.systemDe…...

【Power BI】Power BI 入门指南:版本、下载和报表创建的步骤

文章目录 一、前言二、了解 Power BI 版本三、下载 Power BI Desktop四、如何开始使用 Power BI Desktop五、在 Power BI Desktop 中创建报表六、文末总结 一、前言 Power BI 是微软于 2013 年推出的产品,为一款商业智能与数据可视化工具。它通过引人注目的视觉效果…...

代码随想录算法训练营第23期day21| 235. 二叉搜索树的最近公共祖先 、701.二叉搜索树中的插入操作、450.删除二叉搜索树中的节点

目录 一、(leetcode 235)二叉搜索树的最近公共祖先 二、(leetcode 701)二叉搜索树中的插入操作 三、(leetcode 450)删除二叉搜索树中的节点 一、(leetcode 235)二叉搜索树的最近公…...

小程序页面路由传参的方法?

小程序页面路由传参的方法有三种: 1.URL参数传递:通过在页面跳转的URL中携带参数实现传参。可以使用wx.navigateTo或wx.redirectTo等跳转方法,并在URL中添加参数。 示例: // PageA.wxml <button bindtap"navigateToPage…...

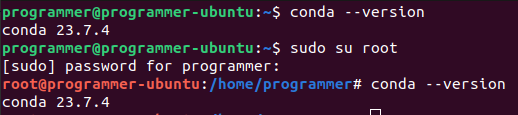

Ubuntu下安装Python

Ubuntu下安装Python 预备知识一、Python安装Python 二、Anaconda安装Anaconda卸载Anaconda 三、Miniconda安装Miniconda 四、异同比较 预备知识 (1) Python是一种编程语言。 (2) Anaconda是一款包管理工具,用来管理Python及其他语言的安装包,预装了很多…...

Knowledge Repo转换器终极指南:10个技巧实现Jupyter、R Markdown等多格式完美转换

Knowledge Repo转换器终极指南:10个技巧实现Jupyter、R Markdown等多格式完美转换 【免费下载链接】knowledge-repo A next-generation curated knowledge sharing platform for data scientists and other technical professions. 项目地址: https://gitcode.com…...

LLM驱动的AI Agent故事生成与叙事能力

LLM驱动的AI Agent故事生成与叙事能力 关键词:LLM(大语言模型)、AI Agent、故事生成、叙事能力、自然语言处理 摘要:本文聚焦于LLM驱动的AI Agent在故事生成与叙事能力方面的技术。首先介绍了研究背景,包括目的、预期读者、文档结构和相关术语。接着阐述了核心概念,如LLM…...

高效视频素材全流程管理工具:Cobalt 开源解决方案详解

高效视频素材全流程管理工具:Cobalt 开源解决方案详解 【免费下载链接】cobalt save what you love 项目地址: https://gitcode.com/GitHub_Trending/cob/cobalt Cobalt 是一款专为内容创作者设计的高效视频素材管理工具,支持从 30 主流平台下载视…...

之 图像处理进阶 - 像素操作与批量保存)

Labview 机器视觉(4)之 图像处理进阶 - 像素操作与批量保存

1. 像素操作:从入门到精通的实战指南 在工业自动化领域,图像处理的核心往往在于对像素级别的精准控制。LabVIEW作为一款强大的图形化编程工具,提供了丰富的像素操作函数,让工程师能够像搭积木一样构建复杂的视觉处理流程。 我第一…...

从一道蓝桥杯EDA赛题,聊聊平衡车硬件设计中那些‘不起眼’却关键的安全电路

平衡车硬件设计中的安全电路:从蓝桥杯赛题到工程实战 去年调试一款平衡车原型机时,我曾遇到一个诡异现象:每次电池快耗尽时,电机就会突然失控。经过三天排查,最终发现问题出在电源检测电路的分压电阻取值上——这个看似…...

告别繁琐安装!3分钟用PPTist打造专业级在线演示文稿

告别繁琐安装!3分钟用PPTist打造专业级在线演示文稿 【免费下载链接】PPTist 基于 Vue3.x TypeScript 的在线演示文稿(幻灯片)应用,还原了大部分 Office PowerPoint 常用功能,实现在线PPT的编辑、演示。支持导出PPT文…...

不止于教程:用QGIS 3.30 + PyQt5从零打造一个极简版GIS桌面应用

从零构建GIS桌面应用:QGIS 3.30与PyQt5深度整合实战 当我们需要开发一个轻量级地理信息系统时,QGIS的Python API提供了强大而灵活的选择。不同于简单的脚本编写,将QGIS作为引擎嵌入到自定义PyQt5应用中,能够实现高度定制化的GIS解…...

革新性网页资源捕获工具:猫抓全方位媒体嗅探与下载解决方案

革新性网页资源捕获工具:猫抓全方位媒体嗅探与下载解决方案 【免费下载链接】cat-catch 猫抓 chrome资源嗅探扩展 项目地址: https://gitcode.com/GitHub_Trending/ca/cat-catch 猫抓浏览器插件是一款革新性的开源资源嗅探工具,能够智能识别并捕获…...

使用Typora与Qwen3.5-4B打造智能写作工作流:大纲生成与文稿润色

使用Typora与Qwen3.5-4B打造智能写作工作流:大纲生成与文稿润色 1. 写作痛点与解决方案 对于内容创作者和技术文档工程师来说,Markdown写作过程中常遇到三个核心问题:一是从零开始构思文章大纲耗时费力;二是反复检查语法和风格一…...

Comsol 多裂纹水力压裂扩展:拉伸与压缩下的破坏探索

comsol多裂纹水力压裂扩展,可以实现拉伸和压缩下的破坏。在工程领域,水力压裂是一项至关重要的技术,尤其在石油和天然气开采等方面应用广泛。而 Comsol 作为强大的多物理场仿真软件,为我们研究多裂纹水力压裂扩展提供了有力工具&a…...