XIlinx提供的DDR3 IP与 UG586

DDR系统需要关注的三样东西:控制器、PHY、SDRAM颗粒,但这是实现一个DDR3 IP所需要的,如果只希望调用IP的话,则只需要调用IP即可,目前时间紧急,我先学一学如何使用IP,解决卡脖子的问题,自研日后再说。

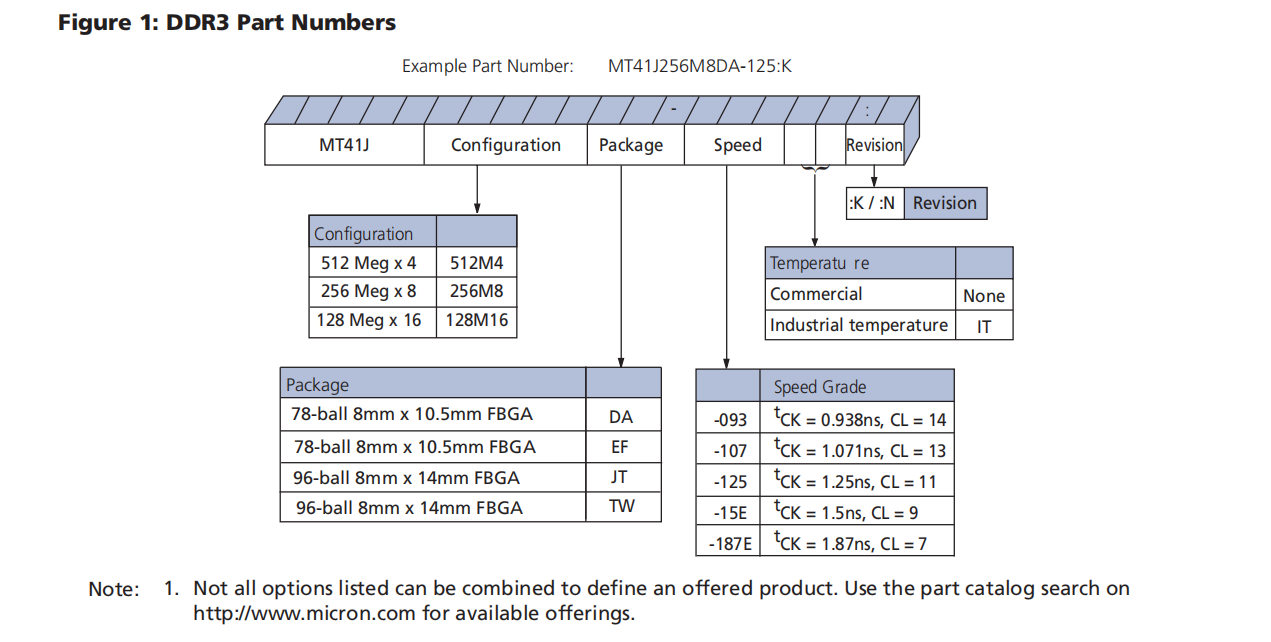

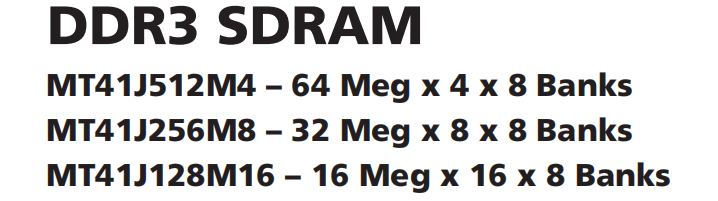

使用的DDR3器件:MT41J128M16JT-093K

总览

DDR3 IP配置

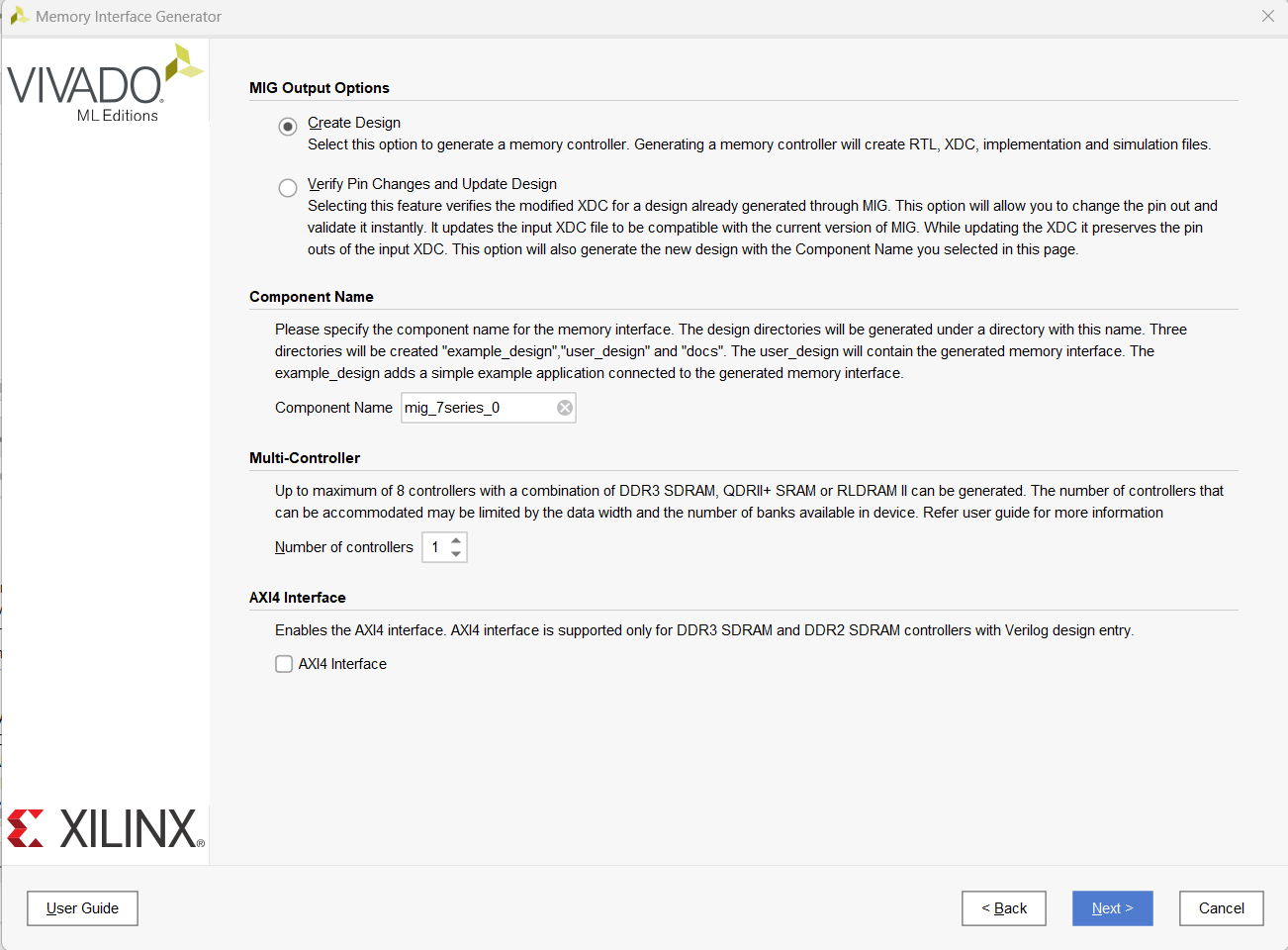

第一部分

Create Design

选择此选项可生成内存控制器。生成内存控制器将创建 RTL、XDC、implementation 和simulation 文件。

Verify Pin Changes and Update Design

选择此功能可验证已通过 MIG 生成的设计的修改后的 XDC。此选项允许您更改引脚分配并立即验证它,它会更新输入 XDC 文件以与当前版本的 MG 兼容。更新 XDC 时,它会保留输入 XDC 的引脚分配。此选项还将使用您在此页面中选择的组件名称生成新设计。

多控制器

通过 DDR3 SDRAM、QDR1+-SRAM 或 RLDRAM 的组合,最多可生成 8 个控制器。可容纳的控制器数量可能受到数据宽度和器件中可用存储体数量的限制。有关详细信息,请参阅用户指南 控制器数量 。

不使能则为APP接口:

Xilinx DDR3 —— MIG IP核的原理(APP接口)_XPii的博客-CSDN博客

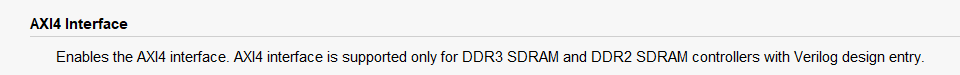

第二部分 选择可拓展器件

3

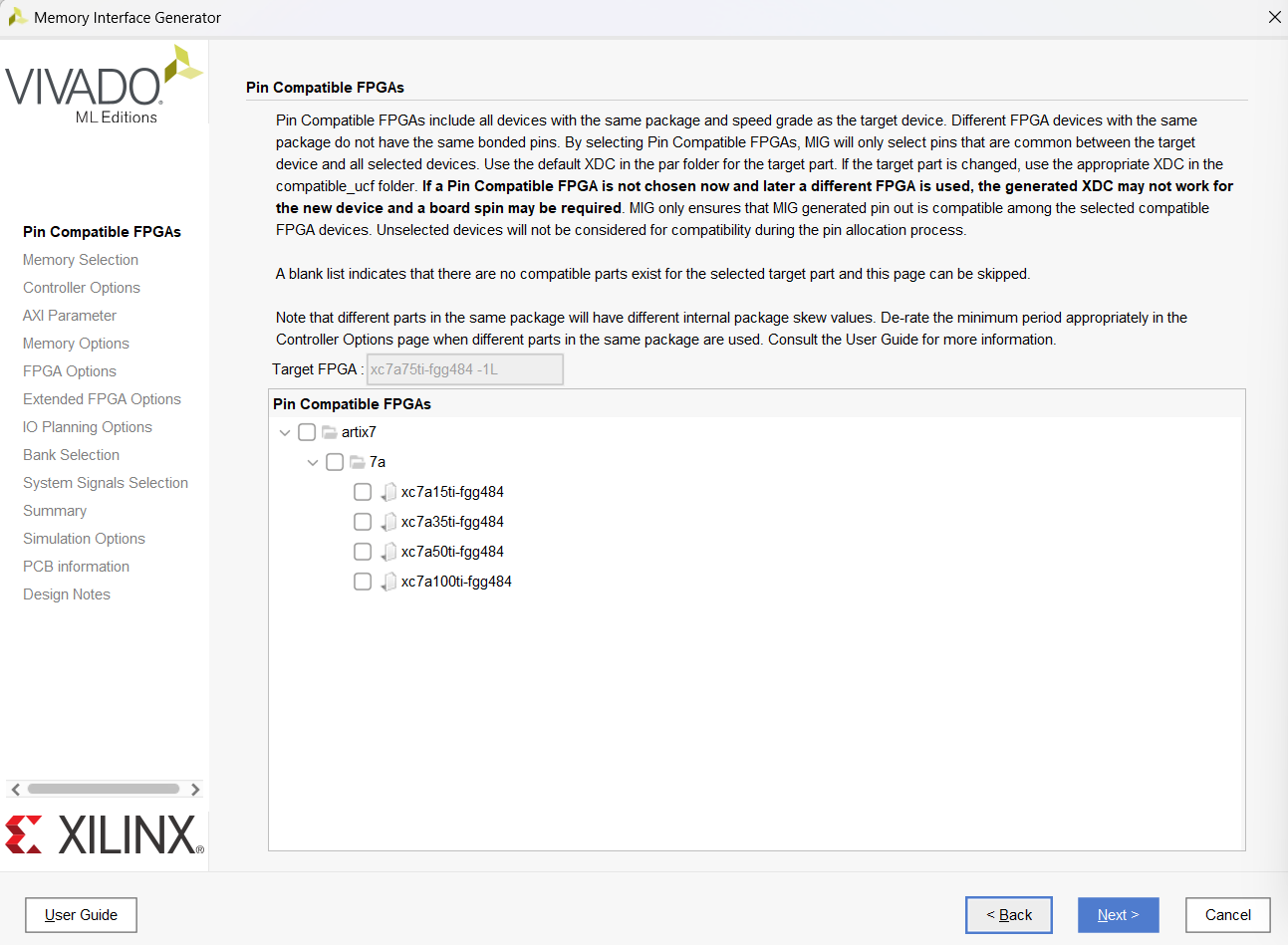

第三部分 选择内存接口类型。

请参阅用户指南,了解每个 FPGA 系列支持的控制器的详细列表。下面的列表显示了特定 FPGA、速度等级和所选设计条目的当前可用接口。

4.

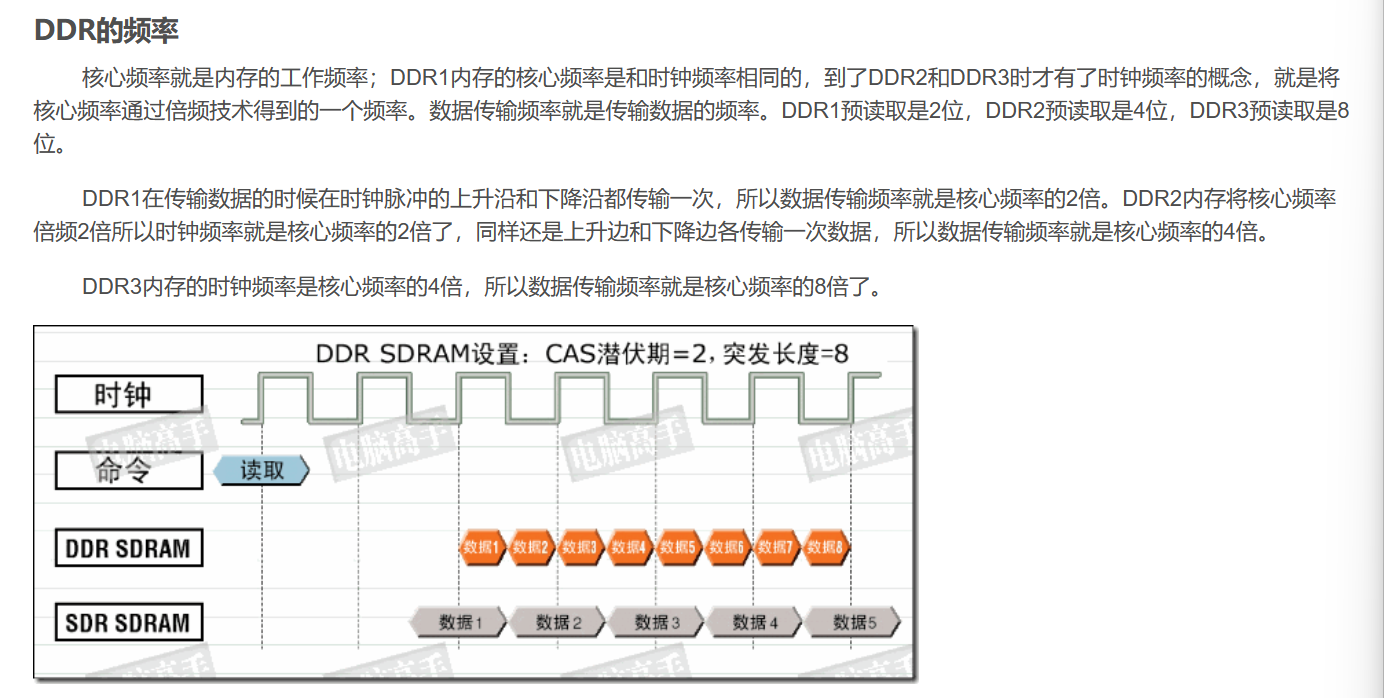

DDR的时钟速率

时序标准

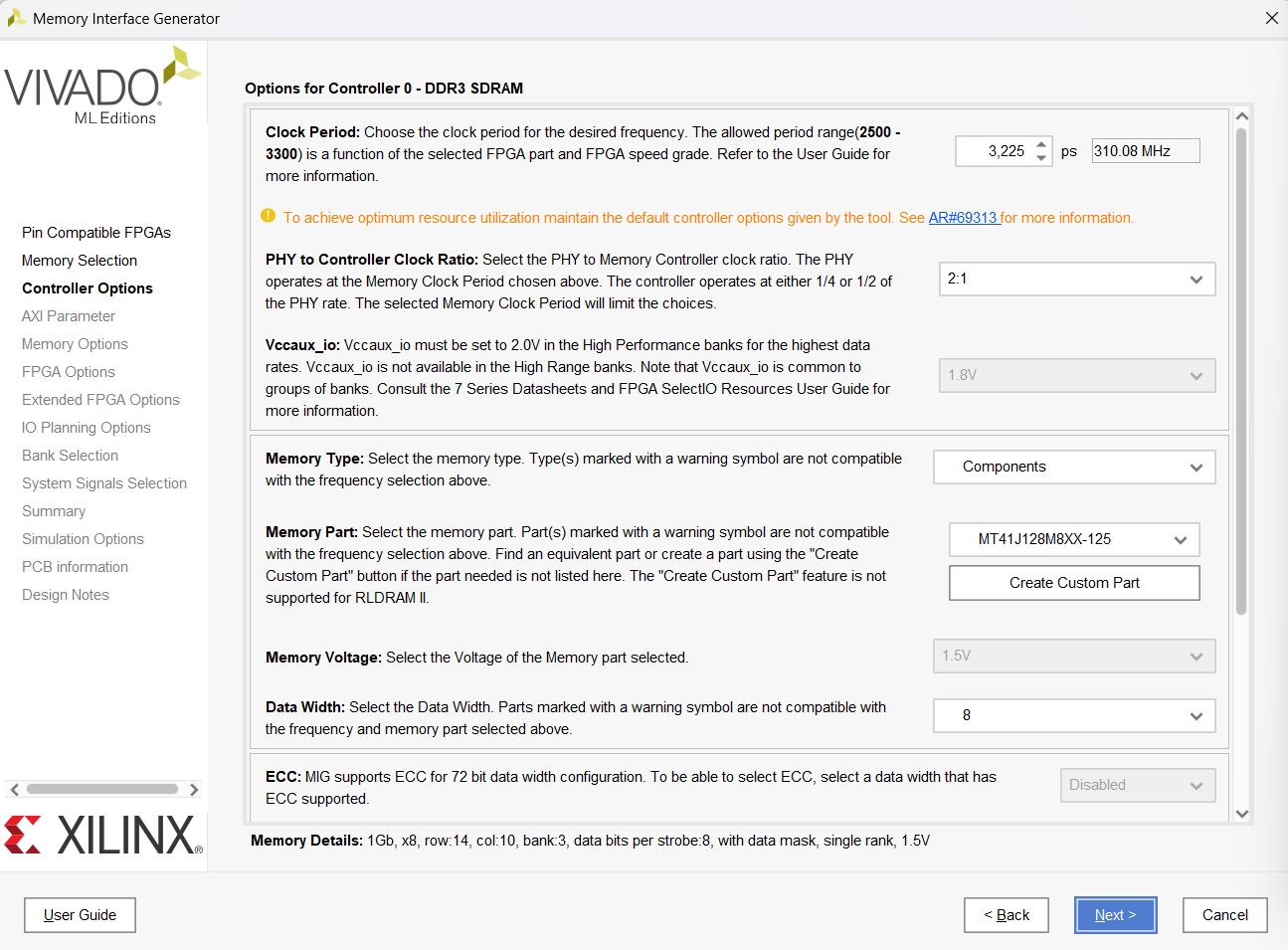

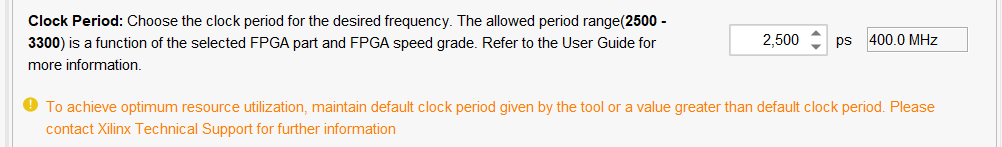

时钟周期:选择所需频率的时钟周期。允许的周期范围(2500 -3300)是所选 FPGA 部件和 FPGA 速度等级的函数。请参阅用户指南了解更多信息。

所以此处配置的实际上是时钟频率。

Clock Period

①Clock Period设置的参数就是 MIG 的PHY 接口对DDR3的时钟,也就是DDR3芯片实际跑的IO时钟频率,它由system clock(主时钟)倍频而来,最大频率不能超过DDR3 和MIG支持的最大频率中的最小值。

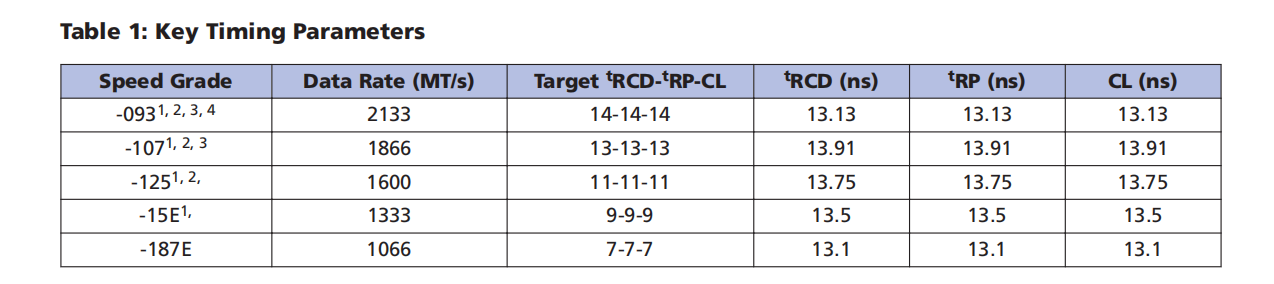

器件名称:MT41J128M16JT-125:K

tCK = 1.25ns,就可以算出芯片支持的最大IO时钟频率:1/1.25ns = 800Mhz;此处的IO时钟频率也就是DDR3的频率。

双边沿都发送,所以数据传输速率:1600M。

虽然DDR3器件最大支持800MHZ。

虽然DDR3器件最大支持800MHZ。

但是A7只支持800MHZ的PHY(数据传输速率)速率,所以工作时钟频率只能设置为400MHZ,但是K7可以支持1600MHZ的PHY所以可以设置为1250PS = 1.25NS。

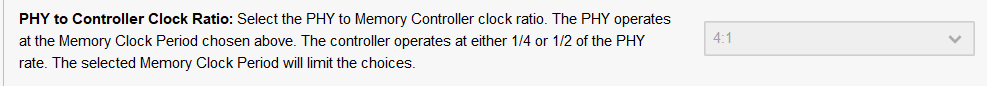

PHY 与控制器时钟比率:(低于 350M 才可选)

选择 PHY 与内存控制器时钟比率。 PHY 以上面选择的内存时钟周期运行。控制器以 PHY 速率的 1/4 或 1/2 运行。所选的内存时钟周期将限制选择。

PHY to Controller Clock Ratio:DDR3 物理芯片运行时钟和 MIG IP 核的用户端(FPGA)的时钟之比, 一般有 4:1 和 2:1 两个选项,本次实验选 4:1。由于 DDR 芯片的运行时钟是 400Mhz,因此 MIG IP 核的用户时钟(ui_clk)就是 100Mhz。一般来说高速传输的场合选择 4:1,要求低延时的场合选择 2:1。这里还要指 出,当 DDR3 时钟选择选择了 350M 到最高的 400M,比例默认只为 4:1,低于 350M 才有 4:1 和 2:1 两个选 项。

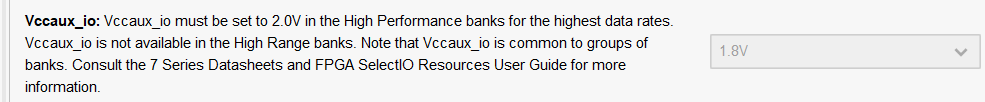

Vccaux_io

在高性能组中,Vccaux_io 必须设置为 2.0V,以获得最高数据速率。Vccaux_io 在高范围组中不可用。请注意,Vccaux_io 对于Bank组来说是通用的。有关更多信息,请参阅 7 系列数据表和 FPGA SelectIlO 资源用户指南。

这是 FPGA 高性能 bank(High Performance bank)的供电电压。它的设置取决于 MIG 控制器运行的周期/频率。当用户让控制器工作在最快频率的时候,系统会默认为 1.8V,当然在 1.8V 下用 户可以运行低一点的频率。本实验默认 1.8V。

内存类型:

选择内存类型。标有警告符号的类型与上述频率选择不兼容。

内存部分:

选择内存部分。标有警告符号的部分与上述频率选择不兼容。如果此处未列出所需的部件,请查找等效部件或使用“创建自定义部件”按钮创建部件。RLDRAM II 不支持“创建自定义部件”功能。

根据实际需求选择。

数据位宽

同样根据实际需求选择。

实在找不到自己翻手册配。

ECC:ECC 校验使能

MIG 支持 72 位数据宽度配置的 ECC。为了能够选择 ECC,请选择支持 ECC 的数据宽度。

数据位宽为 72 位的时候才能使用。

Data Mask:数据掩码

使用此复选框启用或禁用数据掩码 (DM) 引脚的生成。仅当所选存储器部分具有 DM 引脚时才可选择此选项。取消选中此框可不使用数据掩码并保存用于 DM 信号的 FPGAIO。 ECC 设计(DDR3 SDRAM、DDR2 SDRAM)不会使用数据掩码。

数据屏蔽管脚使能。勾选它才会产生屏蔽信号。

Number of Bank Machines:

Bank Machine 的数量是用来对具体的每个或某几个来单独控制的,选择多 了控制效率就会高,相应的占用的资源也多,本实验选择 4 个,平均一个 Bank Machine 控制两个 BANK

(本次实验的 DDR3 芯片是八个 bank)。

ORDERING:

该信号用来决定 MIG 控制器是否可以对它收到的指令进行重新排序,选择 Normal 则允 许,Strict 则禁止。本实验选择 Normal,从而获得更高效率。

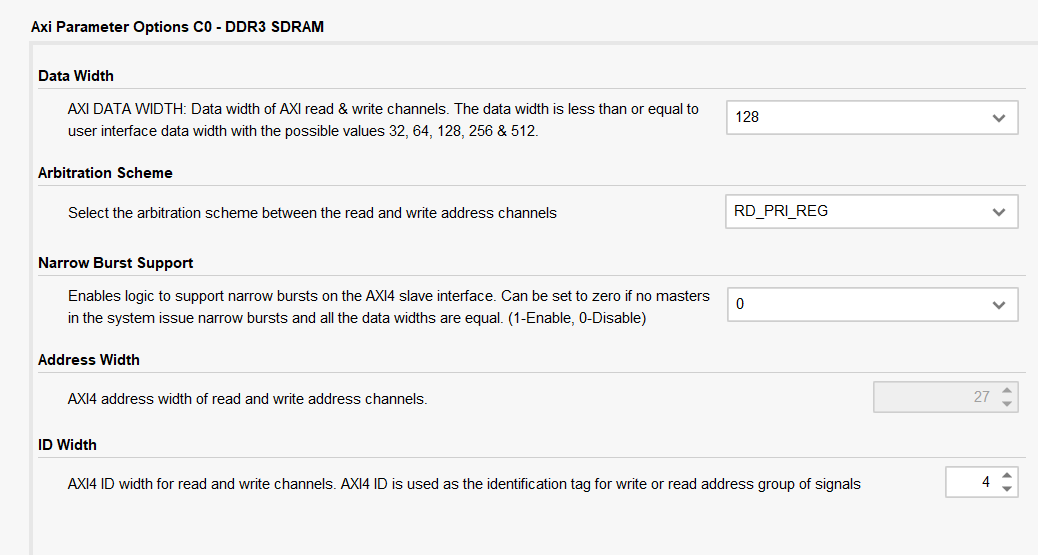

第四部分 Axi 参数配置

数据宽度

AXI DATA WIDTH:AXl 读写通道的数据宽度。

数据宽度小于或等于用户接口数据宽度,可能值为 32,64,128,256&512。

仲裁方案

选择读写地址通道之间的仲裁方案

窄突发支持

使逻辑能够支持 AXl4 从接口上的窄突发。如果系统中没有主机发出窄突发并且所有数据宽度都相等,则可以设置为零。 (1-启用,0-禁用)

地址宽度

AXI4 读写地址通道的地址宽度。

ID 宽度

AXI4 读写通道的 ID 宽度。 AX4 ID用作写入或读取信号组地址的识别标签

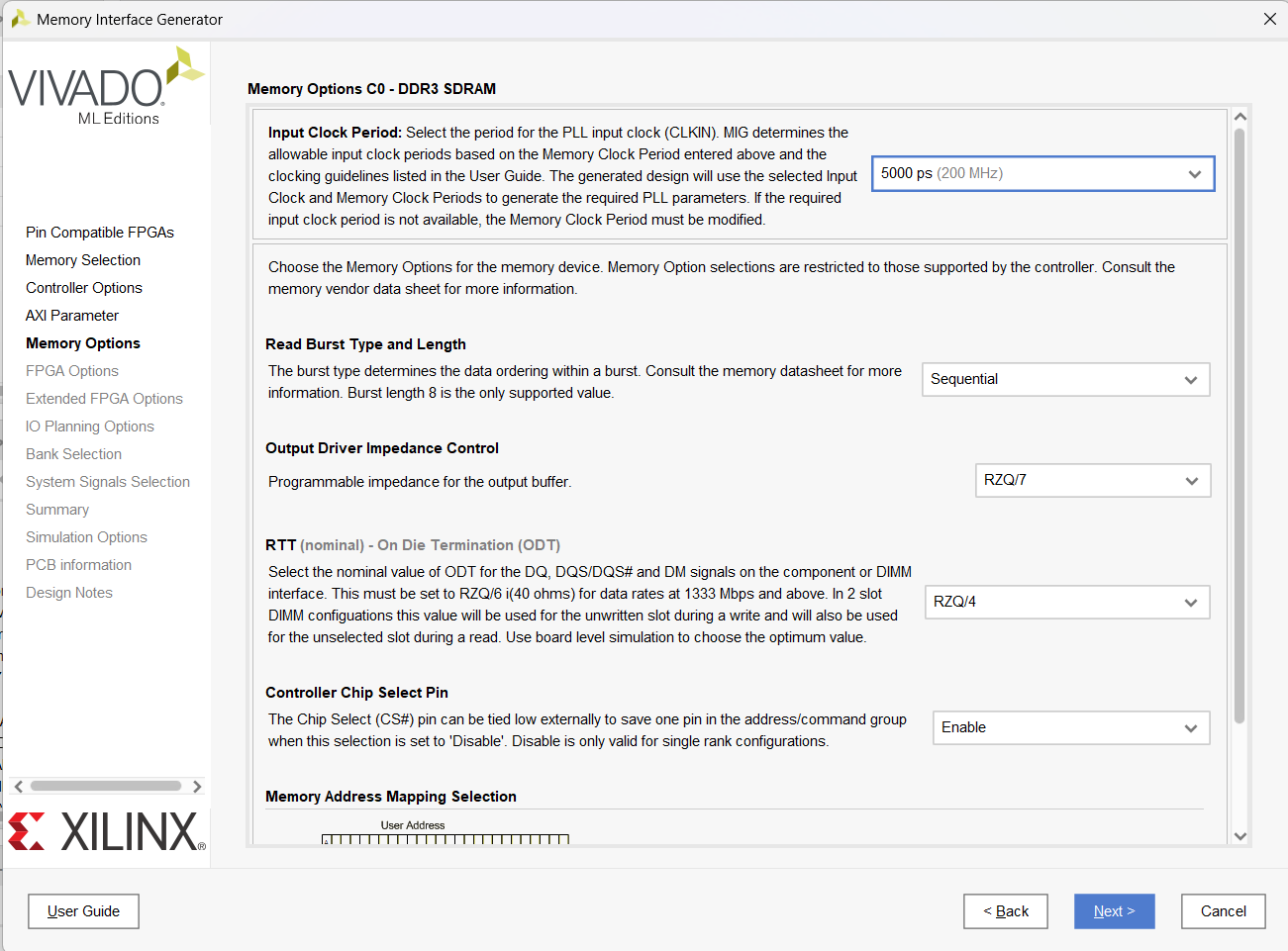

第五部分 存储器配置

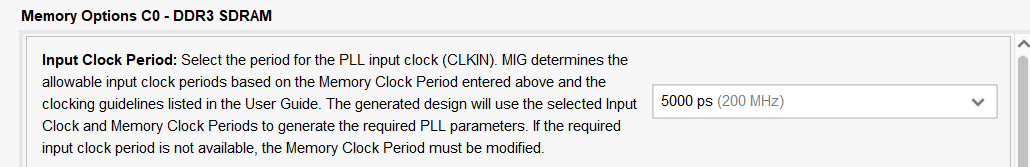

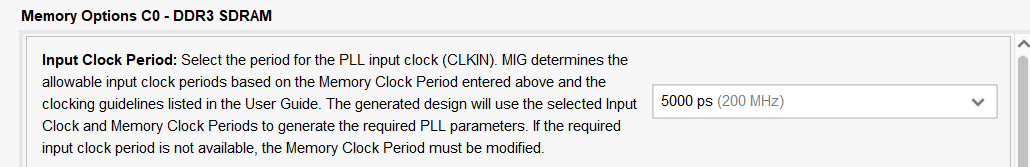

输入时钟周期:(重要)

选择 PLL 输入时钟 (CLKIN) 的周期。MIG 根据上面输入的内存时钟周期和用户指南中列出的时钟指南确定允许的输入时钟周期。生成的设计将使用选定的输入时钟和内存时钟周期来生成所需的 PLL 参数。如果所需的输入时钟周期不可用,则必须修改内存时钟周期。

MIG内部有PLL用来完成从输入时钟频率到DDR3工作频率的倍频。

推荐选择200Mhz,因为参考时钟也是200Mhz,配置的时候参考时钟可以直接使用系统时钟,减少端口信号。

Read Burst Type and Length:

突发类型决定突发内的数据排序。有关详细信息,请参阅内存数据表。突发长度 8 是唯一受支持的值。(基本没人用交叉,到底是谁在用呢)

突发类型选择,突发类型有顺序突发和交叉突发两种,本实验选择

顺序突发(Sequential),其突发长度固定为 8。

Output Driver Impdance Control:

输出阻抗控制。本实验选择 RZQ/7。

RTT(标称) - 片上端接 (ODT)~终结电阻,可进行动态控制。

选择组件或 DIMM 接口上 DQ、DQS/DQS# 和 DM 信号的 ODT 标称值。对于数据速率,必须将其设置为 RZQ/6 i(40 欧姆) 1333 Mbps 及以上。在 2 插槽 DIMM 配置中,该值将用于写入期间未写入的插槽,也将用于读取期间未选择的插槽。使用板级仿真来选择最佳值。

Controller Chip Select Pin:

片选管脚引出使能。本实验选择 enable,

当此选择设置为“禁用”时,片选 (CS#) 引脚可在外部连接为低电平,以在地址/命令组中保存一个引脚。禁用仅对单列配置有效。

实际上DDR3或者说SDRAM的所有指令,包括NOP下,CS_N都设置为0,这里默认为0可以省略一个管脚。

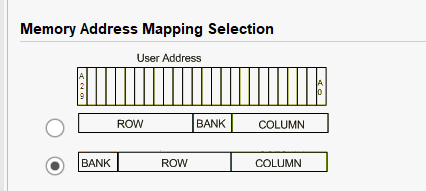

寻址方式选择

BANK_ROW_COLUMN:

寻址方式选择。本实验选择第二种,即 BANK-ROW-COLUMN 的形式,这是一种最常规的 DDR3 寻址方式,即要指定某个地址,先指定 bank,再指定行,最后指定列,这样就确定 了一个具体地址。

一般来说这样寻址方式有利于降低功耗,但是读写性能(效率)上不如 “ROW_BANK_COLUMN”。

第六部分 FPGA配置

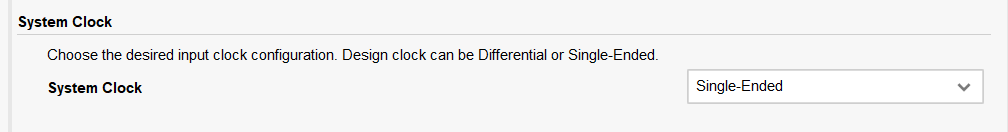

System Clock类型:

MIG IP核输入给内部PLL的时钟类型,就是上一部分这个。/

可选择“No Buffer”,直接选单端时钟是默认有buffer?

因为IP核的输入系统时钟是单端时钟, 是由内部的MMCM产生的,MMCM所产生的时钟默认添加了buffer。

Reference Clock参考时钟类型:

MIG IP 核参考时钟。同样可选择“No Buffer”,将由时钟模块生成,IP 核参考时钟要求是 200Mhz。如果之前在:

使用了 200Mhz 的系统时钟,则参考时钟就可以直接使用系统时钟(use system clock)

System Reset Polarity:

复位有效电平选择。

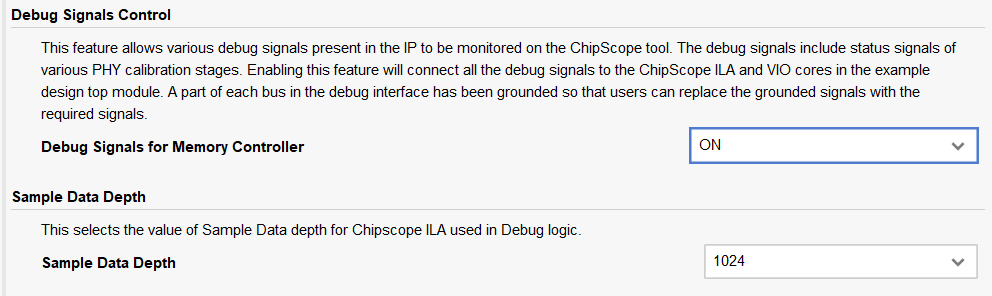

Sample Data Depth:采样深度选择。

此功能允许在 ChipScope 工具上监视 IP 中存在的各种调试信号。

调试信号包括各个 PHY 校准阶段的状态信号。启用此功能会将所有调试信号连接到 exampledesign 顶部模块中的 ChipScope ILA 和 VIO 内核。

调试接口中每条总线都有部分接地,用户可以将接地信号替换为所需的信号。

当“Debug Signals Control”选择“OFF”时,所有采样深度是不可选的。

Internal Vref:

内部参考管脚,表示将某些参考管脚当成普通的输入管脚来用。

由于开发板的 IO 资源 较为紧张,这里需要选择“ON”,把参考管脚当做普通的输入管脚来用。

内部 Vref 可用于允许将 Vref 引脚用作普通 IO 引脚。该选项只能在 800 Mbps 和更低的数据速率下使用。这可以为每个使用输入的组释放 2 个引脚。此设置对仅具有输出的组没有影响。

IO Power Reduction:管脚节能

IO 管脚节省功耗设置。选择“ON”,即开启。

通过在写入期间和不活动期间自动禁用 DQ/DQS IBUF 和内部终止,显着降低平均 IO 功率

XADC Instantiation:温度补偿

XADC 模块例化。使用 MIG IP 核运行的时候需要进行温度补偿,可以直接选择 XADC 模块的温度数据引到 MIG IP 核来使用,否则需要额外提供温度数据,选择“Enable”。

存储器接口使用 XADC 块的温度读数来执行温度补偿,并使读数在数据窗口中保持居中。每个设备有一个 XADC 块,如果 XADC 当前未在设计中的任何地方使用,请启用此选项以拥有该块实例化。

如果已使用 XADC,请禁用此 MIG 选项。

然后,用户需要向顶级 12 位 device_temp_i 输入端口提供温度值。有关详细信息,请参阅答复记录 51687 或 UG586。

第七部分 内部高性能 bank 端接匹配阻抗

选择高范围 (HR) 组的内部终端 (N_TERM) 阻抗。

此设置仅适用于界面中使用的 HR BANK。内部终端阻抗 50 Ohms

第八部分 管脚模式选择

如果选择第二种则可以直接导入。

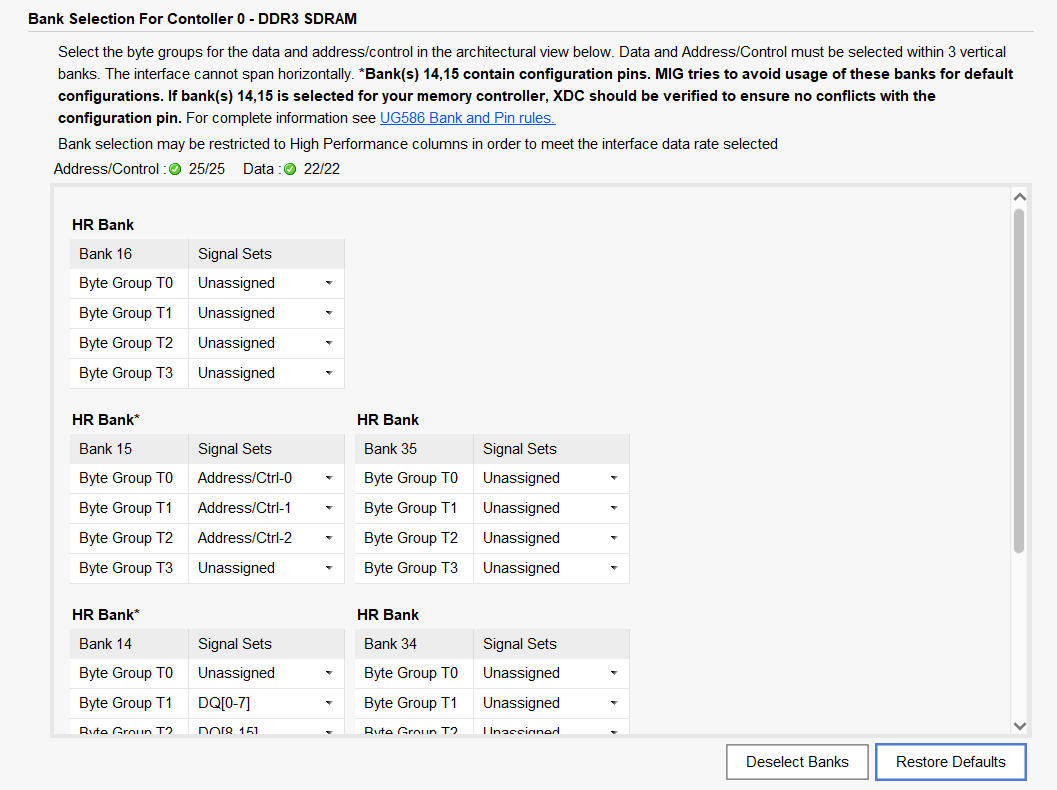

第九部分 BANK选择

第八部分选择了第一种的情况下:

在下面的架构视图中选择数据和地址控制的字节组。

数据和地址控制必须在 3 个垂直组内选择。接口不能水平跨越。

“Bank/s) 14,15 包含配置引脚。MlG 尝试避免使用这些 Bank 进行默认配置。如果为内存控制器选择了 Bank(s) 14,15,则应验证 XDC 以确保与配置引脚不发生冲突。

有关完整信息,请参阅 UG586 Bank 和 Pin 规则。

Bank 选择可能仅限于高性能列,以满足所选的接口数据速率

第二种:

导入后则直接跳到倒数第二步。

相关文章:

XIlinx提供的DDR3 IP与 UG586

DDR系统需要关注的三样东西:控制器、PHY、SDRAM颗粒,但这是实现一个DDR3 IP所需要的,如果只希望调用IP的话,则只需要调用IP即可,目前时间紧急,我先学一学如何使用IP,解决卡脖子的问题࿰…...

C++数据结构X篇_19_排序基本概念及冒泡排序(重点是核心代码)

文章目录 1. 排序基本概念2. 冒泡排序2.1 核心代码2.2 冒泡排序代码2.3 查看冒泡排序的时间消耗2.4 冒泡排序改进版减小时间消耗 1. 排序基本概念 现实生活中排序很重要,例如:淘宝按条件搜索的结果展示等。 概念 排序是计算机内经常进行的一种操作,其目…...

LeetCode LCR 179. 查找总价格为目标值的两个商品

和为 s 的两个数字 题目链接 LCR 179. 查找总价格为目标值的两个商品 购物车内的商品价格按照升序记录于数组 price。请在购物车中找到两个商品的价格总和刚好是 target。若存在多种情况,返回任一结果即可。 示例 1: 输入:price [3, 9, 12, …...

上架用的SDK三方应用隐私

SDK名称:华为推送 使用目的:用于向华为手机用户推送消息 使用场景:用户账号相关促销活动、消息提醒更新时 信息收集类型:设备相关信息(Android_ID)使用的敏感权限:不涉及 使用的敏感权限&am…...

从REST到GraphQL:升级你的Apollo体验

前言 「作者主页」:雪碧有白泡泡 「个人网站」:雪碧的个人网站 「推荐专栏」: ★java一站式服务 ★ ★ React从入门到精通★ ★前端炫酷代码分享 ★ ★ 从0到英雄,vue成神之路★ ★ uniapp-从构建到提升★ ★ 从0到英雄ÿ…...

Jupyter使用技巧-环境篇

不同于其他IDE,有时会出现找不到文件路径,通常是因为当前工作目录(working directory)不同所导致的。Jupyter Notebook 会在启动时选择一个初始的工作目录,而这个目录可能与你运行 .py 文件时所在的目录不同。 import…...

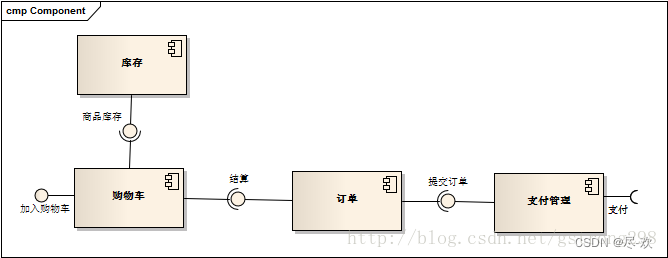

软件项目管理【UML-组件图】

目录 一、组件图概念 二、组件图包含的元素 1.组件(Component)->构件 2.接口(Interface) 3.外部接口——端口 4.连接器(Connector)——连接件 4.关系 5.组件图表示方法 三、例子 一、组件图概念…...

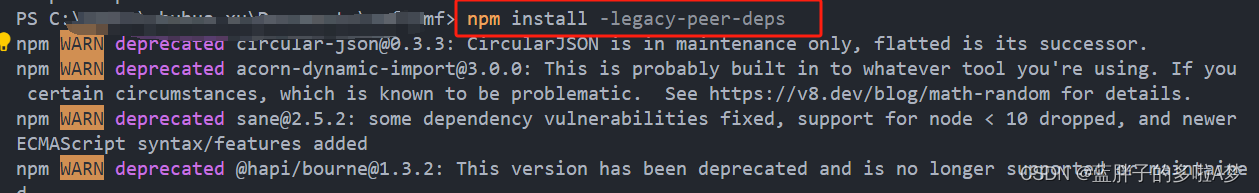

npm版本错误——npm ERR! code ERESOLVE 解决方法

起因 项目中echart版本过低,导致某些图表不能正确显示,所以大手一挥,将echart版本从4升级到了5, 再去运行项目的时候 就发现项目报错了 npm ERR! code ERESOLVE npm ERR! ERESOLVE unable to resolve dependency tree npm ERR! …...

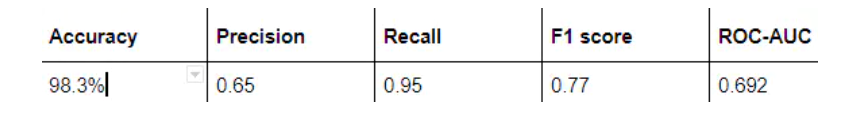

基于卷积神经网络的乳腺癌分类 深度学习 医学图像 计算机竞赛

文章目录 1 前言2 前言3 数据集3.1 良性样本3.2 病变样本 4 开发环境5 代码实现5.1 实现流程5.2 部分代码实现5.2.1 导入库5.2.2 图像加载5.2.3 标记5.2.4 分组5.2.5 构建模型训练 6 分析指标6.1 精度,召回率和F1度量6.2 混淆矩阵 7 结果和结论8 最后 1 前言 &…...

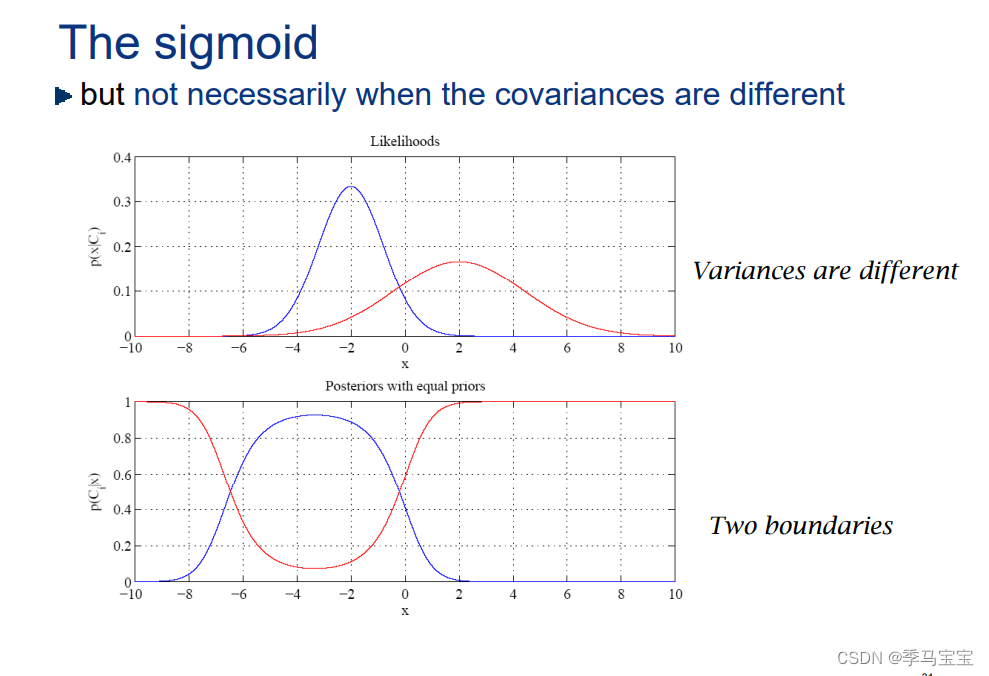

模式识别——高斯分类器

模式识别——高斯分类器 需知定义特殊情况(方差一致)Sigmoid 需知 所有问题定义在分类问题下,基于贝叶斯决策 定义 条件概率为多元高斯分布,此时观测为向量 X X 1 , X 2 , . . . , X n X{X_1,X_2,...,X_n} XX1,X2,...,Xn…...

LeetCode 15. 三数之和

三数之和 题目链接 15. 三数之和 给你一个整数数组 nums ,判断是否存在三元组 [nums[i], nums[j], nums[k]] 满足 i ! j、i ! k 且 j ! k ,同时还满足 nums[i] nums[j] nums[k] 0 。请 你返回所有和为 0 且不重复的三元组。 **注意:**答案…...

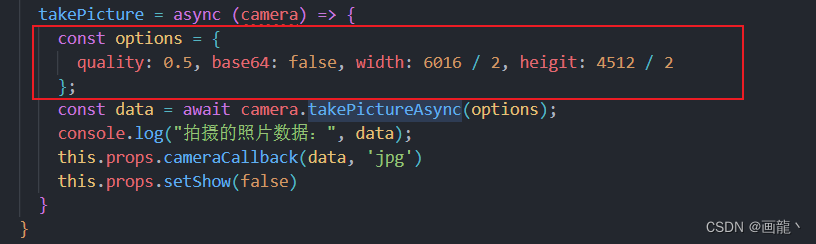

React-native-camera 在小米手机上拍照查看闪退

场景:为实现可拍照和录像的相机用react-native-camera这个库手写一个相机,发现了拍出来的图片在小米10上查看闪退 根据手机后台捕获的错误信息是什么玩意太大了(之前还以为是图片显示组件的问题) 改进:相机吊起的时候…...

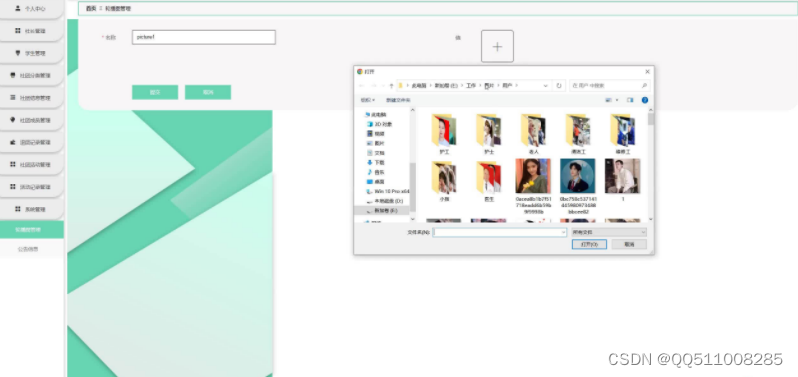

nodejs+vue大学生社团管理系统

通过软件的需求分析已经获得了系统的基本功能需求,根据需求,将大学生社团管理系统平台功能模块主要分为管理员模块。管理员添加社团成员管理、社团信息管理,社长管理、用户注册管理等操作。 目 录 摘 要 I ABSTRACT II 目 录 II 第1章 绪论 1…...

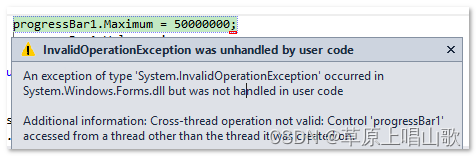

异步编程详解(.NET)

在之前写的一篇关于async和await的前世今生的文章之后,大家似乎在async和await提高网站处理能力方面还有一些疑问,很多网站本身也做了不少的尝试。今天我们再来回答一下这个问题,同时我会做一个async和await在WinForm中的尝试,并且…...

excel怎么固定前几行前几列不滚动?

在Excel中,如果你想固定前几行或前几列不滚动,可以通过以下几种方法来实现。详细的介绍如下: **固定前几行不滚动:** 1. 选择需要固定的行数。例如,如果你想要固定前3行,应该选中第4行的单元格。 2. 在E…...

elasticsearch完整学习

文章目录 elasticsearch一、概念二、ELK集群部署三、图形化界面 elasticsearch 一、概念 1、ELKStack简介(都是java架构,需要jdk底层) 什么是ELK?通俗来讲,ELK是由Elasticsearch、Logstash、Kibana 三个开源软件组成的…...

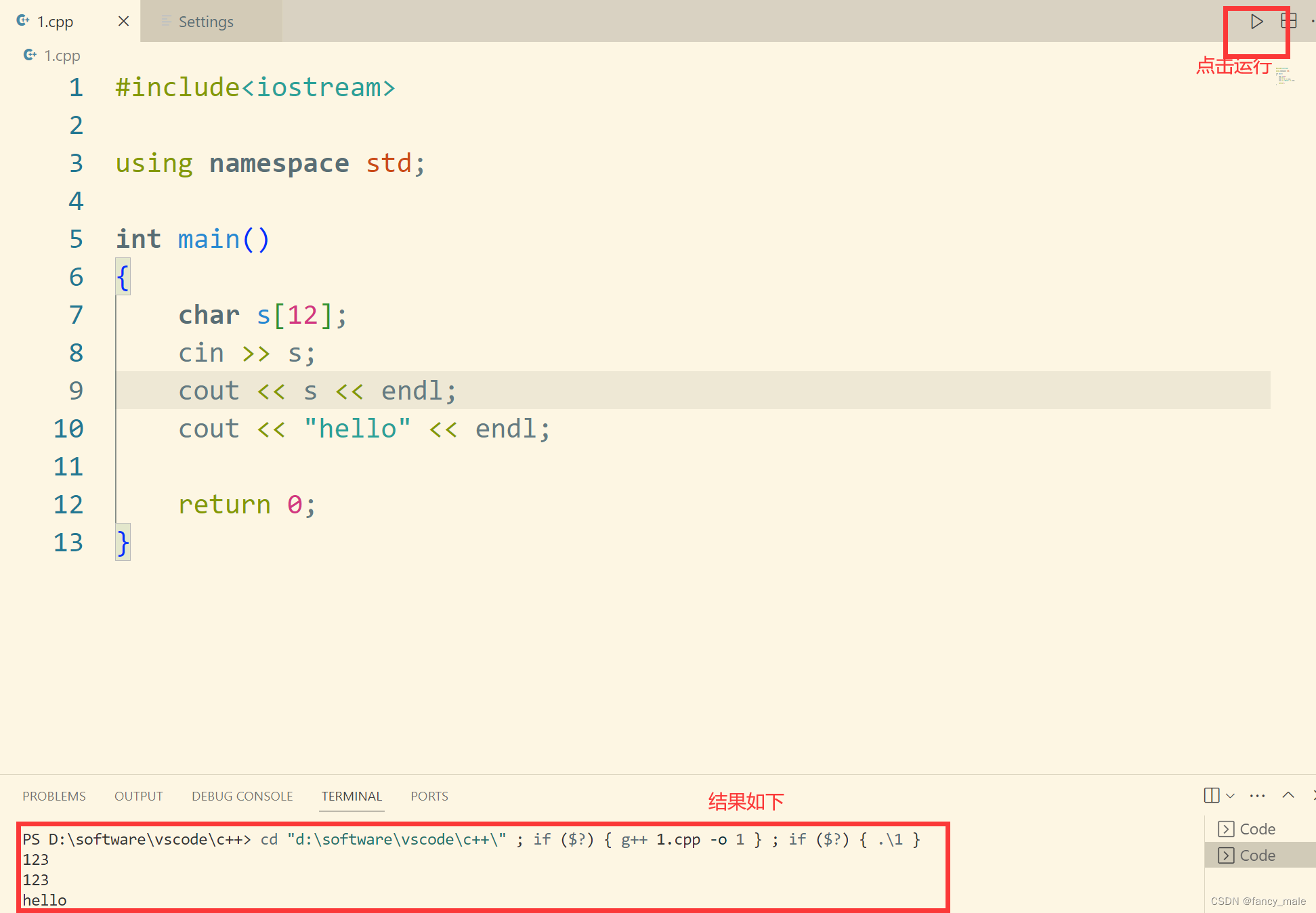

vscode Coder Runner 运行C++

1. 设置Code Runner 2. 防止输入读不到,把在终端运行勾上。 3. 设置minw/bin的环境变量 安装mingw教程:https://blog.csdn.net/fancy_male/article/details/133992000 4. 见图...

牛客网刷题-(2)

🌈write in front🌈 🧸大家好,我是Aileen🧸.希望你看完之后,能对你有所帮助,不足请指正!共同学习交流. 🆔本文由Aileen_0v0🧸 原创 CSDN首发🐒 如…...

FreeRTOS基础(如何学好FreeRTOS?)

目录 基础知识 进阶内容 后期“摆烂” 基础知识 实时操作系统 (RTOS):FreeRTOS是一个实时操作系统,它提供了任务管理、调度和同步等功能,在嵌入式系统中有效地管理多个任务。 任务(Task):任务是在RTOS…...

、条款44(概念明确)、条款45-50(杂项))

读书笔记:Effective C++ 2.0 版,条款43(多继承)、条款44(概念明确)、条款45-50(杂项)

条款43: 明智地使用多继承 并没有禁止,从概念上讲,多继承可能更符合真实世界。 条款44: 说你想说的;理解你所说的 概念明确 条款45: 弄清C在幕后为你所写、所调用的函数 隐性成本,看下编译后的c、asm源码。 条款46: 宁可编译和…...

变量 varablie 声明- Rust 变量 let mut 声明与 C/C++ 变量声明对比分析

一、变量声明设计:let 与 mut 的哲学解析 Rust 采用 let 声明变量并通过 mut 显式标记可变性,这种设计体现了语言的核心哲学。以下是深度解析: 1.1 设计理念剖析 安全优先原则:默认不可变强制开发者明确声明意图 let x 5; …...

[2025CVPR]DeepVideo-R1:基于难度感知回归GRPO的视频强化微调框架详解

突破视频大语言模型推理瓶颈,在多个视频基准上实现SOTA性能 一、核心问题与创新亮点 1.1 GRPO在视频任务中的两大挑战 安全措施依赖问题 GRPO使用min和clip函数限制策略更新幅度,导致: 梯度抑制:当新旧策略差异过大时梯度消失收敛困难:策略无法充分优化# 传统GRPO的梯…...

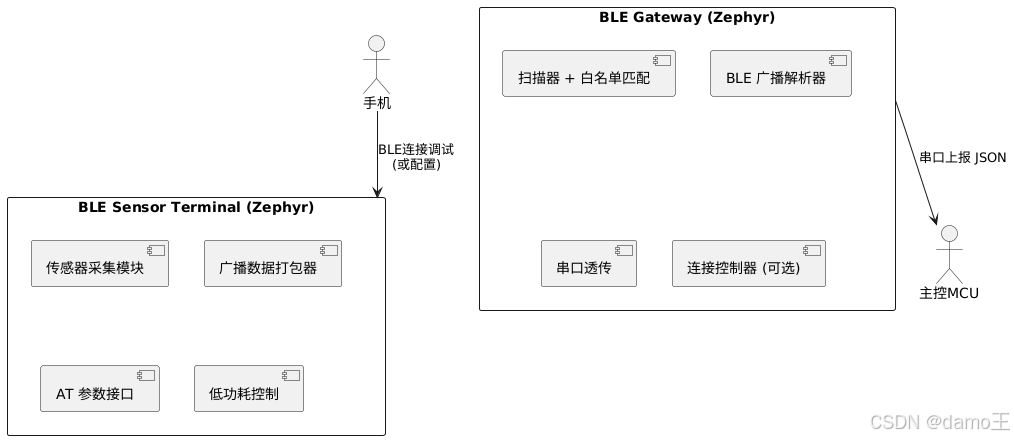

【Zephyr 系列 10】实战项目:打造一个蓝牙传感器终端 + 网关系统(完整架构与全栈实现)

🧠关键词:Zephyr、BLE、终端、网关、广播、连接、传感器、数据采集、低功耗、系统集成 📌目标读者:希望基于 Zephyr 构建 BLE 系统架构、实现终端与网关协作、具备产品交付能力的开发者 📊篇幅字数:约 5200 字 ✨ 项目总览 在物联网实际项目中,**“终端 + 网关”**是…...

leetcodeSQL解题:3564. 季节性销售分析

leetcodeSQL解题:3564. 季节性销售分析 题目: 表:sales ---------------------- | Column Name | Type | ---------------------- | sale_id | int | | product_id | int | | sale_date | date | | quantity | int | | price | decimal | -…...

聊一聊接口测试的意义有哪些?

目录 一、隔离性 & 早期测试 二、保障系统集成质量 三、验证业务逻辑的核心层 四、提升测试效率与覆盖度 五、系统稳定性的守护者 六、驱动团队协作与契约管理 七、性能与扩展性的前置评估 八、持续交付的核心支撑 接口测试的意义可以从四个维度展开,首…...

蓝桥杯 冶炼金属

原题目链接 🔧 冶炼金属转换率推测题解 📜 原题描述 小蓝有一个神奇的炉子用于将普通金属 O O O 冶炼成为一种特殊金属 X X X。这个炉子有一个属性叫转换率 V V V,是一个正整数,表示每 V V V 个普通金属 O O O 可以冶炼出 …...

Spring是如何解决Bean的循环依赖:三级缓存机制

1、什么是 Bean 的循环依赖 在 Spring框架中,Bean 的循环依赖是指多个 Bean 之间互相持有对方引用,形成闭环依赖关系的现象。 多个 Bean 的依赖关系构成环形链路,例如: 双向依赖:Bean A 依赖 Bean B,同时 Bean B 也依赖 Bean A(A↔B)。链条循环: Bean A → Bean…...

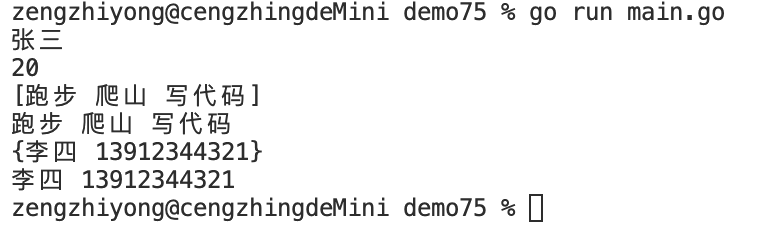

Golang——7、包与接口详解

包与接口详解 1、Golang包详解1.1、Golang中包的定义和介绍1.2、Golang包管理工具go mod1.3、Golang中自定义包1.4、Golang中使用第三包1.5、init函数 2、接口详解2.1、接口的定义2.2、空接口2.3、类型断言2.4、结构体值接收者和指针接收者实现接口的区别2.5、一个结构体实现多…...

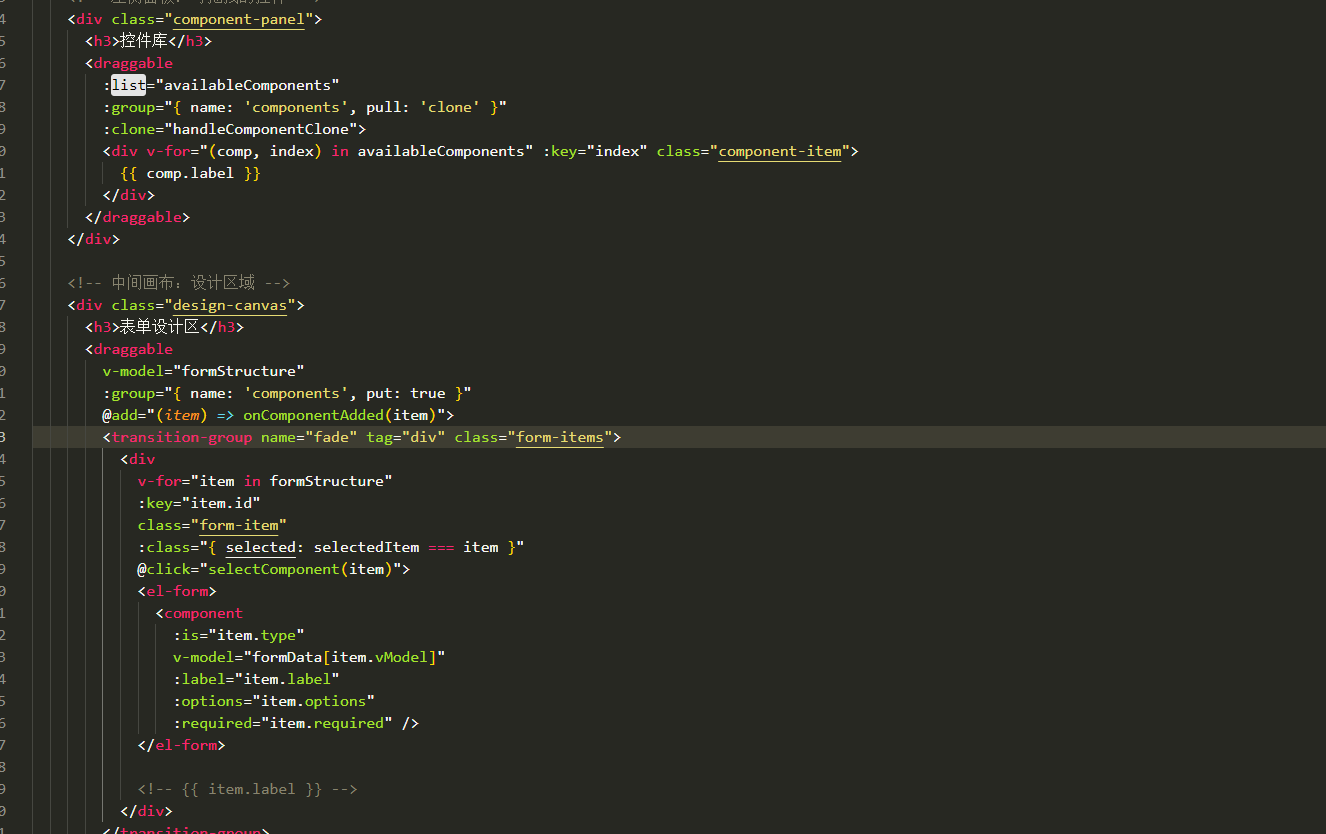

表单设计器拖拽对象时添加属性

背景:因为项目需要。自写设计器。遇到的坑在此记录 使用的拖拽组件时vuedraggable。下面放上局部示例截图。 坑1。draggable标签在拖拽时可以获取到被拖拽的对象属性定义 要使用 :clone, 而不是clone。我想应该是因为draggable标签比较特。另外在使用**:clone时要将…...

)

零基础在实践中学习网络安全-皮卡丘靶场(第十一期-目录遍历模块)

经过前面几期的内容我们学习了很多网络安全的知识,而这期内容就涉及到了前面的第六期-RCE模块,第七期-File inclusion模块,第八期-Unsafe Filedownload模块。 什么是"遍历"呢:对学过一些开发语言的朋友来说应该知道&…...