【计算机组成与设计】Chisel取指和指令译码设计

本次试验分为三个部分:

目录

设计译码电路

设计寄存器文件

实现一个32个字的指令存储器

设计译码电路

输入位32bit的一个机器字,按照课本MIPS 指令格式,完成add、sub、lw、sw指令译码,其他指令一律译码成nop指令。输入信号名为Instr_word,对上述四条指令义译码输出信号名为add_op、sub_op、lw_op和sw_op,其余指令一律译码为nop;

给出Chisel设计代码和仿真测试波形,观察输入Instr_word为add R1,R2,R3; sub R0,R5,R6,lw R5,100(R2), sw R5,104(R2)、JAL RA,100(R2)时,对应的输出波形

Decode.scala

import chisel3._class Decoder extends Module {val io = IO(new Bundle {val Instr_word = Input(UInt(32.W))val add_op = Output(Bool())val sub_op = Output(Bool())val lw_op = Output(Bool())val sw_op = Output(Bool())val nop_op = Output(Bool())})// 定义操作码val OPCODE_ADD = "b000000".Uval OPCODE_SUB = "b000000".Uval OPCODE_LW = "b100011".Uval OPCODE_SW = "b101011".U//定义功能码val FUNCT_ADD = "b100000".Uval FUNCT_SUB = "b100010".U// 提取MIPS指令的操作码val opcode = io.Instr_word(31, 26)//提取MIPS指令的功能码val funct = io.Instr_word(5, 0)// 译码io.add_op := opcode === OPCODE_ADD && funct === FUNCT_ADDio.sub_op := opcode === OPCODE_SUB && funct === FUNCT_SUBio.lw_op := opcode === OPCODE_LWio.sw_op := opcode === OPCODE_SWio.nop_op := !(io.add_op || io.sub_op || io.lw_op || io.sw_op)

}object Decoder extends App {(new chisel3.stage.ChiselStage).emitVerilog(new Decoder())

}

DecoderTest.scala

import chiseltest._

import org.scalatest.flatspec.AnyFlatSpec

import chisel3._class DecoderTest extends AnyFlatSpec with ChiselScalatestTester {behavior of "Decoder"it should "correctly decode instructions" in {test(new Decoder).withAnnotations(Seq(WriteVcdAnnotation)) { c =>// Test instructionsval addInstruction = "b000000_00010_00011_00001_00000_100000".Uval subInstruction = "b000000_00101_00110_00000_00000_100010".Uval lwInstruction = "b100011_00010_00101_0000000001100100".Uval swInstruction = "b101011_00010_00101_0000000001101000".Uval jalInstruction = "b000011_00000_00000000000000000000".U// Set the input instruction and evaluate the decoderc.io.Instr_word.poke(addInstruction)c.clock.step()c.io.add_op.expect(true)c.io.sub_op.expect(false)c.io.lw_op.expect(false)c.io.sw_op.expect(false)c.io.nop_op.expect(false)c.io.Instr_word.poke(subInstruction)c.clock.step()c.io.add_op.expect(false)c.io.sub_op.expect(true)c.io.lw_op.expect(false)c.io.sw_op.expect(false)c.io.nop_op.expect(false)c.io.Instr_word.poke(lwInstruction)c.clock.step()c.io.add_op.expect(false)c.io.sub_op.expect(false)c.io.lw_op.expect(true)c.io.sw_op.expect(false)c.io.nop_op.expect(false)c.io.Instr_word.poke(swInstruction)c.clock.step()c.io.add_op.expect(false)c.io.sub_op.expect(false)c.io.lw_op.expect(false)c.io.sw_op.expect(true)c.io.nop_op.expect(false)c.io.Instr_word.poke(jalInstruction)c.clock.step()c.io.add_op.expect(false)c.io.sub_op.expect(false)c.io.lw_op.expect(false)c.io.sw_op.expect(false)c.io.nop_op.expect(true)}}

}

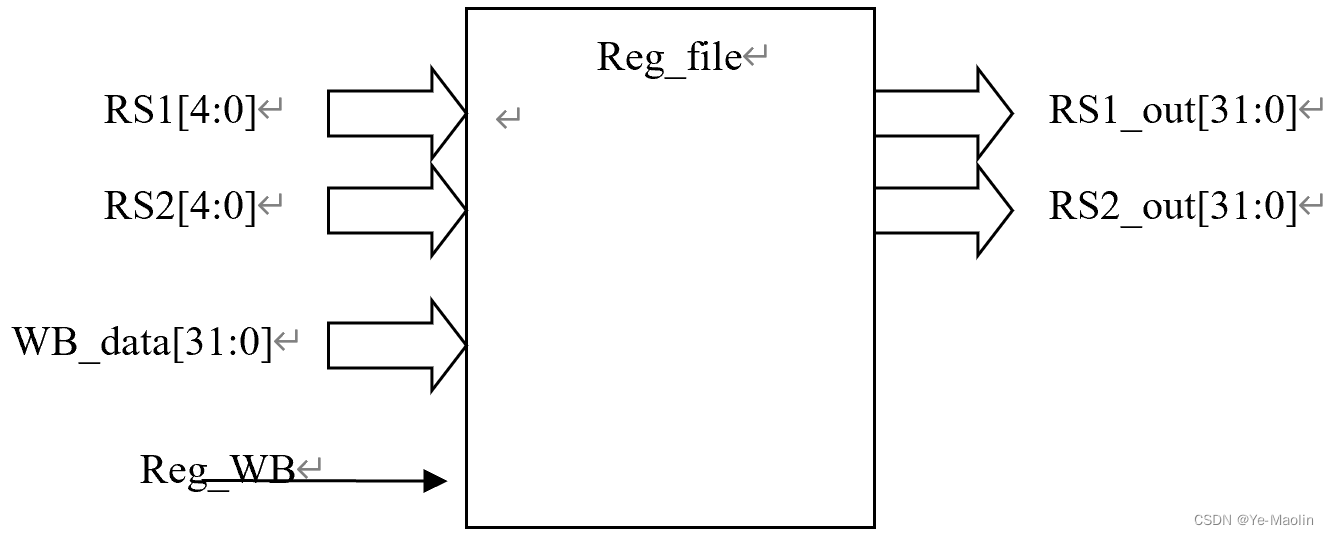

设计寄存器文件

共32个32bit寄存器,允许两读一写,且0号寄存器固定读出位0。四个输入信号为RS1、RS2、WB_data、Reg_WB,寄存器输出RS1_out和RS2_out;寄存器内部保存的初始数值等同于寄存器编号

给出Chisel设计代码和仿真测试波形,观察RS1=5,RS2=8,WB_data=0x1234,Reg_WB=1的输出波形和受影响寄存器的值。

Register.scala

import chisel3._

import chisel3.util._class RegisterFile extends Module {val io = IO(new Bundle {val RS1 = Input(UInt(5.W)) // RS1输入信号,用于选择要读取的寄存器val RS2 = Input(UInt(5.W)) // RS2输入信号,用于选择要读取的寄存器val WB_data = Input(UInt(32.W)) // 写入数据信号,用于写入寄存器val Reg_WB = Input(UInt(5.W)) // 选择写入数据的寄存器val RS1_out = Output(UInt(32.W)) // RS1输出数据val RS2_out = Output(UInt(32.W)) // RS2输出数据})val registers = RegInit(VecInit((0 until 32).map(_.U(32.W)))) // 32个32位寄存器,初始值等于寄存器编号registers(io.Reg_WB) := io.WB_data // 写入数据到寄存器io.RS1_out := Mux(io.RS1 === 0.U, 0.U, registers(io.RS1)) // RS1输出数据,0号寄存器固定读出位0io.RS2_out := Mux(io.RS2 === 0.U, 0.U, registers(io.RS2)) // RS2输出数据,0号寄存器固定读出位0

}object RegisterFile extends App {(new chisel3.stage.ChiselStage).emitVerilog(new RegisterFile())

}

RegisterTest.scala

import chisel3._

import chiseltest._

import org.scalatest.flatspec.AnyFlatSpec

import chisel3.util._class RegisterFileTest extends AnyFlatSpec with ChiselScalatestTester {behavior of "RegisterFile"it should "correctly update and read registers" in {test(new RegisterFile).withAnnotations(Seq(WriteVcdAnnotation)) { c =>// 设置输入信号c.io.RS1.poke(5.U)c.io.RS2.poke(8.U)c.io.WB_data.poke(0x1234.U)c.io.Reg_WB.poke(1.U)c.clock.step()c.io.RS1_out.expect(5.U)c.io.RS2_out.expect(8.U)}}

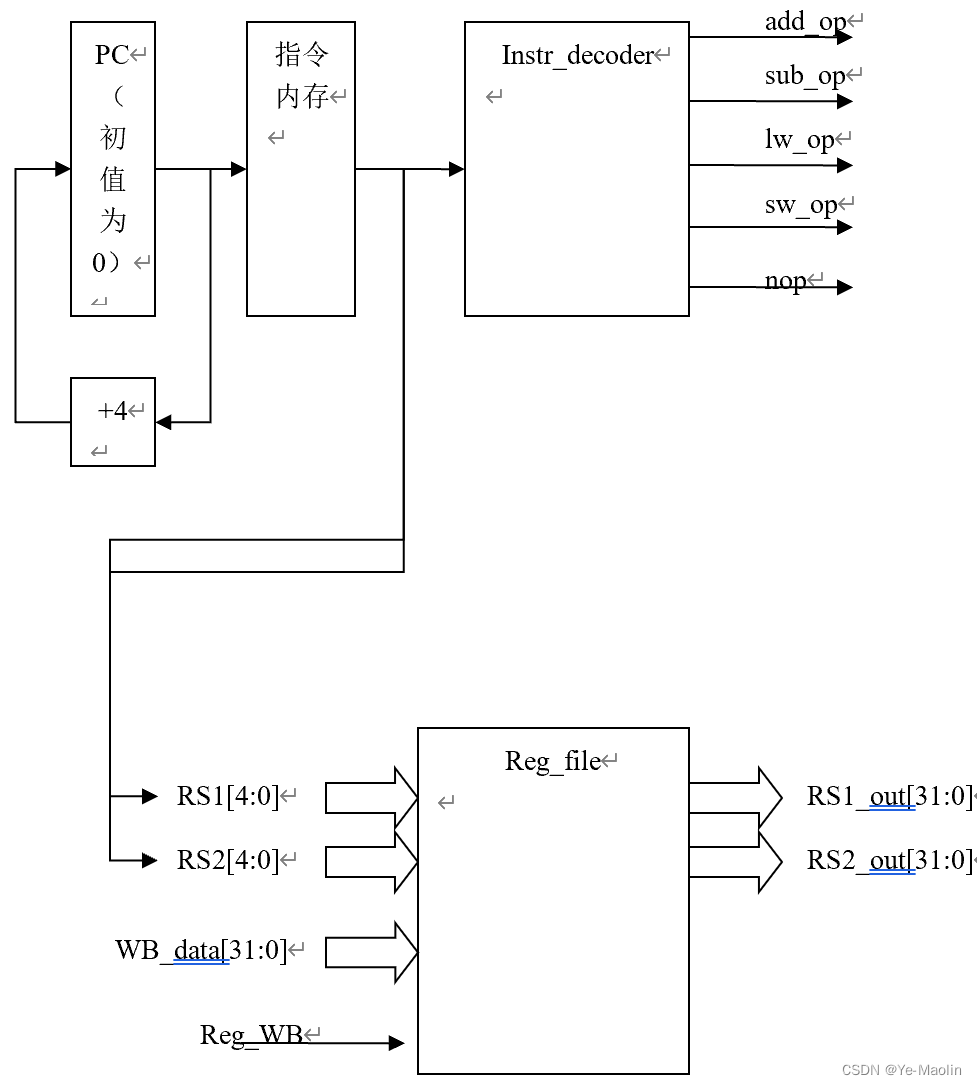

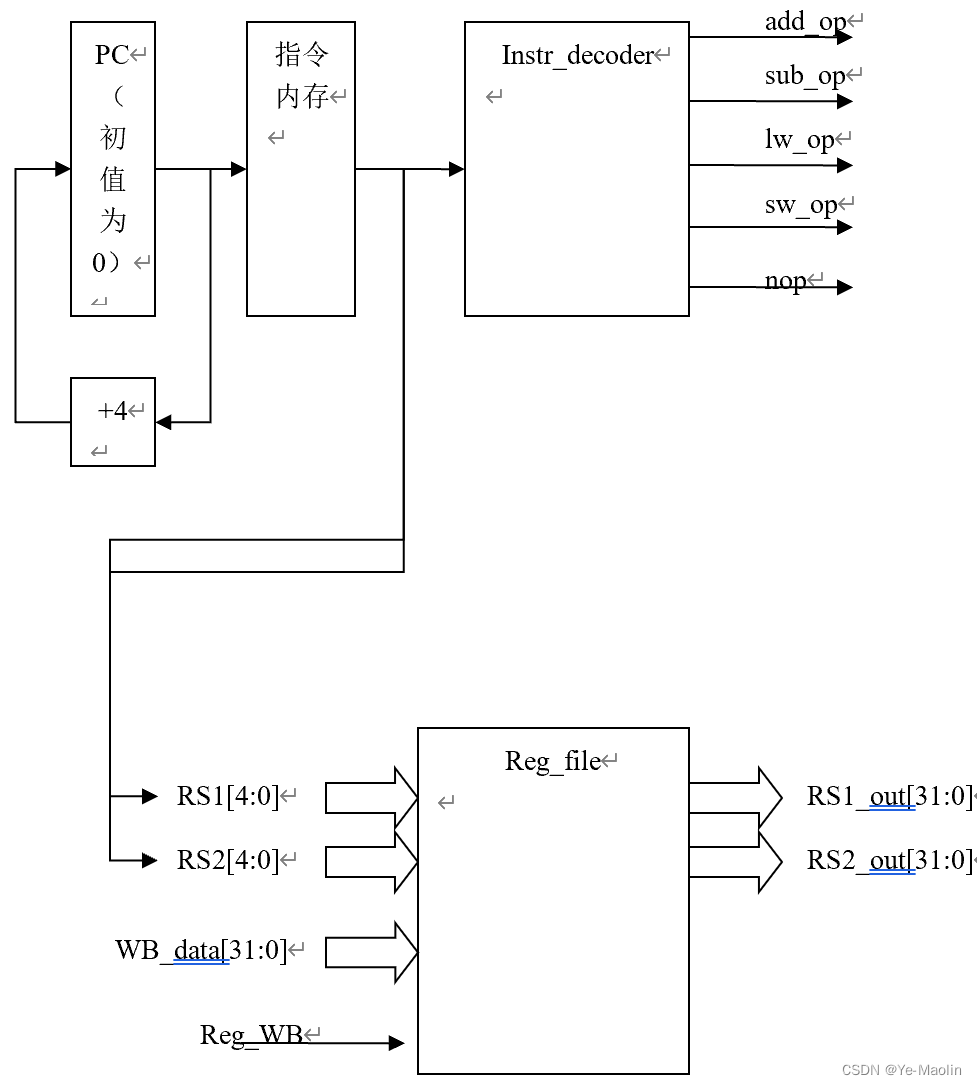

}实现一个32个字的指令存储器

从0地址分别存储4条指令add R1,R2,R3; sub R0,R5,R6,lw R5,100(R2), sw R5,104(R2)。然后组合指令存储器、寄存器文件、译码电路,并结合PC更新电路(PC初值为0)、WB_data和Reg_WB信号产生电路,最终让电路能逐条指令取出、译码(不需要完成指令执行)。

给出Chisel设计代码和仿真测试波形,观察四条指令的执行过程波形,记录并解释其含义。

InstructionMemory.scala

import chisel3._class InstructionMemory extends Module {val io = IO(new Bundle {val address = Input(UInt(5.W)) // 32个字,需要5位地址val instruction = Output(UInt(32.W))})// 创建一个32个字的指令存储器val mem = Mem(32, UInt(32.W))// 初始化存储器,存储MIPS指令mem.write(0.U, "b000000_00010_00011_00001_00000_100000".U) // add R1, R2, R3mem.write(1.U, "b000000_00101_00110_00000_00000_100010".U) // sub R0, R5, R6mem.write(2.U, "b100011_00010_00101_0000000001100100".U) // lw R5, 100(R2)mem.write(3.U, "b101011_00010_00101_0000000001101000".U) // sw R5, 104(R2)// 从存储器中读取指令io.instruction := mem.read(io.address)

}

Circuit.scala

import chisel3._

import chisel3.util._class Circuit extends Module {val io = IO(new Bundle {// 寄存器的输入输出val WB_data = Input(UInt(32.W)) // 写入数据信号,用于写入寄存器val Reg_WB = Input(UInt(5.W)) // 选择写入数据的寄存器val RS1_out = Output(UInt(32.W))val RS2_out = Output(UInt(32.W))// 译码val add_op = Output(Bool())val sub_op = Output(Bool())val lw_op = Output(Bool())val sw_op = Output(Bool())val nop_op = Output(Bool())})val instructionMemory = Module(new InstructionMemory)val registerFile = Module(new RegisterFile)val decoder = Module(new Decoder)val pc = RegInit(0.U(5.W))// 根据pc的值取出指令寄存器相应指令instructionMemory.io.address := pcdecoder.io.Instr_word := instructionMemory.io.instructionregisterFile.io.RS1 := instructionMemory.io.instruction(25, 21)registerFile.io.RS2 := instructionMemory.io.instruction(20, 16)registerFile.io.WB_data := (0.U(32.W))registerFile.io.Reg_WB := (0.U(5.W))// 更新输出io.RS1_out := registerFile.io.RS1_outio.RS2_out := registerFile.io.RS2_outio.add_op := decoder.io.add_opio.sub_op := decoder.io.sub_opio.lw_op := decoder.io.lw_opio.sw_op := decoder.io.sw_opio.nop_op := decoder.io.nop_op// 更新PCpc := pc + 1.U

}object Circuit extends App {(new chisel3.stage.ChiselStage).emitVerilog(new Circuit())

}Circuit.scala

import chiseltest._

import org.scalatest.flatspec.AnyFlatSpec

import chisel3._class CircuitTest extends AnyFlatSpec with ChiselScalatestTester {behavior of "Circuit"it should "correct circuit" in {test(new Circuit).withAnnotations(Seq(WriteVcdAnnotation)) { c =>c.clock.step()c.clock.step()c.clock.step()c.clock.step()}}

}

相关文章:

【计算机组成与设计】Chisel取指和指令译码设计

本次试验分为三个部分: 目录 设计译码电路 设计寄存器文件 实现一个32个字的指令存储器 设计译码电路 输入位32bit的一个机器字,按照课本MIPS 指令格式,完成add、sub、lw、sw指令译码,其他指令一律译码成nop指令。输入信号名…...

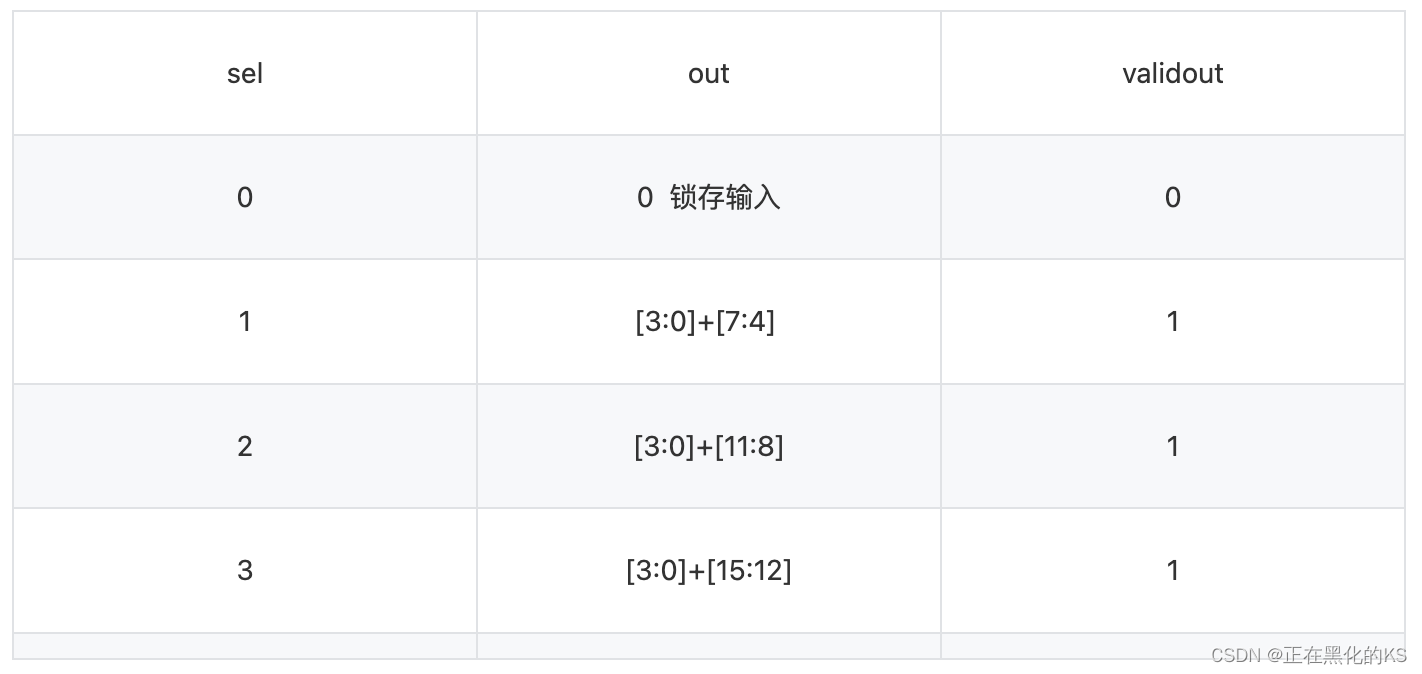

「Verilog学习笔记」位拆分与运算

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 1、寄存器的位是可以分开单独运算的,并不是一个输入就一定是一个数据,在很多情况下,一个输入既包括数据又包括地址等其他有效信息 2、需…...

protobufjs实现protobuf序列化与反序列化

系列文章目录 websocket训练地址:https://www.qiulianmao.com,正在搭建中 基础-websocket逆向基础-http拦截基础-websocket拦截基础-base64编码与解码基础-python实现protobuf序列化与反序列化基础-前端js实现protobuf序列化与反序列化基础-protobufjs实现protobuf序列化与反…...

el-select多选以tag展示时,超过显示长度以...省略号显示,且在一行展示

效果: 代码: <span>系统词典维度:</span><el-selectv-model"dNum"placeholder"请选择"multiplecollapse-tags //设置collapse-tags属性将它们合并为一段文字size"small"style"width:160p…...

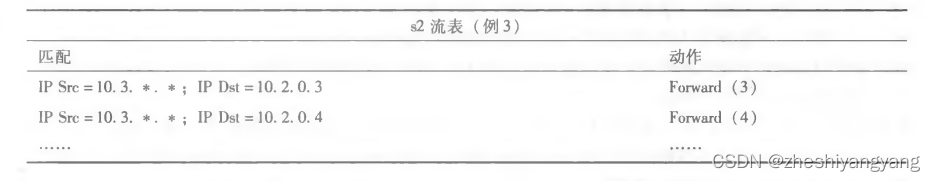

计算机网络第4章-通用转发和SDN

引子: 在前面,我们将基于目的地转发的特征总结为两个步骤: 查找目的IP地址(匹配),然后将分组发送到有特定输出端口的交换结构(“动作”)。 但是这种转发特征会带来许多问题&#…...

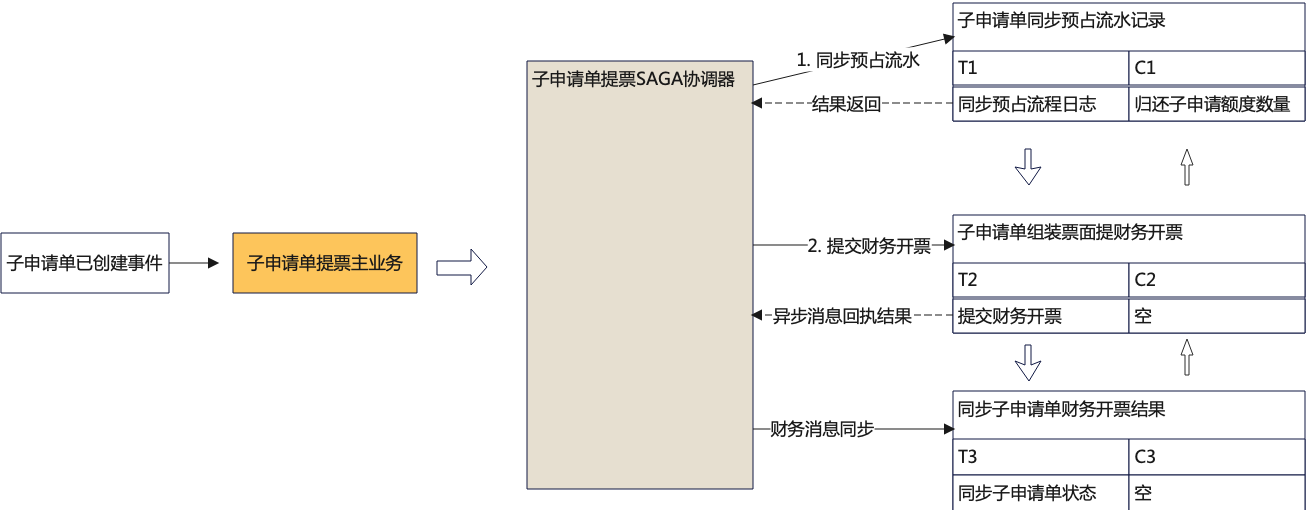

DDD技术方案落地实践 | 京东云技术团队

1. 引言 从接触领域驱动设计的初学阶段,到实现一个旧系统改造到DDD模型,再到按DDD规范落地的3个的项目。对于领域驱动模型设计研发,从开始的各种疑惑到吸收各种先进的理念,目前在技术实施这一块已经基本比较成熟。在既往经验中总…...

MySQL 案例:update set 和 and 的坑

问题描述 最近碰到到一个奇怪的问题,update 语句执行没有报错,但是没有更新数据,具体有问题的语句类似于如下形式: update test.stu set cname 0 and math 90 and his 80 where id 100; 复制 原因分析 直观上看ÿ…...

VSCode remote-ssh 连接远端服务器失败

系统 Mac os Intel处理器 描述 该问题在上午时还没有,下午突然毫无征兆的发生,当时没有更新vscode,没有更新插件。 分析 网上对于该问题的答案多是说磁盘空间不够vscode不能下载相应插件,我所遇到的并不是这种情况。报的错误多是…...

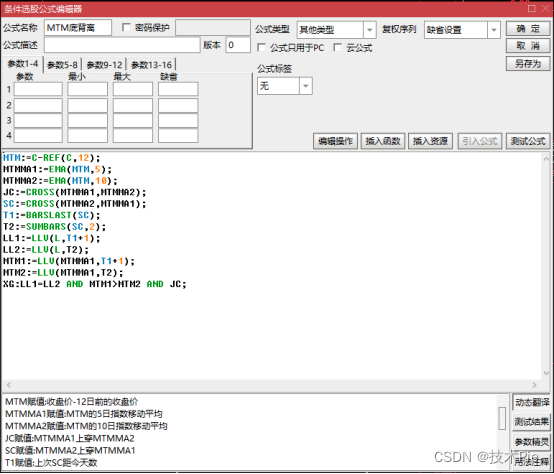

通达信动量线MTM指标原理详解及MTM底背离选股公式

MTM指标(动量线指标)用于衡量价格的动量和趋势,以判断未来价格的变化。计算方法很简单,用当前价格减去一段时间(通常为12日)前的价格,计算得到的差值的正负和大小,可以判断可能的趋势…...

汇编-DUP操作符

DUP操作符使用整数表达式作为计数器, 为多个数据项分配存储空间。 在为字符串或数组分配存储空间时,这个操作符尤其有用,并且可以使用初始化或非初始化数据: .data BYTE 20 DUP(0) ;20个字节,都等于0 BYTE 20 …...

2311C++抽象工厂

1,为啥需要工厂设计模式?工厂设计模式可解决什么问题? 先看一下示例,多态示例. #include <iostream> using namespace std; class Shape { public:Shape() { }virtual void drawShape(){cout << "base draw shape" << endl;} }; class Rectang…...

Lavarel定时任务的使用

系统为window 执行命令(执行一次命令只会根据当前时间运行一次定时任务) php artisan schedule:run创建一个任务类(在Jobs文件夹下面) <?phpnamespace App\Jobs;use Illuminate\Bus\Queueable; use Illuminate\Contracts\Queue\ShouldBeUnique; use Illuminate\Contract…...

)

Java开发者的网络安全指南(二)

目录 一、加密和数据保护 二、身份验证和授权 三、Web应用程序安全 四、安全编码实践 五、网络防火墙和入侵检测系统 六、日志和监视 七、漏洞管理 八、安全教育和培训 九、结论 介绍: 简要说明网络安全的重要性和为什么Java开发者需要关注它。 一、加密…...

Python基础学习016__UnitTest

# UnitTest是python自带的一个单元测试框架,不需要额外安装 # 也是自动化脚本执行框架,使用UnitTest来管理,运行多个框架 # 为什么使用:能够组织多个用例去执行.提供了丰富的断言方法,能够生成测试报告 # 核心要素: # Testcase:测试用例:这个测试用例是UnitTest的组成部分,不是…...

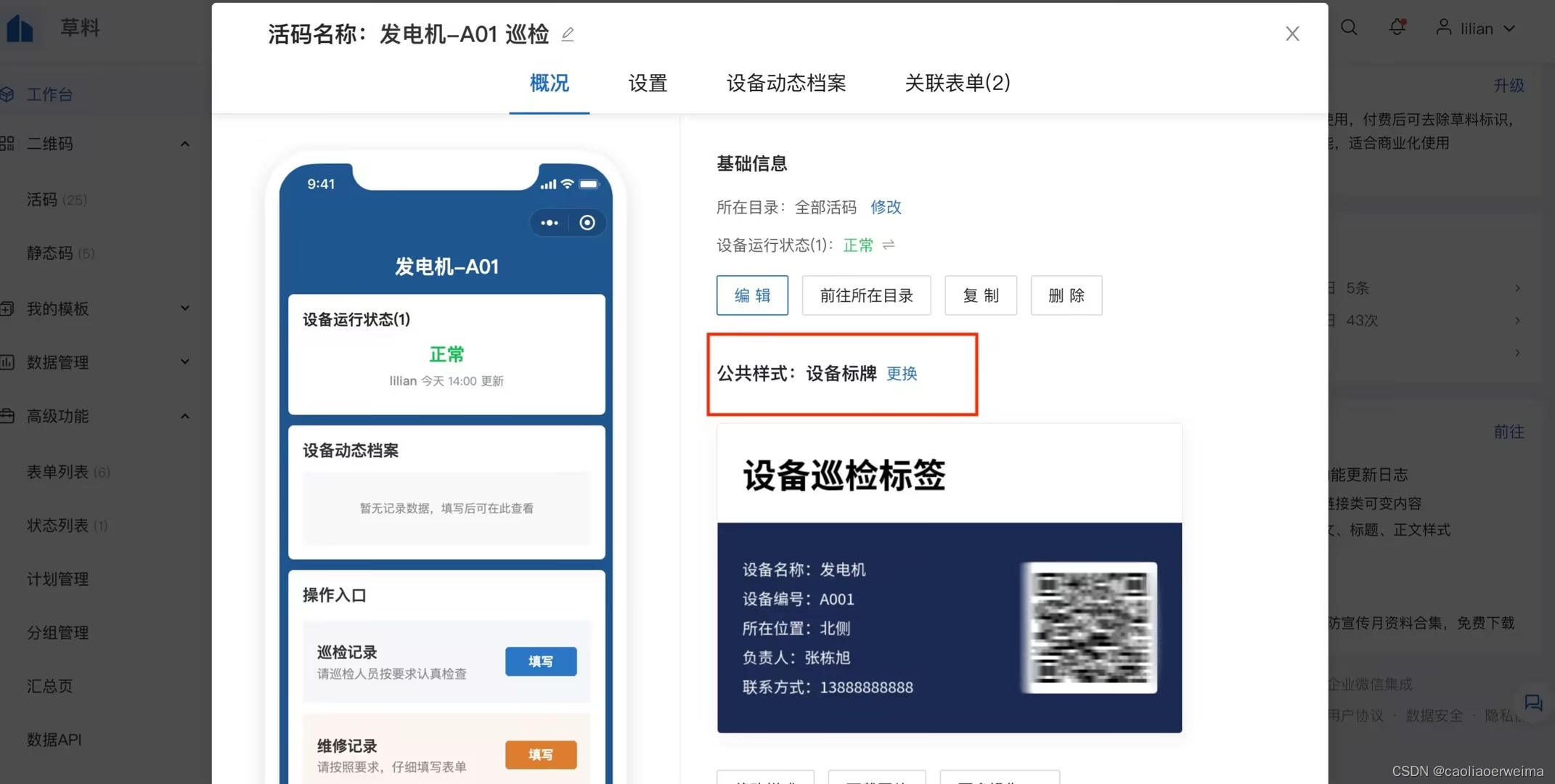

一物一码需求,标签制作功能轻松解决

许多行业存在为人员、物品、设备等做一物一码标签的需求,可使用草料标签制作功能。直接选择标签样式,填入数据,即可批量生成标签,还可批量排版,更易落地。还可保存标签样式,后续多次复用样式,批…...

【Linux】七、基础IO

预备知识 文件 属性(本质上也是数据)内容; 文件的所有操作大致有两种,对内容的操作,和对属性的操作; 文件在磁盘中放置,磁盘是硬件,只有操作系统可以真正的访问磁盘;C\C…...

Elasticsearch语法之Term query不区分大小写

设置关键词是否区分大小写 说明:case_insensitive是term的可选参数,默认为false,表示关键词区分大小写,设置为true表示关键词不区分大小写。该参数在7.10.0开始有效 需求:分别使用关键词"iphone"和"I…...

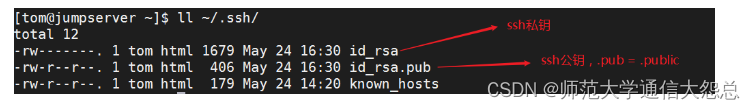

远程管理SSH服务

一、搭建SSH服务 1、关闭防火墙与SELinux # 关闭firewalld防火墙 # 临时关闭 systemctl stop firewalld # 关闭开机自启动 systemctl disable firewalld # 关闭selinux # 临时关闭 setenforce 0 # 修改配置文件 永久关闭 vim /etc/selinux/config SELINUXdisabled 2、配置…...

Linux 实现原理 — NUMA 多核架构中的多线程调度开销与性能优化

前言 NOTE:本文中所指 “线程” 均为可执行调度单元 Kernel Thread。 NUMA 体系结构 NUMA(Non-Uniform Memory Access,非一致性存储器访问)的设计理念是将 CPU 和 Main Memory 进行分区自治(Local NUMA node&#x…...

Oracle锁处理

背景: 随着数据库版本不断迭代更新, v$session 视图的内容越来越丰富,可以直接使用blocking_session、blocking_instance、final_blocking_instance和final_blocking_session字段进行定位。对于锁层次的排查可以重复查询v$session来确定&am…...

Ext2Read:Windows用户如何轻松读取Linux分区文件

Ext2Read:Windows用户如何轻松读取Linux分区文件 【免费下载链接】ext2read A Windows Application to read and copy Ext2/Ext3/Ext4 (With LVM) Partitions from Windows. 项目地址: https://gitcode.com/gh_mirrors/ex/ext2read 你是否遇到过这样的情况&a…...

服务自启动配置2024最新指南:从痛点解决到跨平台实现

服务自启动配置2024最新指南:从痛点解决到跨平台实现 【免费下载链接】lucky 软硬路由公网神器,ipv6/ipv4 端口转发,反向代理,DDNS,WOL,ipv4 stun内网穿透,cron,acme,阿里云盘,ftp,webdav,filebrowser 项目地址: https://gitcode.com/GitHub_Trending/luc/lucky …...

人工智能应用- 走向未来:02.人工智能研究方向

随着技术的发展,以深度神经网络为代表的人工智能技术在取得突破的同时,也逐渐暴露出一些基础性问题。这些问题促使科学家们思考人工智能的下一步发展。本节将从几个关键方面,探讨当前人工智能的重要研究方向。可解释性与可控性首先࿰…...

对于对话中的文本简化,OpenClaw 的压缩比和可读性如何平衡?

关于文本简化中压缩比与可读性的平衡,这其实是一个在工程实践中经常遇到的核心矛盾。OpenClaw 的处理方式,仔细推敲起来,背后反映的是一种偏向实用主义的权衡思路。 压缩比高,通常意味着文本被大幅度精简,只保留最核心…...

【开题答辩全过程】以 校园超市购物系统为例,包含答辩的问题和答案

个人简介一名14年经验的资深毕设内行人,语言擅长Java、php、微信小程序、Python、Golang、安卓Android等开发项目包括大数据、深度学习、网站、小程序、安卓、算法。平常会做一些项目定制化开发、代码讲解、答辩教学、文档编写、也懂一些降重方面的技巧。感谢大家的…...

)

嵌入式Linux开发板CH340驱动安装避坑指南(附详细步骤图)

嵌入式Linux开发板CH340驱动安装全流程解析与疑难排错 第一次接触嵌入式Linux开发板时,最让人头疼的往往不是代码编写,而是最基础的开发环境搭建。作为连接电脑与开发板的重要桥梁,CH340串口驱动的安装质量直接决定了后续调试效率。许多初学者…...

wxappUnpacker:让微信小程序源代码重见天日的开发者利器

wxappUnpacker:让微信小程序源代码重见天日的开发者利器 【免费下载链接】wxappUnpacker 项目地址: https://gitcode.com/gh_mirrors/wxappu/wxappUnpacker 在微信小程序开发过程中,开发者常常面临源代码被打包加密的困境,特别是当需…...

TwinCAT3 PLC安装避坑指南:从EtherCAT驱动到系统配置的完整流程

TwinCAT3 PLC实战安装指南:从零搭建工业控制系统的关键步骤 第一次接触TwinCAT3的工程师往往会被其强大的功能和复杂的配置流程所震撼。作为工业自动化领域的瑞士军刀,TwinCAT3将PLC、运动控制和实时通信集成在一个平台上,但这也意味着安装过…...

咱们今天聊点干货——用MATLAB玩转储能电站和微电网的协同优化。这玩意儿听起来高大上,实操起来其实挺有意思。先看上层优化的核心代码段

MATLAB代码:基于储能电站服务的冷热电多微网系统双层优化 MATLAB代码:基于储能电站服务的冷热电多微网系统双层优化|||配置 关键词:储能电站 共享储能电站 冷热电多微网 双层优化配置 参考文档:《基于储能电站服务的冷热电多微…...

4大维度解锁TrafficMonitor插件扩展能力:定制化系统监控全攻略

4大维度解锁TrafficMonitor插件扩展能力:定制化系统监控全攻略 【免费下载链接】TrafficMonitorPlugins 用于TrafficMonitor的插件 项目地址: https://gitcode.com/gh_mirrors/tr/TrafficMonitorPlugins 价值定位:为什么需要TrafficMonitor插件系…...