ZYNQ_project:key_beep

通过按键控制蜂鸣器工作。

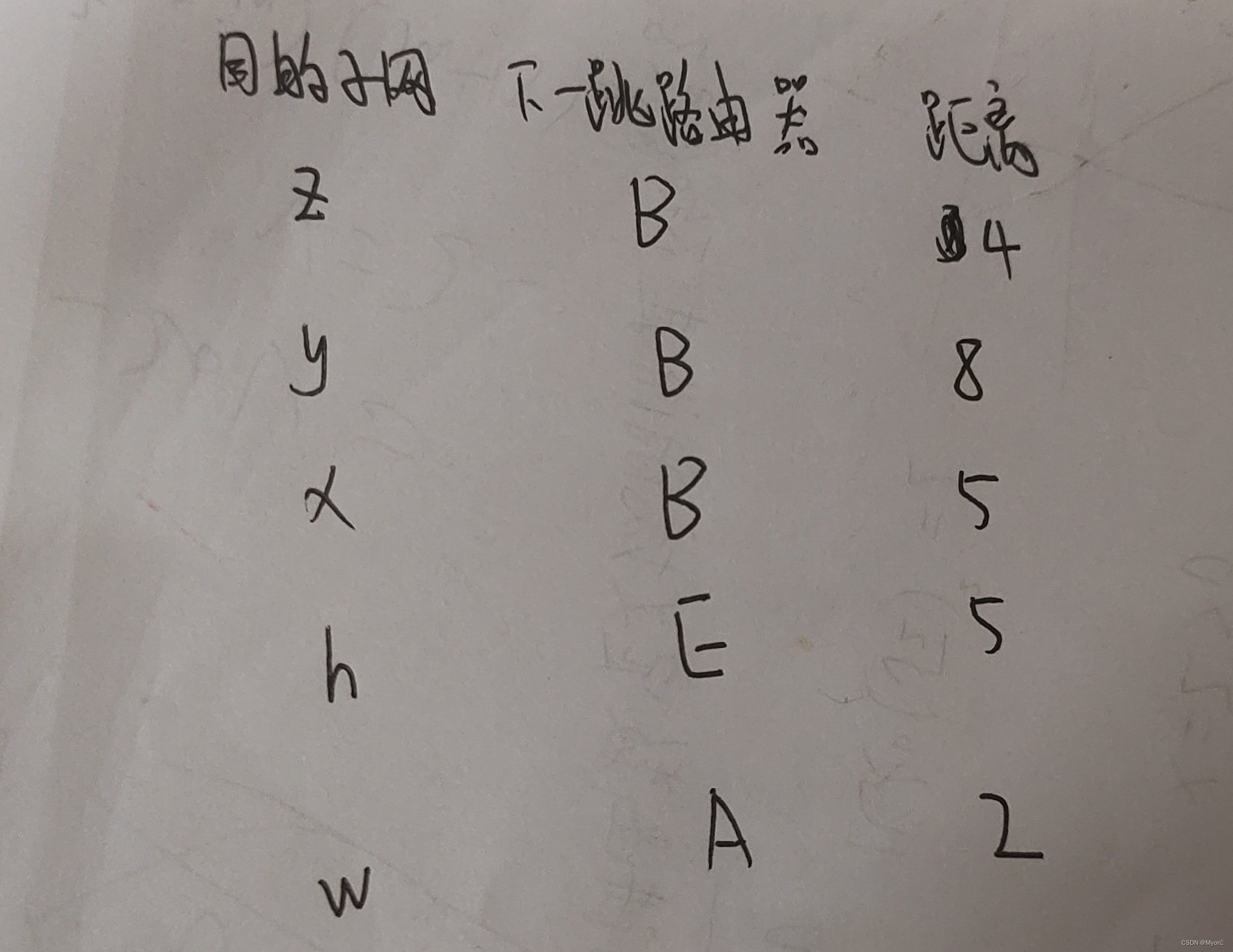

模块框图:

时序图:

代码:

/*1位按键消抖

*/

module key_filter (input wire sys_clk ,input wire sys_rst_n ,input wire key_in ,output reg key_flag

);// 参数定义parameter MAX_CNT_10MS = 500_000 ;localparam IDLE = 4'b0001 ,FILTER_UP = 4'b0010 ,SAMPLING = 4'b0100 ,FILTER_BACK = 4'b1000 ;// reg signal define reg key_in_r1 ; reg key_in_r2 ;reg [18:0] cnt_core ;reg [3:0] state_c ;reg [3:0] state_n ;// wire signal define wire nege ;wire pose ;wire IDLEtoFILTER_UP ;wire FILTER_UPtoIDLE ;wire FILTER_UPtoSAMPLING ;wire SAMPLINGtoFILTER_BACK ;wire FILTER_BACKtoIDLE ;wire filter_done ; /******************************************************************/// reg key_in_r1 ; always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) key_in_r1 <= 1'b1 ;elsekey_in_r1 <= key_in ;end // reg key_in_r2 ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) key_in_r2 <= 1'b1 ;elsekey_in_r2 <= key_in_r1 ;end // wire nege ;assign nege = ~key_in_r1 && key_in_r2 ;// wire pose ; assign pose = key_in_r1 && ~key_in_r2 ;// reg [3:0] state_c ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) state_c <= IDLE ;elsestate_c <= state_n ;end// reg [3:0] state_n ;always @(*) begincase(state_c)IDLE : if(IDLEtoFILTER_UP)state_n = FILTER_UP ;else state_n = IDLE ;FILTER_UP : if(FILTER_UPtoIDLE)state_n = IDLE ;else if(FILTER_UPtoSAMPLING)state_n = SAMPLING ;else state_n = FILTER_UP ;SAMPLING : if(SAMPLINGtoFILTER_BACK)state_n = FILTER_BACK ;else state_n = SAMPLING ;FILTER_BACK:if(FILTER_BACKtoIDLE)state_n = IDLE ;elsestate_n = FILTER_BACK ;default : state_n = IDLE ;endcaseendassign IDLEtoFILTER_UP = (state_c == IDLE) && (nege) ;assign FILTER_UPtoIDLE = (state_c == FILTER_UP) && (pose) ;assign FILTER_UPtoSAMPLING = (state_c == FILTER_UP) && (filter_done) ;assign SAMPLINGtoFILTER_BACK = (state_c == SAMPLING) && (pose) ;assign FILTER_BACKtoIDLE = (state_c == FILTER_BACK)&& (filter_done) ;// reg [18:0] cnt_core ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_core <= 19'd0 ;elsecase (state_c)IDLE :cnt_core <= 19'd0 ; FILTER_UP :if(filter_done)cnt_core <= 19'd0 ;else cnt_core <= cnt_core + 1'b1 ;SAMPLING :cnt_core <= 19'd0 ; FILTER_BACK:if(filter_done)cnt_core <= 19'd0 ;else cnt_core <= cnt_core + 1'b1 ;default : cnt_core <= 19'd0 ;endcaseend// wire filter_doneassign filter_done = (cnt_core == MAX_CNT_10MS - 1) ;// output reg key_flagalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) key_flag <= 1'b0 ;else if(FILTER_UPtoSAMPLING)key_flag <= ~key_in_r2 ;else key_flag <= 1'b0 ;endendmodule/*蜂鸣器驱动模块,NPN三极管,beep_en == 1 鸣叫。有源电磁式。1, 初始状态鸣叫,按键每按下一次,蜂鸣器状态翻转。2. 初始状态蜂鸣器工作,响100ms , 不响100ms, 响100ms, 不响300ms.按键每按下一次,蜂鸣器工作状态翻转。

*/

module beep (input wire sys_clk ,input wire sys_rst_n ,input wire key_flag ,output reg beep_en

);// // output reg beep_en// always @(posedge sys_clk or negedge sys_rst_n) begin// if(~sys_rst_n) // beep_en <= 1'b1 ;// else if(key_flag)// beep_en <= ~beep_en ;// end// parameterparameter MAX_CNT_100MS = 5_000_000 ,MAX_CNT_300MS = 15_000_000 ;localparam RING = 3'b001 ,NO_RING_MOD1 = 3'b010 ,NO_RING_MOD2 = 3'b100 ;// reg signal definereg beep_work ;reg [23:0] cnt_core ;reg [2:0] state_c ;reg [2:0] state_n ;reg mod1_flag ;// wire signal definewire RINGtoNO_RING_MOD1 ;wire RINGtoNO_RING_MOD2 ;wire NO_RING_MOD1toRING ;wire NO_RING_MOD2toRING ;wire no_ring_done ;/*****************************************************/// reg beep_work ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beep_work <= 1'b1 ;else if(key_flag)beep_work <= ~beep_work ;else beep_work <= beep_work ;end// reg [2:0] state_c ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) state_c <= RING ;else state_c <= state_n ;end// reg [2:0] state_n ;always @(*) beginif(beep_work) begincase(state_c)RING : if(RINGtoNO_RING_MOD1)state_n = NO_RING_MOD1 ;else if(RINGtoNO_RING_MOD2)state_n = NO_RING_MOD2 ;elsestate_n = RING ;NO_RING_MOD1: if(NO_RING_MOD1toRING)state_n = RING ;else state_n = NO_RING_MOD1 ;NO_RING_MOD2: if(NO_RING_MOD2toRING)state_n = RING ;else state_n = NO_RING_MOD2 ;default : state_n = RING ;endcaseendelsestate_n = RING ;endassign RINGtoNO_RING_MOD1 = (state_c == RING) && (no_ring_done && (mod1_flag)) ;assign RINGtoNO_RING_MOD2 = (state_c == RING) && (no_ring_done && (!mod1_flag)) ;assign NO_RING_MOD1toRING = (state_c == NO_RING_MOD1) && (no_ring_done) ;assign NO_RING_MOD2toRING = (state_c == NO_RING_MOD2) && (no_ring_done) ;// reg [23:0] cnt_core ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_core <= 24'd0 ;elseif(beep_work) begincase (state_c)RING : if(no_ring_done)cnt_core <= 24'd0 ;else cnt_core <= cnt_core + 1'b1 ; NO_RING_MOD1: if(no_ring_done)cnt_core <= 24'd0 ;else cnt_core <= cnt_core + 1'b1 ; NO_RING_MOD2: if(no_ring_done)cnt_core <= 24'd0 ;else cnt_core <= cnt_core + 1'b1 ; default : cnt_core <= 24'd0 ;endcaseendelse cnt_core <= 24'd0 ;end// reg mod1_flag ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) mod1_flag <= 1'b1 ;else if(beep_work) beginif((state_c != RING) && (no_ring_done))mod1_flag <= ~mod1_flag ;else mod1_flag <= mod1_flag ;endelse mod1_flag <= 1'b1 ;end// wire no_ring_done;assign no_ring_done = (((state_c != NO_RING_MOD2)&&(cnt_core == MAX_CNT_100MS - 1))||((state_c == NO_RING_MOD2)&&(cnt_core == MAX_CNT_300MS - 1))) ? 1'b1 : 1'b0 ;// output reg beep_enalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beep_en <= 1'b1 ;else if(beep_work) beginif(state_c == RING)beep_en <= 1'b1 ;else beep_en <= 1'b0 ;endelse beep_en <= 1'b0 ; endendmodule

module top(input wire sys_clk ,input wire sys_rst_n ,input wire key_in ,output wire beep

);// 例化间连线wire key_flag ;

key_filter key_filter_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key_in ) ,.key_flag ( key_flag )

);beep beep_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_flag ( key_flag ) ,.beep_en ( beep )

);endmodule

`timescale 1ns/1ns

module test_top();reg sys_clk ;reg sys_rst_n ;reg key_in ;wire beep ;top top_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key_in ) ,.beep ( beep )

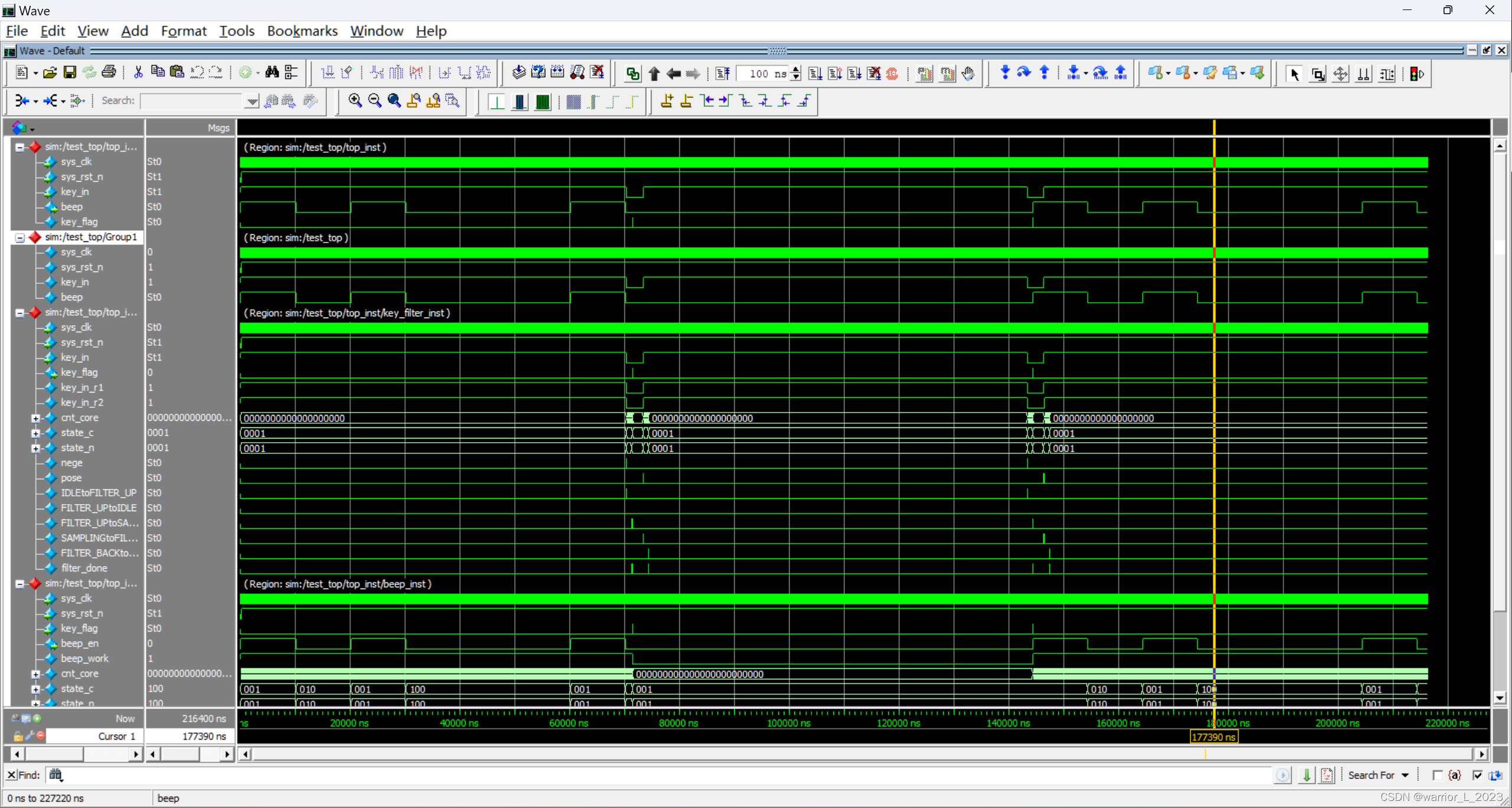

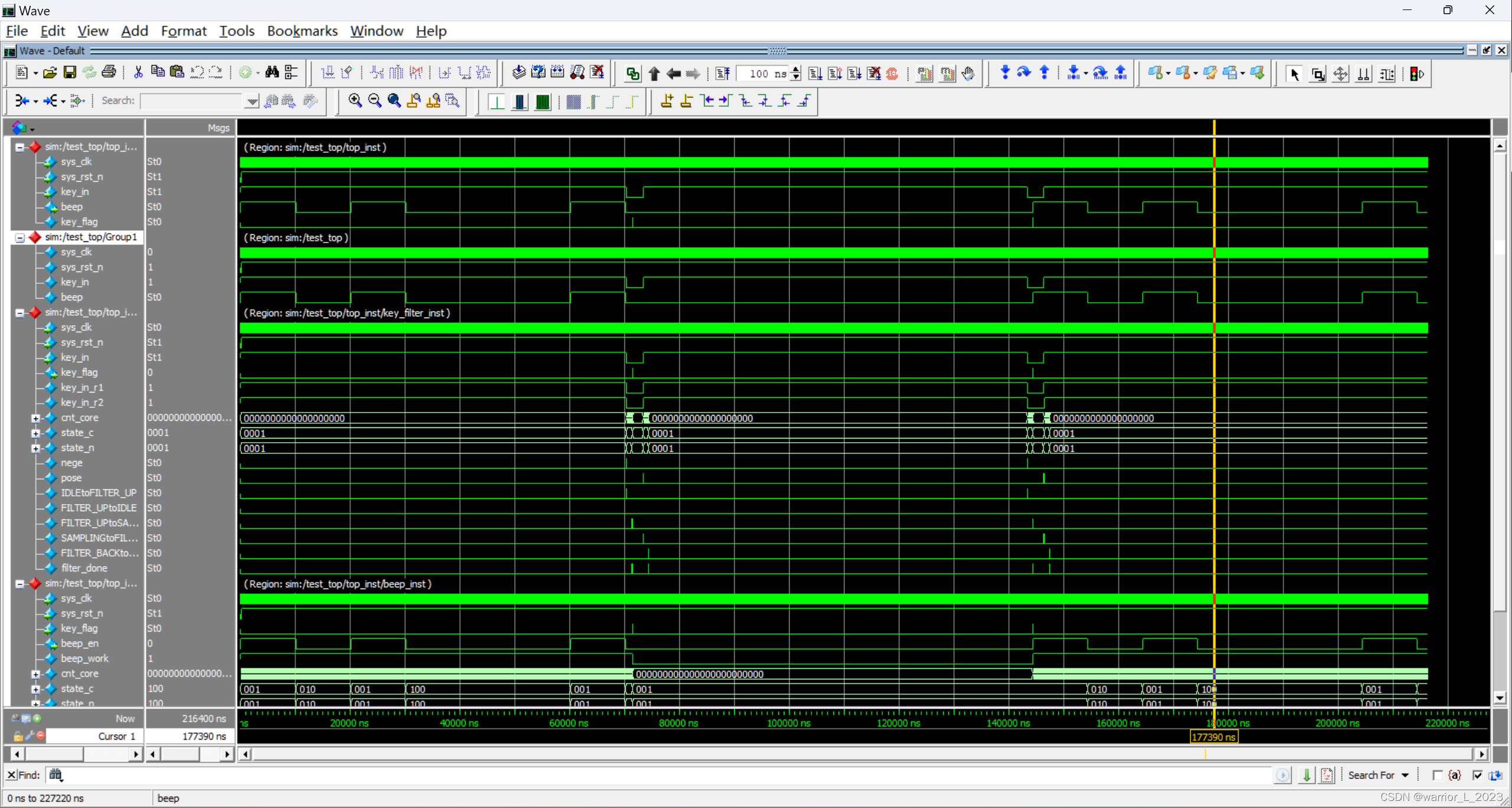

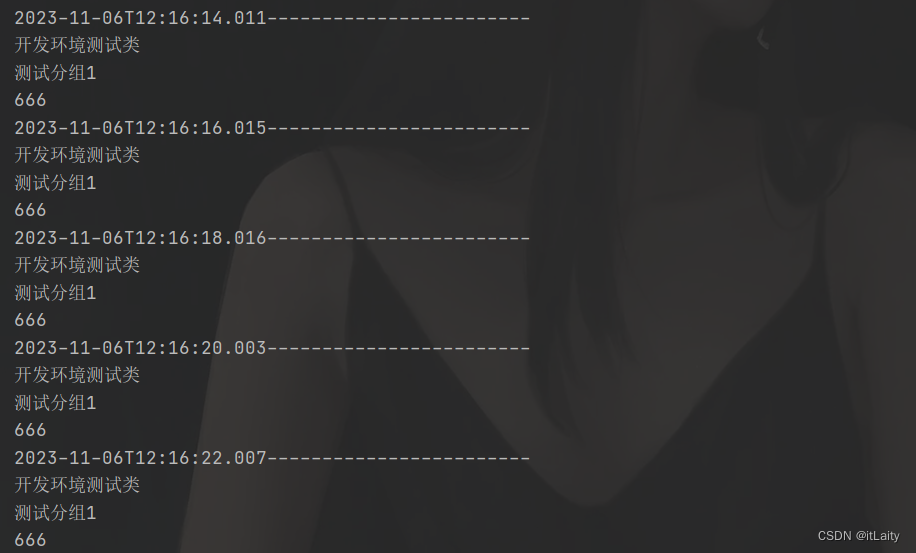

);parameter CYCLE = 20 ;defparam top_inst.key_filter_inst.MAX_CNT_10MS = 50 ;defparam top_inst.beep_inst.MAX_CNT_100MS = 500 ;defparam top_inst.beep_inst.MAX_CNT_300MS = 1500 ;initial beginsys_clk = 1'b1 ;sys_rst_n <= 1'b0 ;key_in <= 1'b1 ;#( CYCLE * 10 ) ;sys_rst_n <= 1'b1 ;#( CYCLE * 10 ) ;#( CYCLE * 3000 ) ;#( CYCLE * 500 ) ; // 检测蜂鸣器状态机是否正常工作。key_in <= 1'b0 ;#( CYCLE * 50 * 3 ); // 按下足够长的时间,第一次按键按下。key_in <= 1'b1 ;#( CYCLE * 3000 ) ;#( CYCLE * 500 ) ; // 检测蜂鸣器状态机是否正常工作。key_in <= 1'b0 ;#( CYCLE * 50 * 3 ); // 按下足够长的时间,第二次按键按下。key_in <= 1'b1 ;#( CYCLE * 3000 ) ;#( CYCLE * 500 ) ; // 检测蜂鸣器状态机是否正常工作。$stop ;endalways #( CYCLE / 2 ) sys_clk = ~sys_clk ;endmodule仿真:

相关文章:

ZYNQ_project:key_beep

通过按键控制蜂鸣器工作。 模块框图: 时序图: 代码: /*1位按键消抖 */ module key_filter (input wire sys_clk ,input wire sys_rst_n ,input wire key_in ,output …...

css3文字环绕旋转

目录 固定数量文字环绕旋转不固定数量文字环绕旋转效果图 固定数量文字环绕旋转 <!-- 文字旋转测试 --> <template><div class"page"><div><div v-for"(item, index) in [...Array(20).keys()]" :key"index" style&…...

Linux 进程优先级 | 环境变量

目录 进程优先级 基本概念 认识优先级 PRI and NI NI值的范围 查看进程优先级 用top命令更改已存在进程的nice: 如何修改优先级 其他概念 环境变量 基本概念 常见环境变量 和环境变量相关的命令 环境变量的组织方式 通过代码如何获取环境变量 环境变量通…...

Nginx(五)

负载均衡 官网文档 Using nginx as HTTP load balancer nginx中实现反向代理的方式 HTTP:通过nginx配置反向代理到后端服务器,nginx将接收到的HTTP请求转发给后端服务器。使用 proxy_pass 命令 HTTPS:通过nginx配置反向代理到后端服务器&…...

永达理简析:利用保险的“财务规划”功能维持退休后生活水平

现代社会环境背景下,“自养自老”已经是一种未来养老趋势,很多人会为自己准备一份长期、比较周全的保障,这样财务规划不仅会分担子女的压力,也让自己有一个长远的保障。在各种财务储蓄工具中,商业保险占据着不可取代的…...

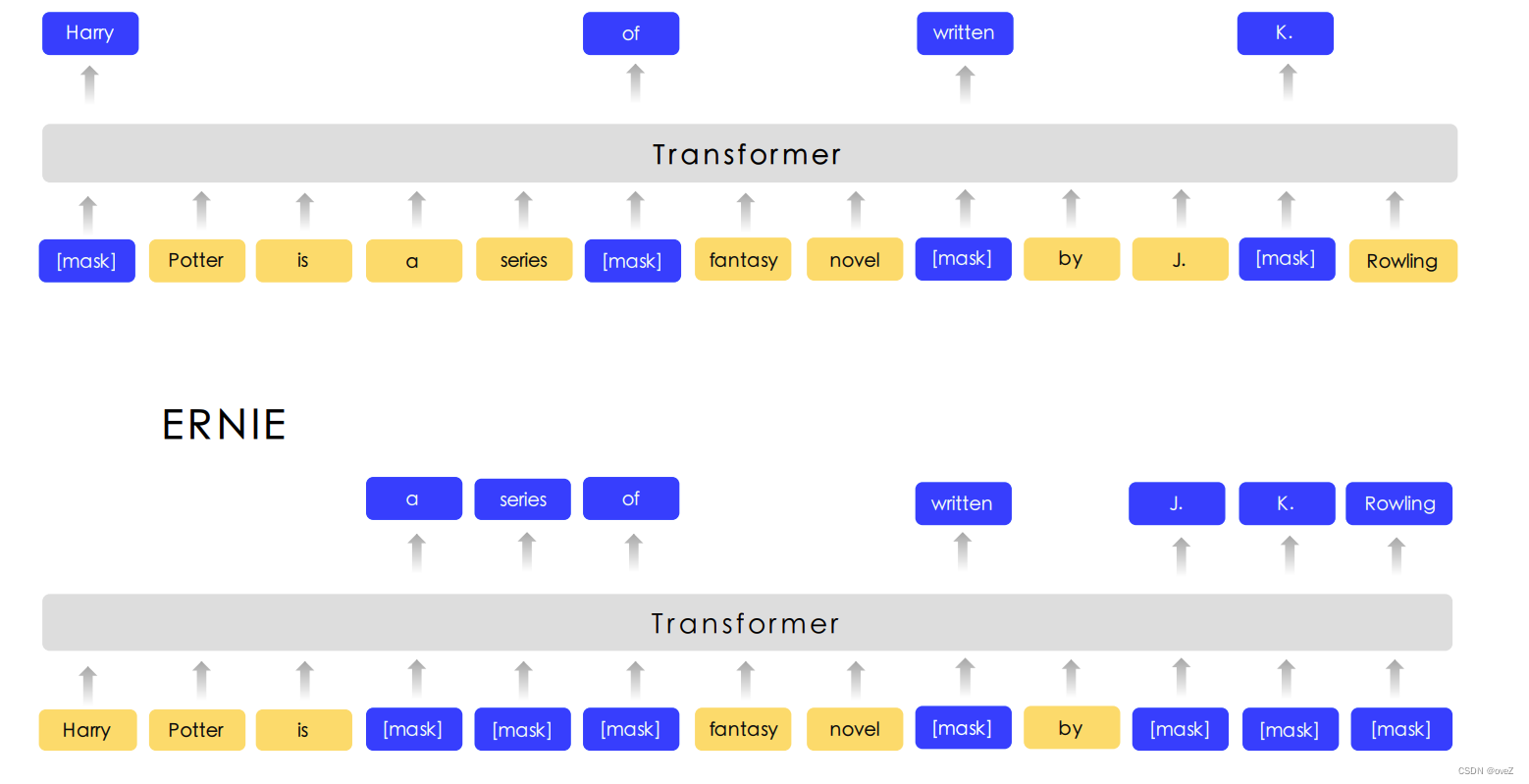

拓展认知边界:如何给大语言模型添加额外的知识

Integrating Knowledge in Language Models P.s.这篇文章大部分内容来自Stanford CS224N这门课Integrating Knowledge in Language Models这一节😁 为什么需要给语言模型添加额外的知识 1.语言模型会输出看似make sense但实际上不符合事实的内容 语言模型在生成…...

C语言assert断言

断言是对某种假设条件进行检查。 C语言中,断言被定义成宏的形式,原型在<assert.h>中。 #include <assert.h> void assert( int expression );assert将通过检查表达式expression的值来决定是否需要终止执行程序。 如果expression的值为假&am…...

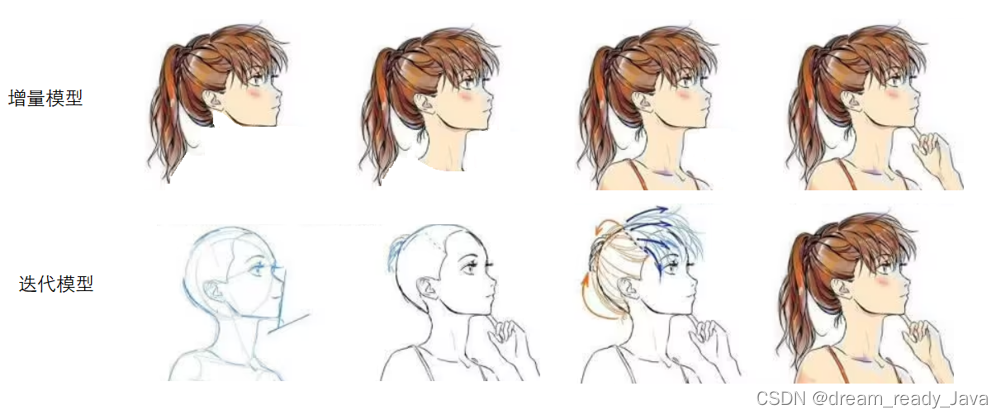

开发模型(瀑布、螺旋、scrum) 和 测试模型(V、W)、增量和迭代、敏捷(思想)及敏捷开发 scrum

🧸欢迎来到dream_ready的博客,📜相信您对这篇博客也感兴趣o (ˉ▽ˉ;) 震惊!测试人员对BUG的全方位解析,测试的执行和BUG管理! 原来测试人员遇到BUG是这样返回给开发的!什么是BUG&am…...

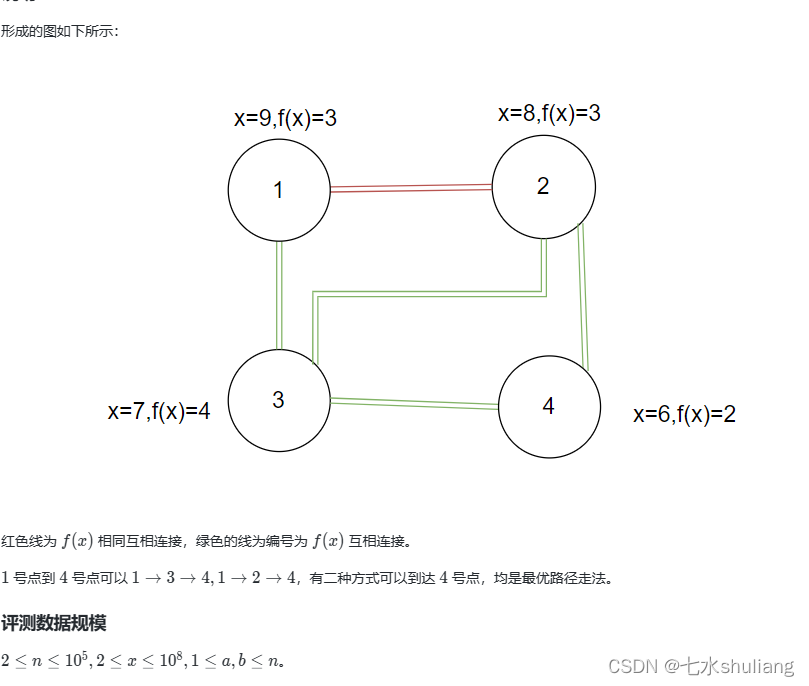

[蓝桥杯复盘] 第 3 场双周赛20231111

[蓝桥杯复盘] 第 3 场双周赛20231111 总结深秋的苹果1. 题目描述2. 思路分析3. 代码实现 鲜花之海1. 题目描述2. 思路分析3. 代码实现 斐波拉契跳跃2. 思路分析3. 代码实现 星石传送阵2. 思路分析3. 代码实现 六、参考链接 总结 做了后4题。https://www.lanqiao.cn/oj-contes…...

浅析移动端车牌识别技术的工作原理及其过程

随着社会经济的发展与汽车的日益普及带来巨大的城市交通压力,在此背景下,智能交通系统成为解决这一问题的关键。而在提出发展无线智能交通系统后,作为智能交通的核心,车牌识别系统需要开始面对车牌识别移动化的现实需求。基于实现车牌识别移动化这一目标,一种基于Android移动终…...

计算机网络期末复习-Part4

1、UDP和TCP的比较 TCP提供可靠传输;UDP提供不可靠传输。TCP有连接;UDP无连接(减小时延)。TCP提供流量控制;UDP不提供流量控制。TCP提供拥塞控制;UDP不提供拥塞控制(传输快)。TCP提…...

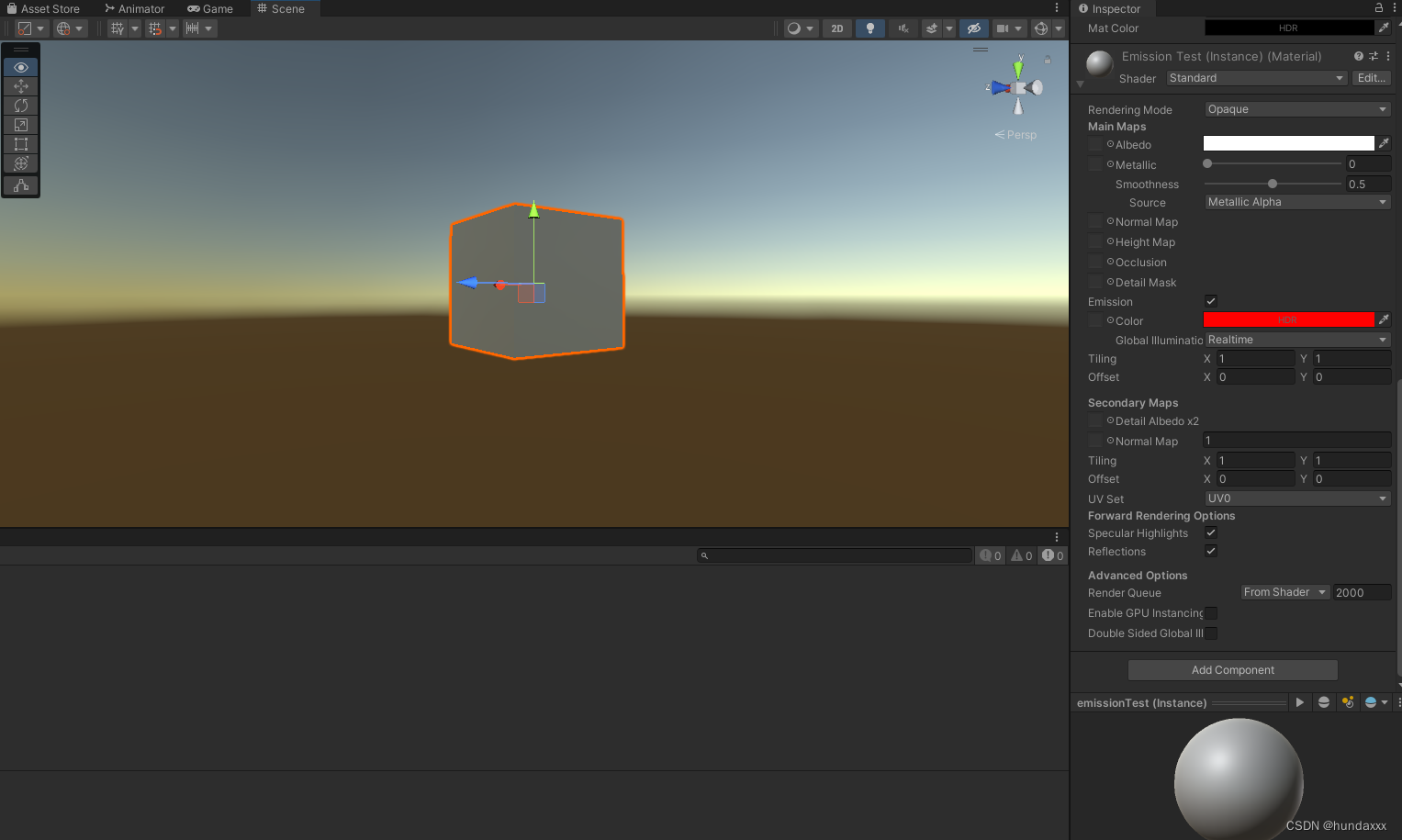

解决EnableKeyword(“_Emission“)运行状态不起作用

我使用的是Standard Shader,一开始“_Emission”没有开启 当我运行下面的代码,可以看到Inspector窗口已经生效,然而物体本身并没有重新开始渲染,反射没有开启 public GameObject go; // Start is called before the first frame…...

管理能力测评,如何提升管理能力?

管理能力是综合能力的体现,通常也解读为组织管理能力,如果要再细分的话,可能还包括有沟通能力,协调能力,组织能力,执行力和专业能力等等。不过没有办法说的太细节,因为每个部分铺开了都是一个独…...

基于工业智能网关的汽车充电桩安全监测方案

近年来,我国新能源汽车产业得到快速发展,电动车产量和销量都在持续增长,不仅国内市场竞争激烈,而且也远销海外,成为新的经济增长点。但与此同时,充电设施的运营却面临着安全和效率的双重挑战。 当前的充电桩…...

基于JavaWeb+SpringBoot+微信小程序的酒店商品配送平台系统的设计和实现

基于JavaWebSpringBoot微信小程序的酒店商品配送平台系统的设计和实现 源码传送入口前言主要技术系统设计功能截图Lun文目录订阅经典源码专栏Java项目精品实战案例《500套》 源码获取 源码传送入口 前言 本章内容概括了基于微信小程序的酒店商品配送平台的可行性分析、系统功…...

Android修行手册-POI操作Excel实现超链接并且变为蓝色

点击跳转>Unity3D特效百例点击跳转>案例项目实战源码点击跳转>游戏脚本-辅助自动化点击跳转>Android控件全解手册点击跳转>Scratch编程案例点击跳转>软考全系列 👉关于作者 专注于Android/Unity和各种游戏开发技巧,以及各种资源分享&…...

:Halcon导出c#脚本)

Halcon WPF 开发学习笔记(2):Halcon导出c#脚本

文章目录 前言HalconC#教学简单说明如何二开机器视觉 前言 我目前搜了一下我了解的机器视觉软件,有如下特点 优点缺点兼容性教学视频(B站前三播放量)OpenCV开源,免费,因为有源码所以适合二次开发学习成本极高,卡学历。研究生博士…...

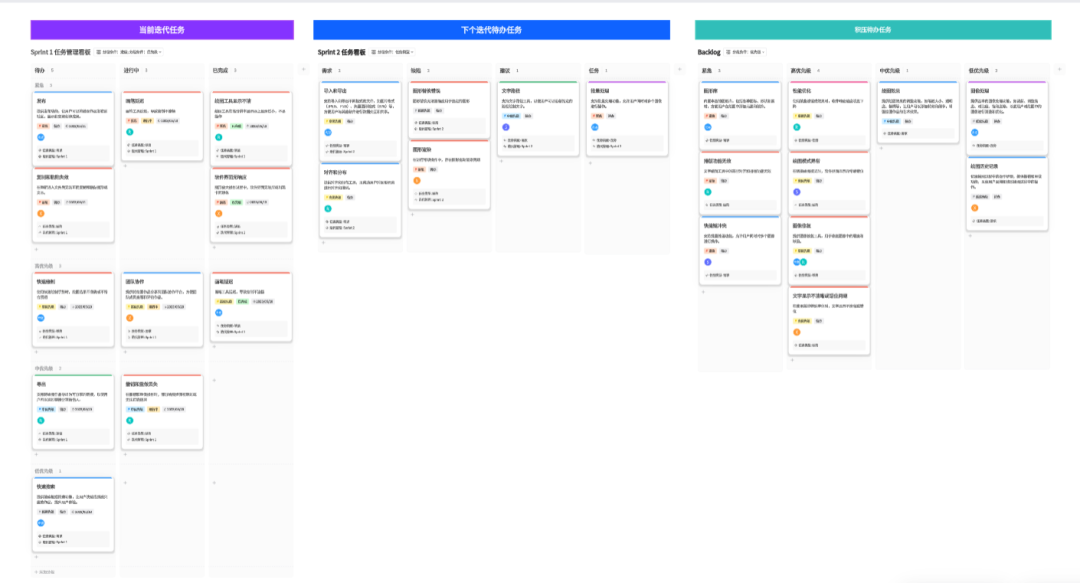

Scrum敏捷开发全流程,3款必备的项目管理工具!

Scrum是一种敏捷方法,致力于帮助团队高效地协作和完成复杂的项目。它强调迭代和快速迭代、自组织、快速响应变化等原则,使得项目开发变得更加灵活和高效。 在Scrum敏捷开发过程中,项目管理工具是必不可少的。下面介绍3款常用的敏捷开发工具…...

基于Quartz实现动态定时任务

生命无罪,健康万岁,我是laity。 我曾七次鄙视自己的灵魂: 第一次,当它本可进取时,却故作谦卑; 第二次,当它在空虚时,用爱欲来填充; 第三次,在困难和容易之…...

-41)

hdlbits系列verilog解答(计算向量中1出现次数)-41

文章目录 一、问题描述二、verilog源码三、仿真结果一、问题描述 “频次计数”电路对输入向量中的“1”数进行计数。为 255 位输入向量构建频次计数电路。 Module Declaration module top_module( input [254:0] in, output [7:0] out ); 二、verilog源码 module top_module…...

HunyuanVideo-Foley多场景落地:虚拟主播直播实时AI音效增强方案

HunyuanVideo-Foley多场景落地:虚拟主播直播实时AI音效增强方案 1. 引言:直播音效的AI革命 在虚拟主播直播领域,音效质量直接影响观众体验。传统Foley音效制作面临三大痛点: 成本高昂:专业音效师按小时计费效率低下…...

的AI技术可提升数学建模论文的复现质量,并简化排版流程)

爱毕业(aibiye)的AI技术可提升数学建模论文的复现质量,并简化排版流程

还在为论文写作头痛?特别是数学建模的优秀论文复现与排版,时间紧、任务重,AI工具能帮上大忙吗?今天,我们评测10款热门AI论文写作工具,帮你精准筛选最适合的助手。 aibiye:专注于语法润色与结构…...

PMD自定义规则开发终极指南:打造专属代码质量检查工具

PMD自定义规则开发终极指南:打造专属代码质量检查工具 【免费下载链接】pmd An extensible multilanguage static code analyzer. 项目地址: https://gitcode.com/gh_mirrors/pm/pmd PMD作为一款强大的多语言静态代码分析工具,允许开发者通过自定…...

【AIAgent社会影响白皮书】:SITS2026首席专家独家解码3大颠覆性冲击与5年治理路线图

第一章:SITS2026专家:AIAgent的社会影响 2026奇点智能技术大会(https://ml-summit.org) AIAgent已从实验室原型演进为嵌入城市治理、医疗决策与教育服务的常态化社会基础设施。在SITS2026大会上,来自全球17个国家的跨学科专家共同指出&…...

)

计算机科学基础的重要性(操作系统、网络、组成原理)

计算机科学基础:数字世界的基石 在人工智能与云计算蓬勃发展的今天,计算机科学基础学科如操作系统、计算机网络和计算机组成原理,依然是技术创新的底层支柱。无论是开发高性能应用还是设计分布式系统,缺乏这些核心知识的程序员如…...

超级智能太过单一!菲尔兹奖得主陶哲轩首提“哥白尼式智能观”:人类智能和AI各有好坏,最会用AI的往往是会“带人”的人

在真实世界中,AI究竟是什么?人类智能又是什么?它们之间有着什么样的关系?近日,“越来越关注如何利用 AI 和其他现代技术来重塑数学,甚至是整个科学体系”的菲尔兹奖得主Terence Tao(陶哲轩&…...

IndexTTS 2.0创意玩法:用AI语音合成制作有声小说,一人搞定全部角色配音

IndexTTS 2.0创意玩法:用AI语音合成制作有声小说,一人搞定全部角色配音 1. 引言:有声小说制作的新革命 你是否曾经想过制作一部属于自己的有声小说?传统的有声书制作需要聘请多位配音演员,租用专业录音棚,…...

Python Final 类型限定符详解

一、基本概念与起源 Python中的Final是一种类型限定符(type qualifier),包含typing.Final类型标注和typing.final装饰器两种形式,用于告诉类型检查器(如mypy、pyright)某个实体不应该被重新赋值、重定义或覆…...

【实践指南】从零到一:手把手完成Lidar-IMU联合标定

1. 为什么需要Lidar-IMU联合标定? 当你第一次把激光雷达和IMU装到机器人上时,可能会发现一个奇怪的现象:明明机器人是静止的,但雷达点云和IMU数据对不上号。我去年调试一台服务机器人时就遇到过这种情况——IMU显示设备正在旋转&a…...

【AI】Gemma 4

Gemma 4 是 Google DeepMind 于 2026 年 4 月 2 日 发布的最新开源模型家族,这是 Gemma 系列迄今为止最重大的升级。以下是关键信息总结:核心亮点特性详情发布时间2026 年 4 月 2 日许可证Apache 2.0(首次完全开源商用)模型家族4 …...