S25FL256S介绍及FPGA实现思路

本文介绍 S25FL256S 这款 FLASH 芯片,并进行 FPGA 读写控制的实现(编程思路及注意事项)。

文章目录

- S25FL-S 介绍

- 管脚功能说明

- SPI 时钟模式

- SDR

- DDR

- 工作模式

- FLASH存储阵列(地址空间映射)

- 常用寄存器及相关指令

- Status Register 1 (SR1)

- Status Register 2 (SR2)

- Configuration Register 1 (CR1)

- Autoboot Register (ABR)

- Bank Address Register (BAR)

- 关于部分常用命令的解释

- 写使能命令(WREN 06h)

- 写寄存器命令(WRR 01h)

- Autoboot

- 读 flash 命令

- 写 flash 命令

- flash 擦除命令

- FPGA 实现(思路)

S25FL-S 介绍

管脚功能说明

- RESET#,input,硬件复位信号;

- CS#,input,片选信号;

- SCK,input,串行时钟;

- SI/IO0,inout,在 single mode 下的串行输入,在 Dual/Quad mode 下的 IO0;

- SO/IO1,inout,在 single mode 下的串行输出,在 Dual/Quad mode 下的 IO1;

- WP#/IO2,inout,在 single/Dual mode 下的写入保护,Quad mode 下的 IO2。在该管脚作为写入保护管脚时,当 WP# 为LOW时,在 WRR 命令期间,如果状态寄存器的状态寄存器写禁用(SRWD)位被设置为 1 时,将无法写入状态和配置寄存器,这可以防止状态寄存器的块保护(BP2、BP1、BP0)和 TBPROT 位的任何更改。同时,如果在 WRR 命令期间 WP# 为低电平,内存区域中受块保护和 TBPROT 位保护的所有数据字节也将被硬件保护,防止数据修改。WP# 芯片内部存在上拉电阻。

- HOLD#/IO3,inout,在 single/Dual mode 下的保持/暂停传输控制信号,Quad mode 下的 IO3。HOLD# 信号可用于暂停与设备的任何串行通信,而无需取消片选(CS#)或停止串行时钟(SCK),在 HOLD# 拉低后,若 SCK 处于 LOW,则立即进入保持状态,否则会在 SCK 的下降沿到达时进入保持状态,如下图。需注意,HOLD 不会终止已经在执行的操作。HOLD# 芯片内部存在上拉电阻。

在 SDR 情况下,FLASH 会在 SCK 上升沿寄存数据,并在 SCK 下降沿转换输出数据;在 DDR 模式下将在 SCK 的每个边沿进行数据转换。

在 single mode(也即传统的 SPI 协议)下,通过 SI 进行数据写入,通过 SO 进行数据读取;在 Dual/Quad Output mode 下,通过 SI 进行指令和地址的写入,而分别通过 IO0/IO1、IO0/IO/IO2/IO3 进行数据读回;而在 Dual/Quad Input/Output mode 下,通过 SI 传输指令,分别通过 IO0/IO1、IO0/IO1/IO2/IO3 进行地址写入(及可能存在的模式写入)和数据读回。

SPI 时钟模式

S25FL256S 支持两种模式的 SPI 时钟:

- mode 0,时钟极性 CPOL=0,时钟相位 CPHA=0;

- mode 3,时钟极性 CPOL=1,时钟相位 CPHA=1;

SDR

在 SDR 模式,两种时钟模式下,芯片都是在 SCK 上升沿锁存数据,在 SCK 下降沿转换数据。两种模式的不同之处在于空闲状态下 SCK 的状态,如下图所示

DDR

DDR 模式也支持以上两种时钟模式。指令位总是锁定在时钟的上升边缘,与 SDR 模式中相同。而地址和输入输出数据都被锁定在 SCK 的上升和下降边缘上。如下图

工作模式

在 single mode 模式以及 Dual/Quad Output Commands 模式下,命令和地址在 SI 线上单比特传输,而数据分别从 SO、IO0/IO1、IO0/IO1/IO2/IO3 传输;在 Dual/Quad I/O Commands 模式下,命令在 SI 上传输,而地址和数据都以数据对的形式在 IO0/IO1、IO0/IO1/IO2/IO3 上传输。时序分别如下图

- Single Bit Wide Commands

- Single Bit Wide I/O Commands

- Dual/Quad Output Commands

- Dual/Quad I/O Commands

- DDR Single Commands

- DDR Dual/Quad I/O Commands

在图中读数据时序中的 Dummy 阶段,S25FL256S 不会对 I/O 进行响应,期间 FLASH 正在准备数据,Dummy 延迟的长度由配置寄存器的 CR[7:6] 决定。Dummy 期间,应当保持 CS#=L、RESET#=H、HOLD#/IO3=H,WP#/IO2 被忽略。由于 HOLD、WP 内部都具有上拉电阻,因此建议在 Dummy 期间主控端释放 IO0~IO3,以避免可能出现的驱动器冲突。

FLASH存储阵列(地址空间映射)

S25FL 系列的 FALSH 存储阵列被划分为被称为**扇区(Sector)**的擦除单元。这些 Sector 要么是 4kB 和 64kB 扇区的组合,要么是统一的 256kB 扇区,与 FLASH 型号有关。对于笔者使用的 S25FL256SAGNFI00,关于其 Sector Type 的描述为 ‘A hybrid of 32 x 4-KB sectors with all remaining sectors being 64 KB, with a 256B programming buffer’,因此是如下的结构

对于 FL-S 系列具有 64KB Sector 的 128Mb/256Mb 芯片,针对 4KB Sector 区域,可以使用支持一次清除 4KB 的擦除命令,也可以使用 64KB 的擦除命令来一次性擦除 16 个 4KB 扇区。

FL-S 128Mb 和 256Mb 具有混合扇区架构的 FLASH,其 4KB 扇区在初次交付时位于阵列地址的底部。然而,配置寄存器的 TBPARM 位 (Configuration Register 1 - bit2,CR1[2] )可以被编程以反转扇区映射,以将 4-KB 扇区放置在阵列地址映射的顶部。因此用户必须检查 TBPARM 位,以确定扇区是否被倒置。

常用寄存器及相关指令

寄存器状态有易失性(Volatile)、非易失性(Non-Volatile)、一次性可编程(OTP,One Time Programmable)等,其中非易失性和 OTP 类型的寄存器初始值与出厂时的配置有关,非易失性寄存器的持久性与 FLASH 存储阵列的相同。

Status Register 1 (SR1)

SR1 寄存器相关指令:读 SR1 指令(RDSR1 05h)、写寄存器指令(WRR 01h)、写使能 (WREN 06h)、写失能(WRDI 04h)、清空状态寄存器(CLSR 30h)。

- SR1[7],SR1 寄存器写失能,非易失性,为 1 时启用 WP# 的写保护功能。当 SRWD=1 且 WP#=H ,或 SRWD=0 时,SRWD 和 BP 位可以被 WRR 命令改变;

- SR1[6],指示编程是否发生错误,易失性,只读,可使用 CLSR 重新置零;

- SR1[5],指示擦除是否发生错误,易失性,只读,可使用 CLSR 重新置零;

- SR1[4:2],块保护。当 CR1[3] 为 0 时,BP[2:0] 为非易失性,出厂时默认值被设为 0;当 CR1[3] 为 1 时,为易失性,且默认值为 1;

- SR1[1],SR1 写使能,易失性,为 1 时可以进行写寄存器操作(WRR)、flash 编程和擦除操作。该位只会由 WREN、WRDI 命令影响,不会被 WRR 写入。由于默认值为 0,因此如果要写寄存器(WRR)、编程/擦除 flash,需要先执行 WREN 命令,随后才能执行对应命令;

- SR[0],指示设备是否忙碌,只读,1 表示设备忙,0 表示空闲。

Status Register 2 (SR2)

SR2 相关指令:读 SR2 指令(RDSR2 07h)。

- SR2[1],擦除挂起,只读;

- SR2[0],编程挂起,只读。

Configuration Register 1 (CR1)

CR1 相关指令:读 CR1 指令(RDCR 35h)、写寄存器指令(WRR 01h)。在 16 数据周期的 WRR 命令中,可以对 CR1 进行写入操作。注意到 WRR 命令对应了多个寄存器的写入,如何控制 WRR 写入不同寄存器见本文下一小节。

-

CR1[7:6],控制延迟周期的 mode 和 Dummy 的长度,在不同时钟模式(SDR/DDR)和芯片型号(高性能 HPLC、增强高性能 EHPLC)下不尽相同,详见官方手册;

-

CR1[5],块保护配置起始。SR1 的 BP[2:0] 位允许用户可选择地保护阵列的一部分,范围从1/64、1/4、1/2等,一直到整个阵列,当TBPROT 被设置为 0 时,块保护被定义为从数组的顶部(最大地址)开始。出厂时 TBPORT 被配置为 0,如果被配置为 1 后,再尝试将它修改回 0 将会失败,并置位 R_ERR(SR1[6]),下面几个 OTP 的也是;

-

CR1[3],配置 SR1[4:2](BP[2:0])是否为易失性;

-

CR1[2],配置 Sector 地址是否倒置。由于 CR1[5:2] 都是 OTP 的,因此用户务必要检查这几个位;

-

CR1[1],非易失性,1 配置设备到 Quad 模式,0 则为 Dual 或 Single 模式。在配置到 1 时,WP# 与 HOLD# 功能不被监控,并在内部置为 HIGH,这两个引脚被用作 IO2、IO3。要使用 Quad Output Read、Quad I/O Read、Quad Page Programming 等四元功能时必须置位 Quad bit,而 Dual、Single 的操作不受影响,只是不需要驱动 WP# 和 HOLD# 了;

-

CR1[0],是否启用块保护以及 OTP 锁定。Freeze 位默认为 0,当 Freeze 位置为 1 时,将锁定状态寄存器中的 BP[2:0] 位、配置寄存器中的 TBPROT 和 TBPARM 位以及 OTP 地址空间(S25FL-S 具有独立的 1024 Byte 的 OTP 空间,被分为 32 个 32Byte 的Sector)。一旦 Freeze 位被置为 1,就只能通过断电重启或硬件复位重新置 0,而通过 WRR 或软复位重新置为 0 的尝试都会失败。

关于 BP 位、TBPROT 位设置下的保护范围见下表

Autoboot Register (ABR)

ABRD 相关指令:AutoBoot Read(ABRD 14h) 、 AutoBoot Write(ABWR 15h)。Autoboot 寄存器提供了一种自动读取启动代码的方法,作为开机重置、硬件重置或软件重置过程的一部分。

-

ABR[31:9],为启动引导代码的起始地址。ABSA 为 512 字节对齐地址,23bit 地址支持最大 32Gbit 地址空间的寻址,对于 256Mb 设备而言,只会用到 065535dec(0h00FFFFh);

-

ABR[8:1],启动代码延迟;

-

ABR[0],Autoboot 使能。

Bank Address Register (BAR)

BRAC 相关指令:访问块地址寄存器(BRAC B9h)、块地址寄存器读(BRRD 16h)、块地址寄存器写 (BRWR 17h)。

该寄存器用于扩展高位地址,以实现对 3Byte 命令的兼容。对于 128Mb 以下的设备,只需要 24 位地址就可以访问(字节地址),而对于 256Mb 以上容量的设备,就需要第四字节来提供对更高地址的访问。对于遗留的 3 字节命令,需要该寄存器提供额外的高位地址。

-

BAR[7],EXTADD,易失性,默认值 0。当为 1 时,所有 3Byte 遗留指令也同新版指令一样采用 32bit 寻址,本寄存器的 BRAC[6:0] 不被使用;当为 0 时,遗留指令采用传统的 24bit 寻址,而由 BRA[6:0] 提供对高位地址的补充(由于当前只有最大 256Mb 的设备,所以只用到了 BRA[0])。所以还是建议 256Mb 以上的设备直接采用新版的采用 32bit 寻址的命令,方便好多;

-

BAR[0],高位地址补充。

关于部分常用命令的解释

写使能命令(WREN 06h)

任何编程非易失性存储空间的指令执行前都要先执行 WREN 命令,该命令会置位 WEL(SR1[1])位。在上电、硬复位、相关编程命令执行完成后,WEL 都会重新复位为 0:

写寄存器命令(WRR 01h)

WRR 命令可以写 SR1 和 CR1 寄存器,有 8 数据周期、16 数据周期两种,如果 CS# 在第 8 个数据周期后拉高,则只会写 SR1,而如果在 16 数据周期后再拉高 CS#,则会在 CS# 拉高后同时写入 SR1 和 CR1。

Autoboot

自动引导功能允许主机内存控制器在复位结束后立即从 S25FL-S 设备获取引导代码,而无需发送读取命令,这节省了 32 个或更多的周期,并简化了启动引导代码读取所需的逻辑。ABE bit(ABR[0])控制 Autoboot 功能是否启用。

在上电、硬复位、命令复位(RESET F0h)后,Autoboot 功能将从预定地址(ABSA, ABR[31:9])自动读取引导程序,主控制器只需要将 CS# 拉低并给入 SCK,则 S25FL-S 设备将在延迟指定周期(ABSD, ABR[8:1])后输出代码流,在 CS# 拉高前将持续移出高位数据。需要注意,如果 ABSD=0,则 SCK 最大支持 50MHz。

在 Autoboot 输出至少一个字节数据后任意时刻拉高 CS#,设备将回到标准 SPI 模式,可以接收并响应各种指令。

根据 QUAD bit(CR1[1])的配置情况,将分别在 SI 或 IO0~IO3 上传回数据。

读 flash 命令

关于 main flash memory 的一系列读取命令,可以从任意字节地址开始读取,只要 CS# 没有拉高,flash 会将地址自动加一,顺序输出下一字节数据。如果在顺序读取过程中地址达到了最大,那么下一个数据地址将为 0。

READ 命令和 FAST_READ 命令的时序都是一样的,只是支持的最大时钟不同,前者最大支持 50M,后者可支持最大 133MHz,时序如下

对于 Quad Output Read,时序如下,地址也是在 SI 上顺序给出,而数据在 IO0~IO3 上返回;Dual Output 类似,只不过数据只从 IO0~IO1 上返回,这两种指令都不存在 mode 位

对于 Dual I/O Read,地址和数据都在 IO0~IO1 上传输,根据芯片型号(HPLC or EHPLC)而决定有无 mode 字段

在存在模式位时,如果模式位为 Axh,则设备将保持在 Dual I/O 模式,在下一次 CS# 拉高再拉低后,可以直接从地址开始,而忽略命令字段,如下图

而如果模式位为 Axh 以外的任何值,设备都将在 CS# 拉高后回到传统的 SPI 模式下。

对于 Quad I/O Read 模式,地址和数据都在 IO0~IO3 上传输,具有 mode 字段

若 mode 字段为 Axh,则会在 CS# 拉高后保持在 Quad I/O 模式,可在下一个 CS# 下降沿后直接从地址字段开始

如果模式位为 Axh 以外的任何值,设备将在 CS# 拉高后回到传统的 SPI 模式下。

写 flash 命令

在执行写命令前必须先执行写使能命令 WREN,随后可以通过写 flash 命令写入 1~256/512 Byte 数据(具体最大数目以具体型号的 Page Size 确定),有 Page Programming(PP)、Singl Byte Programming 两类写指令。flash 存储空间的默认值为 1,通过写 flash 可以修改到 0 或保持为 1;如果 flash 中的数据已经被写入了 0,那么要修改回 1 必须通过擦除命令实现。

对于 Page Programming,Page 在 Page 大小边界对齐,建议每次编程 16 Byte 的倍数个数据,且与 Page Size 对齐。Single Byte Programming 允许在任意字节地址写入单个字节数据(没有单独的 Single Byte Programming 命令,PP 命令可以在任意字节地址开始编程,因此兼容了 Single Byte Programming)。为了获取最优性能,建议 PP 在 Page 末尾处结束。

注意到写 flash 命令和 Erase 命令都依赖于 WEL bit(SR1[1]),因此一个完整的 flash 写过程如下:WREN --> Erase --> WREN --> Write Flash。

Page Programming 只能在单个 Page 里进行数据写入。如果 Addr 低 9/10 位(视 Page Size 决定)不为 0,则超出当前 Page 的数据会无法写入;而对于 Addr 低位为 0 的情况,由于 Programming Buffer 大小的限制,自然不会越界。

当 PP 一次写入少于一个 Page 的数据时,将从指定地址开始依次写入数据,而不对当前 Page 内的其他数据造成影响。为了优化写入时间,建议每次写入一个完整的 Page。

S25FL-S 有两类 PP 指令,Single Wide mode 和 Quad mode,而不支持 Dual mode。对于 Single mode,时序如下,最高可支持 133 MHz

对于 Quad mode,时序如下,最大支持 80MHz

需注意,这里不像 Quad I/O Read,不支持地址通过 IO0~IO3 传输,只能通过 SI 单线传输。

Programming 过程可以被编程挂起命令(Program Suspend, PGSP 85h)中断,然后可以从其他非擦除 Sector 或非编程挂起的 Page 中读取数据,可以通过编程恢复命令(Program Resume, PGRS 8Ah)恢复写入。

flash 擦除命令

有两类擦除命令:扇区擦除命令(Sector Erase, SE)、批量擦除命令(Bulk Erase, BE)。SE 命令仅擦除一个扇区,而 BE 命令会擦除整个 flash。在擦除命令的 CS# 拉高后,擦除循环就会启动;由于擦除过程较慢,因此用户可以检查 WIP bit(SR1[0])查看是否完成擦除,擦除过程中 WIP=1,擦除完成后 WIP 将为 0。CS# 必须在最后一个地址位被移入后拉高,才可以启动擦除循环;如果没有被拉高,将不会进行擦除。

可以通过 4P4E(21h)擦除 4KB 扇区,通过 4SE(DCh)擦除一个标准扇区(64KB 或 256KB),擦除操作会将扇区所有单元的值置为 1。4P4E 只能用于擦除 4KB 扇区,对于其他扇区将不会执行,且不会置位 E_ERR bit(SR1[5]),而应用于被保护的 4KB 扇区时,则会擦除失败,并置位 E_ERR bit。SE 命令用于受保护扇区时,也会擦除失败并置位 E_ERR bit。时序如下

批量擦除命令(Bulk Erase, BE 60h or C7h),会将整个闪存中所有 bit 置 1。必须在第 8 个SCK 后拉高 CS# 以启动擦除循环,否则擦除循环不会启动。只有当 BP[2:0] 都为 0 时才能启动 BE,否则将不会执行 BE,也不会置位 E_ERR bit。

可以通过擦除挂起命令(Erase Suspend, ERSP 75h)和擦除恢复命令(Erase Resume, ERRS 7Ah)挂起/恢复擦除操作。执行擦除挂起命令后,需要等待 t E S L t_{ESL} tESL 后设备才会挂起并置位 ES bit(SR2[1]),之后可以执行其他操作。擦除挂起命令只在 SE 操作期间有效,而 BE 操作期间将被忽略。在擦除挂起后,WIP bit 会被置 0,此时可以检查 ES bit 查看当前是擦除挂起(ES=1)还是擦除完成(ES=0)。

FPGA 实现(思路)

(行文至此,内容较多,就不再附代码了,先进行思路的介绍,之后另开一篇专门放代码)

笔者的芯片具体型号为 S25FL256SAGNFI00,存储容量 256Mb,增强高性能 EHPLC,4KB 与 64KB 混合 Sector 的存储阵列,256 Byte 的 Page Programming Buffer 大小,最高支持 133MHz,无硬复位 RESET# 引脚。

为简单起见,采用 SDR 时钟模式;为了兼顾读写速度,采用 Quad mode;同时考虑到 Quad Page Programming 地址只能通过 SI 单线传输,因此读、写 FLASH 分别采用 Quad Output Read、Quad Page Programming,以实现时序格式的统一,简化编程。

由于 S25FL-S 在 SCK 上升沿锁存数据,在 SCK 下降沿转换数据,因此主控端应在 SCK 下降沿转换数据,在 SCK 上升沿锁存数据。

由于写 FLASH 需要先进行写使能以及擦除操作,而擦除操作需要检查 WIP bit(SR1[0]);要使用 Quad 读写模式,需要置位 Quad bit(CR1[1]);要判断地址映射类型和四元读模式下的 Dummy 长度,需要实现读写寄存器。因此需要实现以下功能:写使能 WREN、写失能 WRDI、写寄存器 WRR、清除状态寄存器 CLSR、读状态寄存器 RDSR1/RDSR2、读配置寄存器 RDCR、擦除操作(扇区擦除 4SE、批量擦除 BE)、四元编程操作 4QPP、Quad Output Read 操作 4QOR 等。

为每一种功能单独写一个模块当然也是可行的思路,但过于繁杂;观察到在时序层面上述指令可以归类为简单的四种:单 8bit 指令(如 WREN、WRDI、CLSR、BE 等)、写寄存器(8bit 指令后跟随 1~4Byte 数据,SI 单线传输,如 WRR、ABWR、BRWR 等,甚至 8bit 指令 + 4Byte 地址的 4SE 也可归于此类)、读寄存器(8bit 指令(SI)后跟随 1~4Byte 输出(SO),如 RDSR1、RDSR2、RDCR1、ABRD、BRRD 等)、四元写 FLASH (8bit 指令(SI)+ 32bit 地址(SI)+ 1~256Byte 数据(IO0~IO3写),如 4QPP)、四元读 FLASH (8bit 指令(SI)+ 32bit 地址(SI)+ xbit Dummy + xByte 数据(IO0~IO3读回),如 4QOR)。

因此可以首先实现以上四个基础模块,然后根据需要在上层模块中用状态机控制几个基础模块的运行。

(完)

相关文章:

S25FL256S介绍及FPGA实现思路

本文介绍 S25FL256S 这款 FLASH 芯片,并进行 FPGA 读写控制的实现(编程思路及注意事项)。 文章目录 S25FL-S 介绍管脚功能说明SPI 时钟模式SDRDDR 工作模式FLASH存储阵列(地址空间映射)常用寄存器及相关指令Status Reg…...

淘宝客APP源码/社交电商自营商城源码/前端基于Uniapp开发

淘宝客APP源码,前端基于Uniapp开发的社交电商自营商城源码。Thinkphp的后台,不是很标准,感兴趣的可以自行研究。 商城功能 1、首页基础装修;2、丰富选品库;3、淘口令解析;4、支持京东;5、支持…...

Oracle 服务器日常巡检

文章目录 1、数据库基本状况检查2、数据库相关资源使用情况检查3、检查Oracle数据库性能4、数据库服务器CPU、MEM、I/O性能5、数据库服务器安全检查 Oracle数据库的日常巡检内容包括: (1)Oracle数据库基本状况检查; (…...

【轨道机器人】实现Windows与下位机串口通信(未完成)

方案一:QT,编写类似串口调试助手的APP,连接上硬件,qt有个好像是串口缓存函数,可以防止占用CPU。(缺点qt估计要时间学) 方案二:利用vscode、C,编写一个可执行exe文件&…...

无人机内存卡数据恢复

1.插入内存卡 2.选择对应的品牌 3.点击恢复 建议:发现数据打不开或者丢失情况,建议及时断电,以免影响数据的正常恢复! #无人机##数据恢复##储存卡#...

基于SSM的校园二手物品交易市场设计与实现

末尾获取源码 开发语言:Java Java开发工具:JDK1.8 后端框架:SSM 前端:Vue 数据库:MySQL5.7和Navicat管理工具结合 服务器:Tomcat8.5 开发软件:IDEA / Eclipse 是否Maven项目:是 目录…...

Android14 Beta 5

Beta 5,这是 Android 14 Beta 计划中的最后一次计划更新。这是确保您的应用程序已准备就绪并在非 Beta 用户开始获取 Android 14 之前提供反馈的最后机会。为了使您能够在跨多种外形尺寸的设备上测试您的应用程序,Beta 5 适用于 Pixel Tablet 和 Pixel F…...

力扣labuladong——一刷day32

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、力扣654. 最大二叉树二、力扣105. 从前序与中序遍历序列构造二叉树三、力扣106. 从中序与后序遍历序列构造二叉树四、力扣889. 根据前序和后序遍历构造二叉…...

Day01_《MySQL索引与性能优化》摘要

一、资料 视频:《尚硅谷MySQL数据库高级,mysql优化,数据库优化》—周阳 其他博主的完整笔记:MySQL 我的笔记:我的笔记只总结了视频p14-p46部分,因为只有这部分是讲解了MySQL的索引与explain语句分析优化…...

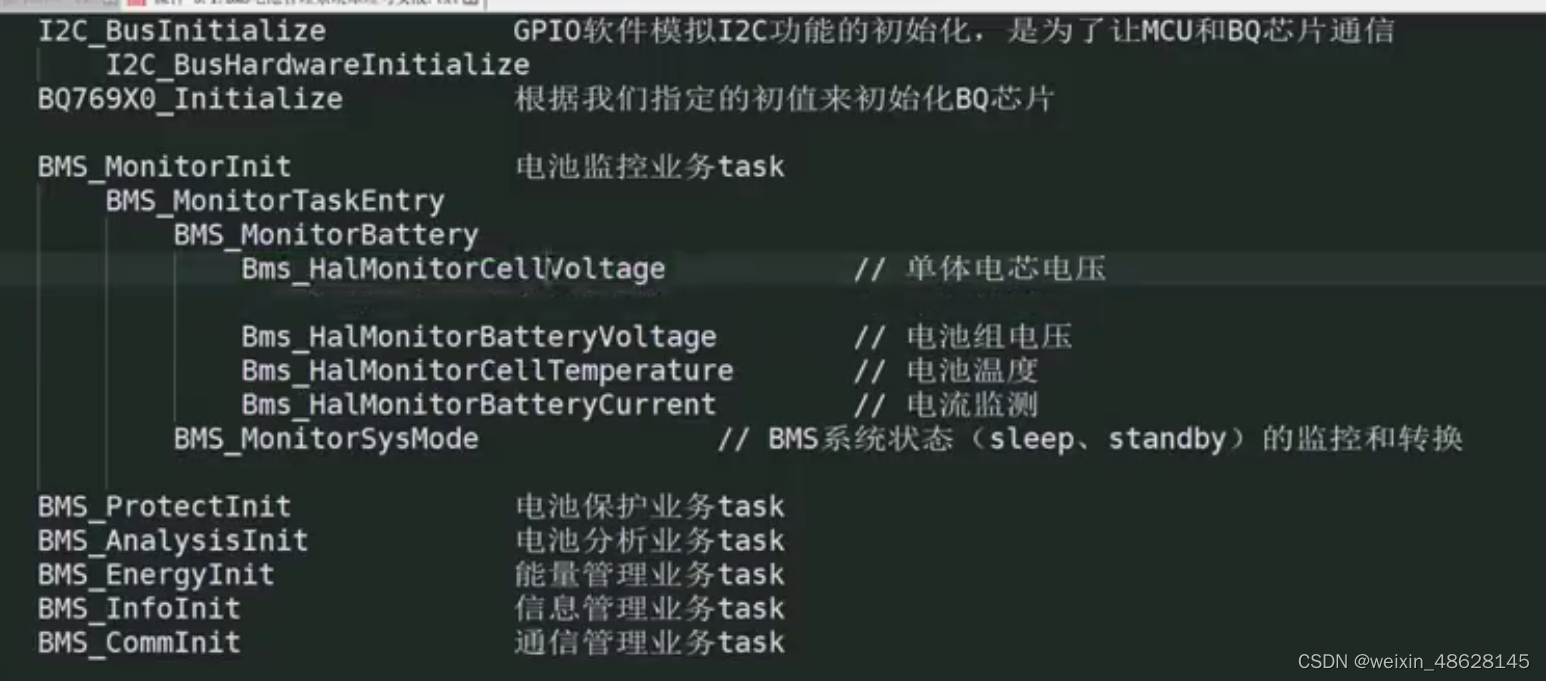

BMS系统项目

1、通过电压监测是否冲满,通过电压可以监测是否放完电 电池得参数 单体过压(充满电) 过压恢复(百分之90多) 欠压保护(百分之几得电,快关机了) 欠压恢复(就是欠压之上…...

sql server 多行数据合并一行显示

在 SQL Server 中,可以使用 STUFF 和 FOR XML PATH 进行多行合并成一行。例如,假设有一个表名为 orders ,其中包含订单号和产品名称: order_idproduct_name1Product A1Product B2Product C2Product D 以下查询将在 order_id 列上…...

「我的AIGC咒语库:分享和AI对话交流的秘诀——如何利用Prompt和AI进行高效交流?」

文章目录 每日一句正能量前言基础介绍什么是Prompt?什么是 Prompt Engineering?为什么需要 Prompt Engineering?如何进行 Prompt Engineering?Prompt的基本原则Prompt的编写模式AI 可以帮助程序员做什么?技术知识总结拆解任务阅读…...

强国有我助力苔花绽放 | 爱心捐赠仪式在西安顺利举办

2023年11月2日,由中国儿童中心、全国少年儿童“双有”主题教育活动组委会、中华少年儿童慈善救助基金会强国有我项目主办,陕西省青少年宫协会、陕西省妇女儿童活动中心、陕西回归儿童救助中心承办的“苔花绽放”事实无人抚养儿童关爱计划捐赠仪式在陕西回…...

Flink SQL -- CheckPoint

1、开启CheckPoint checkpoint可以定时将flink任务的状态持久化到hdfs中,任务执行失败重启可以保证中间结果不丢失 # 修改flink配置文件 vim flink-conf.yaml# checkppint 间隔时间 execution.checkpointing.interval: 1min # 任务手动取消时保存checkpoint execu…...

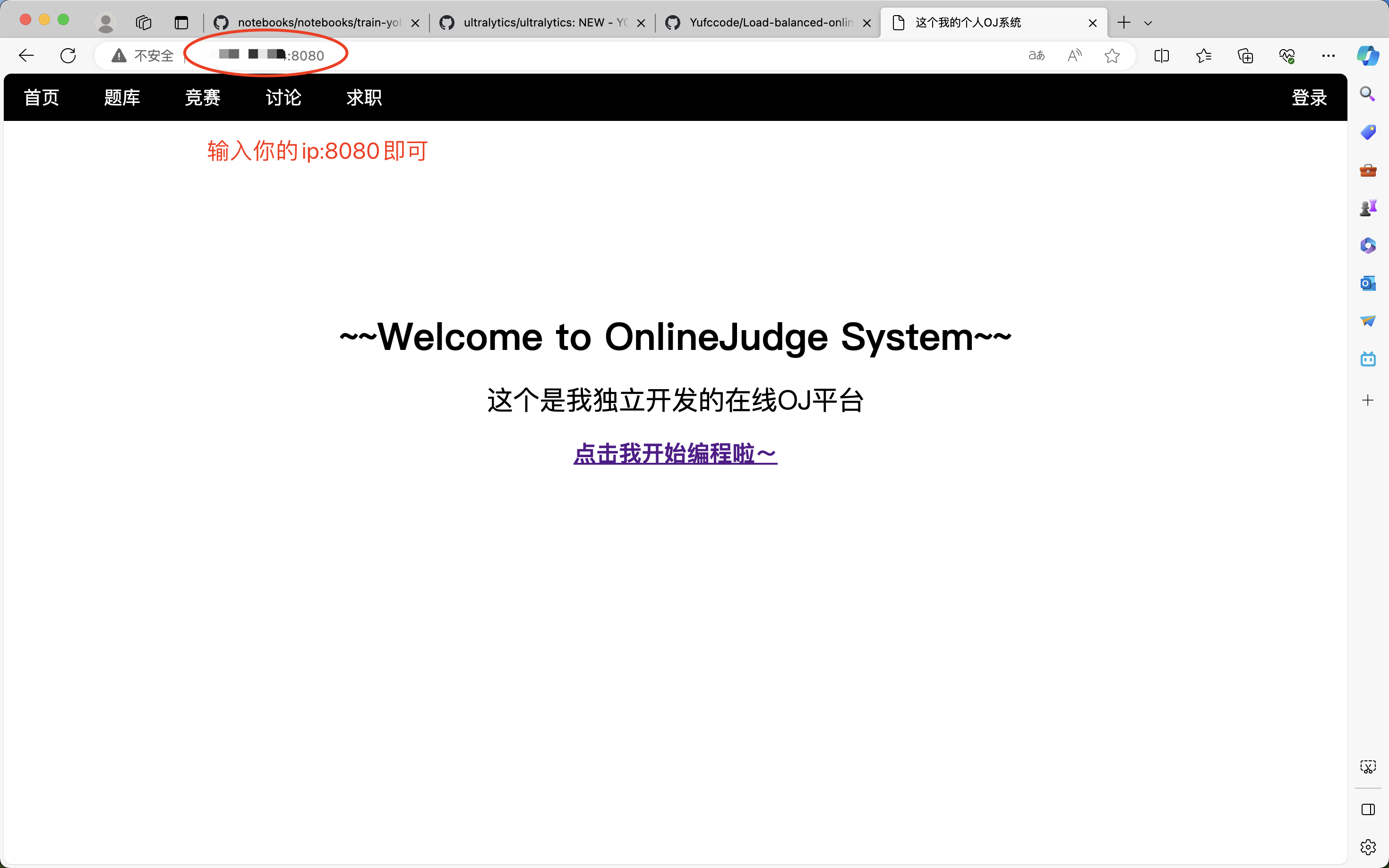

Load-balanced-online-OJ-system 负载均衡的OJ系统项目

前言 那么这里博主先安利一些干货满满的专栏了! 首先是博主的高质量博客的汇总,这个专栏里面的博客,都是博主最最用心写的一部分,干货满满,希望对大家有帮助。 高质量博客汇总 本项目Github地址 - Load-balanced-o…...

ES6 导入导出

ES6 导入导出 ES6引入了原生的模块化支持,使得JavaScript代码可以被划分为可重用的模块。这些模块可以导出部分代码(如函数、对象、类等),并被其他模块导入使用。 export 命名导出(Named Exports) 可以从…...

【Liunx】部署Ansible自动化运维工具

Ansible自动化运维工具 概述安装部署1.通过yum下载Ansible2.对自己做免密配置3.修改ansiable host配置对服务器进行分组4.测试:对所有服务器进行ping命令5.写playbook6.执行我们写的playbook脚本7.验证 概述 ansible是新出现的自动化运维工具,基于Pytho…...

Python的基础语法

1. 注释:在Python中,使用井号(#)表示单行注释,三个单引号()或三个双引号(""")表示多行注释。 2. 变量:在Python中,不需要声明变量…...

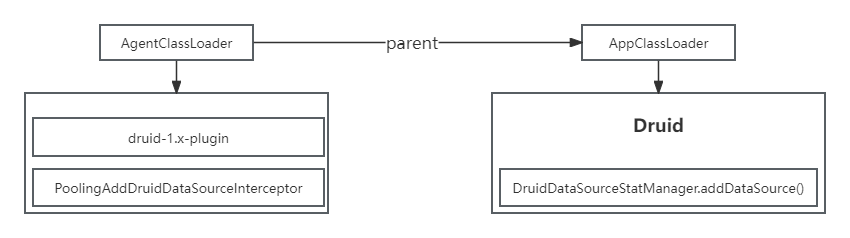

Skywalking流程分析_8(拦截器插件的加载)

前言 在之前的文章中我们将,静态方法、构造方法、实例方法的增强逻辑都分析完毕,但在增强前,对于拦截类的加载是至关重要的,下面我们就来详细的分析 增强插件的加载 静态方法增强前的加载 //clazz 要修改的字节码的原生类 Sta…...

智能AI系统ChatGPT网站源码+支持OpenAI DALL-E3文生图+支持ai绘画(Midjourney)/支持GPT全模型+国内AI全模型

一、AI创作系统 SparkAi创作系统是基于OpenAI很火的ChatGPT进行开发的Ai智能问答系统和Midjourney绘画系统,支持OpenAI-GPT全模型国内AI全模型。本期针对源码系统整体测试下来非常完美,可以说SparkAi是目前国内一款的ChatGPT对接OpenAI软件系统。那么如…...

企业级OA系统高可用方案:泛微ecology+Nginx负载均衡最佳实践

企业级OA系统高可用架构设计与实践:泛微ecologyNginxResin全栈解决方案 在数字化转型浪潮中,办公自动化系统(OA)已成为企业核心IT基础设施。作为国内领先的协同管理平台,泛微ecology承载着企业关键业务流程,其稳定性直接影响组织运…...

技术无罪,人心可畏 —— 写在 315 “GEO 投毒” 话题之后

2026 年央视 315 晚会,将镜头对准了人工智能领域的灰色地带 ——“AI 投毒” 与 “GEO” 一夜之间成为公众热议的话题。记者虚构了一款名为 “Apollo-9” 的智能手环,借助 “GEO 优化系统” 批量生成虚假内容,短短数小时就让多个主流 AI 大模…...

iptables实战指南:从链表关系到规则配置的完整解析

1. iptables基础概念与核心组件 第一次接触iptables时,我盯着那些复杂的规则配置看了整整一个下午。后来才发现,理解iptables的关键在于掌握它的"四表五链"架构。简单来说,iptables就像是一个多层安检系统,数据包要经过…...

抖音音频高效提取工具:从繁琐操作到一键解决方案

抖音音频高效提取工具:从繁琐操作到一键解决方案 【免费下载链接】douyin-downloader A practical Douyin downloader for both single-item and profile batch downloads, with progress display, retries, SQLite deduplication, and browser fallback support. 抖…...

Python 批量导出数据库数据至 Excel 文件

简介 langchain专门用于构建LLM大语言模型,其中提供了大量的prompt模板,和组件,通过chain(链)的方式将流程连接起来,操作简单,开发便捷。 环境配置 安装langchain框架 pip install langchain langchain-community 其中…...

PyTorch核心模块实战指南:从nn.Sequential到nn.MaxPool2d的深度解析

1. 快速上手nn.Sequential:像搭积木一样构建神经网络 第一次接触PyTorch时,我被各种复杂的网络结构吓到了——直到发现nn.Sequential这个"乐高积木盒"。这个容器让我能用拼积木的方式组合网络层,比如下面这个图像分类器的经典结构&…...

Qwen3智能字幕对齐系统与Dify工作流集成:打造自动化视频内容生产线

Qwen3智能字幕对齐系统与Dify工作流集成:打造自动化视频内容生产线 1. 引言 你有没有算过,一个视频剪辑师一天要花多少时间在字幕上?从听写、校对、再到调整时间轴,一个十分钟的视频,光是字幕可能就要耗掉一两个小时…...

RePKG:突破动态壁纸资源壁垒的开源工具

RePKG:突破动态壁纸资源壁垒的开源工具 【免费下载链接】repkg Wallpaper engine PKG extractor/TEX to image converter 项目地址: https://gitcode.com/gh_mirrors/re/repkg 当你面对一个包含丰富素材的动态壁纸资源包(PKG文件)却无…...

[Linux][虚拟串口]x一个特殊的字节

目标:构建带上下文记忆的猫咪聊天机器人 先看代码: from langchain_openai import ChatOpenAI from langchain_core.prompts import ChatPromptTemplate from langchain_core.messages import SystemMessage,HumanMessage,AIMessage import os from dote…...

Starry Night Art Gallery效果展示:黄金渐变按钮交互+实时生成反馈

Starry Night Art Gallery效果展示:黄金渐变按钮交互实时生成反馈 1. 沉浸式艺术体验:当AI遇见文艺复兴 想象一下,你走进的不是一个冰冷的AI工具界面,而是一座数字艺术殿堂。四周是深邃的墨蓝色背景,如同梵高笔下的夜…...