Verilog基础:时序调度中的竞争(一)

相关阅读

Verilog基础![]() https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482

作为一个硬件描述语言,Verilog HDL常常需要使用语句描述并行执行的电路,但其实在仿真器的底层,这些并行执行的语句是有先后顺序的,然而Verilog标准并没有将这些事件调度的顺序定死,而是给予了仿真器厂商一定的自由去实现自己的产品,这就导致了设计者如果不遵循一定的编程习惯,会导致意想不到的仿真结果,下面是一些相关的规则。

1、不要在两个及以上的always或initial结构中对同一个变量赋值

当两个以上的过程结构同时执行时,它们之间的执行顺序是不一定的,Verilog标准只规定了在一个顺序块(begin end)中的所有语句是按照其先后顺序执行的,但并没有规定同一个时间执行的多个结构的执行顺序,下面举例详细说明。

//例1

`timescale 1ns/1ps

module test();initial $display("The initial_0 execute");initial $display("The initial_1 execute");initial $display("The initial_2 execute");

endmodule在上例中,三个initial结构在0ns时同时执行,仿真器执行他们的顺序是不定的,但测试表明,许多仿真器都选择顺序执行这三个initial结构,如下所示。

对于Mentor Modelsim SE,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Aldec Riviera Pro,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Cadence Xcelium,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Mentor Questa,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Synopsys VCS,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Icarus Verilog,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute虽然看起来仿真器的行为都是一致的,但其实这只是一个巧合,下面的例子就体现出了各种仿真器对同一段代码之间的不同行为。

//例2

`timescale 1ns/1ps

module test();reg a;initial #5 a = 1;initial @(a) $display("The initial_0 execute");initial @(a) $display("The initial_1 execute");initial @(a) $display("The initial_2 execute");

endmodule这段代码的三个initial结构都对事件a敏感,所以在5ns时,三个initial结构同时被触发,而他们的执行顺序是不定的,如下所示。

对于Mentor Modelsim SE,输出结果为

The initial_2 execute

The initial_1 execute

The initial_0 execute对于Aldec Riviera Pro,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Cadence Xcelium,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Mentor Questa,输出结果为

The initial_2 execute

The initial_1 execute

The initial_0 execute对于Synopsys VCS,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execut对于Icarus Verilog,输出结果为

The initial_2 execute

The initial_1 execute

The initial_0 execute下面的代码中仍然体现了同一时间的多个结构的执行顺序是不定的,即使触发这些结构的事件在同一时间是有前后关系的。

//例3

`timescale 1ns/1ps

module test();reg a, b, c;initial begin#5;a = 1;b = 1;c = 1;endalways @(a) $display("The initial_0 execute");always @(b) $display("The initial_1 execute");always @(c) $display("The initial_2 execute");

endmodule在5ns时,a、b、c先后被赋值为1,Verilog标准保证了begin end块中的赋值顺序从上到下。但由这些赋值语句触发的其他always结构呢?是否也会按照a、b、c的顺序执行呢?

对于Mentor Modelsim SE,输出结果为

The initial_2 execute

The initial_1 execute

The initial_0 execute对于Aldec Riviera Pro,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Cadence Xcelium,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute对于Mentor Questa,输出结果为

The initial_2 execute

The initial_1 execute

The initial_0 execute对于Synopsys VCS,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execut对于Icarus Verilog,输出结果为

The initial_0 execute

The initial_1 execute

The initial_2 execute依然可以注意到不同仿真器之间的差异,为什么不都是按照a赋值,always @(a)执行,b赋值,always @(b)执行,c赋值,always @(c)执行的顺序执行呢?还是那句话,Verilog标准只规定了一个顺序块(begin end)中的所有语句是按照其先后顺序执行的,并没有保证其他行为。当a赋值后,always @(a)被调度了,但他不一定会在b赋值之前执行,有可能在执行完b赋值、c赋值之后再来执行always @(a),此时always @(b)和always @(c)也应该在队列中,他们执行的先后顺序是标准没有保证的(但需要注意的是,最基本的调度者和被调度者的先后关系是无法改变的,即always @(a)一定在a赋值后,b、c亦然)。下面是一个经典的两个结构交错执行的例子。

//例4

`timescale 1ns/1ps

module test();reg a;wire b;initial begin#1;a = 1;#1;a = 0;$display("b is %b", b);endassign b = a;endmodule当时间来到1ns,a被赋值为1,同时触发assign结构,对b连续赋值为1。1ns后,a被更改为0,紧接着打印b的值,结果是1还是0呢?

对于Mentor Modelsim SE,输出结果为

b is 1对于Aldec Riviera Pro,输出结果为

b is 1对于Cadence Xcelium,输出结果为

b is 1对于Mentor Questa,输出结果为

b is 1对于Synopsys VCS,输出结果为

b is 0对于Icarus Verilog,输出结果为

b is 0上面的结果显示,仿真器可能在执行了a=0的赋值后立刻执行被调度的assign连续赋值,再返回initial结构执行显示语句,也可能继续执行下面的显示语句,再去执行被调度的assign连续赋值。

这就给了我们一个启示,在改变了一个全组合逻辑的电路的输入后,紧接着显示输出,可能无法得到更新后的输出。一个更好的做法是给$display语句一定的延时,这样就能确保在执行$display前,连续赋值已经执行完毕,因为不同时间的语句执行是不会产生竞争的。

//例5

`timescale 1ns/1ps

module test();reg a;wire b;initial begin#1;a = 1;#1;a = 0;#0.01 $display("b is %b", b);endassign b = a;endmodule相关文章:

Verilog基础:时序调度中的竞争(一)

相关阅读 Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 作为一个硬件描述语言,Verilog HDL常常需要使用语句描述并行执行的电路,但其实在仿真器的底层,这些并行执行的语句是有先后顺序…...

)

nginx 配置静态缓存全教程 (以及静态缓存文件没有生成)

一、第一步定义一个缓存目录设置目录结构 在 http 模块下定义(keys_zone 缓存区名:后面是缓存区大小 inactive 不活跃的文件多久清理 max_size 缓存区所占磁盘的上限 use_temp_path 默认关闭(有需要自己百度)) proxy_cache_path /path/your…...

自己动手打包构建编译cri-dockerd

1.背景 本机是 armv7l架构cpu,发现官方文档中竟然没有,因此需要自己编译下; [rootcontainer0 ~]# uname -a Linux container0 5.4.206-v7l.1.el7 #1 SMP Mon Jul 25 14:13:29 UTC 2022 armv7l armv7l armv7l GNU/Linux2.打包/构建/编译 gi…...

Self-Supervised Exploration via Disagreement论文笔记

通过分歧进行自我监督探索 0、问题 使用可微的ri直接去更新动作策略的参数的,那是不是就不需要去计算价值函数或者critic网络了? 1、Motivation 高效的探索是RL中长期存在的问题。以前的大多数方式要么陷入具有随机动力学的环境,要么效率…...

【网络奇幻之旅】那年我与区块链技术的邂逅

🌺个人主页:Dawn黎明开始 🎀系列专栏:网络奇幻之旅 ⭐每日一句:追光的人,终会光芒万丈 📢欢迎大家:关注🔍点赞👍评论📝收藏⭐️ 文章目录 &#…...

1.5.1 git/svn日志格式规范

文章目录 git日志规范一 基本原则二 日志格式1 type:2 keys3 subject4 body5 footergit日志规范 一 基本原则 《规则1》小步提交,每个功能模块分别提交 《规则2》源文件与修改文件,分别提交 《规则3》 二 日志格式 type:keys:subject:body:footer 1 type: - `feat`: 新…...

[autojs]ui线程中更新控件的值的问题

"ui"; ui.layout(<vertical><button id"autoFloatWindow" text"开启悬浮窗" textSize"15sp" /><button id"autoService" text"开启无障碍服务" textSize"15sp" /><button id"…...

机器视觉技术在现代汽车制造中的应用

原创 | 文 BFT机器人 机器视觉技术,利用计算机模拟人眼视觉功能,从图像中提取信息以用于检测、测量和控制,已广泛应用于现代工业,特别是汽车制造业。其主要应用包括视觉测量、视觉引导和视觉检测。 01 视觉测量 视觉测量技术用于…...

学习视频剪辑方法:AI智剪助力,批量处理短视频无忧

随着短视频的兴起,越来越多的人开始关注如何有效地制作和发布这些内容。但是,短视频的制作并不容易,要耗费大量的时间和精力。现在有很多AI智能剪辑工具可以快速、高效地制作短视频。其中,AI智剪是一款非常受欢迎的视频剪辑功能&a…...

振南技术干货集:制冷设备大型IoT监测项目研发纪实(3)

注解目录 1.制冷设备的监测迫在眉睫 1.1 冷食的利润贡献 1.2 冷设监测系统的困难 (制冷设备对于便利店为何如何重要?了解一下你所不知道的便利店和新零售行业。关 于电力线载波通信的论战。) 2、电路设计 2.1 防护电路 2.1.1 强电防护…...

1143. 最长公共子序列

给定两个字符串 text1 和 text2,返回这两个字符串的最长 公共子序列 的长度。如果不存在 公共子序列 ,返回 0 。 一个字符串的 子序列 是指这样一个新的字符串:它是由原字符串在不改变字符的相对顺序的情况下删除某些字符(也可以…...

)

EASYEXCEL(一)

1.读取excel 读监听器 Slf4j public class StudentReadListener extends AnalysisEventListener<Student> {// 每读一样,会调用该invoke方法一次Overridepublic void invoke(Student data, AnalysisContext context) {System.out.println("data "…...

竞赛YOLOv7 目标检测网络解读

文章目录 0 前言1 yolov7的整体结构2 关键点 - backbone关键点 - head3 训练4 使用效果5 最后 0 前言 世界变化太快,YOLOv6还没用熟YOLOv7就来了,如果有同学的毕设项目想用上最新的技术,不妨看看学长的这篇文章,学长带大家简单的…...

第一类曲线积分@对弧长的曲线积分

文章目录 abstract对弧长的曲线积分曲线形构件的质量第一类曲线积分曲线积分存在性利用曲线积分的定义描述曲线形构件质量问题推广曲线积分可加性闭曲线积分 曲线积分性质曲线积分的计算方法证明(部分推导) 小结曲线弧显函数形式方程下的曲线积分公式推广例例例 abstract 在积…...

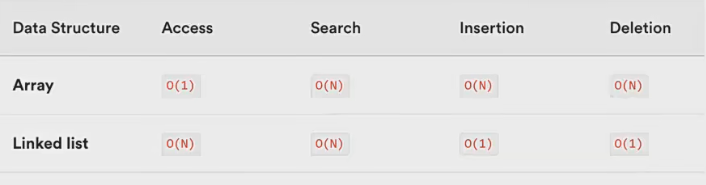

【TypeScript】常见数据结构与算法(二):链表

文章目录 链表结构(LinkedList)链表以及数组的缺点数组链表的优势 什么是链表?封装链表相关方法源码链表常见面试题237-删除链表中的节点206 - 反转链表 数组和链表的复杂度对比 链表结构(LinkedList) 链表以及数组的缺点 链表…...

)

原型模式 (Prototype Pattern)

定义: 原型模式(Prototype Pattern)是一种创建型设计模式,它用于创建重复的对象,同时保持性能。这种模式的核心思想是通过复制一个已存在的实例来创建新的实例,而不是新建实例并对其进行初始化。原型模式适…...

项目总结报告(案例模板)

软件项目总结报告模板套用: 项目概要项目工作分析经验与教训改进建议可纳入的项目过程资产 --------进主页获取更多资料-------...

C++ Qt QByteArray用法介绍

作者:令狐掌门 技术交流QQ群:675120140 csdn博客:https://mingshiqiang.blog.csdn.net/ 文章目录 一、QByteArray的基本用法1、初始化和赋值2、访问和修改元素3、 常用方法4、数据转换二、QByteArray与文件操作三、QByteArray与网络编程四、QByteArray数据编码1、Base64 编解…...

蓝桥杯物联网竞赛_STM32L071_3_Oled显示

地位: 对于任何一门编程语言的学习,print函数毫无疑问是一种最好的调试手段,调试者不仅能通过它获取程序变量的运行状态而且通过对其合理使用获取程序的运行流程,更能通过关键变量的输出帮你验证推理的正确与否,朴素的…...

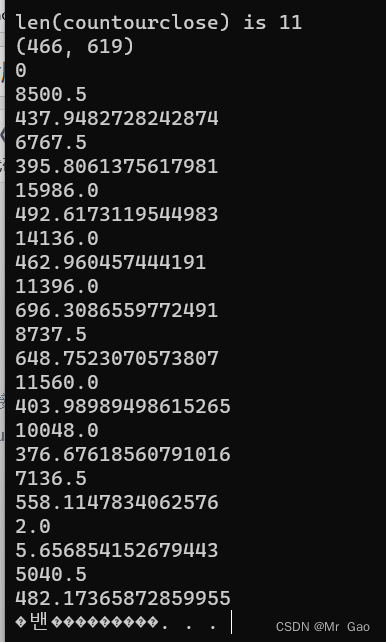

python-opencv轮廓检测(外轮廓检测和全部轮廓检测,计算轮廓面积和周长)

python-opencv轮廓检测(外轮廓检测和全部轮廓检测,计算轮廓面积和周长) 通过cv2.findContours,我们可以进行轮廓检测,当然也有很多检测模式,我们可以通过选择检测模式,进行外轮廓检测ÿ…...

Windows终极优化神器:5个实战场景完全指南,让系统管理变得简单高效

Windows终极优化神器:5个实战场景完全指南,让系统管理变得简单高效 【免费下载链接】winutil Chris Titus Techs Windows Utility - Install Programs, Tweaks, Fixes, and Updates 项目地址: https://gitcode.com/GitHub_Trending/wi/winutil 还…...

2026年Hermes Agent/OpenClaw如何安装?阿里云及Coding Plan配置详细解读

2026年Hermes Agent/OpenClaw如何安装?阿里云及Coding Plan配置详细解读。OpenClaw(前身为Clawdbot/Moltbot)作为开源、本地优先的AI助理框架,凭借724小时在线响应、多任务自动化执行、跨平台协同等核心能力,成为个人办…...

避坑指南:Ensembl版本混乱?手把手教你用biomaRt精准抓取指定版本基因组注释构建OrgDb

精准锁定Ensembl历史版本:biomaRt实战指南与OrgDb高效构建策略 当你在深夜加班分析绵羊RNA-seq数据时,突然发现差异表达基因的染色体位置与参考基因组对不上——这种版本不匹配的噩梦,每个生物信息学分析者都可能经历过。Ensembl数据库每季度…...

AD9371裸机程序里那些容易配错的坑:SPI片选、SYSREF与时钟链详解

AD9371裸机开发实战:SPI片选、时钟链与SYSREF配置避坑指南 当你在深夜的实验室里盯着示波器上杂乱的信号波形,AD9371评估板依然 stubbornly 保持沉默——这种场景对射频工程师来说再熟悉不过。作为一款高性能集成收发器,AD9371的裸机程序配置…...

》)

《UE5_C++多人游戏开发实战》学习笔记3 ——《P4 局域网联机测试与蓝图网络事件(LAN Testing Blueprint Networking)》

1. 局域网联机测试基础准备 在UE5中实现局域网联机功能前,我们需要先搭建好开发环境。我推荐使用最新的UE5.3版本,这个版本对多人游戏网络同步做了不少优化。创建一个第三人称模板项目时,记得选择"C"选项,这样我们既能用…...

)

用Python的SymPy库手把手验证sinx和cosx的泰勒展开式(附代码)

用Python的SymPy库手把手验证sinx和cosx的泰勒展开式(附代码) 泰勒展开式是高等数学中一个极其重要的概念,它将复杂的函数表示为无限多项式的和。对于理工科学生和开发者来说,理解泰勒展开不仅有助于深入掌握微积分,还…...

)

PlatformIO隐藏技巧:用Python脚本自动生成HEX文件(附STM32实测)

PlatformIO高阶技巧:Python脚本自动化生成HEX文件的深度实践 如果你已经习惯了Keil中一键生成HEX文件的便捷,却在PlatformIO中苦苦寻找这个功能,那么这篇文章正是为你准备的。PlatformIO作为现代嵌入式开发的利器,虽然默认不直接生…...

游戏鼠标指针太小看不清?YoloMouse开源工具三步解决光标可视化难题

游戏鼠标指针太小看不清?YoloMouse开源工具三步解决光标可视化难题 【免费下载链接】YoloMouse Game Cursor Changer 项目地址: https://gitcode.com/gh_mirrors/yo/YoloMouse 在激烈的游戏对战中,你是否曾因鼠标指针太小、颜色与背景融合而迷失方…...

如何测试FSFO观察者进程的自动切换_模拟主库断网与Observer心跳超时

FSFO Observer心跳超时不会触发切换,真正执行切换的是Data Guard Broker;Observer失联仅导致状态变为NOT RUNNING或UNKNOWN,Broker仍可依据主库不可达及阈值条件发起failover。FSFO Observer 进程是否在心跳超时后触发切换?fsfo&a…...

Adobe-GenP终极指南:如何免费解锁Adobe全家桶完整功能?

Adobe-GenP终极指南:如何免费解锁Adobe全家桶完整功能? 【免费下载链接】Adobe-GenP Adobe CC 2019/2020/2021/2022/2023 GenP Universal Patch 3.0 项目地址: https://gitcode.com/gh_mirrors/ad/Adobe-GenP Adobe Creative Cloud系列软件以其强…...