Xilinx Zynq-7000系列FPGA多路视频处理:图像缩放+视频拼接显示,提供工程源码和技术支持

目录

- 1、前言

- 免责声明

- 2、相关方案推荐

- FPGA图像处理方案

- FPGA图像缩放方案

- FPGA视频拼接叠加融合方案推荐

- 3、设计思路详解

- HLS 图像缩放介绍

- Video Mixer介绍

- 4、vivado工程介绍

- PL 端 FPGA 逻辑设计

- PS 端 SDK 软件设计

- 5、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 6、上板调试验证并演示

- 准备工作

- 输出静态演示

- 输出动态演示

- 7、福利:工程源码获取

Xilinx Zynq-7000系列FPGA多路视频处理:图像缩放+视频拼接显示,提供工程源码和技术支持

1、前言

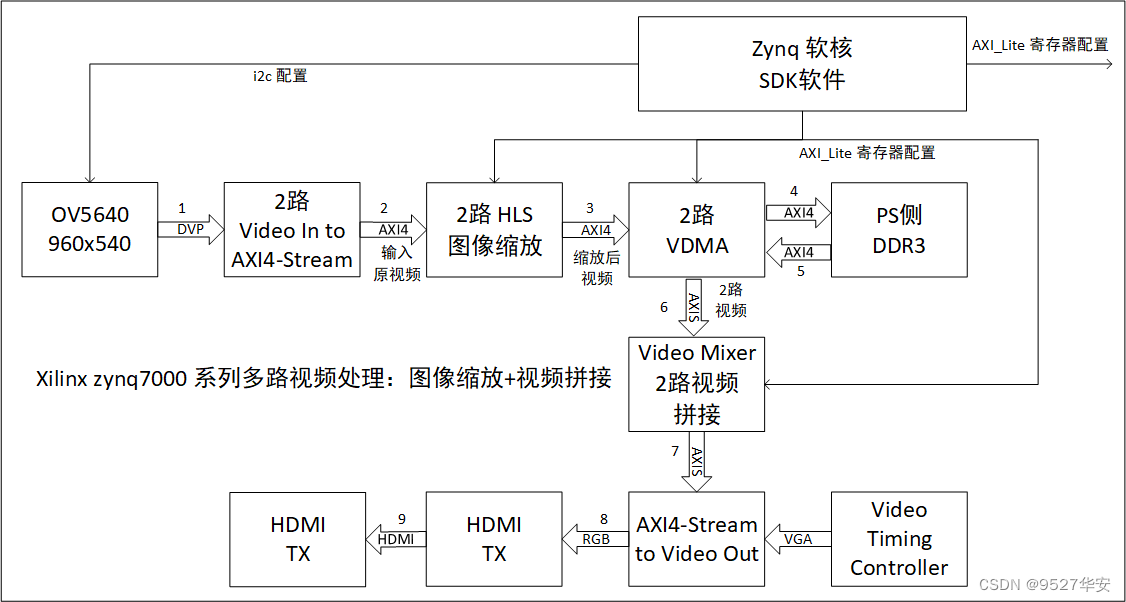

没玩过图像缩放和视频拼接都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。本文使用Xilinx Zynq7000系列FPGA Zynq7020实现HLS图像缩放+视频拼接,输入视频源采用OV5640摄像头模组;调用Zynq软核的片内i2c控制器将OV5640配置为1280x720@30Hz分辨率;然后调用两路自定义IP采集OV5640摄像头视频DVP转RGB888,这里的两路输入均来自同一个OV5640,即用一路来模拟两路输入;然后调用两路Xilinx官方的Video In to AXI4-Stream IP核将RGB视频流转换为AXI4-Stream视频流;添加两路自定义的HLS图像缩放IP核,将输入视频进行任意尺寸图像缩放操作,该操作通过Zynq软核SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;然后调用两路Xilinx官方的VDMA IP将视频做PS侧DDR3的视频缓存操作,调用Zynq将VDMA配置为两帧帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用两路Xilinx官方的Video Mixer IP将两路缓存的视频做视频拼接操作,调用Zynq配置两路视频的不同显示位置,其本质为通过AXI_Lite 做寄存器配置;然后调用两路Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP将AXI4-Stream视频流转换为RGB视频流;然后添加自定义的HDMI发送IP将RGB视频转换为TMDS的差分视频送显示器显示;

提供一套vivado2019.1版本的工程源码和技术支持,通过SDK的配置可做成三套不同的缩放拼接方案,详情如下:

方案1:输入ov5640,分辨率1280x720;输出分辨率960x1080,在输出屏幕左右两边拼接输出;

方案2:输入ov5640,分辨率1280x720;输出分辨率1920x540,在输出屏幕上下两边拼接输出;

方案3:输入ov5640,分辨率1280x720;输出分辨率960x540,在输出屏幕左上角和右下角两边拼接输出;

方案的详细输出演示请看后面的“上板调试验证并演示”章节,三种方案的切换或改变只需修改SDK软件代码,无需修改FPGA逻辑工程;

本博客详细描述了Xilinx Zynq-7000系列FPGA多路视频处理:图像缩放+视频拼接显示的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;整个工程调用Zynq软核做IP的配置,Zynq的配置在SDK里以C语言软件代码的形式运行,所以整个工程包括FPGA逻辑设计和SDK软件设计两部分,需要具备FPGA和嵌入式C语言的综合能力,不适合初学者或者小白;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

FPGA图像处理方案

我的主页目前有FPGA图像处理专栏,改专栏收录了我目前手里已有的FPGA图像处理方案,包括图像缩放、图像识别、图像拼接、图像融合、图像去雾、图像叠加、图像旋转、图像增强、图像字符叠加等等;以下是专栏地址:

点击直接前往

FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

FPGA视频拼接叠加融合方案推荐

我的主页目前有FPGA视频拼接叠加融合专栏,改专栏收录了我目前手里已有的FPGA视频拼接叠加融合方案,从实现方式分类有基于HSL实现的视频拼接、基于纯verilog代码实现的视频拼接;从应用上分为单路、2路、3路、4路、8路、16路视频拼接;视频缩放+拼接;视频融合叠加;从输入视频分类可分为OV5640摄像头视频拼接、SDI视频拼接、CameraLink视频拼接等等;以下是专栏地址:

点击直接前往

3、设计思路详解

没玩过图像缩放和视频拼接都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。本文使用Xilinx Zynq7000系列FPGA Zynq7020实现HLS图像缩放+视频拼接,输入视频源采用OV5640摄像头模组;调用Zynq软核的片内i2c控制器将OV5640配置为1280x720@30Hz分辨率;然后调用两路自定义IP采集OV5640摄像头视频DVP转RGB888,这里的两路输入均来自同一个OV5640,即用一路来模拟两路输入;然后调用两路Xilinx官方的Video In to AXI4-Stream IP核将RGB视频流转换为AXI4-Stream视频流;添加两路自定义的HLS图像缩放IP核,将输入视频进行任意尺寸图像缩放操作,该操作通过Zynq软核SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;然后调用两路Xilinx官方的VDMA IP将视频做PS侧DDR3的视频缓存操作,调用Zynq将VDMA配置为两帧帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用两路Xilinx官方的Video Mixer IP将两路缓存的视频做视频拼接操作,调用Zynq配置两路视频的不同显示位置,其本质为通过AXI_Lite 做寄存器配置;然后调用两路Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP将AXI4-Stream视频流转换为RGB视频流;然后添加自定义的HDMI发送IP将RGB视频转换为TMDS的差分视频送显示器显示;

提供一套vivado2019.1版本的工程源码和技术支持,通过SDK的配置可做成三套不同的缩放拼接方案,详情如下:

方案1:输入ov5640,分辨率1280x720;输出分辨率960x1080,在输出屏幕左右两边拼接输出;

方案2:输入ov5640,分辨率1280x720;输出分辨率1920x540,在输出屏幕上下两边拼接输出;

方案3:输入ov5640,分辨率1280x720;输出分辨率960x540,在输出屏幕左上角和右下角两边拼接输出;

方案的详细输出演示请看后面的“上板调试验证并演示”章节,三种方案的切换或改变只需修改SDK软件代码,无需修改FPGA逻辑工程;vivado工程源码设计框图如下:

HLS 图像缩放介绍

由于工程所用到的IP都是常用IP,所以这里重点介绍一下HLS图像缩放IP;

支持最大分辨率:1920x1080@60Hz;但可以修改HLS源码增大分辨率,前提是你的FPGA逻辑资源要够大;

输入视频格式:AXI4-Stream;

输出视频格式:AXI4-Stream;

需要SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;目前只适用于Xilinx Zynq7000系列FPGA使用,但可以修改HLS工程的器件类型来适应其他器件,比如Artix7、Kintex7等等;

提供自定义的配置API,通过调用该库函数即可轻松使用,具体参考SDK代码;

提供HLS工程源码,可任意修改,HLS版本为2019.1;

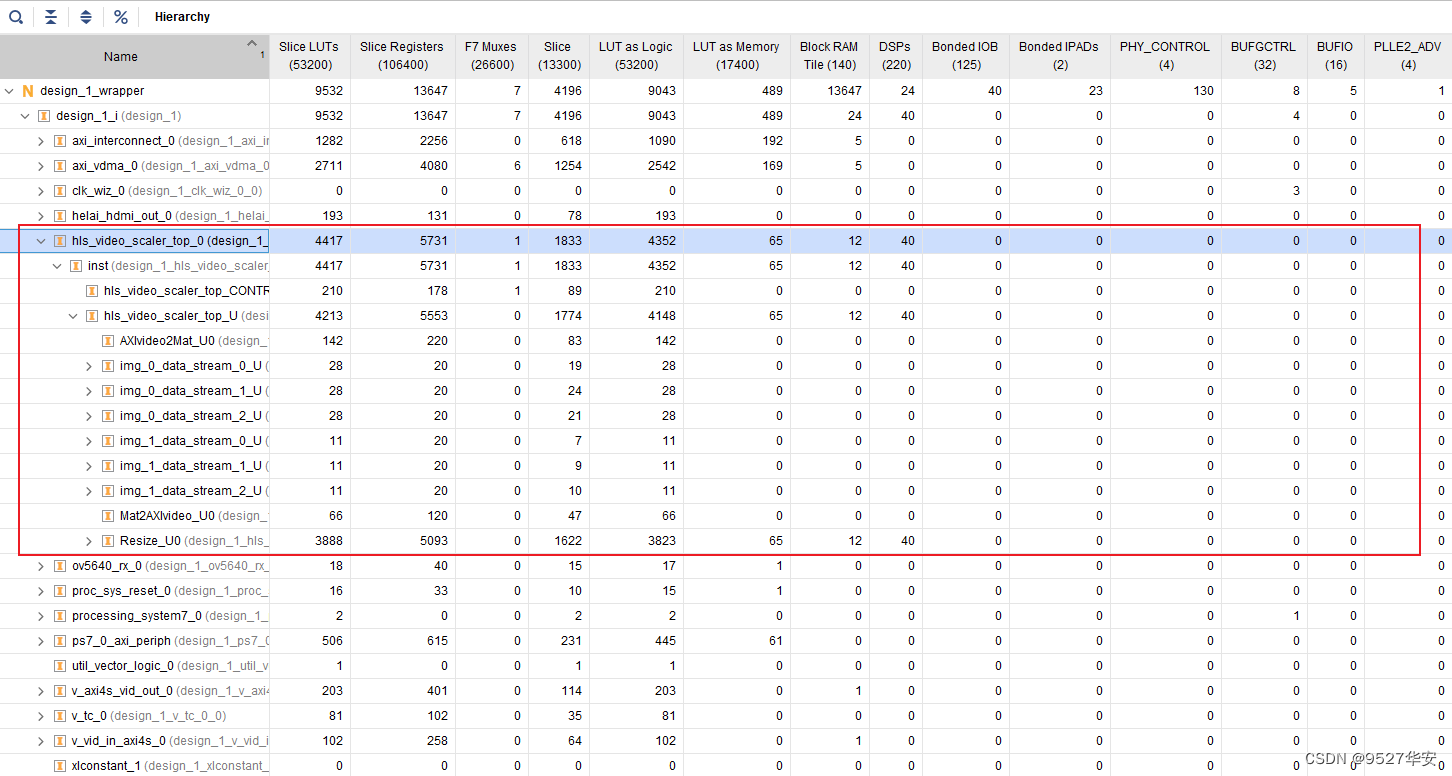

模块占用的FPGA逻辑资源如下:

请谨慎评估你的FPGA资源情况;

Video Mixer介绍

由于工程所用到的IP都是常用IP,所以这里重点介绍一下Video Mixer IP;

支持最大分辨率:8K,即可以处理高达8K的视频;

支持最多16层视频拼接叠加,即最多可拼接16路视频;

输入视频格式:AXI4-Stream;

输出视频格式:AXI4-Stream;

需要SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;

提供自定义的配置API,通过调用该库函数即可轻松使用,具体参考SDK代码;

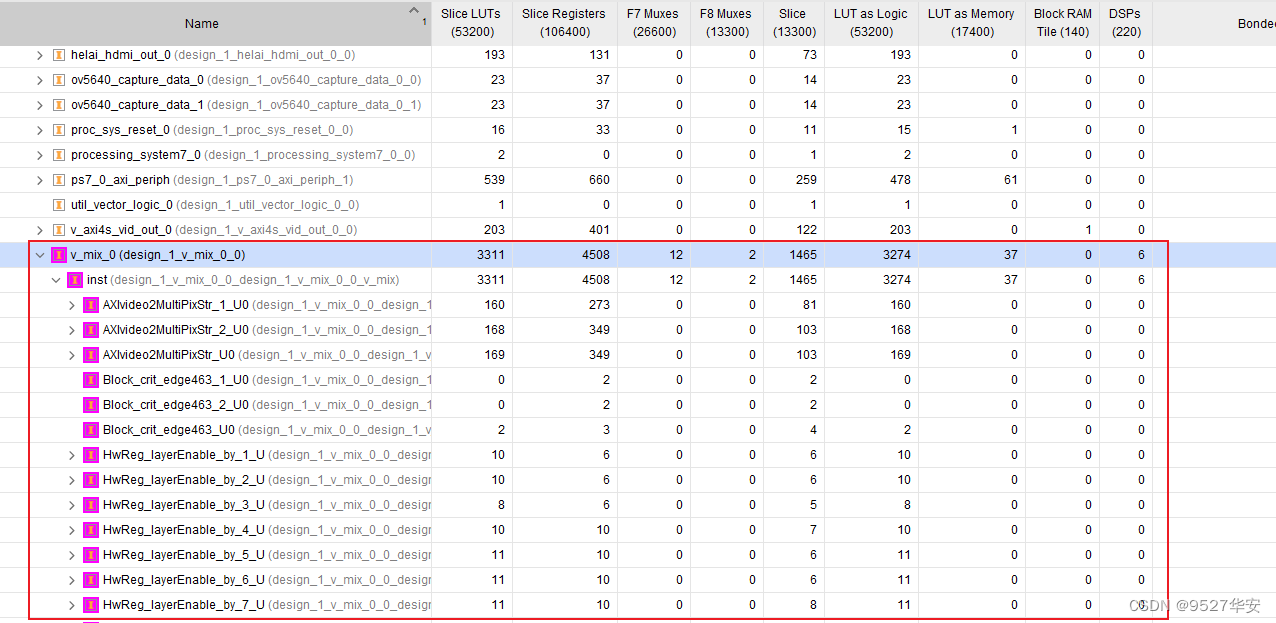

模块占用的FPGA逻辑资源更小,相比于自己写的HLS视频拼接而言,官方的Video Mixer资源占用大约减小30%左右,且更高效:

Video Mixer逻辑资源如下,请谨慎评估你的FPGA资源情况;

4、vivado工程介绍

PL 端 FPGA 逻辑设计

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率1280x720p;

输出:HDMI,1080P分辨率下的有效拼接视频区域显示;

工程作用:Xilinx Zynq-7000系列FPGA多路视频处理:图像缩放+视频拼接显示;

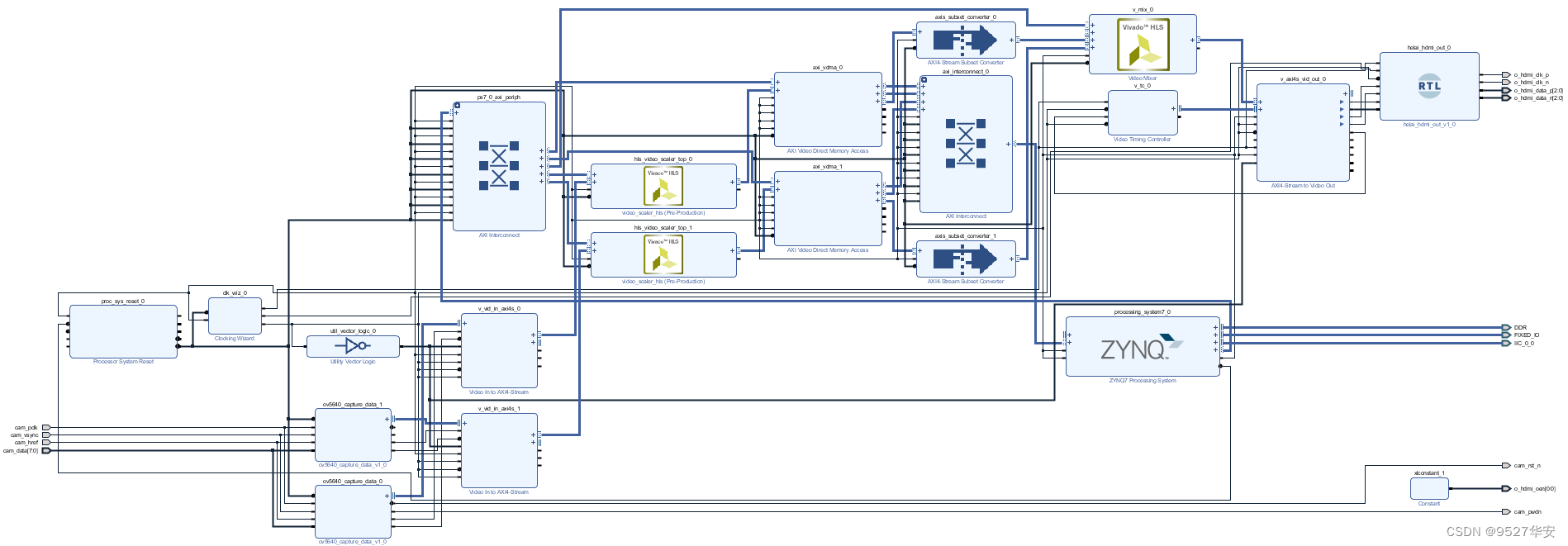

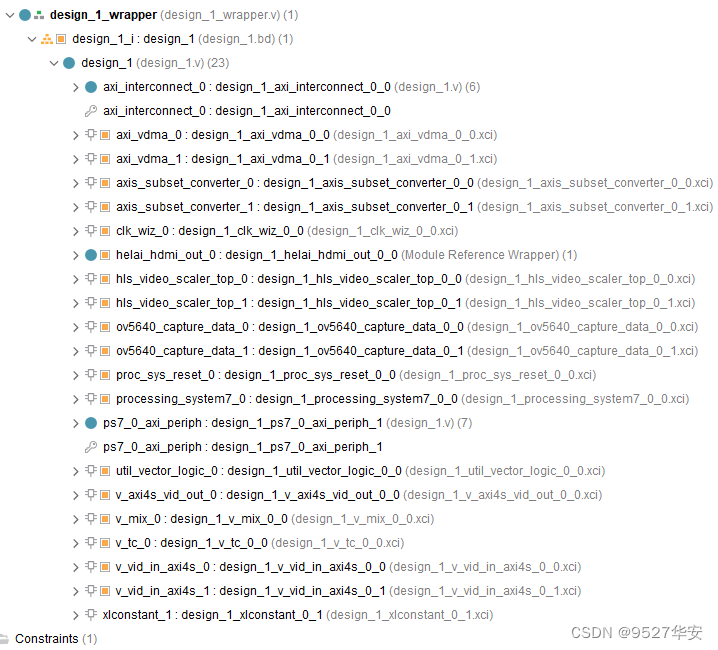

工程BD如下:

工程代码架构如下:

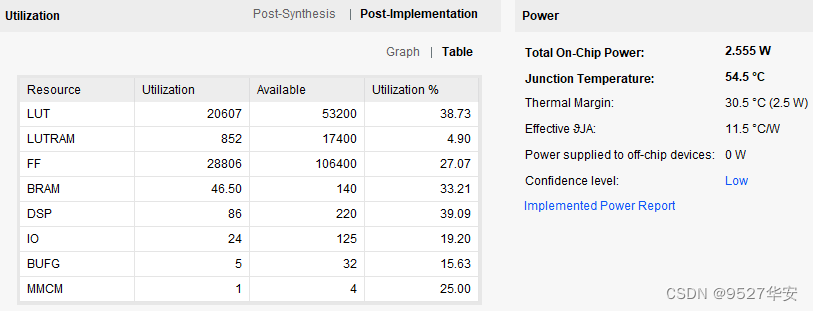

工程的资源消耗和功耗如下:

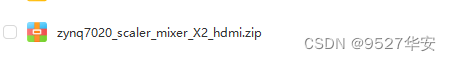

PS 端 SDK 软件设计

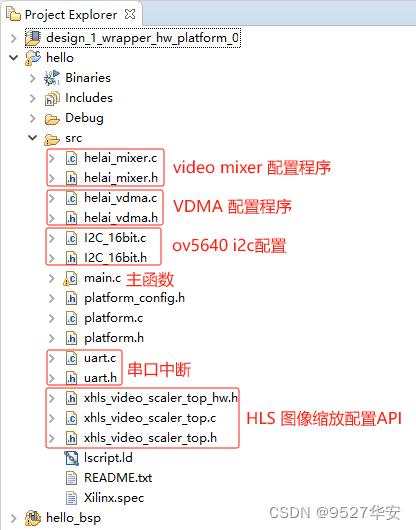

PS 端 SDK 软件工程代码架构如下:

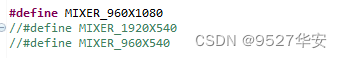

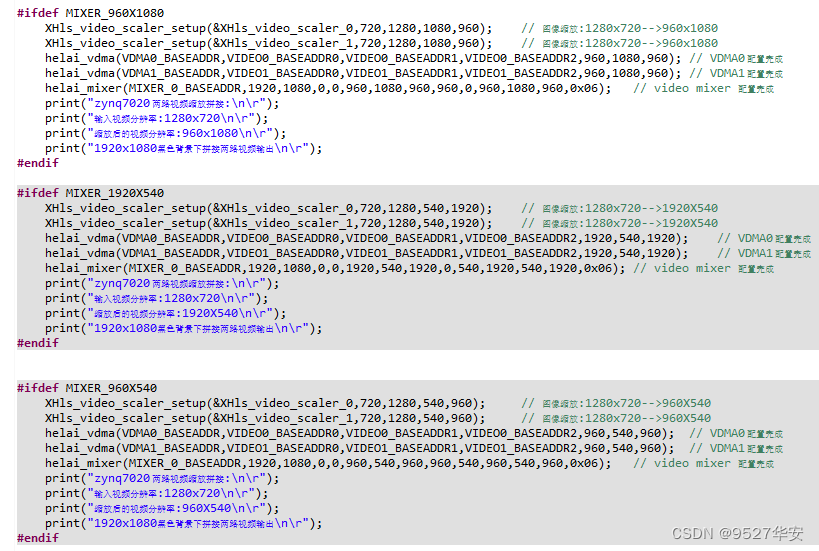

主函数通过如下的3个宏定义设计了3种不同的图像缩放拼接方案,代码如下:

3种不同的图像缩放拼接方案详情如下:

方案1:输入ov5640,分辨率1280x720;输出分辨率960x1080,在输出屏幕左右两边拼接输出;

方案2:输入ov5640,分辨率1280x720;输出分辨率1920x540,在输出屏幕上下两边拼接输出;

方案3:输入ov5640,分辨率1280x720;输出分辨率960x540,在输出屏幕左上角和右下角两边拼接输出;

根据前面的宏定义,主函数进行相应的图像缩放操作,并打印相关信息,代码如下:

5、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

6、上板调试验证并演示

准备工作

Zynq7000系列开发板;

OV5640摄像头;

HDMI显示器或者LCD显示屏,我用到的LCD显示屏为4.3寸分辨率800x480;

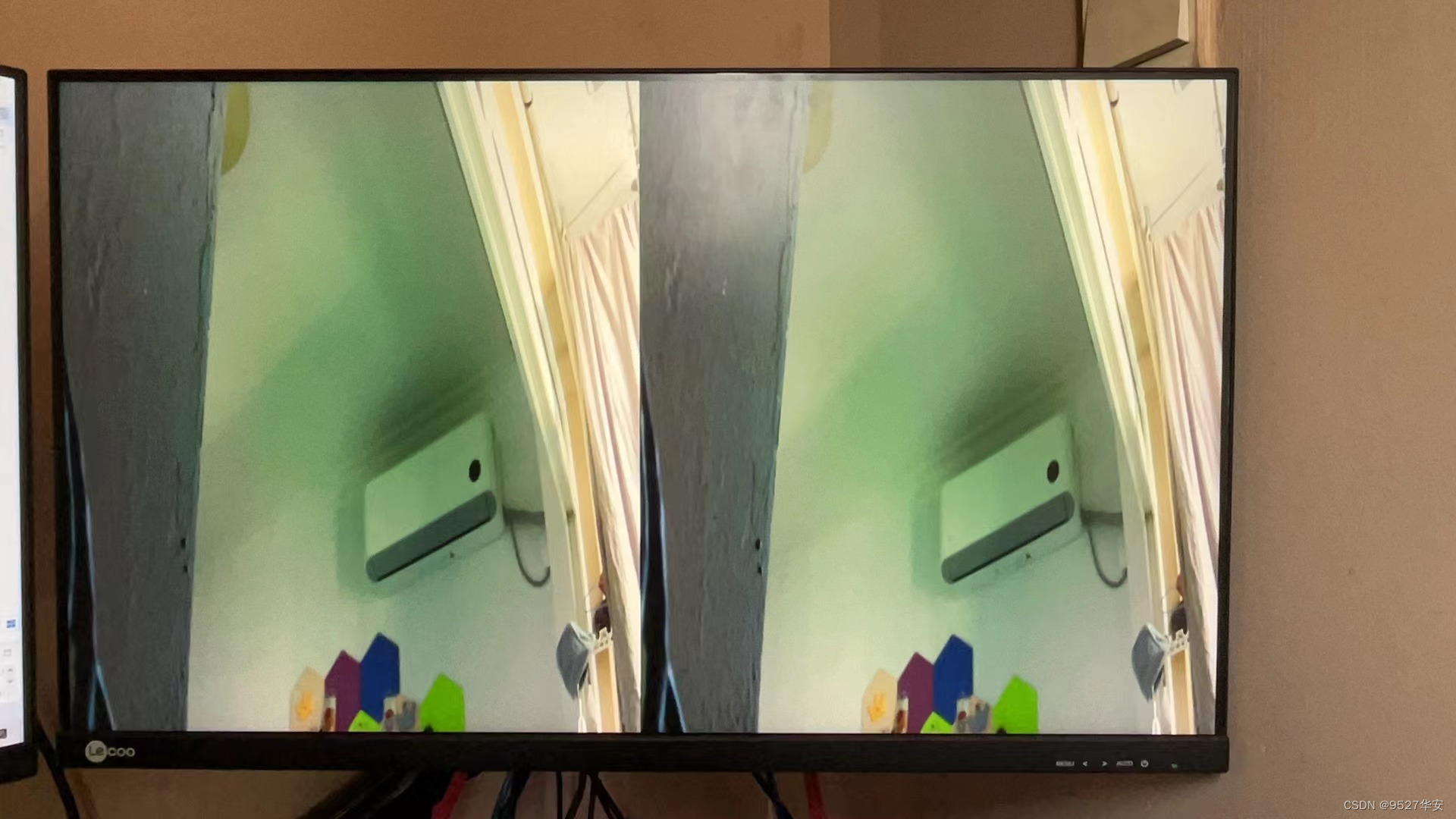

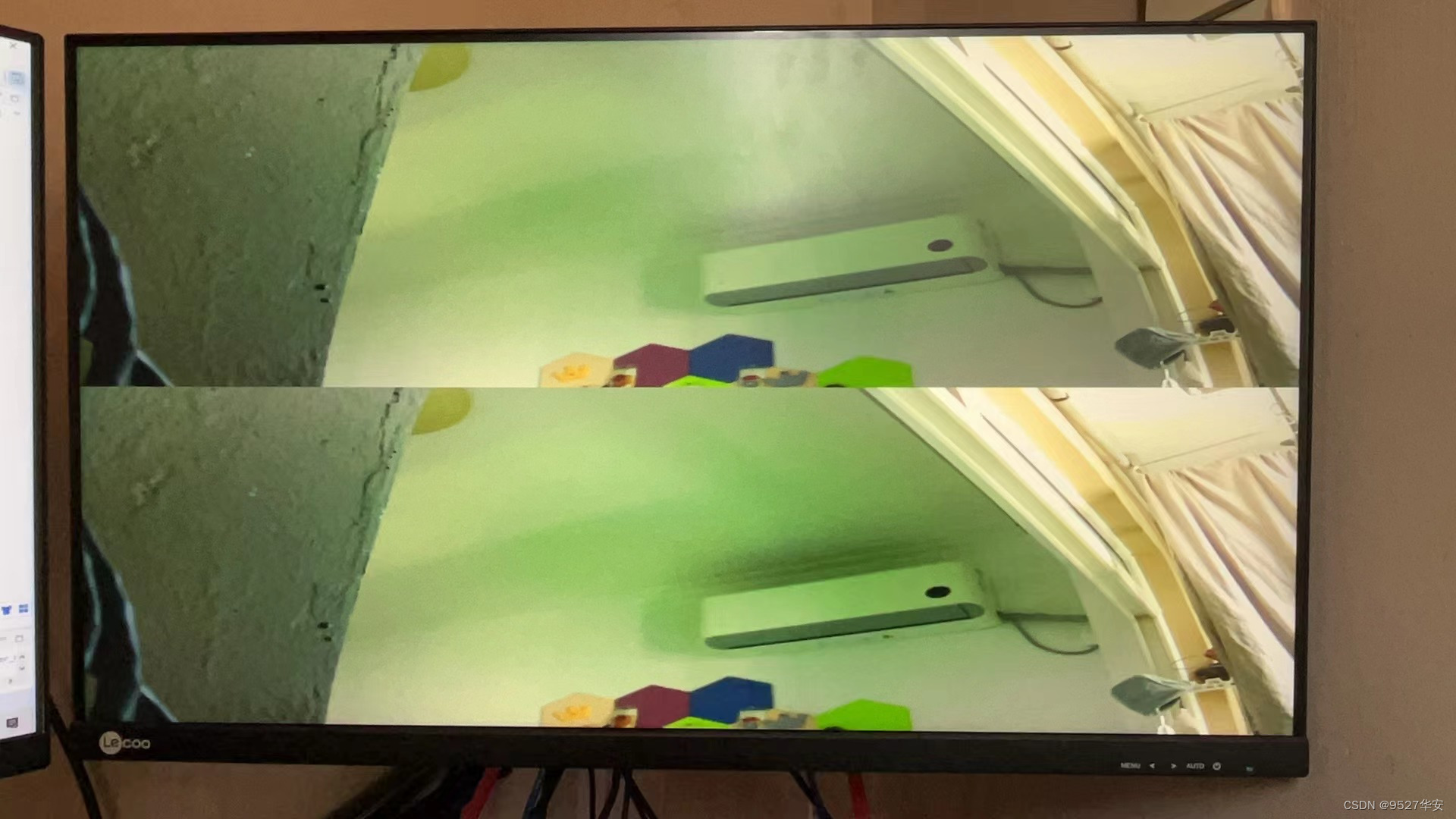

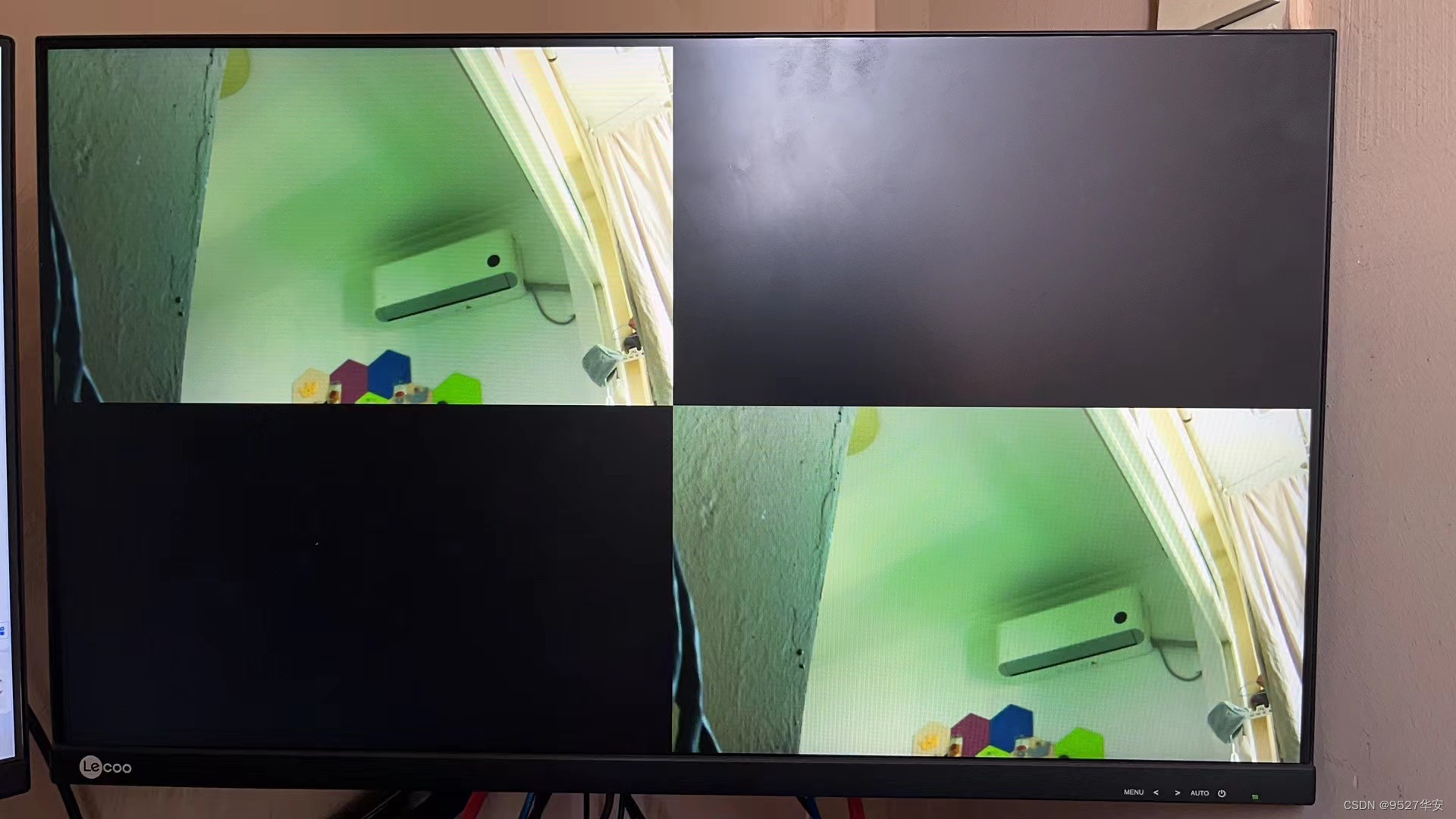

输出静态演示

ov5640输入分辨率1280x720,HDMI输出分辨率960x1080;

ov5640输入分辨率1280x720,HDMI输出分辨率1920x540;

ov5640输入分辨率1280x720,HDMI输出分辨率960x540;

输出动态演示

录制了一个小视频,输出动态演示如下:

缩放拼接

7、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

Xilinx Zynq-7000系列FPGA多路视频处理:图像缩放+视频拼接显示,提供工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA图像缩放方案FPGA视频拼接叠加融合方案推荐 3、设计思路详解HLS 图像缩放介绍Video Mixer介绍 4、vivado工程介绍PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程移植说明vivado版本不一致处理FPGA型号不一致处理其他…...

Web语言基础课程期末代做

《Web语言基础》课程期末考核要求综合运用课程所学知识,使用VS和SQL及相关开发工具,结合DIVCSS等前端设计技术,完成一个具备新闻发布和考试功能的动态系统,要求包括但不限于:用户注册、登录功能、新闻展示功能、后台数…...

Scanner常用知识点

在Java中,Scanner类是用于读取用户输入的工具类,可以从多种输入源读取数据,如标准输入流、文件或字符串。以下是一些Scanner类的常用知识点: Scanner的初始化:在使用Scanner类之前,需要先将其导入到你的Ja…...

uniapp页面使用多个echarts出现数据渲染错乱问题解决

首先,uniapp当中使用echarts是在通过使用renderjs的script模板的前提下实现的,在官方提供的案例当中,核心代码是这一部分: 但如果将其封装为组件,并在一个页面当中引用多次来生成多个charts图标,那么这个时…...

PHP连接数据库 错误抑制 三元运算符 学习资料

PHP连接数据库 PHP可以通过不同的扩展和库来连接各种类型的数据库。下面是一个使用MySQL数据库的连接示例: <?php $servername "localhost"; $username "your_username"; $password "your_password"; $dbname "your_d…...

5G智慧工地整体解决方案:文件全文115页,附下载

关键词:5G智慧工地,智慧工地建设方案,智慧工地管理平台系统,智慧工地建设调研报告,智慧工地云平台建设 一、5G智慧工地建设背景 5G智慧工地是利用5G技术、物联网、大数据、云计算、AI等信息技术,围绕“人…...

数据结构 / 内存的动态申请和释放

1.内存的动态申请 malloc malloc 的头文件: #include <stdlib.h>格式: void *malloc(size_t size);参数: size_t size: 申请堆区内存大小, 单位是字节;size_t: 是数据类型, 是 unsigned long的宏定义的别名;返回值: void *: 通用类型指针,使用时需要强转为具…...

Android手电筒、闪光灯、torch、flash

1. 仅开启手电筒 单纯的开启手电筒我们可以使用CameraManager的.setTorchMode()方法。 cameraCharacteristics.get(CameraCharacteristics.FLASH_INFO_AVAILABLE)获取该相机特征是否可获取闪光灯。 CameraManager cameraManager (CameraManager) getSystemService(CAMERA_SE…...

C语言--每日选择题--Day26

第一题 1.在C语言中,表示一次性地给数组a的10元素赋值() int a[10];scanf("%d",a); A:正确 B:错误 答案及解析 B 我们知道单独的数组名就是首元素地址,但是也有…...

[ACTF2020 新生赛]BackupFile

打开题目就一句话:尝试找到源文件 和上一题一样,用dirsearch扫描网站找到了一下内容 flag.php,0B,虚假flag 瞅一眼index.php.bak是啥 下载了一个文件,把bak后缀删掉,打开了index.php源码 is_numeric()&am…...

WPF面试题:WPF绘图技术介绍

作者:令狐掌门 技术交流QQ群:675120140 csdn博客:https://mingshiqiang.blog.csdn.net/ 文章目录 WPF绘图基本用法绘制直线在XAML中绘制直线在C#代码中绘制直线使用Path绘制直线注意矩形绘制在XAML中绘制矩形在C#代码中绘制矩形设置矩形的位置使用圆角矩形画刷1. SolidColor…...

三、Lua变量

文章目录 一、变量分类二、变量赋值三、索引 一、变量分类 lua变量分为全局变量,局部变量。 全局变量:默认,全局有效。 局部变量:从作用范围开始到作用范围结束,需加local 修饰。 a1function ff()local b1 endprint(a…...

C#每天复习一个重要小知识day4:枚举的概念/申明/使用

目录 1.枚举的概念: 2.申明枚举和申明枚举变量: 申明枚举语法: 申明枚举变量语法: 1.枚举的概念: 枚举是什么?枚举是一个比较特别的存在,它是一个命名的整形常量的集合,一般用它…...

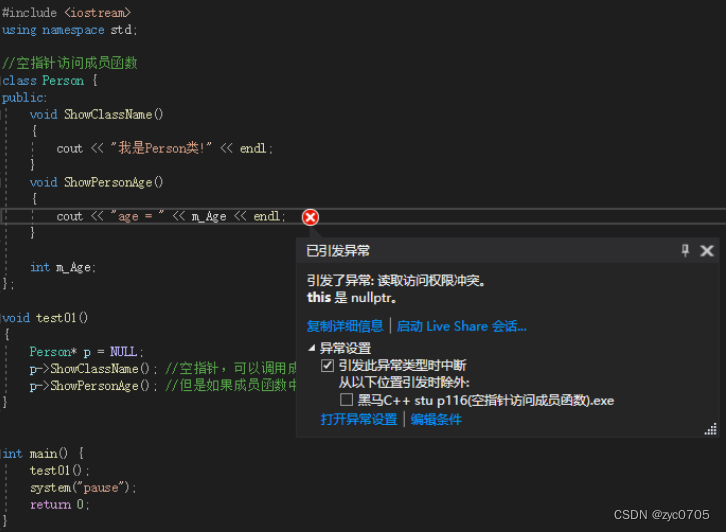

C++:对象模型和this指针

对象模型: 成员变量和成员函数分开存储 在C中,类内的成员变量和成员函数分开存储 只有非静态成员变量才属于类的对象上 空对象占用空间: 1字节 C编译器会给每个空对象也分配一个字节空间,是为了区分空对象占内存的位置 每个…...

碳酸氢锂/硫酸锂溶液纯化除钙镁解决方案

碳酸锂是锂电行业阳极生产中的一个重要原材料,主要用于制造钴酸锂、镍酸锂、锰酸锂等电极材料,也用于充电 锂电池中作非水溶液电解质等,具有良好的电化学性能,应用领域还在不断扩大。工业级碳酸锂主含量(Li2CO3&#x…...

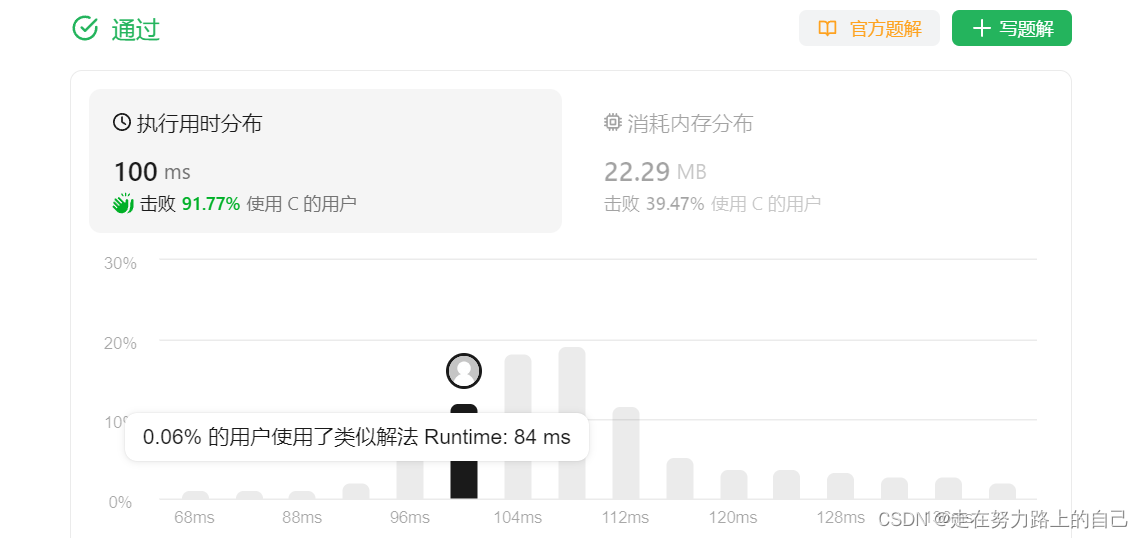

消失的数字,旋转数组(leetcode 一题多解)

目录 一、消失的数字 思路一(暴力求解)代码实现: 思路二(数列的思想)代码实现: 思路三(异或的运用)代码实现: 二、轮转数组 思路一(暴力求解)…...

肠道菌群16s检测粪便采样工具包 粪便采样套装

肠道菌群16s检测是一种常见的分子生物学技术,用于研究人体肠道中的微生物群落。该技术通过分析16s rRNA基因序列,可以快速、准确地鉴定并定量不同种类的肠道微生物。 肠道菌群16s检测通常通过采集粪便样本进行分析。在实验室中,通过提取微生物…...

实现领域驱动设计-07-领域服务

领域中的服务表示一个无状态的操作,它用于实现特定于某个领域的任务。当某个操作不适合放在聚合和值对象上时,为了避免过程式的编程方式,最好的方式便是使用领域服务来实现该操作。 什么是领域服务? 当领域中的某个操作过程或转换过程不是实…...

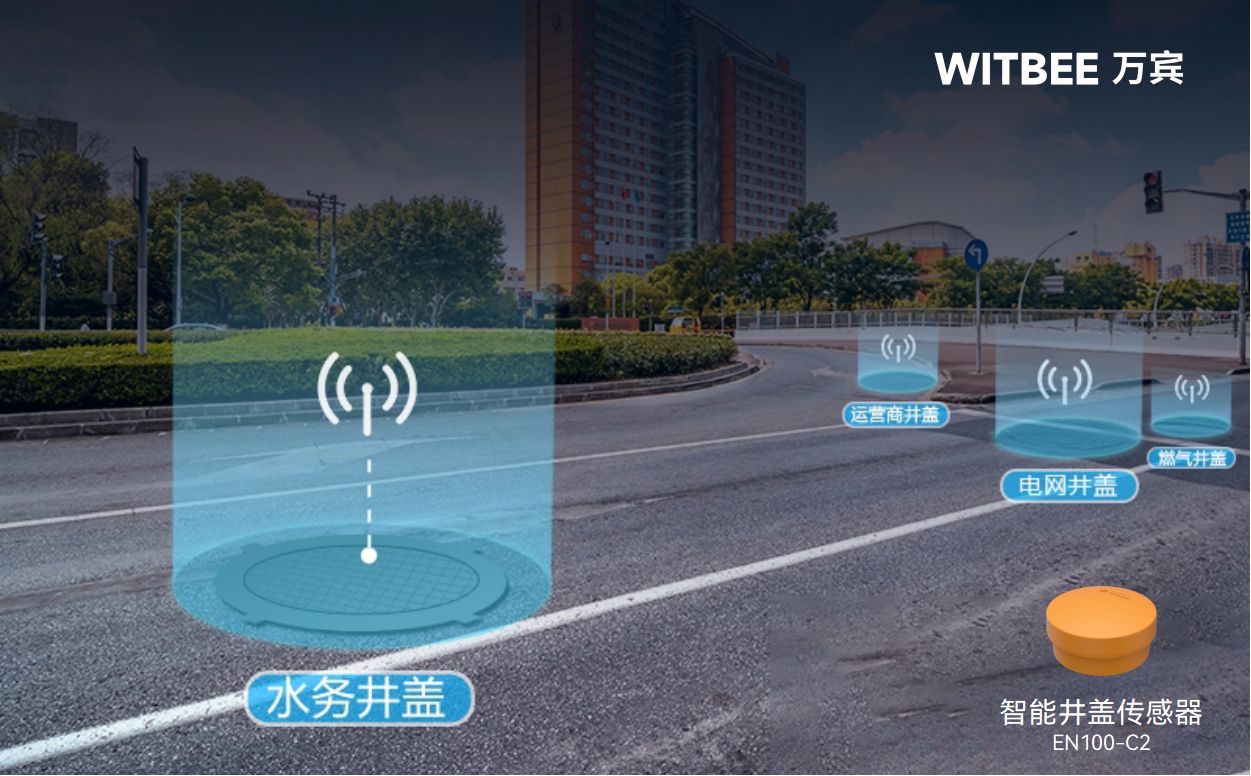

井盖位移传感器厂家批发,守护井盖安全

窨井盖广泛分布于城市街道,其管理效果直接反映了城市治理的现代化程度。根据住房和城乡建设部发布的《关于进一步加强城市窨井盖安全管理的通知》,全国各地需加强窨井盖的安全管理。作为市政基础设施的一个重要的组成部分,井盖的管理工作不仅…...

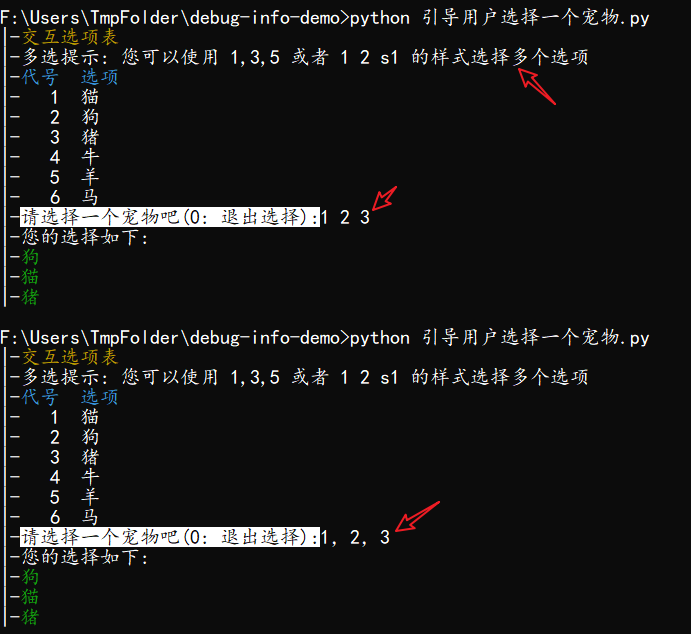

python命令行交互 引导用户选择宠物

字多不看,直接体验 代码 以下代码将在命令行中,引导用户选择一个或者多个宠物,并反馈用户选择的宠物 # -*- coding:UTF-8 -*- """ author: dyy contact: douyaoyuan126.com time: 2023/11/22 15:19 file: 在命令行中引导用户…...

从几何视角理解Givens旋转:为什么它能完美解决QR分解?

几何动画拆解Givens旋转:QR分解的视觉化通关指南 想象你手里握着一根倾斜的多节天线,如何通过最简单的旋转操作让它完全竖直?这个看似简单的物理问题,恰恰揭示了Givens旋转在矩阵分解中的核心思想——通过一系列精心设计的平面旋…...

降重 + 降 AIGC 双效通关!虎贲等考 AI:改写不伤逻辑,论文查重零压力

如今高校毕业论文、期刊投稿不仅查重复率,更严查AIGC 生成痕迹,一旦超标直接打回、延迟答辩、影响毕业,让无数学生陷入 “写得快、改不动、过不了” 的困境。普通降重工具只会同义词替换、语序颠倒,越改越不通顺;AI 痕…...

结构光三维重建中的标定技术全解析:从理论到实践

1. 结构光三维重建的核心:为什么标定如此重要? 第一次接触结构光三维扫描时,我盯着重建出的扭曲模型百思不得其解——明明采用了高精度工业相机,为什么物体边缘会出现明显的波浪形畸变?后来发现是投影仪标定误差导致的…...

如何在macOS上快速定制个性化光标:Mousecape完全指南

如何在macOS上快速定制个性化光标:Mousecape完全指南 【免费下载链接】Mousecape Cursor Manager for OSX 项目地址: https://gitcode.com/gh_mirrors/mo/Mousecape 厌倦了macOS默认的单调鼠标指针?想要让光标更有个性、更符合你的审美࿱…...

Noto字体终极指南:如何为900+语言提供完美字体支持

Noto字体终极指南:如何为900语言提供完美字体支持 【免费下载链接】noto-fonts Noto fonts, except for CJK and emoji 项目地址: https://gitcode.com/gh_mirrors/no/noto-fonts Noto字体是Google开发的终极免费字体解决方案,致力于消除数字世界…...

uniapp中SQLite表缺失问题的排查与解决——以“no such table”错误为例

1. 初识"no such table"错误:从报错信息说起 第一次在uniapp开发中遇到SQLite的"no such table"错误时,我盯着控制台输出的-1404错误代码足足愣了三分钟。控制台清晰地显示着: { "code": -1404, "message…...

如何用猫抓扩展轻松下载网页视频:从零开始的完整指南

如何用猫抓扩展轻松下载网页视频:从零开始的完整指南 【免费下载链接】cat-catch 猫抓 浏览器资源嗅探扩展 / cat-catch Browser Resource Sniffing Extension 项目地址: https://gitcode.com/GitHub_Trending/ca/cat-catch 还在为无法下载网页视频而烦恼吗&…...

【无标题】第1章 分布式认知雷达网络与多智能体协同

目录 1.1 异构网络化感知架构 1.1.1 分布式相参阵列与频谱共生 1.1.2 频谱共享的势博弈模型 1.2 去中心化部分可观测马尔可夫决策过程(Dec-POMDP) 1.2.1 数学形式化 1.2.2 值分解网络(VDN)的可加性验证 1.3 MultiAgentRadarSim 仿真框架 1.4 验证与批判性分析 1.4.…...

AI时代的算法思维:大经典排序学习竞

引言 在现代软件开发中,性能始终是衡量应用质量的重要指标之一。无论是企业级应用、云服务还是桌面程序,性能优化都能显著提升用户体验、降低基础设施成本并增强系统的可扩展性。对于使用 C# 开发的应用程序而言,性能优化涉及多个层面&#x…...

抓取不规则表面物体机械手的设计

目 录 第一章 绪论 1 1.1 课题研究的意义及背景 1 1.2 机械手研究概况 2 1.2.1国外研究现状 2 1.2.2国内研究现状 2 1.3 研究的内容 2 第二章 抓取物体机械手总体结构设计 4 2.1机械手设计思路 4 2.2总体方案的设计 5 2.2.1驱动方式的选择 5 2.2.2传动结构的分析 6 2.2.3传动方…...