FPGA高端项目:Xilinx Artix7系列FPGA 多路视频缩放拼接 工程解决方案 提供4套工程源码+技术支持

目录

- 1、前言

- 版本更新说明

- 给读者的一封信

- FPGA就业高端项目培训计划

- 免责声明

- 2、相关方案推荐

- 我这里已有的FPGA图像缩放方案

- 我已有的FPGA视频拼接叠加融合方案

- 本方案的Xilinx Kintex7系列FPGA上的ov5640版本

- 本方案的Xilinx Kintex7系列FPGA上的HDMI版本

- 3、设计思路框架

- 设计框图

- 视频源选择

- ov5640 i2c配置及采集

- silcon9011的i2c配置

- 动态彩条

- 图像缩放模块详解

- 图像缩放模块使用

- 多路视频拼接算法

- 图像缓存

- 视频输出

- 工程源码架构

- 4、工程代码1详解:ov5640版本-->掌握2路视频缩放+拼接

- 5、工程代码2详解:ov5640版本-->掌握4路视频缩放+拼接

- 6、工程代码3详解:HDMI版本-->掌握2路视频缩放+拼接

- 7、工程代码4详解:HDMI版本-->掌握4路视频缩放+拼接

- 8、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 9、上板调试验证并演示

- 准备工作

- 工程1:ov5640输入版本-->2路视频缩放拼接输出演示

- 工程2:ov5640输入版本-->4路视频缩放拼接输出演示

- 工程3:HDMI输入版本-->2路视频缩放拼接输出演示

- 工程4:HDMI输入版本-->4路视频缩放拼接输出演示

- 10、福利:工程源码获取

FPGA高端项目:Xilinx Artix7系列FPGA 多路视频缩放拼接 工程解决方案 提供4套工程源码+技术支持

1、前言

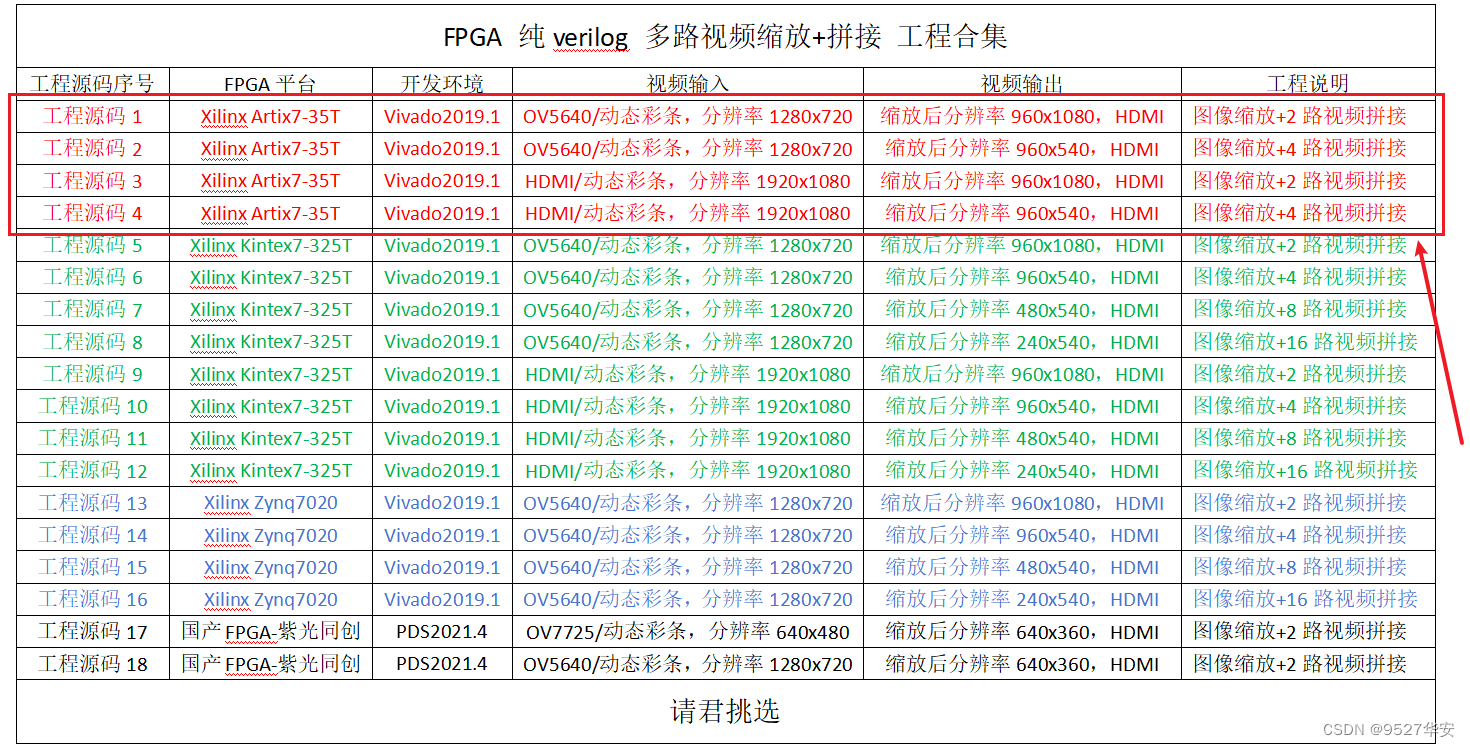

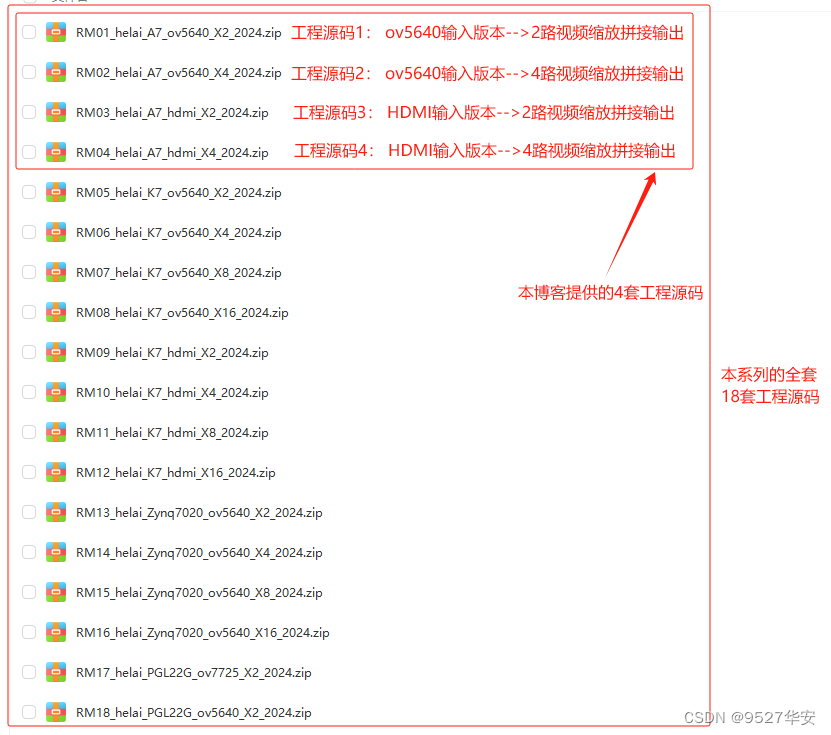

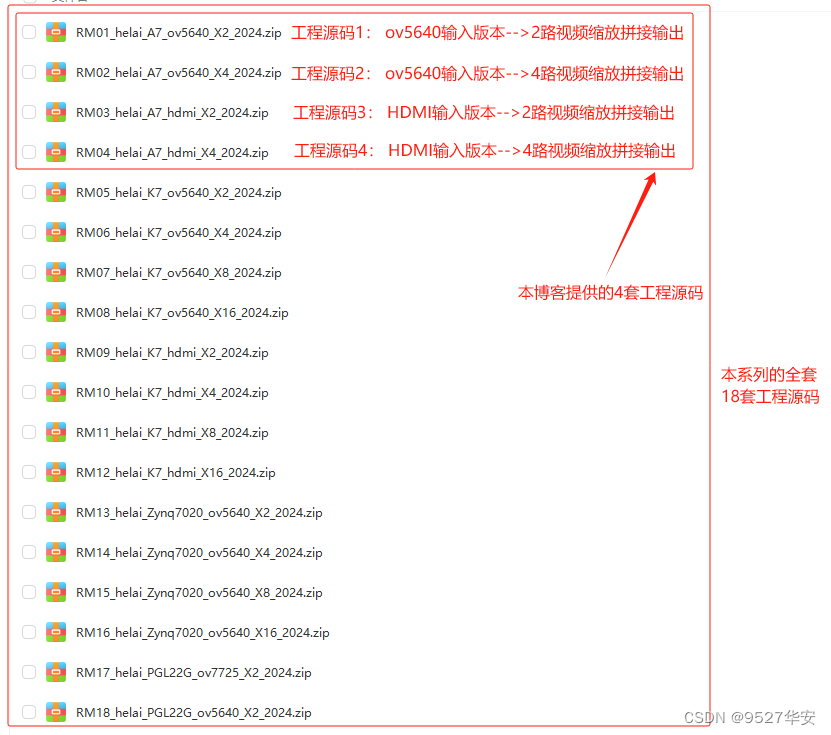

没玩过图像缩放和视频拼接都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。本文使用Xilinx的Artix7系列FPGA实现多路视频缩放拼接方案,视频源有两种,分别对应开发者手里有没有摄像头的情况,一种是使用廉价的OV5640摄像头模组或者板载的HDMI输入接口,HDMI解码采用silcon9011芯片解码方式,如果你的手里没有摄像头或者没有摄像头输入接口,亦或者你的开发板没有HDMI输入接口,或者HDMI解码不是silcon9011芯片解码方式,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行选择,默认使用ov5640或者HDMI作为视频源;FPGA采集到输入视频后,首先经过图像缩放模块对图像进行缩放操作,图像缩放模块支持领域插值和双线性插值2种算法,通过模块顶层参数选择,默认使用双线性插值;缩放后的图像进入我常用的FDMA图像缓存架构进行图像拼接和缓存;这里需要注意的是,我的手里没有多路摄像头,所以用采集到的视频复制N路,以模拟N路视频;视频拼接在调用FDMA的不同方案中得以实现,比如你需要进行4路视频拼接,则需要调用4路FDMA,并对其进行不同的配置,具体方案在后面会介绍;拼接缓存的图像写入DDR中,然后在VGA时序生成模块的控制下读出视频;最后送入板载的silcon9134芯片编码为HDMI视频后,发送视频至显示器即可;如果你的开发板HDMI输出接口不是芯片驱动,而是直连FPGA引脚,代码里也预留了纯verilog代码实现的HDMI输出模块来适应这种情况;针对目前市面上主流的FPGA,本纯verilog图像缩放拼接方案一共移植了18套工程源码,本博文介绍其中基于Xilinx Artix7系列FPGA ov5640版本的4套工程,详情如下:

这里说明一下提供的4套工程源码的作用和价值,如下:

工程源码1:ov5640输入版本–2路视频缩放+拼接

ov5640或者动态彩条输入,输入视频分辨率为1280x720,经过图像缩放模块后视频辨率为960x1080,缩放后的视频复制2份,用以模拟2路视频,调用2路FDMA图像缓存架构做视频拼接和图像缓存,最后HDMI输出,1920x1080的输出分辨率背景上叠加2路分辨率为960x1080的缩放拼接的视频,即2分屏输出显示;此工程目的是让读者掌握2路视频缩放+拼接的用法,以便能够移植和设计自己的项目;

工程源码2:ov5640输入版本–4路视频缩放+拼接

ov5640或者动态彩条输入,输入视频分辨率为1280x720,经过图像缩放模块后视频辨率为960x540,缩放后的视频复制4份,用以模拟4路视频,调用4路FDMA图像缓存架构做视频拼接和图像缓存,最后HDMI输出,1920x1080的输出分辨率背景上叠加4路分辨率为960x540的缩放拼接的视频,即4分屏输出显示;此工程目的是让读者掌握4路视频缩放+拼接的用法,以便能够移植和设计自己的项目;

工程源码3:HDMI输入版本–2路视频缩放+拼接

HDMI或者动态彩条输入,输入视频分辨率为1920x1080,经过图像缩放模块后视频辨率为960x1080,缩放后的视频复制2份,用以模拟2路视频,调用2路FDMA图像缓存架构做视频拼接和图像缓存,最后HDMI输出,1920x1080的输出分辨率背景上叠加2路分辨率为960x1080的缩放拼接的视频,即2分屏输出显示;此工程目的是让读者掌握2路视频缩放+拼接的用法,以便能够移植和设计自己的项目;

工程源码4:HDMI输入版本–4路视频缩放+拼接

HDMI或者动态彩条输入,输入视频分辨率为1920x1080,经过图像缩放模块后视频辨率为960x540,缩放后的视频复制4份,用以模拟4路视频,调用4路FDMA图像缓存架构做视频拼接和图像缓存,最后HDMI输出,1920x1080的输出分辨率背景上叠加4路分辨率为960x540的缩放拼接的视频,即4分屏输出显示;此工程目的是让读者掌握4路视频缩放+拼接的用法,以便能够移植和设计自己的项目;

本博客详细描述了Xilinx Artix7系列FPGA 多路视频缩放拼接工程解决方案的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

版本更新说明

此版本为第3版,根据读者的建议,对第1版工程做了改进和更新形成如下第2版本:

1:增加了输入视频动态彩条的选择,有的读者说他手里没有OV5640摄像头或者摄像头原理图和我的不一致,导致在移植过程中困难很大,基于此,增加了动态彩条,它由FPGA内部产生,不需要外接摄像头就可以使用,使用方法在后文有说明;

2:优化了FDMA,之前的FDMA内AXI4的数据读写突发长度为256,导致在低端FPGA上带宽不够,从而图像质量不佳,基于此,将FDMA内AXI4的数据读写突发长度改为128;

3:优化了HDMI输出模块,之前用的自定义IP,有读者说IP无法更新,虽能正常使用,但看源码不方便,基于此,将HDMI输出模块改为纯verilog实现的,直接了当;

4:更新了输出时序模块,我的输出时序模块采用1080P背景中显示有效区域图像的方式,之前的版本,除有效区域图像外,其他区域是花屏的,有读者说看着不舒服,基于此,将,除有效区域图像外的图像优化为黑色,即黑色背景中显示有效区域图像的方式,在后面有贴图;

根据读者的建议,对第2版工程做了改进和更新形成如下第3版本:

1:优化了图像缩放模块代码结构,将原来的跨时钟域FIFO纳入图像缩放模块内部,并添加了新的顶层接口和配置参数,使能原来复杂的顶层接口和参数变得十分简洁;

2:新增了纯verilog实现的异步FIFO,代码里可选Xilinx的FIFO IP核,也可选verilog实现的异步FIFO,通过顶层参数选择,这样就使得图像缩放模块移植性和通用性更强;

3:工程整体使用难度大大降低,由于优化了图像缩放模块和整体代码架构,加之将原来很多参数进行了统一的设置,代码量和行数减少了近45%,仅需修改集合参数就能快速实现工程的移植和修改;

给读者的一封信

FPGA作为当今热门行业,入行门槛很高,工资待遇不错,一时间引无数英雄尽折腰,但很多初学者甚至工程师都还有很多误区,现给读者一封信如下:

1、矮要承认挨打站稳

要学FPGA,甚至吃这碗饭,每个人都是从零基础开始的,你对自己有自信,认为你行,就自学;你不自信,就找别人学;和古代拜师学艺是一回事儿;首先思维要符合逻辑;

2、基础问题需要自己解决

最基础的知识,比如:verilog语法、vivado工具使用、模电数电基础常识、电脑使用、计算机基本结构。。。这些基础知识在网上都是免费的,既有文字资料也有视频资料;这些基础知识你一定要具备,因为这是你能获得的性价比最高的东西了,首先它免费;其次它简单,只需要你花时间,不需要花脑子;最后它重要,这是你干FPGA的基础;

3、有了源码等于零

你可能认为,我有了源码就能做项目了,我可以肯定的告诉你,该醒醒了;原子弹的详细原理和原料配方甚至生产工艺流程在网上都是公开的,为啥全世界就那联合国几大流氓能造出来的?同样的,源码给你,你看得懂吗?你知道怎么用吗?看不懂不会用的源码,跟废物有什么区别?你需要的是源码+工程,最完美的是源码+工程+技术支持;有了源码,就有了可开发的底层架构,有了工程就知道源码或者模块怎么使用,有了技术支持就可以根据源码修改开发自己的项目;

4、先学会爬在学会跑

对于初学者,没有资格研究代码,你首先需要做的是对工程进行复现;比如给你一个图像的工程,你首先在自己的开发板上复现这个工程的功能,然后再去阅读理解代码,然后对代码的功能部分做小幅修改,比如改一下接口,增加几个输出接口,比如加一个LED输出;小幅修改后再慢慢增加修改幅度,以符合自己的需求;

5、学FPGA要不求甚解

学FPGA要不求甚解,甚至不需要理解,这句话咋听着有点不符合逻辑呢?对于很多功能性模块而言,你不需要理解它怎么实现的,你只需要知道怎么使用它,比如一个图像缩放模块,这种东西都是很老的知识,以你目前的知识水平,该模块的代码你怎么看也看不懂的,但你只要知道怎么使用它就行了,知道怎么使用,就能做项目,就能在公司呆下去了,原因很简单,老板招你来是干活儿的,不是招你来学习的,那是学校的事儿;如果要等什么都懂了才干活儿,那公司早垮了,学FPGA就是在实践中学习,先上前线去干活,边干边学,在实践中遇到问题,并主动去查资料问大佬理解问题,才是成长最快的,而不是一味的咬文嚼字刨根问底;

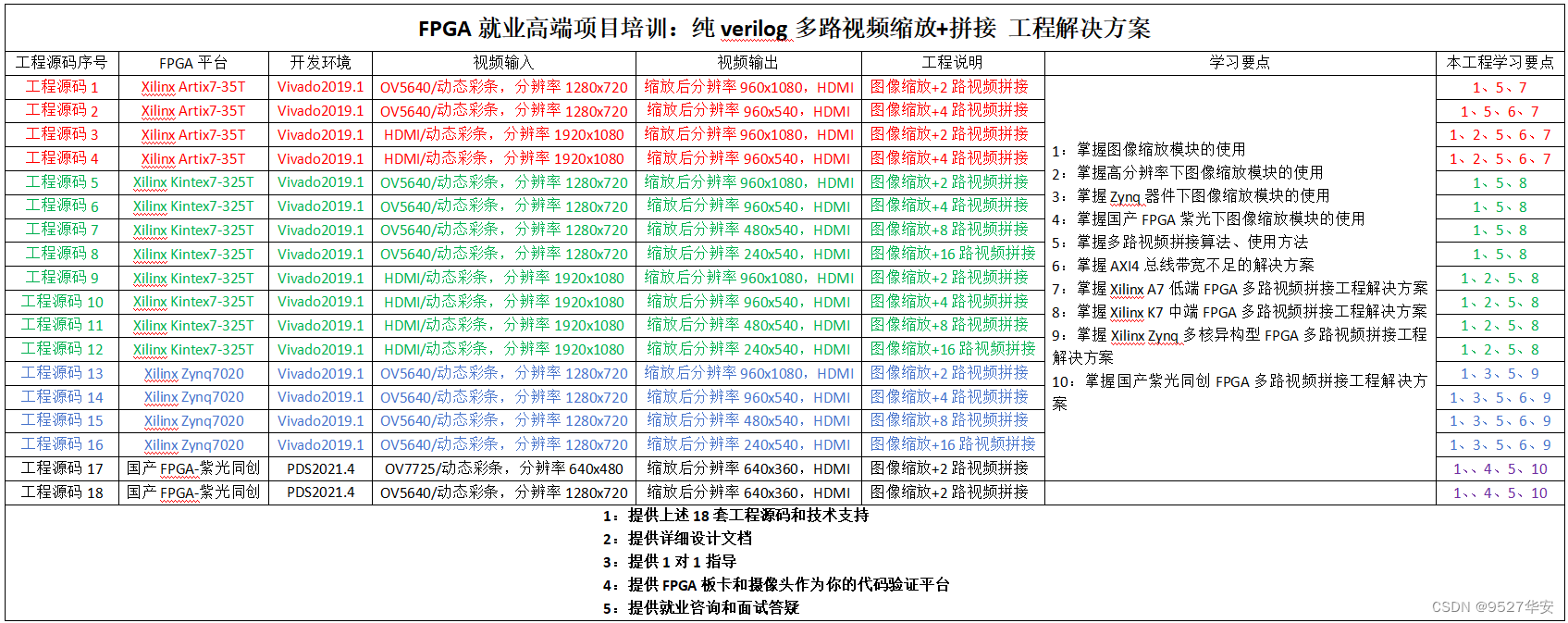

FPGA就业高端项目培训计划

鉴于目前的FPGA就业和行业现状,本博推出了FPGA就业高端项目培训:纯verilog多路视频缩放+拼接 工程解决方案的计划,该计划旨在让一部分人先学会FPGA纯verilog图像缩放,提高从业者的技术水平和工资待遇,详细计划如下:

FPGA就业高端项目培训计划细节:

1、我发你上述18套工程源码和对应的工程设计文档网盘链接,你保存下载,作为培训的核心资料;

2、你根据自己的实际情况安装好对应的开发环境,然后对着设计文档进行浅层次的学习;

3、遇到不懂的随时问我,包括代码、职业规划、就业咨询、人生规划、战略规划等等;

4、每周末进行一次腾讯会议,我会检查你的学习情况和面对面沟通交流;

5、你可以移植代码到你自己的FPGA开发板上跑,如果你没有板子,你根据你自己的需求修改代码后,编译工程,把bit发我,我帮你下载到我的板子上验证;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我这里已有的FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

我已有的FPGA视频拼接叠加融合方案

我的主页目前有FPGA视频拼接叠加融合专栏,改专栏收录了我目前手里已有的FPGA视频拼接叠加融合方案,从实现方式分类有基于HSL实现的视频拼接、基于纯verilog代码实现的视频拼接;从应用上分为单路、2路、3路、4路、8路、16路视频拼接;视频缩放+拼接;视频融合叠加;从输入视频分类可分为OV5640摄像头视频拼接、SDI视频拼接、CameraLink视频拼接等等;以下是专栏地址:

点击直接前往

本方案的Xilinx Kintex7系列FPGA上的ov5640版本

本方案适应于所有FPGA平台,针对目前市面上主流的FPGA,本博将本方案分别移植到了Xilinx 的Artix7、Kintex7、Zynq7020、紫光同创等平台共计18套工程源码,本文讲述的是在Xilinx Artix7系列FPGA上的应用,想要直接应用于Xilinx Kintex7系列FPGA上的ov5640视频缩放拼接应用的读者,可以参考我之前写得博客,以下是博客地址:

点击直接前往

本方案的Xilinx Kintex7系列FPGA上的HDMI版本

本方案适应于所有FPGA平台,针对目前市面上主流的FPGA,本博将本方案分别移植到了Xilinx 的Artix7、Kintex7、Zynq7020、紫光同创等平台共计18套工程源码,本文讲述的是在Xilinx Artix7系列FPGA上的应用,想要直接应用于Xilinx Kintex7系列FPGA上的HDMI视频缩放拼接应用的读者,可以参考我之前写得博客,以下是博客地址:

点击直接前往

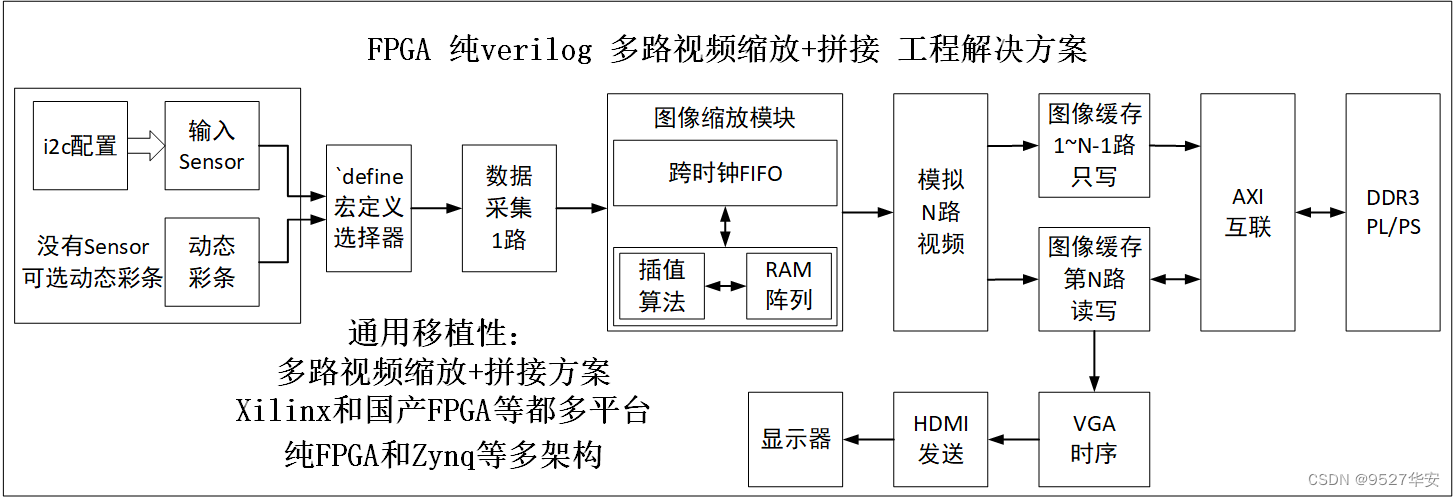

3、设计思路框架

设计框图

本博客提供4套vivado工程源码,设计框图如下:

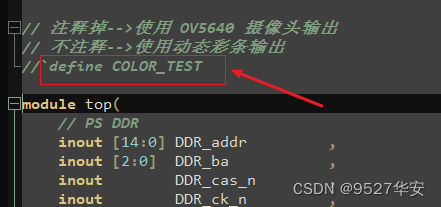

视频源选择

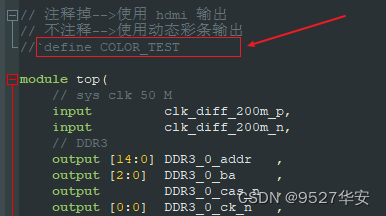

工程1和工程2的输入默认为OV5640摄像头模组,视频源有两种,分别对应开发者手里有没有摄像头的情况,一种是使用廉价的OV5640摄像头模组;如果你的手里没有摄像头,或者你的开发板没有摄像头接口,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行,默认使用ov5640作为视频源;视频源的选择通过代码顶层的`define宏定义进行;如下:

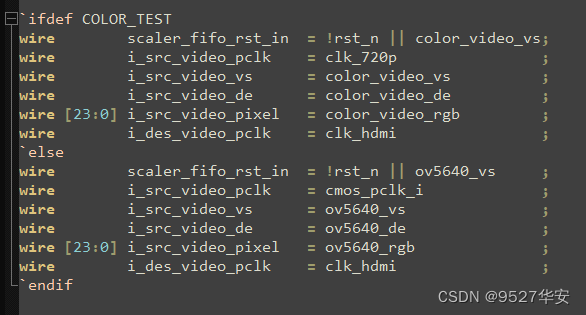

选择逻辑代码部分如下:

选择逻辑如下:

当(注释) define COLOR_TEST时,输入源视频是ov5640摄像头;

当(不注释) define COLOR_TEST时,输入源视频是动态彩条;

工程3和工程4的输入默认为HDMI,视频源有两种,分别对应开发者手里有没有摄像头的情况,板载的HDMI输入接口,HDMI解码采用silcon9011芯片解码方式,如果你的开发板没有HDMI输入接口,或者HDMI解码不是silcon9011芯片解码方式,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行,默认使用HDMI作为视频源;视频源的选择通过代码顶层的`define宏定义进行;如下:

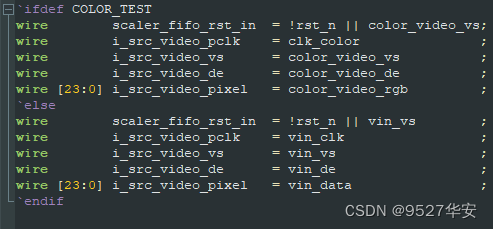

选择逻辑代码部分如下:

选择逻辑如下:

当(注释) define COLOR_TEST时,输入源视频是HDMI输入视频;

当(不注释) define COLOR_TEST时,输入源视频是动态彩条;

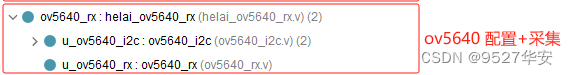

ov5640 i2c配置及采集

工程1和工程2的输入默认为OV5640摄像头模组,视频源有两种,分别对应开发者手里有没有摄像头的情况,一种是使用廉价的OV5640摄像头模组;如果你的手里没有摄像头,或者你的开发板没有摄像头接口,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行,默认使用ov5640作为视频源;ov5640需要i2c配置才能使用,需要i2c配置分辨率,然后将DVP接口的两个时钟一个像素的GRB565视频数据采集为一个时钟一个像素的RGB565或者RGB888视频数据;ov5640i2c配置及采集代码如下:

ov5640配置和采集模块顶层参数如下:

module helai_ov5640_rx #(parameter RGB_TYPE = 1'b0 , // 设为0-->输出RGB565;设为1-->输出RGB888parameter SENSOR_ADDR = 8'h78, // i2c 从机器件地址parameter DISPAY_H = 1280 , // ov5640输出视频宽度parameter DISPAY_V = 720 // ov5640输出视频高度

)(input clk , // 输入时钟input rst_n , // 低电平复位input [15:0] clk_div_cnt , // 分频参数 clk_div_cnt=clk/(5*i2c_scl)-1 inout cam_scl , //cmos i2c clock 即上面公式里的i2c_sclinout cam_sda , //cmos i2c datainput cam_vsync , //cmos vsyncinput cam_href , //cmos hsync refrence,data validinput cam_iclk , //cmos pxiel clock input cam_pclk , //cmos pxiel clockoutput cam_xclk , //cmos externl clock input [7:0] cam_data , //cmos dataoutput cam_rst_n , //cmos reset output cam_pwdn , //cmos power downoutput o_ov5640_hs , // 输出的RGB视频行同步信号 output o_ov5640_vs , // 输出的RGB视频场同步信号 output o_ov5640_de , // 输出的RGB视频像素数据有效信号 output [23:0] o_ov5640_data // 输出的RGB视频像素数据

);

ov5640配置和采集模块的例化请参考工程源码的顶层代码;

silcon9011的i2c配置

工程3和工程4的输入默认为HDMI,视频源有两种,分别对应开发者手里有没有摄像头的情况,板载的HDMI输入接口,HDMI解码采用silcon9011芯片解码方式,如果你的开发板没有HDMI输入接口,或者HDMI解码不是silcon9011芯片解码方式,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行,默认使用HDMI作为视频源;silcon9011需要i2c配置才能使用,配置代码如下:

更多关于更多silcon9011的信息,请参考我之前的博客,链接如下:

直接点击前往

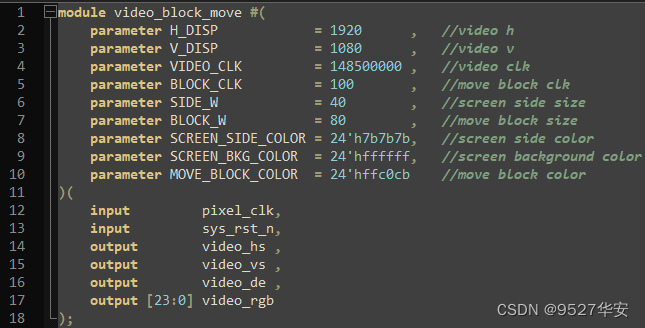

动态彩条

如果你的手里没有Sensor(ov5640或者HDMI),或者你得开发板没有Sensor(ov5640或者HDMI)接口,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行,动态彩条可配置为不同分辨率的视频,视频的边框宽度,动态移动方块的大小,移动速度等都可以参数化配置,动态彩条模块代码位置和顶层接口和例化如下:

动态彩条模块的例化请参考工程源码的顶层代码;

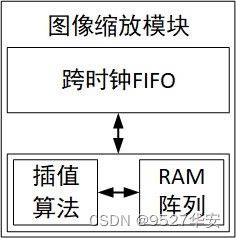

图像缩放模块详解

图像缩放模块功能框图如下,由跨时钟FIFO、插值+RAM阵列构成,跨时钟FIFO的目的是解决跨时钟域的问题,比如从低分辨率视频放大到高分辨率视频时,像素时钟必然需要变大,这是就需要异步FIFO了,插值算法和RAM阵列具体负责图像缩放算法层面的实现;

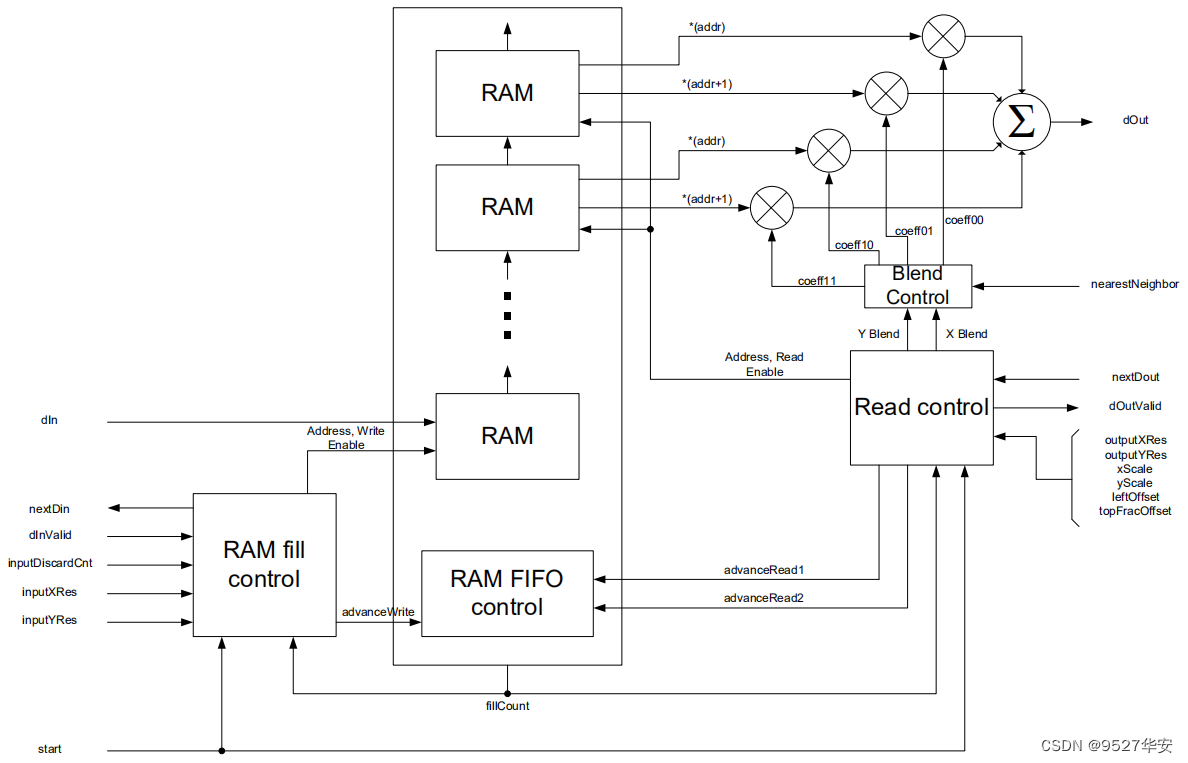

插值算法和RAM阵列以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

图像缩放模块代码架构如下:模块的例化请参考工程源码的顶层代码;

图像缩放模块FIFO的选择可以调用工程对应的vivado工具自带的FIFO IP核,也可以使用纯verilog实现的FIFO,可通过接口参数选择,图像缩放模块顶层接口如下:

module helai_video_scale #(//---------------------------Parameters----------------------------------------parameter FIFO_TYPE = "xilinx", // "xilinx" for xilinx-fifo ; "verilog" for verilog-fifoparameter DATA_WIDTH = 8 , //Width of input/output dataparameter CHANNELS = 1 , //Number of channels of DATA_WIDTH, for color imagesparameter INPUT_X_RES_WIDTH = 11 //Widths of input/output resolution control signals

)(input i_reset_n , // 输入--低电平复位信号input [INPUT_X_RES_WIDTH-1:0] i_src_video_width , // 输入视频--即缩放前视频的宽度input [INPUT_X_RES_WIDTH-1:0] i_src_video_height, // 输入视频--即缩放前视频的高度input [INPUT_X_RES_WIDTH-1:0] i_des_video_width , // 输出视频--即缩后前视频的宽度input [INPUT_X_RES_WIDTH-1:0] i_des_video_height, // 输出视频--即缩后前视频的高度input i_src_video_pclk , // 输入视频--即缩前视频的像素时钟input i_src_video_vs , // 输入视频--即缩前视频的场同步信号,必须为高电平有效input i_src_video_de , // 输入视频--即缩前视频的数据有效信号,必须为高电平有效input [DATA_WIDTH*CHANNELS-1:0] i_src_video_pixel , // 输入视频--即缩前视频的像素数据input i_des_video_pclk , // 输出视频--即缩后视频的像素时钟,一般为写入DDR缓存的时钟output o_des_video_vs , // 输出视频--即缩后视频的场同步信号,高电平有效output o_des_video_de , // 输出视频--即缩后视频的数据有效信号,高电平有效output [DATA_WIDTH*CHANNELS-1:0] o_des_video_pixel // 输出视频--即缩后视频的像素数据

);

FIFO_TYPE选择原则如下:

1:总体原则,选择"xilinx"好处大于选择"verilog";

2:当你的FPGA逻辑资源不足时,请选"xilinx";

3:当你图像缩放的视频分辨率较大时,请选"xilinx";

4:当你的FPGA没有FIFO IP或者FIFO IP快用完了,请选"verilog";

5:当你向自学一下异步FIFO时,,请选"verilog";

6:不同FPGA型号对应的工程FIFO_TYPE参数不一样,但选择原则一样,具体参考代码;

2种插值算法的整合与选择

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

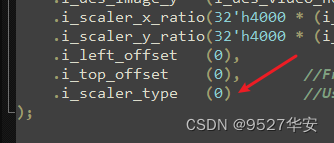

代码里的配置如下:

图像缩放模块使用

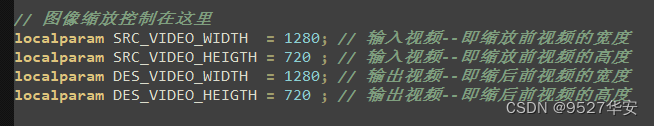

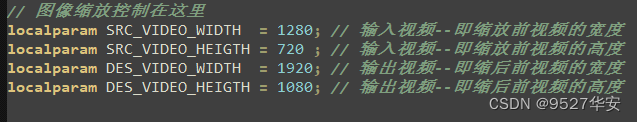

图像缩放模块使用非常简单,顶层代码里设置了四个参数,如下:

上图视频通过图像缩放模块但不进行缩放操作,旨在掌握图像缩放模块的用法;如果需要将图像放大到1080P,则修改为如下:

当然,需要修改的不仅仅这一个地方,FDMA的配置也需要相应修改,详情请参考代码,但我想要证明的是,图像缩放模块使用非常简单,你都不需要知道它内部具体怎么实现的,上手就能用;

多路视频拼接算法

纯verilog多路视频拼接方案如下:以4路OV5640摄像头拼接为例;

输出屏幕分辨率为1920X1080;

输入摄像头分辨率为960X540;

4路输入刚好可以占满整个屏幕;

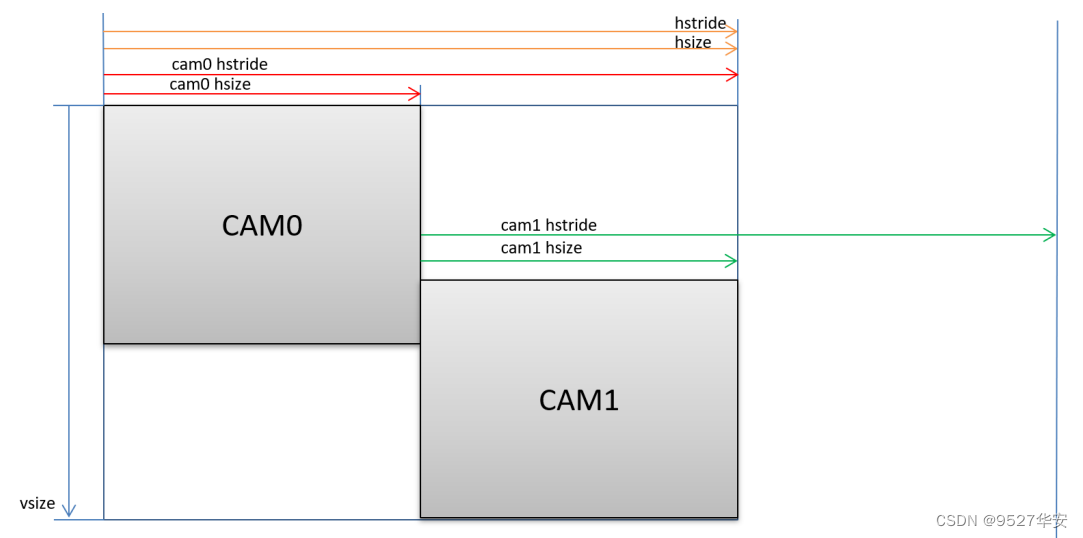

多路视频的拼接显示原理如下:

以把 2 个摄像头 CAM0 和 CAM1 输出到同一个显示器上为列,为了把 2 个图像显示到 1 个显示器,首先得搞清楚以下关系:

hsize:每 1 行图像实际在内存中占用的有效空间,以 32bit 表示一个像素的时候占用内存大小为 hsize X 4;

hstride:用于设置每行图像第一个像素的地址,以 32bit 表示一个像素的时候 v_cnt X hstride X 4;

vsize:有效的行;

因此很容易得出 cam0 的每行第一个像素的地址也是 v_cnt X hstride X 4;

同理如果我们需要把 cam1 在 hsize 和 vsize 空间的任何位置显示,我们只要关心 cam1 每一行图像第一个像素的地址,可以用以下公式 v_cnt X hstride X 4 + offset;

uifdma_dbuf 支持 stride 参数设置,stride 参数可以设置输入数据 X(hsize)方向每一行数据的第一个像素到下一个起始像素的间隔地址,利用 stride 参数可以非常方便地摆放输入视频到内存中的排列方式。

关于uifdma_dbuf,可以参考我之前写的文章点击查看:FDMA实现视频数据三帧缓存

根据以上铺垫,每路摄像头缓存的基地址如下:

CAM0:ADDR_BASE=0x80000000;

CAM1:ADDR_BASE=0x80000000+(1920-960)X4;

CAM2:ADDR_BASE=0x80000000+(1080-540)X1920X4;

CAM3:ADDR_BASE=0x80000000+(1080-540)X1920X4+(1920-960)X4;

地址设置完毕后基本就完事儿了;

注意!

注意!

注意!

在Zynq的地址分配中,FDMA的基地址不是上述的0x80000000,而是0x01000000;因为0x00000000是Zynq内核启动及其片内外设的基地址,所以不能以0x00000000作为PL端设备的基地址,由于Zynq地址分配从0x00000000开始,所以也不可能将FDMA基地址人为设置为0x80000000了;

图像缓存

经常看我博客的老粉应该都知道,我做图像缓存的套路是FDMA,他的作用是将图像送入DDR中做3帧缓存再读出显示,目的是匹配输入输出的时钟差和提高输出视频质量,关于FDMA,请参考我之前的博客,博客地址:点击直接前往

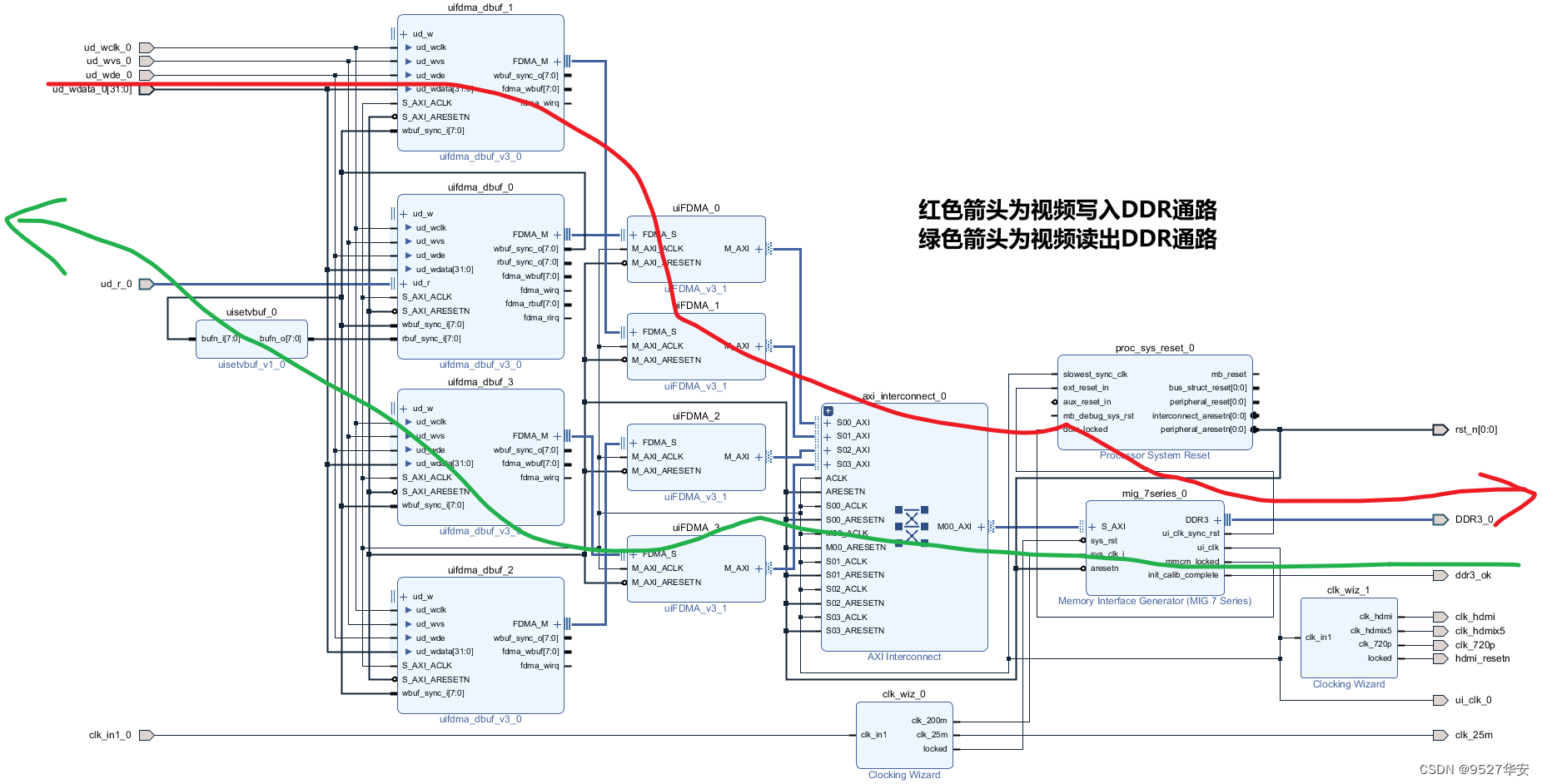

FDMA图像缓存架构如下图所示:截图为4路视频拼接,其他多路视频拼接与之类似;

需要注意的是,Xilinx系列的Artix7、Kintex7以及紫光和高云工程都使用DDR3作为缓存,Zynq7020工程使用PS端的DDR3作为缓存;Artix7、Kintex7工程调用MIG IP实现DDR3读写;Zynq7020工程调用Zynq软核实现DDR3读写;没有用到VDMA之类的IP,所以不需要SDK配置;

这里多路视频拼接时,调用多路FDMA进行缓存,具体讲就是每一路视频调用1路FDMA,以4路视频拼接为例:

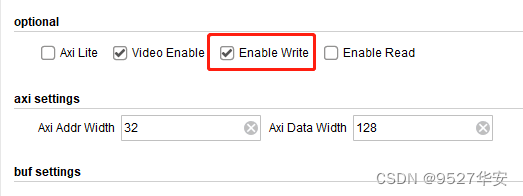

调用4路FDMA,其中三路配置为写模式,因为这三路视频在这里只需要写入DDR3,读出是由另一个FDMA完成,配置如下:

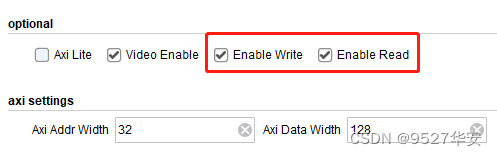

另外1路FDMA配置为读写模式,因为4路视频需要同时一并读出,配置如下:

视频拼接的关键点在于4路视频在DDR3中缓存地址的不同,还是以4路视频拼接为例,4路FDMA的写地址以此为:

第一路视频缓存写基地址:0x80000000;

第二路视频缓存写基地址:0x80000f00;

第三路视频缓存写基地址:0x803f4800;

第四路视频缓存写基地址:0x803f5700;

视频缓存读基地址:0x80000000;

视频输出

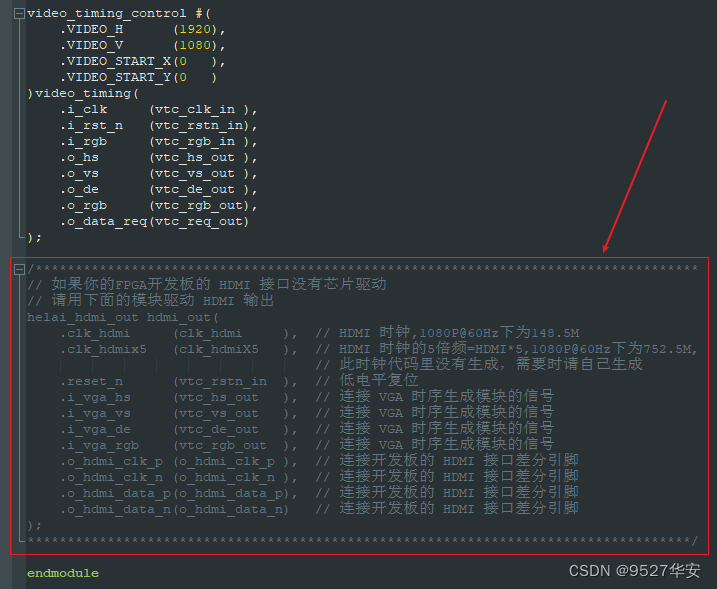

拼接缓存的图像写入DDR中,然后在VGA时序生成模块的控制下读出视频;最后送入板载的silcon9134芯片编码为HDMI视频后,发送视频至显示器即可;如果你的开发板HDMI输出接口不是芯片驱动,而是直连FPGA引脚,代码里也预留了纯verilog代码实现的HDMI输出模块来适应这种情况;silcon9134需要i2c配置才能使用,配置代码如下:

更多关于更多silcon9011的信息,请参考我之前的博客,链接如下:

直接点击前往

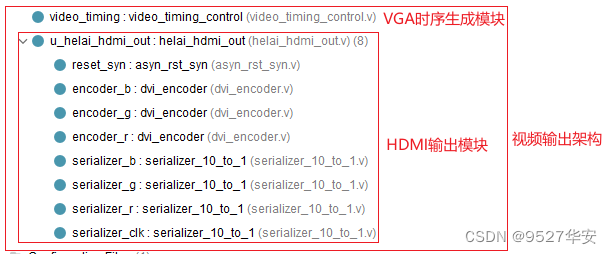

如果你的开发板HDMI输出接口不是芯片驱动,而是直连FPGA引脚,代码里也预留了纯verilog代码实现的HDMI输出模块来适应这种情况;如下:

纯verilog代码实现的HDMI输出模块代码如下:

关于纯verilog代码实现的HDMI输出模块,请参考我之前的博客,博客地址:点击直接前往

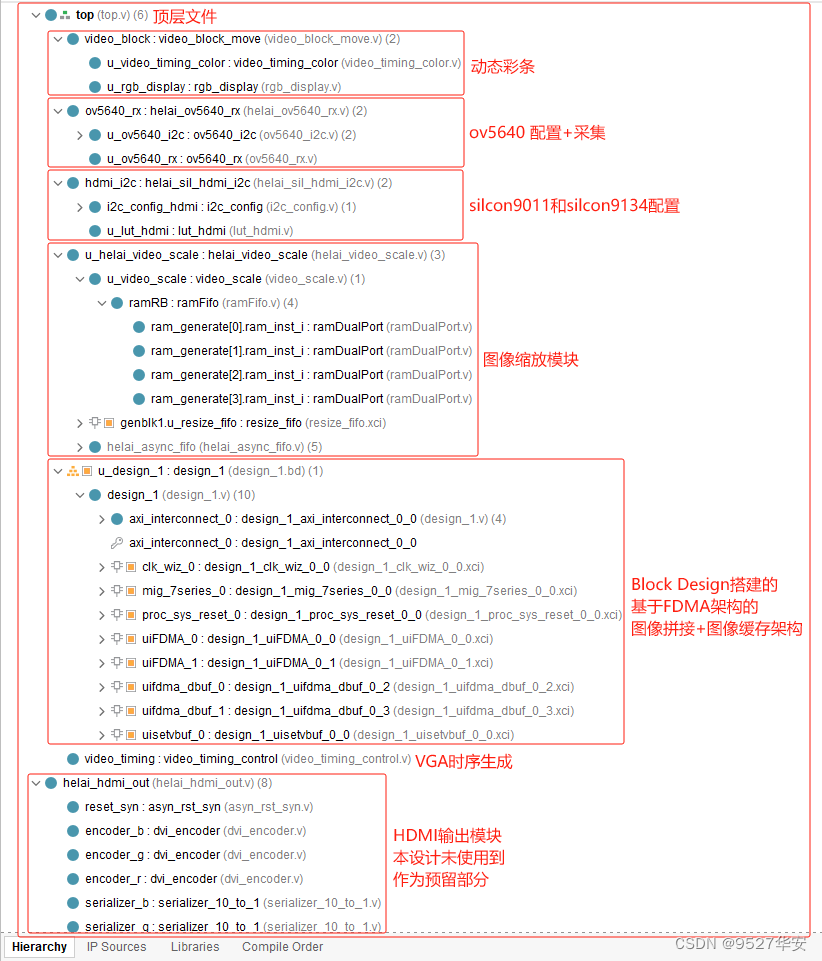

工程源码架构

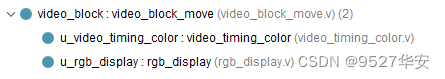

Xilinx Artix7系列FPGA工程源码架构具有高度相似性,以工程1为例截图如下:

4、工程代码1详解:ov5640版本–>掌握2路视频缩放+拼接

开发板FPGA型号:Xilinx–Artix7–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头或动态彩条,分辨率1280x720;

输出:1920x1080的输出分辨率背景上叠加2路分辨率为960x1080的缩放拼接的视频,即2分屏输出显示;

视频缩放方案:输入1280x720–>输出960x1080;

视频拼接方案:2路视频拼接;

工程作用:此工程目的是让读者掌握2路视频缩放+拼接的用法,以便能够移植和设计自己的项目;

工程Block Design请参考第3章节“设计思路框架”的“图像缓存”小节内容;

工程代码架构请参考第3章节“设计思路框架”的“工程源码架构”小节内容;

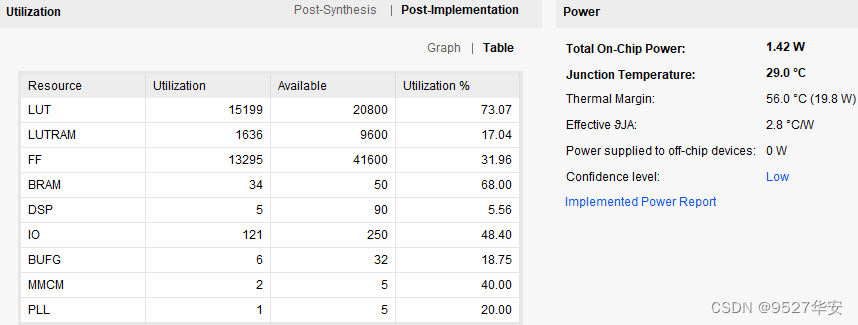

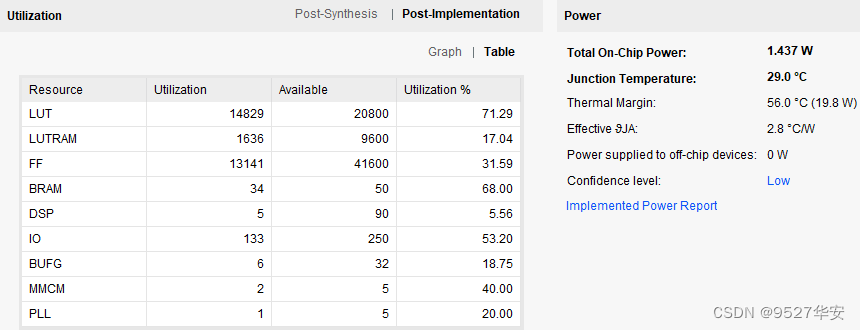

工程的资源消耗和功耗如下:该工程使用的是Xilinx fifo方案;

5、工程代码2详解:ov5640版本–>掌握4路视频缩放+拼接

开发板FPGA型号:Xilinx–Artix7–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头或动态彩条,分辨率1280x720;

输出:1920x1080的输出分辨率背景上叠加4路分辨率为960x540的缩放拼接的视频,即4分屏输出显示;

视频缩放方案:输入1280x720–>输出960x540;

视频拼接方案:4路视频拼接;

工程作用:此工程目的是让读者掌握4路视频缩放+拼接的用法,以便能够移植和设计自己的项目;

工程Block Design请参考第3章节“设计思路框架”的“图像缓存”小节内容;

工程代码架构请参考第3章节“设计思路框架”的“工程源码架构”小节内容;

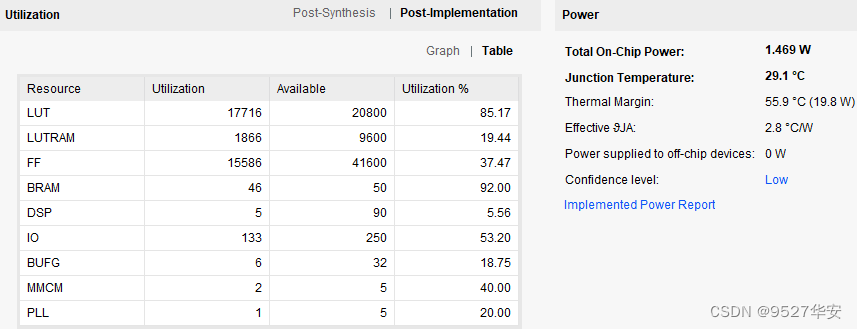

工程的资源消耗和功耗如下:该工程使用的是Xilinx fifo方案;

6、工程代码3详解:HDMI版本–>掌握2路视频缩放+拼接

开发板FPGA型号:Xilinx–Artix7–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入:HDMI或动态彩条,分辨率1920x1080;

输出:1920x1080的输出分辨率背景上叠加2路分辨率为960x1080的缩放拼接的视频,即2分屏输出显示;

视频缩放方案:输入1920x1080–>输出960x1080;

视频拼接方案:2路视频拼接;

工程作用:此工程目的是让读者掌握2路视频缩放+拼接的用法,以便能够移植和设计自己的项目;

工程Block Design请参考第3章节“设计思路框架”的“图像缓存”小节内容;

工程代码架构请参考第3章节“设计思路框架”的“工程源码架构”小节内容;

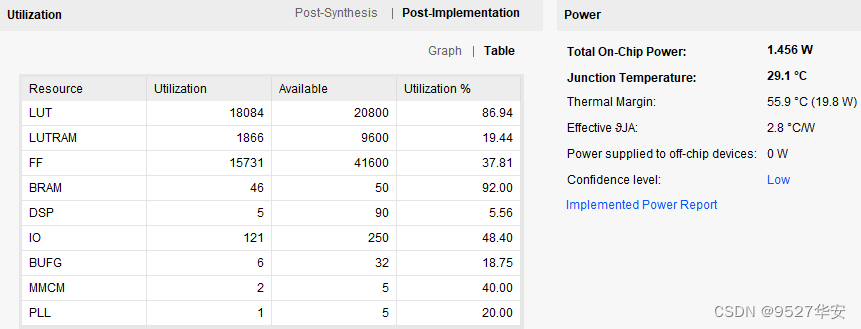

工程的资源消耗和功耗如下:该工程使用的是Xilinx fifo方案;

7、工程代码4详解:HDMI版本–>掌握4路视频缩放+拼接

开发板FPGA型号:Xilinx–Artix7–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入:HDMI或动态彩条,分辨率1920x1080;

输出:1920x1080的输出分辨率背景上叠加4路分辨率为960x540的缩放拼接的视频,即4分屏输出显示;

视频缩放方案:输入1920x1080–>输出960x540;

视频拼接方案:4路视频拼接;

工程作用:此工程目的是让读者掌握4路视频缩放+拼接的用法,以便能够移植和设计自己的项目;

工程Block Design请参考第3章节“设计思路框架”的“图像缓存”小节内容;

工程代码架构请参考第3章节“设计思路框架”的“工程源码架构”小节内容;

工程的资源消耗和功耗如下:该工程使用的是Xilinx fifo方案;

8、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

9、上板调试验证并演示

准备工作

需要如下器材设备:

1、FPGA开发板;

2、OV5640摄像头或HDMI输入设备,比如笔记本电脑,两者都没有则使用动态彩条;

2、HDMI连接线和显示器;

工程1:ov5640输入版本–>2路视频缩放拼接输出演示

工程1输出演示,我将动态彩条和ov5640摄像头缩放拼接输出的视频剪辑整理后如下:

视频前半段为动态彩条缩放拼接输出;

视频前后段为ov5640摄像头缩放拼接输出;

ov5640输入2路视频缩放拼接输出演示

工程2:ov5640输入版本–>4路视频缩放拼接输出演示

工程2输出演示,我将动态彩条和ov5640摄像头缩放拼接输出的视频剪辑整理后如下:

视频前半段为动态彩条缩放拼接输出;

视频前后段为ov5640摄像头缩放拼接输出;

ov5640输入4路视频缩放拼接输出演示

工程3:HDMI输入版本–>2路视频缩放拼接输出演示

工程3输出演示,我将动态彩条和HDMI缩放拼接输出的视频剪辑整理后如下:

视频前半段为动态彩条缩放拼接输出;

视频前后段为HDMI缩放拼接输出;

HDMI输入2路视频缩放拼接输出演示

工程4:HDMI输入版本–>4路视频缩放拼接输出演示

工程4输出演示,我将动态彩条和HDMI缩放拼接输出的视频剪辑整理后如下:

视频前半段为动态彩条缩放拼接输出;

视频前后段为HDMI缩放拼接输出;

HDMI输入4路视频缩放拼接输出演示

10、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA高端项目:Xilinx Artix7系列FPGA 多路视频缩放拼接 工程解决方案 提供4套工程源码+技术支持

目录 1、前言版本更新说明给读者的一封信FPGA就业高端项目培训计划免责声明 2、相关方案推荐我这里已有的FPGA图像缩放方案我已有的FPGA视频拼接叠加融合方案本方案的Xilinx Kintex7系列FPGA上的ov5640版本本方案的Xilinx Kintex7系列FPGA上的HDMI版本 3、设计思路框架设计框图…...

开源模型应用落地-业务优化篇(三)

一、前言 假如您跟随我的脚步,学习到上一篇的内容,到这里,相信细心的您,已经发现了,在上一篇中遗留的问题。那就是IM服务过载的时候,如何进行水平扩容? 因为在每个IM服务中,我们用JV…...

基于SpringBoot+Vue实现的物流快递仓库管理系统

基于SpringBootVue实现的物流快递仓库管理系统 文章目录 基于SpringBootVue实现的物流快递仓库管理系统系统介绍技术选型成果展示账号地址及其他说明源码获取 系统介绍 系统演示 关注视频号【全栈小白】,观看演示视频 基于SpringBootVue实现的物流快递仓库管理系…...

编程笔记 html5cssjs 072 JavaScrip BigInt数据类型

编程笔记 html5&css&js 072 JavaScrip BigInt数据类型 一、BigInt 数据类型二、BigInt 的创建和使用三、BigInt 操作与方法三、示例小结 JavaScript BigInt 数据类型是一种内置的数据类型,用于表示大于 Number.MAX_SAFE_INTEGER(即2^53 - 1&…...

matlab simulink 步进电机控制

1、内容简介 略 41-可以交流、咨询、答疑 2、内容说明 电动执行器定位控制在生产生活中具有广泛的应用,在使用搭载步进电机的电动执行器进行定位控制的时候,定位系统的定位精度和响应波形,会随着负载质量的变化而变化,这是由电…...

使用阿里云的IDaaS实现知行之桥EDI系统的单点登录

,在开始测试之前,需要确定用哪个信息作为“登陆用户的ID字段”。 这个字段用来在完成SSO登陆之后,用哪个信息将阿里云IDaaS的用户和知行之桥EDI系统的用户做对应。这里我们使用了 phonenumber 这个自定义属性。需要在阿里云做如下配置&#x…...

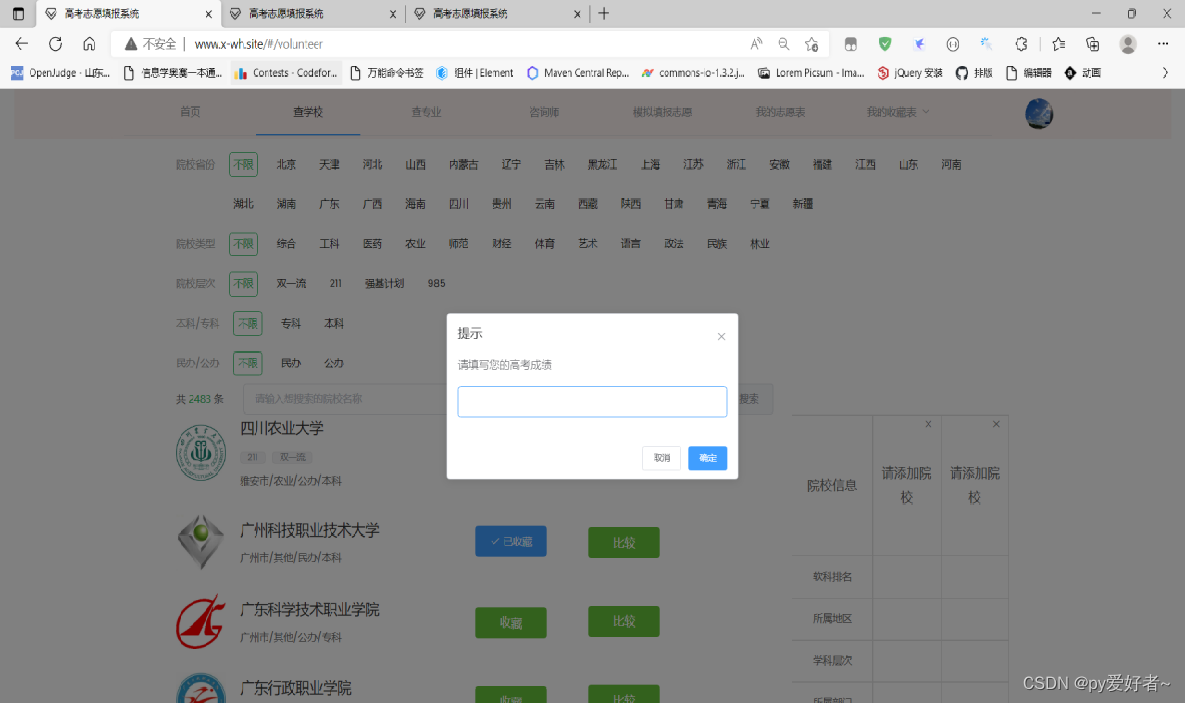

基于微服务的高考志愿智能辅助决策系统(附源码)

目录 一.引言 1、编写目的 2、系统功能概述 二.功能分析 三.微服务模块 1、微服务用户相关模块 (1)用户注册 (2)用户登录 (3)用户信息管理 (4)用户操作 2、微服务文件云存…...

LeetCode —— 137. 只出现一次的数字 II

😶🌫️😶🌫️😶🌫️😶🌫️Take your time ! 😶🌫️😶🌫️😶🌫️😶🌫️…...

pnpm、npm、yarn 包管理工具

1、npm 关键词:软件包管理器、命令行工具、一个社区和一个平台 npm(Node Package Manager)是一个用于Node.js环境的软件包管理器。它是一个命令行工具,用于安装、升级、删除和管理JavaScript软件包。npm最初是随同Node.js一起发布…...

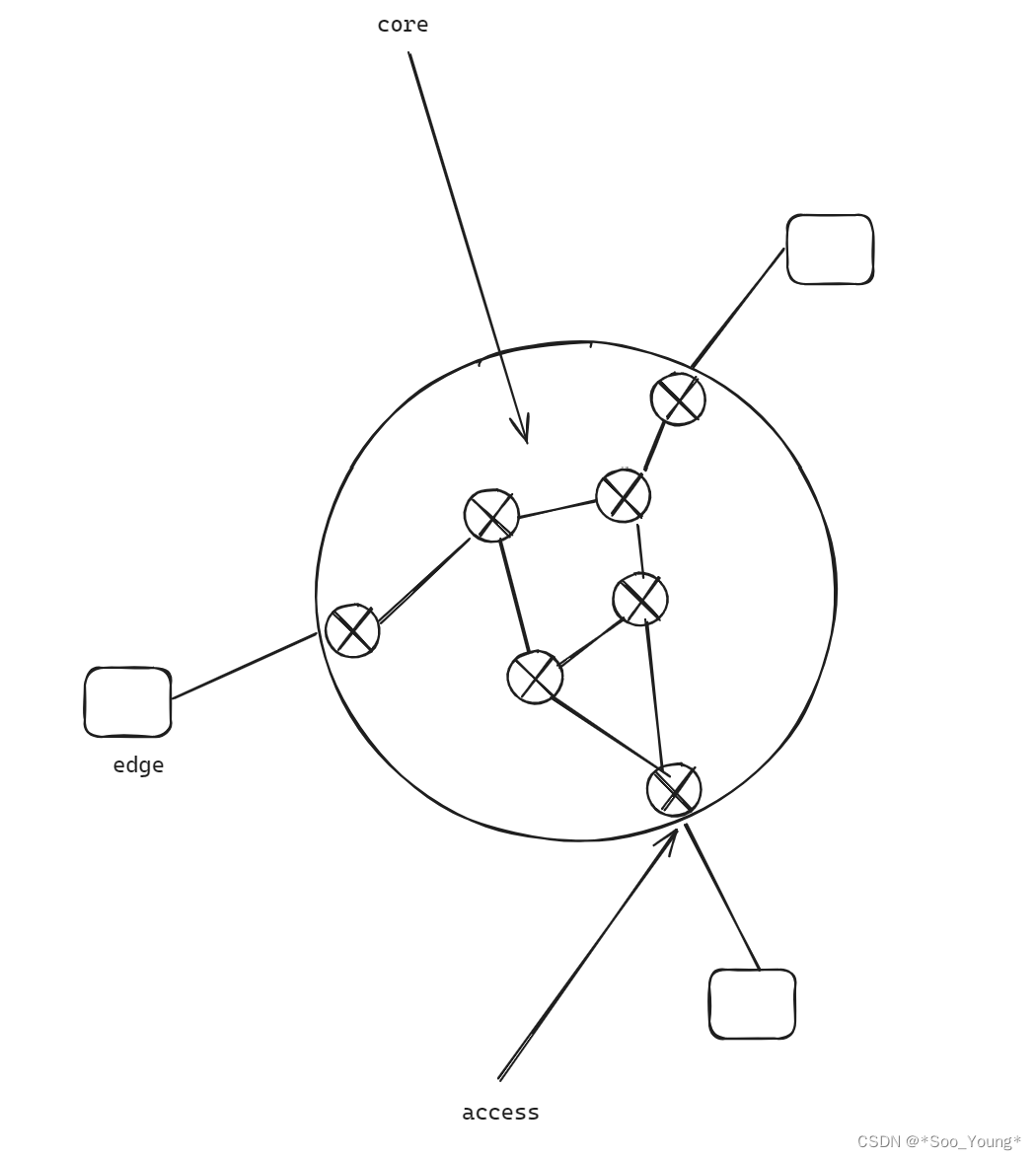

微服务知识

1、概念 大型单体应用拆分成多个独立部署运行的微服务(解决并发问题) 2、特点 3、技术栈 4、微服务带来的问题 5、微服务的注册中心 服务注册与发现:微服务实例在启动时会向注册中心注册自己的信息…...

如何在微信搭建私域流量池?

A: ①给客户打标签 添加标签,多维度构建用户画像,精准发送消息。 ②群发信息 选择自定义时间,上传内容 (支持文字,图片) ,一键群发 。 ③建立专属素材库 将常用的话术、图片与文件录入至素材库,员工可随…...

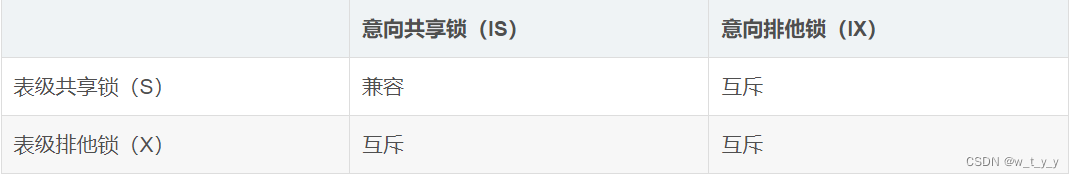

MySQL原理(三)锁定机制(1)综述

一、介绍: 1、锁的本质 业务场景中存在共享资源,多个进程或线程需要竞争获取并处理共享资源,为了保证公平、可靠、结果正确等业务逻辑,要把并发执行的问题变为串行,串行时引入第三方锁当成谁有权限来操作共享资源的判…...

Qt知识点总结

将枚举类型转换为字符串 这里使用的在网络编程中,获取socket状态并显示的时候,遇到的一个问题 #include <QMetaEnum>// 将枚举类型转换为字符串 QMetaEnum metaEnum QMetaEnum::fromType<QAbstractSocket::SocketState>(); const char *c…...

13)

什么是系统工程(字幕)13

0 00:00:00,670 --> 00:00:01,582 如果不加图 1 00:00:01,582 --> 00:00:02,130 怎么加 2 00:00:02,130 --> 00:00:03,225 我们来看一下 3 00:00:03,225 --> 00:00:03,590 你看 4 00:00:03,980 --> 00:00:06,720 右键点这个,添加元素 5 00:00:0…...

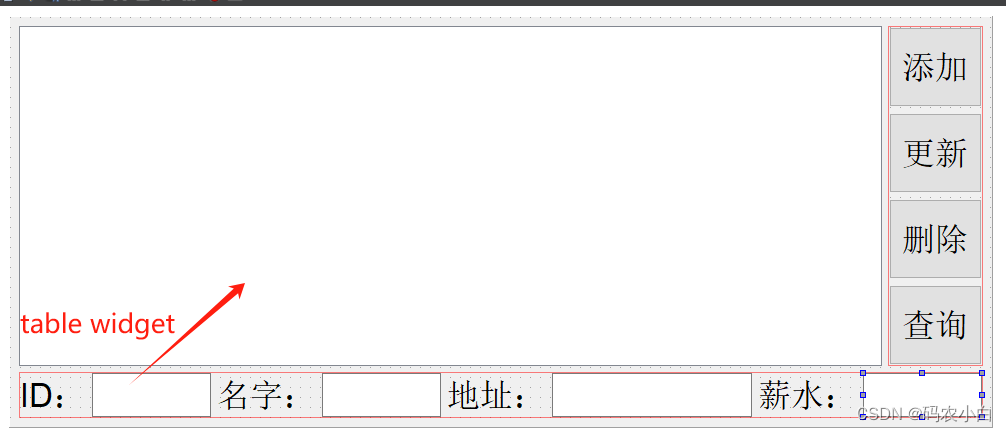

qt学习:Table widget控件

目录 头文件 实战 重新配置ui界面 添加头文件 在构造函数中添加初始化 显示方法 该实例是在sqlite项目上添加qt学习:QTSQL连接sqlite数据库增删改查-CSDN博客 头文件 #include <QTableWidgetItem> 实战 重新配置ui界面 用法介绍,可以双击…...

Android --- Content Provider是使用示例,通俗易懂

当两个应用程序之间需要共享数据时,可以通过 Content Provider 来实现。在这个示例中,我们将创建一个简单的 Content Provider,让 App_B 暴露人口总数的数据,并由 App_A 来获取这个数据。 首先,我们来创建一个简单的示…...

02-opencv简单实例效果和基本介绍-上

机器视觉概述 机器视觉是人工智能正在快速发展的一个分支。简单说来,机器视觉就是用机器代替人眼来做测量和判断。机器视觉系统是通过机器视觉产品(即图像摄取装置,分CMOS和CCD两种)将被摄取目标转换成图像信号,传送给专用的图像处理系统,得到被摄目标的形态信息,根据像素…...

中科大计网学习记录笔记(一):Internet | 网络边缘

计算机网络 前言: 学习视频:中科大郑烇、杨坚全套《计算机网络(自顶向下方法 第7版,James F.Kurose,Keith W.Ross)》课程 该视频是B站非常著名的计网学习视频,但相信很多朋友和我一样在听完前面…...

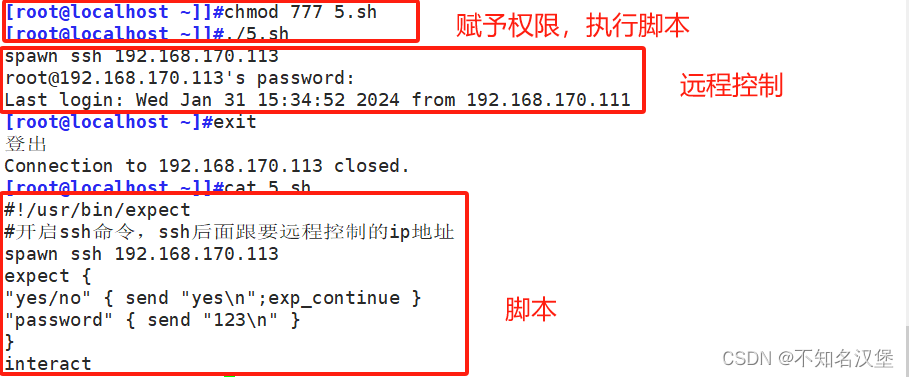

Shell脚本——免交互

目录 一、Here Document免交互 1、免交互概述 2、语法格式 2.1示例:免交互方式实现对行数的统计,将要统计的内容置于标记EOF之间,直接将内容传给wc-l来统计 3、变量设定 ①变量图换成实际值 ②整行内容作为变量并输出结果 ③使输出内…...

【数据分享】1929-2023年全球站点的逐月最高气温数据(Shp\Excel\无需转发)

气象数据是在各项研究中都经常使用的数据,气象指标包括气温、风速、降水、湿度等指标,其中又以气温指标最为常用!说到气温数据,最详细的气温数据是具体到气象监测站点的气温数据! 之前我们分享过1929-2023年全球气象站…...

让薪酬跟着人才走:国企核心人才激励保留的五个管理命题

当前,国有企业三项制度改革已进入攻坚深化期。劳动合同签订率、岗位说明书覆盖率、绩效考核实施率等量化指标普遍处于高位,制度框架的“四梁八柱”已基本确立。但在改革向纵深推进过程中,核心人才流失问题却时有发生。据调研反映,…...

DNS欺骗攻击原理与Wireshark实战防御指南

1. 这不是黑客电影桥段,而是每天都在发生的网络基础层失守DNS欺骗攻击——这个词听起来像极了影视作品里黑衣人敲几行代码就让银行网站跳转到钓鱼页面的炫技桥段。但现实远比剧情更朴素、更隐蔽、更危险:它不依赖0day漏洞,不挑战防火墙规则&a…...

3DS GBA硬件直通终极指南:用open_agb_firm获得原生游戏体验

3DS GBA硬件直通终极指南:用open_agb_firm获得原生游戏体验 【免费下载链接】open_agb_firm open_agb_firm is a bare metal app for running GBA homebrew/games using the 3DS builtin GBA hardware. 项目地址: https://gitcode.com/gh_mirrors/op/open_agb_fir…...

LimboAI在Godot 4中实现可维护游戏AI的工程化方案

1. 这不是又一个“AI行为树”教程——LimboAI在Godot 4里真正解决的是什么问题? 你有没有在Godot 4里写过这样的AI逻辑:一个巡逻的守卫,发现玩家后追击,进入攻击距离就挥剑,被击中后后退、喊话、短暂硬直,…...

【Lovable开发避坑红宝书】:17个被大厂隐藏的移动端情感设计陷阱及修复代码模板

更多请点击: https://intelliparadigm.com 第一章:Lovable移动端情感设计的底层认知与价值重定义 Lovable移动端情感设计并非界面动效或拟物图标的技术叠加,而是以人类情绪反馈回路为锚点,重构交互系统底层逻辑的设计范式。它要求…...

3分钟实现网页图片格式自由转换:Chrome扩展终极指南

3分钟实现网页图片格式自由转换:Chrome扩展终极指南 【免费下载链接】Save-Image-as-Type Save Image as Type is an chrome extension which add Save as PNG / JPG / WebP to the context menu of image. 项目地址: https://gitcode.com/gh_mirrors/sa/Save-Ima…...

PET模型完全指南:如何利用完形填空问题实现少样本文本分类与自然语言推理

PET模型完全指南:如何利用完形填空问题实现少样本文本分类与自然语言推理 【免费下载链接】pet This repository contains the code for "Exploiting Cloze Questions for Few-Shot Text Classification and Natural Language Inference" 项目地址: htt…...

从零到课标对齐:用Claude批量生成校本课程资源,72小时内完成一学期备课,你还在手动写?

更多请点击: https://intelliparadigm.com 第一章:从零到课标对齐:用Claude批量生成校本课程资源,72小时内完成一学期备课,你还在手动写? 教育数字化转型已进入深水区,一线教师却仍陷于“写教案…...

网易2026年Q1财报:游戏增长背后,AI、跨端与全球化面临哪些挑战?

网易发布2026年Q1财报5月21日,网易发布2026年第一季度财报。大体上,网易呈现出基本面企稳、公司效率提升以释放利润的态势。财报显示,网易Q1净收入306亿元,同比增长6.1%,Non - GAAP归母净利润为107亿元。游戏及相关增值…...

终极Ghidra逆向工程指南:30分钟从零掌握二进制分析

终极Ghidra逆向工程指南:30分钟从零掌握二进制分析 【免费下载链接】ghidra Ghidra is a software reverse engineering (SRE) framework 项目地址: https://gitcode.com/GitHub_Trending/gh/ghidra Ghidra作为一款由美国国家安全局(NSAÿ…...