2024 IC FPGA 岗位 校招面试记录

引言

各位看到这篇文章时,24届校招招聘已经渐进尾声了。 在这里记录一下自己所有面试(除了时间过短或者没啥干货的一些研究所外,如中电55所(南京),航天804所(上海))的经历以及感悟。希望给秋招的小伙伴或者明年、后年要找工作的小伙伴一些借鉴。

本人的话,研究生期间所做的项目都是跟FPGA相关,并未参与ASIC芯片设计相关的项目。

HR面试不记录在内,只记录跟技术面沾边的一些问题。

联发科技

实习 一面

岗位:IC设计验证

意向地点:安徽合肥

面试时间:2023 - 05 - 11 9:30

持续时间:半小时

面试官:2人(男)

面试流程:

- 自我介绍

- 面试官看简历,根据简历写的项目,让自己选择一个很熟悉的,做的时间最长的项目描述一下。

- 面试官要求打开白板,画出整个项目的流程图。

- 面试官问了DDR3读写的内容。

- 面试官问项目中的时钟分配,时钟是否同源等,以及一些CDC。

- 面试官问了有没有做过代码覆盖率。

- 面试官问有没有用过IC的一些EDA软件。

- 面试官询问可实习时长。(最好长一些,3个多月)

- 面试官简单介绍实习内容。

- 我咨询实习问题。

经验教训:

- DDR3读写控制,我上来就是说了用Xilinx 的7系列MIG IP核实现DDR3的读写控制器,自己负责对DDR3读写仲裁的一些逻辑实现。但是感觉面试官觉得既然用IP核实现就没啥好问的,感觉我没有做什么主要逻辑。当时我还强调了一下,用的AXI接口控制DDR3读写,以为面试官会问AXI协议,但是也没问。

- 项目介绍,由于我的项目是做雷达信号处理,但是他们可能不做雷达相关产品,对这个也了解比较少。可能也不太感兴趣。还有就是,实现的工程里面包含比较多的IP核,比如CSI2的一些IP,FFT IP、MIG IP等。他们感觉我的代码量不够,还专门问我,具体哪一部分是我自己编程实现的。感觉发哥这个对coding的要求还比较高。

- 实习时间,两个月左右应该有点短,至少可能是3个月。他们希望实习时间可以长一些。

总结:

这次面试我自己总体感觉不是很顺利,也可能是准备不足。一些项目的细节点本来想说的,但是有些遗忘。后面还是多复盘项目,准备要更细一点,更充分一些。不能只有个大概。特别是在特别能表现个人能力的地方。

后续:这个实习的话可能我去得意愿也不大,觉得比较麻烦。所以这个实习的事情后面也没有后话了。

提前批 一面

岗位:数字IC工程师(设计方向、验证方向、整合方向)

意向地点:安徽合肥

面试时间:2023 - 08 - 14 16:00

持续时间:1小时

面试官:2人(男)

面试流程:

- 自我介绍。

- 面试官问了我本科期间国家励志奖学金的获得门槛,是否可以连续多年获得。

- 简历里面写了熟练掌握IIC总线,其实挖了一个小坑,面试官问了几个问题,第一个问题,你这个 IIC 的模块是自己写的还是借鉴网络上的写法;第二个问题问的 IIC 有几种传输速度:彻底搞懂IIC总线(5)I2C总线传输速度;第三个问题问的 IIC 最快的传输速度为3.4Mbps,那么为什么不能更快。这个问题还没想到具体是为啥。第四个问题IIC的IO有什么特点:基础通信协议之 IIC (I2C) 详细讲解 这里面提到一点,IIC总线上所有器件的SDA、SCL引脚输出驱动都为 开漏(OD) 结构,通过外接上拉电阻实现总线上所有节点SDA、SCL信号的线与逻辑关系。第五个问题,如果现在有一个IIC或者UART的功能模块设计,你的设计思路是什么会分为哪几个模块:ASIC内部需要通过APB或者AHB总线向其他模块获取到将要发送的数据或者将接收到数据通过总线的形式传给需要的模块,另外串行通信还需要一些串/并转换模块,数据收发模块等。他主要想问的是ASIC或者FPGA内部模块之间通信的都会借助于一些总线访问(比如AXI AHB APB 协议)。这位面试官后面也给出了答案,原话:通常在芯片里面大部分都是用 AMBA BUS 做模块与模块之间的连接。

- 接下来是另外一位面试官。主要是问了简历上具体的几个项目。给我的感觉,面试官很想知道一个项目中一共有几个人负责,你个人起到了什么作用,做了什么事情,是否有创新,做的代码是前人就有的还是说自己写的,还以就是代码量有多少。我知道很多研究生的FPGA项目为了尽可能短时间的完成项目任务,都会使用一些IP CORE,但是这在面试官看来可能不是一个好的点,在他们看来大部分工作由IP CORE来完成,那么你的工作量到底在哪里。真的建议规避这一点,把自己写代码做的东西多说,调用IP核的事情少说。

- 面试官问我某次数学建模比赛获奖的相关问题。这里面可以发挥的点就比较多了,如果你是参赛队伍的主要负责人或者主要代码实现人就可以说挺多的。

- 简历上写了了解UVM,面试官让我简单说一下我所了解的UVM是什么?后面又问我为什么想着学UVM?

- 简历上写了了解DFT,所以面试官顺带就问了一嘴,DFT了解哪些相关的知识?插入的寄存器链和设计里面的寄存器区别在哪里?数字 IC 技能拓展(29)浅谈 DFT 与扫描链,主要的区别就是扫描的寄存器链相比于普通的寄存器多了1个MUX。

- 面试官说问一个Verilog相关的问题,关于deburrs电路,就是信号去毛刺的电路设计怎么做:计时毛刺的宽度,低于一定时间认为是毛刺,否则就是有用信号。

- 开始问求职意向地,有无女朋友,感觉自己最强的地方是什么,自己的弱点在哪里。

- 最后就是写一个 verilog 的握手小模块,他们说主要就是看下代码功底。最后时间快结束他们说不用往后写了,差不多了解了。

- 最后就是问了一些联发科技公司的情况。

总结,有些技术问题还是需要多抠一下,需要更深入一点。还有就是项目的细节还需要仔细复盘。

后续:次日HR就通知我一面通过,约二面的时间。发哥的效率这波很高。

提前批 二面

岗位:数字IC工程师(设计方向、验证方向、整合方向)

意向地点:安徽合肥

面试时间:2023 - 08 - 18 17:00

持续时间:40 min

面试官:1人(男)

面试流程:

- 自我介绍。

- 我的简历上的项目都写的项目负责人,面试官关于“项目负责人”的事情问了一些:项目都是你一个人来做的的吗还是说有一个团队,你是这个团队的主要负责人?那我的回答肯定是第二个,其实我建议简历上都写上项目负责人,问起来也没关系,就说是项目团队的主要负责人,另外最好结合具体的项目细说一点,体现出你项目负责人的功能,让面试官相信你的能力。

- 面试官问,这几个项目都是从头开始的还是说继承之前的项目继续做。他可能比较关心的是,这个项目里你自己真正能够参与的有多少。这里我建议大家实话实说,但是要加一点凸显自己能力的修饰,这很重要,也别是一些继承师兄师姐的项目。

- 面试官:哪个项目你觉得收获最大或者说投入的时间精力最大?这种问题就是到自己发挥的时候了,展现自己实力,多说一些项目里自己真正抠明白,很熟练的东西多说。

- 面试官问,找工作的思路或者考量的点是什么?这个点的话我觉得如果你是真心想以当前求职的IC行业作为后续的职业,那你就大胆直接地说出你的想法,如果你是跨专业就业,那你也要自信地说出支持你跨专业的理由,尽量让面试官觉得,这人说的合理。至于说工作地点的话,最好是包括你正在面试的这家公司的地点,可以更宽一点范围,但是不能不包括这家公司。

- 面试官:那你现在投了哪些公司?我就列说了几个,没有说很多。还对今年的就业行了稍微抱怨了一下,就业真的很难。

- 下面就是聊天,问我上几届师兄都去哪了?这个就实话说一些呗。没太大所谓。

- 面试官:IC前端设计 ,验证,以及后端设计DFT你都是可以接受的?我肯定了他的提问,但是也表达了更想做设计的意愿。

- 你觉得你研究生阶段最大的收获是什么?这个是一个很宽泛的问题,随便发挥,可以说自己对以后职业道路认识更加清晰,有了更明确的规划,也可以说自己技术上的长进。

- 研究生期间做的项目你觉得对你的挑战大吗?你还是一个学生,挑战和困难肯定有的,挑自己觉得最好说的几个说一下,当然也不要太否定自己吧,不要让面试官觉得你做项目很吃力。

- 工程节点加班,这个你怎么看?其实就是问你能不能接收在项目关键节点的时候加班。这个就不用教了哈哈哈,你应该知道咋回答的。我觉得这个完全没问题的,甚至我还举例说自己研究生期间到项目节点出差加班啥的。能够证明你可以应对困难,能吃苦。

- 你对我们这边有多少了解?这个就是要求大家在二面之前要做的准备工作,包括公司理念,业务范围。主要技术分支等等。

- 是否单身?家里人对找工作的态度?

- 问题反问环节,我问了发哥的新人培养流程以及部门划分。这里跟大家透露一点,新员工入职有2个月的整体培训,结束后结合个人意愿,培训表现将每个人分配到不同部门的不同岗位,之后再进行一些与本部门契合的一些专业培训。

整体感觉二面还是比较轻松的。也就这些记录了。

中电38所

提前批 技术面

岗位:FPGA设计

意向地点:安徽合肥

面试时间:2023 - 06 - 30 9:00

持续时间:半小时

面试官:1人(男)

面试流程:

(小插曲:我的简历上写了博客链接的东西,但是奈何线下宣讲时交上去的是纸质简历,面试官提前发邮件给我,加了微信说想看下我写的博客,后来我把电子版的简历发给他,他应该是看了我的博客内容)

- 刚开始他说了一些对写技术博客的看法,对我的博客给了一些肯定,并且说业内人坚持写博客记录的也不多,除了CSDN他说还有GITHUB GITEE等平台可以直接上传工程,便于工程管理。

- 后面就步入正题,由于他对我的整体印象和感觉很不错,他就让我自己说两个在技术上很有成就感的事情。我就说了自己手写FIR滤波器以及CFAR检测器(雷达上用的)的过程。中间的交流还挺愉快的。

- 后面他说提一个需求就是,CFAR检测器有很多诸如保护单元个数、参考单元个数等关键参数,那么想要做到适时调整测试,有什么思路。我当时说了两个:通过串口或者网口建立上位机与FPGA之间的通信,然后将关键参数解析后直接送入CFAR检测器模块。他首先是认同了这种思路,另外就是他提出用AXI-Lite协议,AXI协议支持多主多从,内部有自己的一套仲裁机制。开发起来更方便。并且XILINX 的IP核基本上都用的AXI接口。

- 他问了我对HLS咋看,我说不太了解,基本都是直接写设计代码的。

- 后面基本上就是介绍所内部门情况。面试官自己是数字中心部门的。然后也捎带说了加班情况、出差情况,研究所都那样哈哈。自己斟酌。

总结:

这次面试总体上来说还是比较的轻松愉悦。后面对AXI、以及HLS可能要再准备一些。

后续:

HR面试在线下进行,且与技术关系不大,不做记录了。大约一周后收到了录用意向,给到22W,由于自身的考虑,没有签。

航天804所

面试主要看项目是否对口,个人能力,想招一些进去就能直接干活的。

offer详情:

任职岗位:雷达信号处理设计岗,部门:21室。在征求本人意见的基础上;

合同期:单位将在入职后与你就双方权利义务签订劳动合同,合同期为自入职之日起3年,试用期为6个月。

薪资待遇:

1.试用期工资:不低于13500元/月。

2.转正后年收入:年度考核称职基础生不低手31万元/年,薪酬与绩效考核挂钩。

中电55所

技术面+HR面。技术面问的比较浅,就问一些项目和FPGA的内容。

offer详情:

一、工作岗位:FPGA逻辑设计工程师

二、工作地点:江苏省南京市

三、薪酬福利

(一)编制:给予事业编制。

(二)薪酬:第一年税前年薪总包26-33万元人民币,具体根据岗位价值、个人绩效取酬。

(三)福利:

1.除五险一金外,缴纳职业年金:

2.提供职工食堂、单身公寓、通勤班车、健康体检、补充医疗保险、户籍办理等多方面保障:

3.除国家法定节假日外,提供带薪年休假、春节长假、探亲假等假期。

凌久微电子

技术面

岗位:前端设计工程师

意向地点:湖北武汉

面试时间:2023 - 09 - 14 09:10

持续时间:30 min(腾讯会议)

面试官:1人(男)

面试流程:

- 自我介绍。

- 从数据流角度,介绍一下你的XX项目,以及你自己主要负责的方面。

- 你的项目基本都有一些高速通信的内容,时序约束怎么做的。

- 除了建立保持时间的分析,静态时序分析报告还可以做哪些?

- FPGA设计与ASIC设计时序分析会有哪些区别?

- 反问一些问题。

总结,感觉问的很浅,不知道就是这样还是KPI面,且看后续结果如何。

终面(主管面)

岗位:前端设计工程师

意向地点:湖北武汉

面试时间:2023 - 09 - 22 11:30

持续时间:30 min(线下)

面试官:2人(男)

面试流程:

- 自我介绍。

- 介绍一个项目,认为有挑战性的难点。

- 问入职前有没有时间提前学习芯片设计验证的知识,应该和中科大 “一生一芯” 计划合作,在平台上学习设计精简指令集CPU,最后通过考核的话,入职后的实习培训可考虑缩短或者取消。

- 现场让面试助理打开我的博客查看,问博客的原创性,积累的时长,写博客初衷何在。

- 其他的不太重要

过了终面等待谈薪。

谈薪

谈薪前的交流会

形式:腾讯会议

主要信息:

1、公司详情:

2021年3月18日,注册成立的武汉凌久微电子有限公司,将以做中国人自己的芯片为己任,坚持市场导向,充分发挥研究所沉淀的技术积累,潜心研制安全、稳定、可靠的自主国产芯片,做国产GPU芯片领域的引领者。

2、工作时间:

周一至周五 8: 00-17: 00,午休时间为 12: 00-13: 30 (武汉)周一至周五 8: 30-17: 30,午休时间为 12: 00-13: 30 (西安、成都)

3、培养晋升

- 公司制度流程培训+户外拓展 (1-2周)

- 基础技能培训 (不超过35天)

- 一对一导师制培养

- 两年一次竞聘管理岗机会

- 每年一次调薪机会

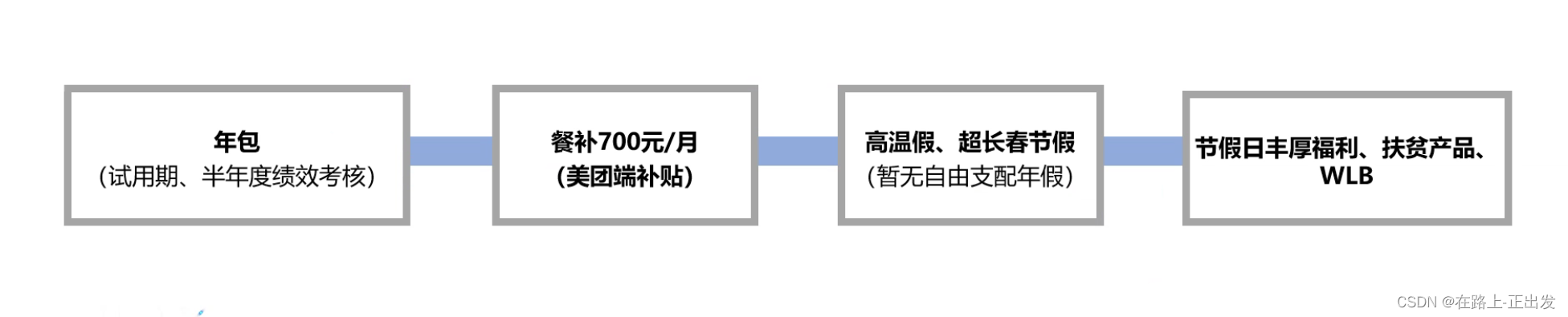

谈薪

基本月工资:11400RMB / 月

绩效:6000RMB / 月

共15薪,12+3(年终奖),总包17400*15=26.1W

每月餐补 700RMB ,发放至美团账户

公积金缴纳按17400的12%(双边),共24%;五险的缴纳按11400的对应比例。

试用期六个月工资发80%,转正后20%的工资会补发。

无末尾淘汰制。一年可申请涨薪一次,涨幅10%~20%。无普调。

由于所开薪资与本人预期存在差距,在申请之后迎来了第二次谈薪,总包29.1W,base提升至12900RMB / 月,绩效提升至6400RMB / 月,其他薪资结构和五险一金缴纳比例保持不变。

签约

违约金13000元

次年三月才处理毁约的三方

遂拒签

华为海思

正式批 技术一面

岗位:芯片与器件设计工程师(数字芯片)

意向地点:上海

面试时间:2023 - 09 - 18 14:15

持续时间:50min 左右

面试官:1人(男)

面试形式:线下面试

面试流程:

- 自我介绍;

- 体现在代码编写上的话,你觉得FPGA设计与ASIC芯片设计区别在哪里,举例说一下?

- 了解STA的话,你项目中有具体用到时序分析和约束吗,结合项目说一下?

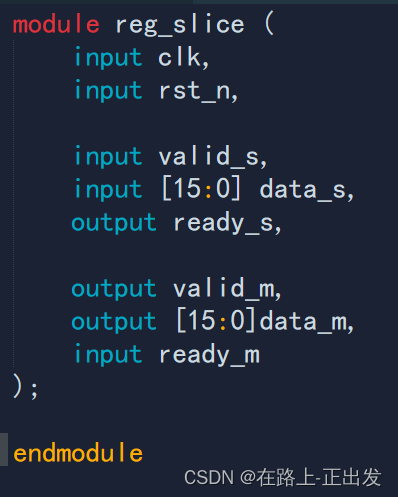

- 手撕一道代码题,关于上下游模块的握手对接;模块的缓存深度为1,主要端口包括:

- 复盘一道笔试题,问验证里面,同步怎么做到?(event、mailbox、semaphore;并且问具体是啥意思,怎么实现同步)

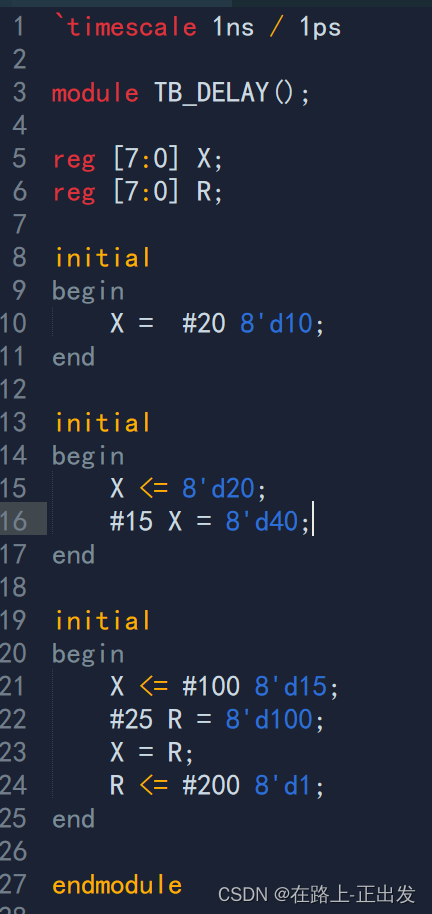

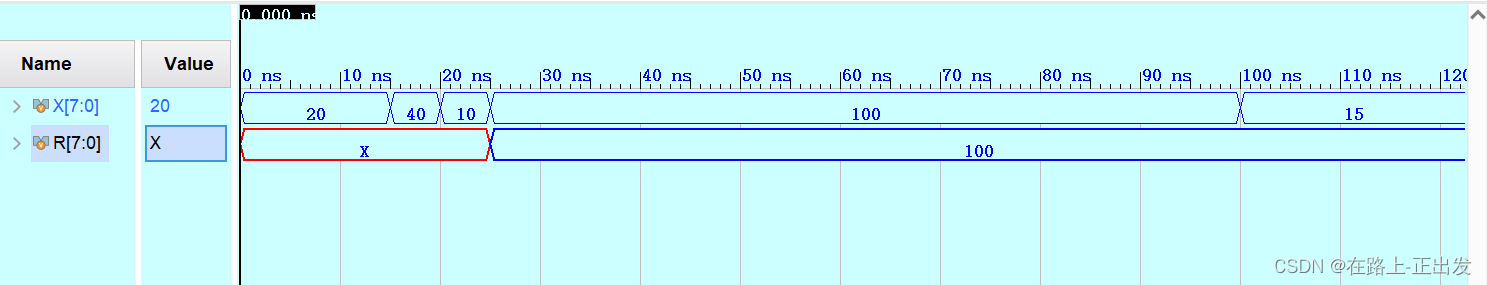

- 看了一道题,关于三个 initial 块里面,对于同一个信号的赋值,问不同仿真时刻,信号的值分别是多少?类似这种:问X在不同时刻的取值。

Vivado仿真结果:

主要的注意点:

1、所有的 initial 块都是在仿真零时刻同时并行执行的;

2、非阻塞赋值的延迟不影响后面阻塞赋值的执行;

3、存疑,面试官告诉我说,最后R变化的时候X也应该变化,但是仿真来看没有变化。可能是不同的仿真平台有差别吧,此处存疑。

后面应该没问啥了,就算问了,可能也是不太重要的,记不得了。

面试完出来,很快就短信通知面试过了,等待二面。

正式批 技术二面

岗位:芯片与器件设计工程师(数字芯片)

意向地点:上海

面试时间:2023 - 09 - 18 15:30

持续时间:60min 左右

面试官:1人(男)

面试形式:线下面试

面试流程:

- 自我介绍;

- 问了芯片的低功耗设计(因为我简历写了);(时钟门控、降低翻转率、电源门控等)

- UART串口的速率用的多少?

- 简单说下IIC协议,问板级这两根通信线,有什么硬件结构。(上拉电阻到高电平)

- 手撕一道代码,关于CDC的,20MHz和30MHz之间的,应用场景是关于CPU中断状态的置位与清零。可以用脉冲展宽然后用同步器打拍处理,也可以握手的方式(稍许麻烦)。题目本身理解了之后不是很难。

- 问AXI总线,有哪些通道?握手咋实现?outstanding?

- 反问环节;

后面应该没问啥了,就算问了,可能也是不太重要的,记不得了。

面试完出来,很快就短信通知面试过了,等待主管面。

正式批 主管面(kirin部门)

岗位:芯片与器件设计工程师(数字芯片)

意向地点:上海

面试时间:2023 - 09 - 18 17:14

持续时间:20min 左右

面试官:1人(女)

面试形式:线下面试

面试流程:

- 自我介绍;

- 挑一个项目说一下,系统结构,你自己负责那部分的主要工作;

- 怎么看待华为的企业文化;

- 今年工作找的咋样了,包括身边人;

- 为啥想来上海;

- 反问环节;

面试完出来,过了一段时间就短信通知面试过了,至此华为秋招面试结束。

华为面试小结:

线下面试,所有的代码都是写在A4纸上,这个环节不要太担心,主要还是写代码,写完以后面试官会让你说思路,怎么想的,即使现场写的代码有点瑕疵或者欠考虑一些条件,都不是很重要,毕竟没有给你debug的时间和条件。

所以在交流环节告诉面试官你的理解和想法很关键。

我的这个记录仅作参考,因为每个人项目经历不一样,简历写得也千差万别,所以面试的时候问的内容也是差别很大的,加油吧。

后续

12月22日等到了主管的电话,沟通了薪资待遇,说是已经报批。考虑到以后职业的发展,准备毁约新思签海思。

2024-01-29目前还在等待意向书……(遥遥无期)

2024-01-31收到意向书

2024-02-02签约沟通会议

中新赛克

技术面

岗位:前端设计工程师

意向地点:江苏南京

面试时间:2023 - 09 - 25 15:30

持续时间:30 min(腾讯会议)

面试官:1人(女)

面试流程:

- 共享屏幕,共享简历内容,自我介绍。

- 介绍项目,问道信号处理中乘法器的使用,是否是专用硬件乘法器。问各信号处理环节数据位宽以及截位处理。另一个项目的AD芯片配置(SPI),雷达系统可重构特点体现在哪里。

- 问目前RTL代码量有多少。

中新赛克以前是中兴的子公司,现在好像被卖了。据说没啥技术,加班很严重,绩效就看加班时长,还会裁应届生。如果想去可得打听清楚再决定。我的话也就面一面,看给开多少,应该不去的。

Synopsys(新思科技)

面试前沟通

形式:电话

内容:了解本人籍贯,学历,专业等情况。了解一些IC设计知识的掌握情况。RTL代码编写、测试验证,覆盖率、CDC设计、综合synthesis等等。

技术一面

岗位:数字IC前端设计

意向地点:湖北武汉

面试时间:2023-10-24 16:30~18:20

面试官:2人

面试关键point:

- 自我介绍

- 选择一个最熟悉的项目讲一下,画一下框图并口述介绍。由于项目用到一些知识,关于UART,全双工还是半双工?自己写RTL代码还是用IP实现?RTL代码如何实现的,画一下框图。串口指令结构,是否有校验,如何校验,校验的作用?关于AD采样与数据传输,缓存如何实现?吞吐量评估?让手写一个固定优先级的仲裁器,if-else结构可否替换为case?关于复位,同步复位优点?异步复位优点?异步复位同步释放的电路图?关于时序分析,建立保持时间的概念,一个计算最高时钟频率的时序分析题。关于FPGA开发流程,介绍一下。关于约束,时序约束,用过哪些约束命令?关于CDC,如何实现,异步FIFO的地址数据CDC问题,空满标志判断。

总结:问的很细,没准备的话很容易被问住。

1~2周出结果。

后续进展:

2天后收到HR电话面试;次周一收到offer。

10月31日,签约新思科技了。感觉在武汉外企还是很香的,WLB,弹性工作制,无加班。带薪年假18天,每年加一天,26天封顶。

宇量昇科技

技术一面

岗位:FPGA开发工程师

意向地点:上海

面试时间:2023-12-28 19:00~19:45

面试官:1人

面试关键point:

- 自我介绍

- 问项目,个人感觉主要会问一些接口,比如IIC UART ADC 以太网。

技术二面

岗位:FPGA开发工程师

意向地点:上海

面试时间:2023-12-28 20:30~21:00

面试官:1人

面试关键point:

- 自我介绍

- 问项目,主要问一些静态时序分析、UDP、GTH、serdes

- 问了一个题目,32选1需要几个6输入LUT,逻辑级数是多少

主管面

岗位:FPGA开发工程师

意向地点:上海

面试时间:2024-01-06 16:00~16:10

面试官:1人

面试关键point:

- 自我介绍

- 现有已签约offer情况,年薪多少,签了为啥又找,毁约容易吗

- 期望薪资

- 简单聊FPGA在公司的应用开发情况

offer

大概审批一周给了offer,给的级别是L5,好像说和华子15C持平。

相关文章:

2024 IC FPGA 岗位 校招面试记录

引言 各位看到这篇文章时,24届校招招聘已经渐进尾声了。 在这里记录一下自己所有面试(除了时间过短或者没啥干货的一些研究所外,如中电55所(南京),航天804所(上海))的经…...

Linux 命令 —— top

Linux 命令 —— top 相对于 ps 是选取一个时间点的进程状态,top 则可以持续检测进程运行的状态。使用方式如下: 用法: top [-d secs] | [-p pid] 选项与参数: -d secs:整个进程界面更新 secs 秒。默认是 5 5 5 秒。…...

【Docker】使用VS创建、运行、打包、部署.net core 6.0 webapi

欢迎来到《小5讲堂》,大家好,我是全栈小5。 这是《Docker容器》系列文章,每篇文章将以博主理解的角度展开讲解, 特别是针对知识点的概念进行叙说,大部分文章将会对这些概念进行实际例子验证,以此达到加深对…...

抖音短视频矩阵营销系统源头独立开发搭建

开发背景 抖音短视频矩阵系统源码开发采用模块化设计,包括账号分析、营销活动、数据监控、自动化管理等功能。通过综合分析账号数据,快速发现账号的优势和不足,并提供全面的营销方案,以提高账号曝光率和粉丝数量。同时,…...

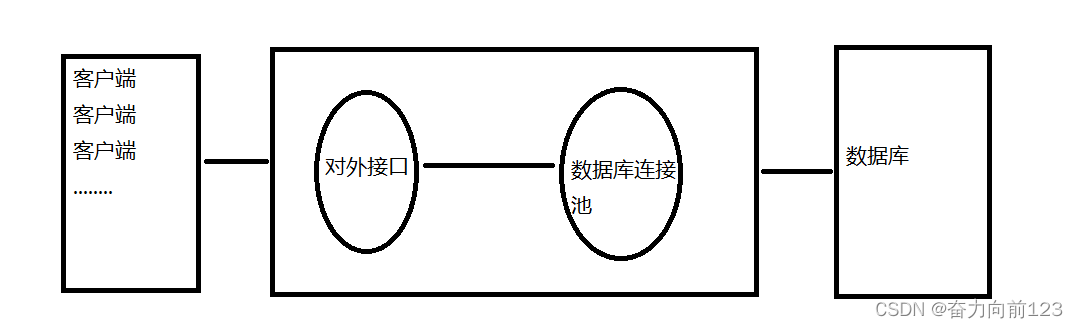

Springboot使用数据库连接池druid

springboot框架中可以使用druid进行数据库连接池,下面介绍druid在springboot中使用和参数配置介绍。 数据库连接池(Druid)是一种用于管理数据库连接的机制,其工作原理和常见使用方法如下: 原理:数据库连接…...

Springboot-前后端分离——第三篇(三层架构与控制反转(IOC)-依赖注入(DI)的学习)

本篇主要对ControllerServiceDAO三层结构以及控制反转(IOC)与DI(依赖注入)进行总结。 目录 一、三层架构: Controller/Service/DAO简介: 二、控制反转(IOC)-依赖注入(DI): 概念介绍: DOC与…...

Open CASCADE学习|曲面上一点的曲率及切平面

曲率(Curvature)是一个几何学的概念,用于描述一个物体的形状在某一点上的弯曲程度。在我们日常生活中,曲率与我们的生活息息相关,如道路的弯道、建筑物的拱形结构、自然界的山脉等等。了解曲率的概念和计算方法&#x…...

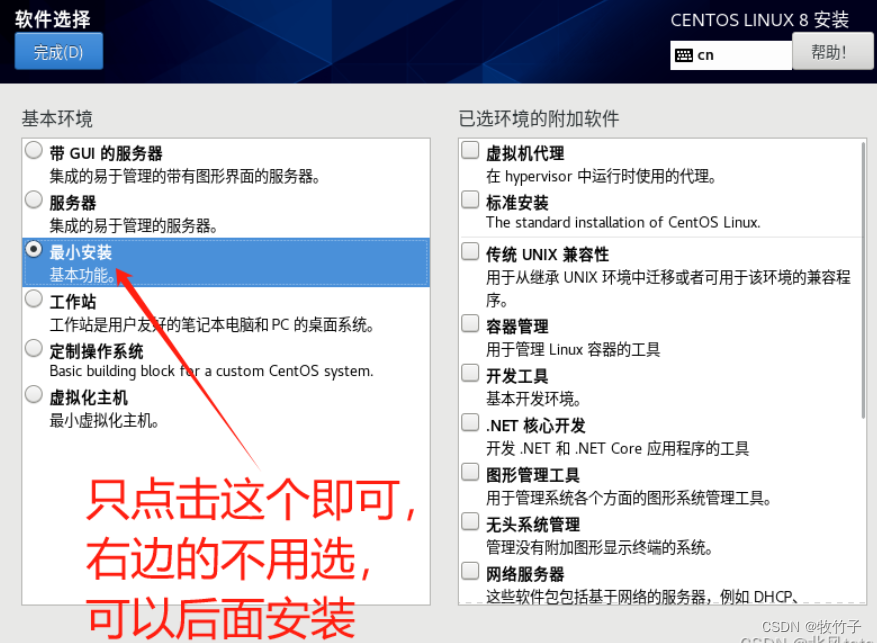

CentOS 8最小安装和网络配置

文章目录 简介下载地址VMware 17创建虚拟机最小化安装拥有的外部命令yum源有问题网络配置开启SSH Server服务关闭防火墙设置host配置JDK环境完整参考 简介 CentOS 8的IOS如果下载DVD版本至少有10G 这里我们直接选择最小安装,因此选择最小系统boot版本 CentOS-8.5.21…...

【代码随想录-链表】环形链表 II

💝💝💝欢迎来到我的博客,很高兴能够在这里和您见面!希望您在这里可以感受到一份轻松愉快的氛围,不仅可以获得有趣的内容和知识,也可以畅所欲言、分享您的想法和见解。 推荐:kwan 的首页,持续学习,不断总结,共同进步,活到老学到老导航 檀越剑指大厂系列:全面总结 jav…...

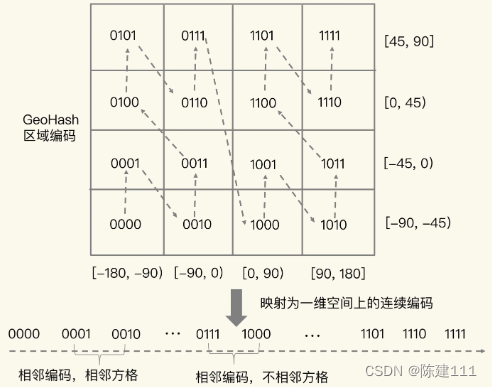

Redis核心技术与实战【学习笔记】 - 7.Redis GEO类型 - 面向 LBS 应用的数据类型

前言 前面,介绍了 Redis 的 5 大基本数据类型:String、List、Hash、Set、Sorted Set,它们可以满足绝大多数的数据存储需求,但是在面对海里数据统计时,它们的内存开销很大。所以对于一些特殊的场景,它们是无…...

银行数据仓库体系实践(17)--数据应用之营销分析

营销是每个银行业务部门重要的工作任务,银行产品市场竞争激烈,没有好的营销体系是不可能有立足之地,特别是随着互联网金融发展,金融脱媒”已越来越普遍,数字化营销方兴未艾,银行的营销体系近些年也不断发展,…...

Linux一键部署telegraf 实现Grafana Linux 图形展示

influxd2前言 influxd2 是 InfluxDB 2.x 版本的后台进程,是一个开源的时序数据库平台,用于存储、查询和可视化时间序列数据。它提供了一个强大的查询语言和 API,可以快速而轻松地处理大量的高性能时序数据。 telegraf 是一个开源的代理程序,它可以收集、处理和传输各种不…...

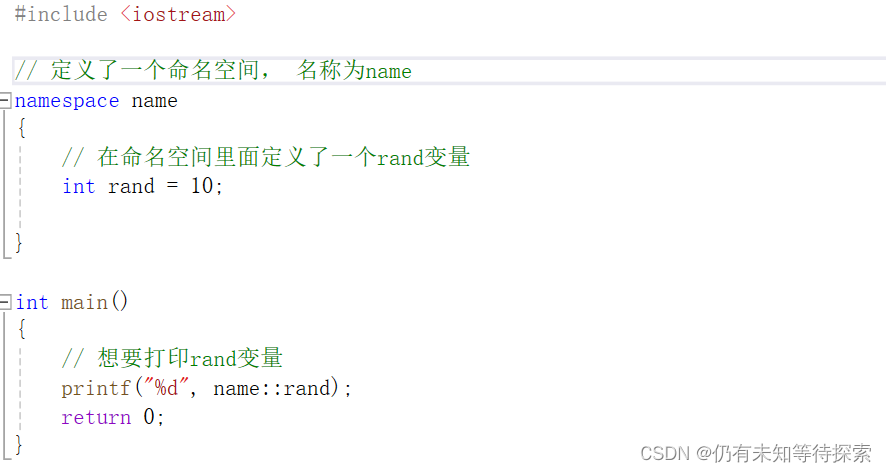

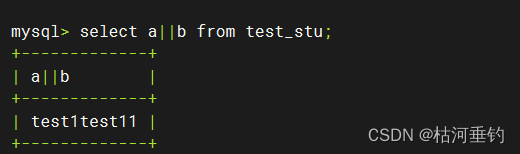

C/C++ C++入门

个人主页:仍有未知等待探索-CSDN博客 专题分栏:C_仍有未知等待探索的博客-CSDN博客 目录 一、C关键字 二、命名空间 1、区别 1. C语言 编辑 2. C 2、命名空间定义 3、命名空间的使用 三、C输入&输出 四、缺省参数 五、函数重载 六、引用 …...

【后端】乐观锁和悲观锁

前置知识点 锁:一种确保数据安全的机制和手段。 在多个线程修改共享变量时,我们可以对修改操作进行加锁。当多个用户修改表中的同一数据时,我们可以对该行数据进行加锁(行锁)。锁是用于控制多个操作在并发环境下按顺…...

软件工程知识梳理1-可行性研究

目的:确定问题是否值得去解决。就是用最小的代价在尽可能短的时间内确定问题是否能够解决。 可行性研究实质上是要进行一次大大压缩简化了的系统分析和设计的过程,也即是在较高层次上以较抽象的方式进行系统分析和设计的过程。 考察点:技术可…...

2024美国大学生数学建模E题财产保险的可持续模型详解思路+具体代码

2024美国大学生数学建模E题财产保险的可持续模型详解思路具体代码 前言 很快啊!啪的一下拿到题目就开始做题!简单介绍一下我自己:博主专注建模五年,参与过大大小小数十来次数学建模,理解各类模型原理以及每种模型的建…...

pytorch nearest upsample整数型tensor

在用 torch.nn.Upsample 给分割 label 上采样时报错:RuntimeError: "upsample_nearest2d_out_frame" not implemented for Long。 参考 [1-3],用 [3] 给出的实现。稍微扩展一下,支持 h、w 用不同的 scale factor,并测试…...

MySQL的SQL MODE

目录 举例: --常见SQL mode --mysql8 sql_mode 官方文档 https://dev.mysql.com/doc/refman/8.0/en/sql-mode.html --查看全局的SQL MODE select global.sql_mode; --查看当前会话的SQL MODE select session.sql_mode; --运行时修改全局的SQL mode set gl…...

GO EASY 框架 之 NET 05

目录 1、Overview 2、Agent接口源码 3、收发消息 4、AgentHandle接收函数 5、conns.Conn接口 1、Overview 名称:agent.Agent 网络链接 接口; DESC:网络链接,服务端与客户端通信媒介; 封装:进一步封…...

【教程】谈一谈 IPA 上传到 App Store Connect 的几种方法

【教程】谈一谈 IPA 上传到 App Store Connect 的几种方法 引言 在应用开发过程中,将应用程序上传到 App Store Connect 是一个关键的环节。本文将探讨几种常见的 IPA 文件上传方法,包括 Xcode、Application Loader、altool、Appuploader以及Transport…...

微信小程序二维码生成实战指南:weapp-qrcode高效解决方案

微信小程序二维码生成实战指南:weapp-qrcode高效解决方案 【免费下载链接】weapp-qrcode 微信小程序快速生成二维码,支持回调函数返回二维码临时文件 项目地址: https://gitcode.com/gh_mirrors/weap/weapp-qrcode 在微信小程序开发中,…...

Win11Debloat:3分钟彻底清理Windows 11臃肿系统,恢复纯净体验

Win11Debloat:3分钟彻底清理Windows 11臃肿系统,恢复纯净体验 【免费下载链接】Win11Debloat A simple, lightweight PowerShell script that allows you to remove pre-installed apps, disable telemetry, as well as perform various other changes t…...

终极文档下载指南:如何用kill-doc一键拯救30+平台的文档资源

终极文档下载指南:如何用kill-doc一键拯救30平台的文档资源 【免费下载链接】kill-doc 看到经常有小伙伴们需要下载一些免费文档,但是相关网站浏览体验不好各种广告,各种登录验证,需要很多步骤才能下载文档,该脚本就是…...

UE5下载安装避坑指南:硬件驱动、VS环境与版本管理实战

1. 这不是“点几下就能好”的安装,而是UE5项目生命周期的第一次关键决策很多人点开Epic Games Launcher,看到那个醒目的“Install”按钮,下意识就点了下去——结果十分钟后卡在98%,或者装完打开编辑器直接报错“Failed to load mo…...

Midjourney中画幅风格不生效?5个致命配置错误正在 silently 毁掉你的成片率

更多请点击: https://kaifayun.com 第一章:Midjourney中画幅风格失效的真相与底层机制 Midjourney 中的中画幅(Medium Format)风格常被用户以 --style medium-format 或关键词 medium format film 调用,但大量实测表…...

基于“点击化学”的聚合物荧光标记定制合成

当化学成为“纽带”:基于点击化学的聚合物荧光标记定制合成关于我们的定制在生物医学成像与材料科学的前沿研究中,获得一种既能稳定发光、又能精准标记目标分子的探针,往往是实验成功的关键。我们专注于为客户提供基于点击化学的聚合物荧光标…...

)

自指系统与算术障碍的跨领域猜想:封闭认知框架下的几何-物理-计算统一理论研究(世毫九实验室原创研究)

自指系统与算术障碍的跨领域猜想:封闭认知框架下的几何-物理-计算统一理论研究(世毫九实验室原创研究) 作者:方见华 单位:世毫九实验室 摘要 本研究提出了一个关于"自指系统与算术障碍的跨领域猜想"的理论框…...

股票打分制方法论

人工列提纲做评审,AI丰富内容AI模型:Deepseek仅供参考,市场有风险,投资需谨慎打分制股票算法:构建系统化、多维度的股票评估体系在股票投资领域,面对纷繁复杂的市场信息和海量数据,如何科学、客…...

从elm-react-native学习React Native最佳实践:10个关键开发技巧

从elm-react-native学习React Native最佳实践:10个关键开发技巧 【免费下载链接】elm-react-native A react native app simulating eleme app,run ios and android. 项目地址: https://gitcode.com/gh_mirrors/el/elm-react-native 想要快速掌握…...

)

Linux 文件隐藏属性 chattr、lsattr 详解——锁住文件防误删(运维必备)

前言很多人只知道 chmod、chown 改权限,却不知道 Linux 还有隐藏文件属性。普通权限能被 root 绕过,而 chattr 隐藏属性可以 锁住文件,root 也无法删除、修改,是服务器防护、防误删、保护配置文件的核心命令。一、命令简介lsattr&…...