PCIE 参考时钟架构

一、PCIe架构组件

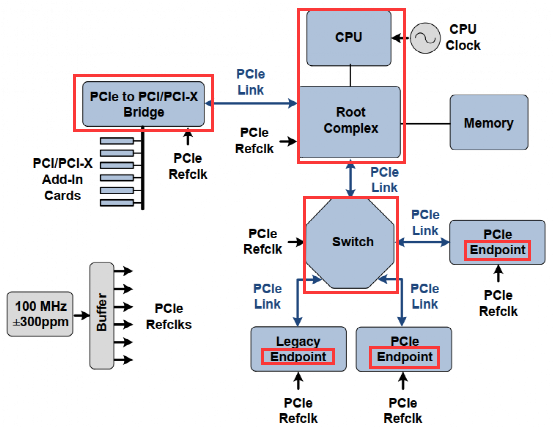

首先先看下PCIE架构组件,下图中主要包括:

ROOT COMPLEX (RC) (CPU);

PCIE PCI/PCI-X Bridge;

PCIE SWITCH;

PCIE ENDPOINT (EP) (pcie设备);

BUFFER;

各个器件的时钟来源都是由100MHz经过Buffer后提供。一个PCIE树上最多可以有256个PCIE设备。

1、RC (ROOT COMPLEX)

RC是PCIE树的根节点,为主模式,RC可以有一个或者多个PCIE端口(port),它可以根CPU 和memory controller相接,CPU 与 PCIe 总线之间的接口可能包含一系列的组件(处理器接口,DRAM 接口等,甚至是包含多个芯片)将这些组件合起来称这一组的组件为根组件(Root Complex);或者说分隔PCIE domain和CPU/MEMORY domain。

个人理解:RC在功能上和Switch几乎一样,都是用于将一个PCIE接口拓展成多个PCIE接口,区别是RC集成在芯片内部,并且还会连接内存,类似PCI总线的根桥;

RC 存在于 PCI 树状拓扑的“根部”,代表 CPU 与系统的其余部分通信;但PCIe 协议规范并没有对 RC 进行严格定义,而是给出了一个 RC 必需功能与可选功能的列表;所以从广义上说,根组件可以被理解为系统 CPU 与 PCIe 拓扑之间的接口,这个 PCIe 端口即是 RC,在配置空间中被标记为“根端口”。

——不同处理器的RC设计并不相同,只有x86才存在PCIe总线规范定义的“标准RC”,而其它很多处理器并不存在真正意义上的RC,而只是PCIe总线控制器。

——RC与HOST主桥并不相同,RC除了完成地址空间的转换之外,还需要完成物理信号的转换(举个栗子:FSB信号协议与PCIe总线的电气特性不兼容,总线事务也不同,必须进行信号协议和总线事务的转换)。

2、Switch

提供了扇出以及聚合能力:使得单个 PCIe 端口上可以连接更多的设备,它作为数据包路由器的角色,可以根据所给数据包的地址或者其他路由信息来识别这个数据包要走哪条路径;

Switch有一个上游端口和两个或者两个以上的下游端口。上游端口是RC或者上游Switch的下游端口。

3、EP(endpoint)

EP就是终端设备,为从模式,没有转发数据的功能;

EP有三种: legacy EP,PCIE EP,RC integrated EP。

Legacy EP:就是PCI device

PCIE EP:

RC integrated EP:集成在RC内部的EP。

4、PCIE bridge

PCIE bridge就是PCI-to-PCI/PCI-X bridge。

提供了一个通往其他总线的接口。现在使用PCI总线的场景应该已经不多,不做扩展分析。

PCI的EP和RC分别对应从模式和主模式,普通的PCI RC主模式可以用于连接PCI-E以太网芯片或PCI-E的硬盘等外设。RC模式使用外设一般都有LINUX 驱动程序,安装好驱动基本都能正常使用。但是对于SOC芯片本身能做EP有能做RC 两者如何互相通信可能就需要对PCIE的使用和基本原理有所了解才能较好的使用。

二、PCIe 参考时钟架构

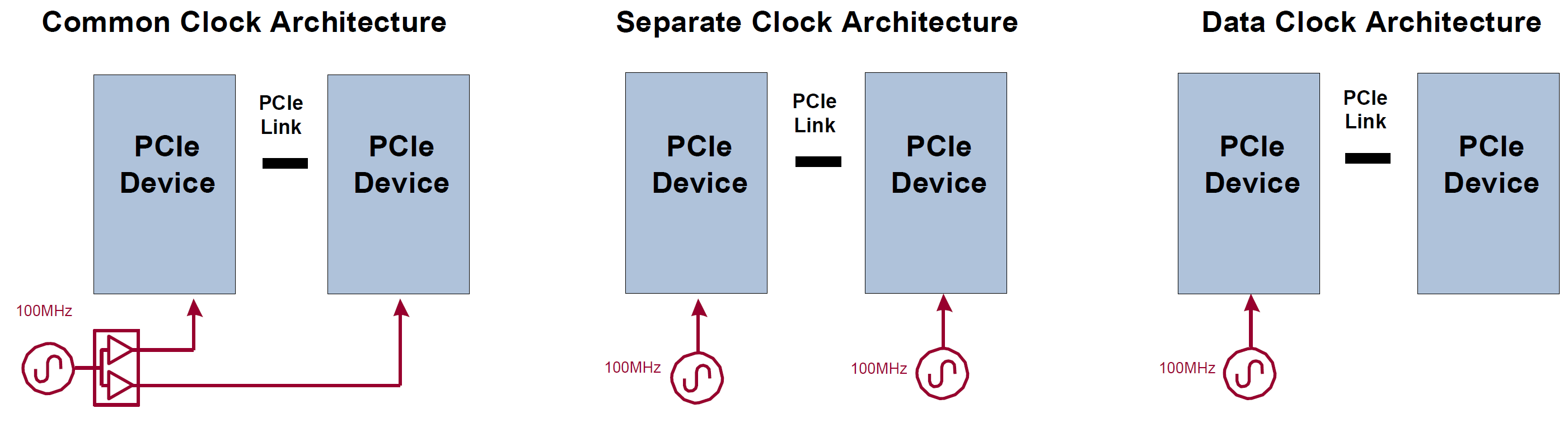

接着上图的架构,我们来简单看下PCIE时钟的三种架构:

1. Common Clock Architecture (即常说的CC架构);

2. Separate Clock Architecture;

3. Data Clock Architecture;

开聊之前先梳理几个概念:

- Jitter,时钟抖动,是对于同一 Clock 而言的, 是时钟源引起的,用来描述被测时钟与理想时钟在时域的偏差(单位为 ps RMS,皮秒均方根)。

- Skew,时钟偏斜,是对于多个时钟线而言的,是时钟树不平衡引起的。

- 此外还有一个概念是频率稳定性,用来描述被测时钟频率与理想时钟频率的偏差(单位 ppm,百万分之一)。

- Refclk Architecture是指 PCIe 系统中收发端设备给定参考时钟的方案。

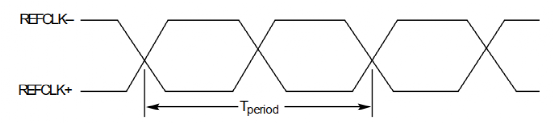

参考时钟

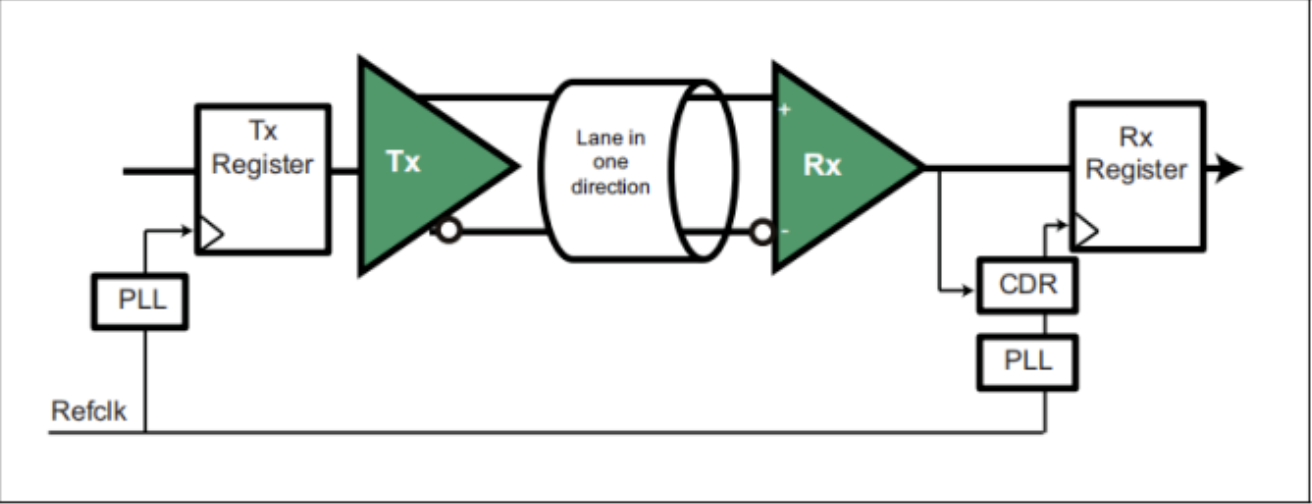

PCIe Serdes 在时钟驱动下收发串行数据流。Serdes 所用时钟由 PHY 内的 PLL 生成,PLL 的参考时钟由外部提供或从接收数据流中恢复出来。

PCIe 协议指定标准的参考时钟为 HCSL 电平的 100 MHz 时钟,Gen1~Gen4 下要求收发端参考时钟精度在 ±300 ppm 以内,Gen5 要求频率稳定性 ±100 ppm。在 FPGA 应用中,为了兼顾其他 IP,采用 LVCMOS/LVDS/LVPECL 电平 125 MHz/250 MHz 的方案也较为常见。

关于参考时钟详细参数需求,已经测试测量等相关内容,本文将不会涉及,具体请参考PCIe CEM Spec和2.0或以上版本的PCIe Base Spec中的相关章节。

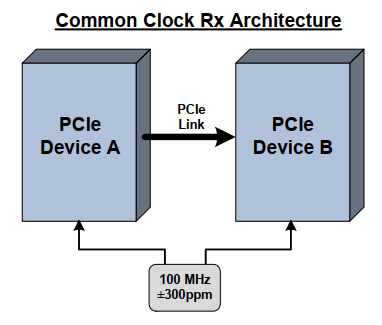

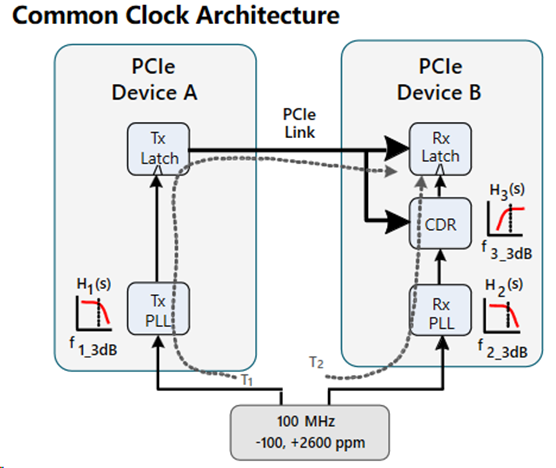

1. Common Refclk Architecture

即同源参考时钟架构,PCIe收发设备共用一个时钟源,PCIe链路的RC和EP都使用同一个参考时钟源发出的时钟,是目前是使用最为广泛的方案,也是Spec推荐使用的,三种 PCIe 参考时钟架构中,Common Clock 是最为常用的一种时钟架构。

对于适用同一 Common Clock 作为参考时钟的 PCIe 设备,所有设备的参考时钟分布必须匹配到15英寸以内在系统板上。在接收端数据和时钟之间的传输延迟增量(时钟偏斜(Clock Skew))必须要小于等于12ns。通常允许PCIE卡上的时钟线长不大于4inch。特别注意这点,涉及到我们实际PCB走线。这无疑对大型电路板上或跨板的 PCIe 设备间布局布线形成巨大挑战。

采用 Common Clock 支持时钟扩频(SSC, Spread Spectrum Clock) 且对参考时钟的要求不如 Separate Clock 方案严苛。

即使系统使用了带有扩频的参考时钟源,时钟抖动也只有-300~+2800ppm,对于频率稳定性的要求是 ±300 ppm。这对于物理层中的RxCDR和TxPLL就比较友好了,可以降低RxCDR和TxPLL的复杂程度,达到节约成本的目的。

其次,当PCIe链路处于L0s或者L1状态时,即使链路上没有数据流,RxCDR依然可以设计出保持锁定的状态,这样做的好处是,链路从L0s或L1状态恢复到L0状态的时间将会更短。

缺点:

对于适用同一 Common Clock 作为参考时钟的 PCIe 设备,所有设备间的时钟偏斜(Clock Skew)必须保持在一定范围内(有部分文章介绍是12ns,我目前还没找到数据来源),大型电路板设计或者跨板的PCIe设备布局布线存在很大挑战。

优点:

·收发侧的时钟抖动jitter都是相同的,因此便于跟踪和计算

·在此架构中,支持SSC功能,很容易达到600 ppm的指标

·即使收发端进入L0S和L1低功耗状态,refclk仍然是可用的,即使在缺少bit流提供数据边沿(in the absence of a bit stream to supply the edges in the data)的情况下,接收器的CDR仍然能够保持恢复时钟的平衡,有效阻止了本地PLL的偏移,相对于其他时钟方案,恢复到L0状态所需时间最少。

总结:Common Refclk Architecture 稳定性好,支持SSC,是目前应用最广泛的参考时钟方案,也是最推荐的设计方案。

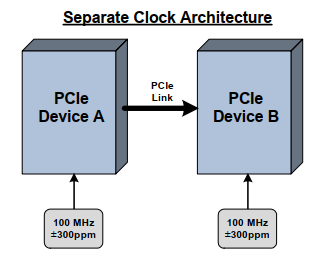

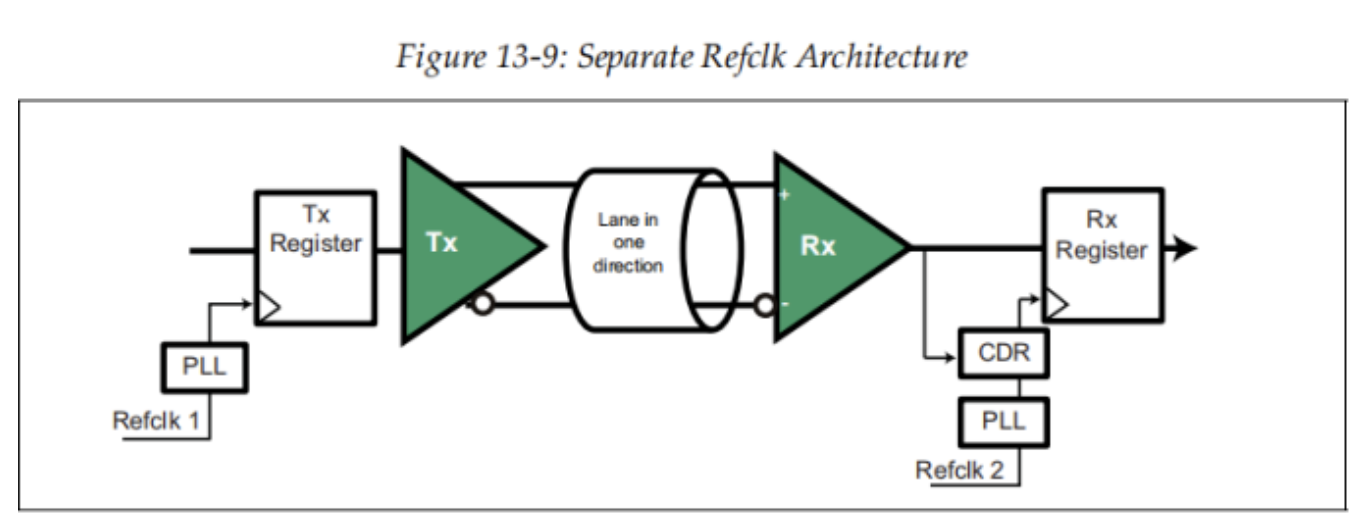

2.Separate Clock Architecture

即独立参考时钟架构,收发端采用独立的参考时钟。 PCIe Spec强烈不推荐使用这种参考时钟架构,尽管这是其提出的三种参考时钟架构之一。PCIe链路的RC和EP使用独立的参考时钟。

两个独立时钟需要满足PCIe协议中规定的精度要求。

PCIe Spec强调,如果使用这种架构,扩频时钟必须被禁止使用(2.5GT/s & 5GT/s),因为这中情况下使用扩频时钟的话,CDR的带宽需甚至需要大于5600ppm,这对于CDR来说是非常大的挑战。

对于收发端采用独立参考时钟的方案,其收发端独立使用不同的参考时钟源,无需单独传递时钟,对布局布线的要求更宽松。SRNS 允许 ±300 ppm (600ppm),而 SRIS 允许 ±2800 ppm (5600 ppm,其中SSC允许 5000ppm,TX/RX允许 600 ppm)。

根据有无 SSC 可进一步分为 SRNS ( Separate Refclk with No SSC) 及 SRIS (Separate Refclk with Independent SSC)。

SRNS:不使用SSC功能,时钟抖动更小,不需要额外加大弹性缓存(Elastic Buffer)的深度

SRIS: 使用SSC功能,能够有效减少电磁干扰(EMI),但是时钟抖动增加,需要额外加大弹性缓存(Elastic Buffer)的深度。

相对于SRNS,SRIS:开启了SSC,接收侧观察到的时钟抖动会加大,因此发生SKP的频率会增加,因此在物理层需要加大弹性缓存(Elastic Buffer)的深度,用于消除开启SSC的负面影响。但是弹性缓存(Elastic Buffer)深度加大后,数据传输路径延时也增加了。

若 PCIe 设备开启了 SRIS,其发生 SKP 的频率应该加大,同时加大弹性缓存(Elastic Buffer)的深度。弹性缓存加大使得延时更大,在一定程度上降低了 performance。对于一条 PCIe 链路,如何知道要不要采用 SRIS 呢?遗憾的是,目前尚没有机制实现收发端之间的 SRIS 协商。

需要注意的是,PCIe Base Spec V3.x中,提到对于8GT/s的PCIe链路而言,在Separate Refclk Architecture下实现扩频时钟也是可行的(即Separate Refclk With Independent SSC (SRIS) Architecture),但是需要更复杂的CDR设计,具体请参考Spec相关章节。

优点:参考时钟独立,参考时钟不需要穿越背板和连接器,从而使PCB设计变得更为简单,使得架构更加的灵活。

缺点:接收侧观察到的时钟抖动(jitter)是两端参考时钟jitter的组合,并且不利于计算,使得参考时钟的设计更加严格。在此模式下,支持SSC模式对设计提出了更高的要求,例如物理层CDR设计更加复杂,物理层需要更大的缓存。

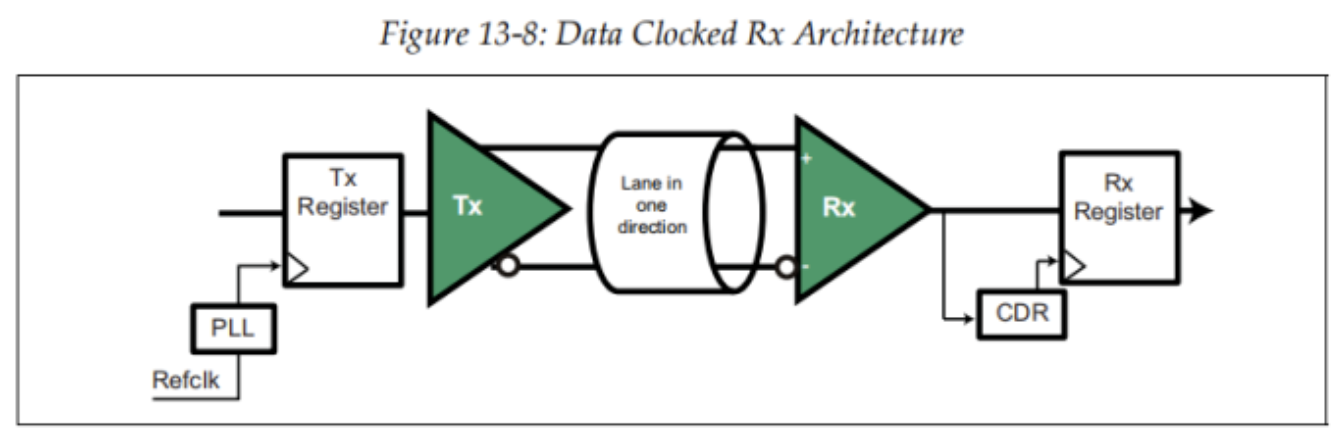

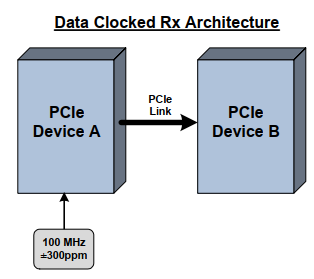

3.Data Clock Architecture

即数据时钟参考时钟架构,仅发送端需要 Refclk,接收端无需外部 RefClk,接收端物理层从数据流中恢复出时钟提供给 CDR(Clock Data Recovery,时钟数据恢复)作为参考时钟。

这种参考时钟架构最为简洁,也是三种方案中最易实现的方案。Rx端器件的CDR并不需要外部参考时钟,而是直接从数据流中恢复出时钟。

Data Clocked Refclk Architecture在PCIe2.0中首次,PCIe3.0中保留了这项技术,该方案仅适用于 Gen2 及 Gen3,单 lane 单向最高速率 8GT/s。但是在PCIe4.0又丢弃了。因此不推荐使用,慎用,有些不支持。

不过这种结构的RxCDR几乎很少在FPGA的SerDes中使用,因为在没有外部参考时钟的协助下,CDR实现锁定都是一个很大的挑战,还要保证在5600ppm的抖动范围内不失锁(对于带有扩频时钟的PCIe链路来说)。

注:绝大部分的FPGA SerDes都是多协议SerDes,除了支持PCIe外,往往还需要支持其他主流的串行协议,比如SATA、USB、DisplayPort、HDMI、Ethernet (Q)SGMII、CoaXpress、CPRI、FPD-Link II/III、Serial RapidIO、SLVS-EC等等。这种参考时钟架构对于PCIe来说行得通,对于其他的某些串行协议来说可能是无法实现的。

优点:实现简单,Data Clock 时钟方案是三种方案中最易实现的方案,其无需外部参考时钟

缺点:PCIe4.0 没有保留此方案,不推荐使用。

注意,虽说PCIE时钟有三种架构,但是最常用的还是CC架构,无特殊情况,不要使用其他时钟架构,如果真的要使用其他两种架构,也需要严谨评估先。

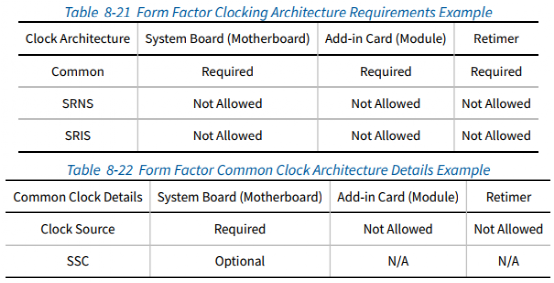

从下表可知,展频跟非CC架构慎用。

鉴于PCIE时钟要求多且复杂的,故此文章给出主要的参数要求,其它详细的要求以及测试方法,后续有机会再编写分享。

信号要求:

PCIE_CLK_P/N是差分信号,通常差分阻抗为100Ω,少部分要求85Ω。

电平:HCSL or LP-HCSL。

频率:100±0.03MHz。

频率稳定度:±300ppm,越小越好。

占空比:50%±10%。

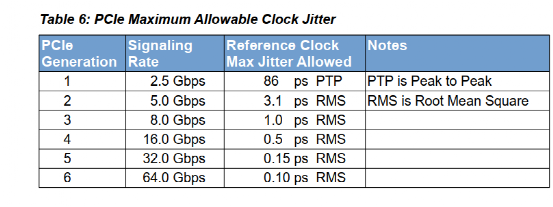

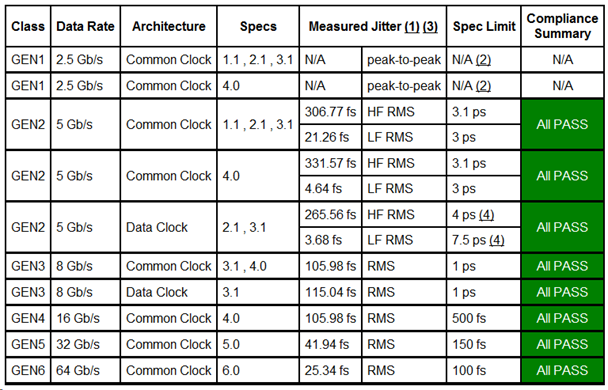

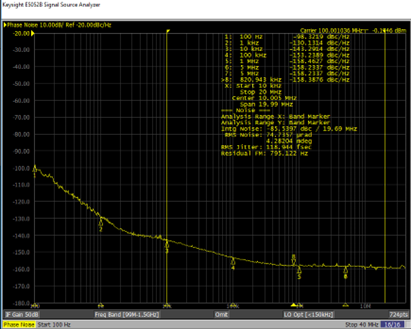

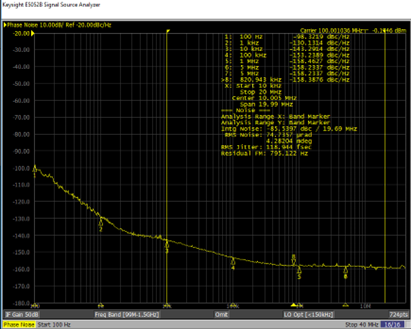

抖动:如下CC模式的要求:

注意:上图给出的是CC时钟架构下的抖动要求;仿真PCIE4.0时候,抖动是按照0.7ps RMS来的;仿真PCIE5.0时候,抖动是按照0.25ps RMS来的;因为标准考虑了实际系统中的额外噪声,故会比较严格。

提到PCIE时钟,相信大部分人会联想到CLKREQ#:

很多时候有疑问,CLKREQ#是否要接,首先要知道的是,这个信号是可选的,可要可不要。那么什么时候需要呢?如果要支持L1-PM子状态(ASPM(Active State Power Management)中的状态)和/支持时钟电源管理,那么这个信号就是必要的(即使你不是使用的CC模式)。

注意:如果硬件电路这个CLKREQ#没接的话,可让BIOS把PCIE中的ASPM的L1状态默认关闭,不然容易出现异常现象。

扩频时钟

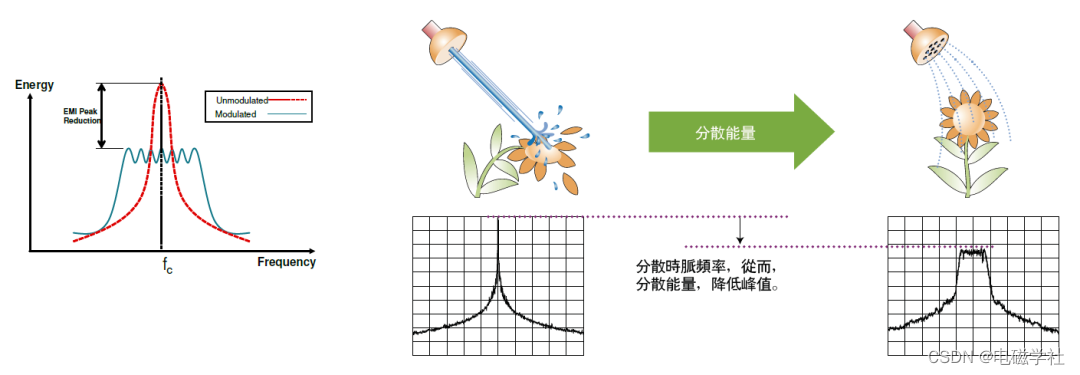

什么是SSC?展频时钟全称Spread Spectrum Clocking 。

顾名思义是一种对时钟频率进行调制以削平时钟产生的峰值能量的技术,可降低由时钟基频及其谐波信号产生的EMI尖峰,从而优化系统EMC结果(含传导与辐射骚扰);

由于信号的能量过于集中在其载波频率位置,导致信号的能量在某一频点位置处的产生过大的辐射发射。为了有效地降低EMI辐射,芯片厂家在设计芯片时也给容易产生EMI的信号增加了SSC扩频时钟的功能,频率变化的时钟,其频谱能量被分散在一定频谱范围上。当前PCIE、SATA、SAS、USB3.0等高速芯片都支持SSC的功能。采用SSC的功能可以有效的降低信号所产生的EMI。

关于SSC,SSC是一种缓慢调制时钟频率的技术,以便降低中心频率处的EMI发射,有了SSC,PCIe时钟的辐射能量就不会产生2.5GHz或5GHz的噪声尖峰信号,因为辐射被分散到中心频率周围的小频率范围上。SSC在减少电磁干扰峰化方面起着非常重要的作用,因此可以简化符合系统电磁辐射限制的工作。

展频的基本原理是通过将窄带信号转换为宽带信号,将能量分散在一定的宽频范围内,从而降低EMI的影响,如下图所示。

扩频时钟可以抑制电磁干扰(EMI)。随着PCIe的速率不断上升,对SSC的需求由不明显逐渐变得迫切,但伴随PCIe速率的增长对时钟精度的要求也在增长。通过背板或线缆长距离传输一个高精度时钟是很困难的。为了降低 PCIe 时钟及数据线的电磁辐射、增强高速数据传输可靠性,PCIe 时钟可以采用 SSC 对参考进行时钟扩频。

如果是采用独立的参考时钟,如果只有一端采用展频,或两个时钟同时展频,两个时钟的精度就很难控制。所以在PCIe Gen1,Gen2上,都限制了只有在共同时钟模式下才能使用SSC。这种情况实际限制了SSC的使用。

于是Separate Refclk Independent SSC(SRIS):独立参考时钟的PCIe展频技术在Gen3中被提出。但一般认为这个功能在Gen3不成熟,实际不可用,正式实施要等到Gen4或Gen5。Gen1~Gen5 都支持 SSC,但只有 Gen3 及以上支持 SRIS。

PCIe 扩频模式为向下扩频,扩频范围为-0.5%~0%,确保最大频率在标称频率之下。最大调制幅度为 -0.5%!调制频率为 30 KHz ~ 33 KHz,确保 PLL 能够跟得上,同时减小音频噪声的引入。调制波形采用三角波,该波形易于实现,且调制后的频谱接近均匀分布。注意:30 KHz ~ 33 KHz 是指频率随时间周期变化的频率,不是展宽的带宽,带宽为时钟频率的 0.5% 。

扩频时钟对于PCIe来说是可选的,并非是强制的。如果选择支持扩频时钟的话,需满足以下要求:

※ 调制范围为+0%到-0.5%,即向下扩频(Down Spreading),如下图所示

※ 调制频率必须在30KHz到33KHz,一般为三角波

※ 参考时钟源的抖动(Jitter)需在300ppm以内

带有SSC的参考时钟频率变化曲线如下图所示:

注:为什么选用的是向下扩频,而不是中心扩频或者向上扩频?主要是考虑到,当100MHz已经是系统最靠基准频率的话, 向上扩频或者中心扩频会导致系统基准频率超过最高值,进而可能引发系统工作异常。

注:三角波的能力较为集中在低次谐波中,相比于正弦波,方波或者锯齿波,更适合用于SSC中。

PCIe CC架构

更多扩频相关介绍,请查看参考资料:http://blog.chinaaet.com/justlxy/p/5100064134。

三、PCIe时钟实现方法和参考设计

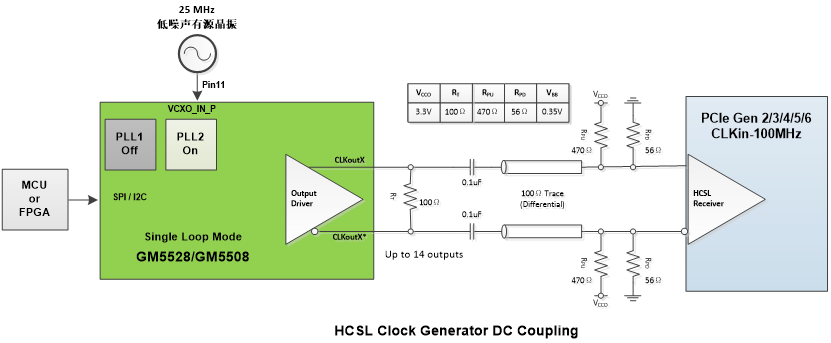

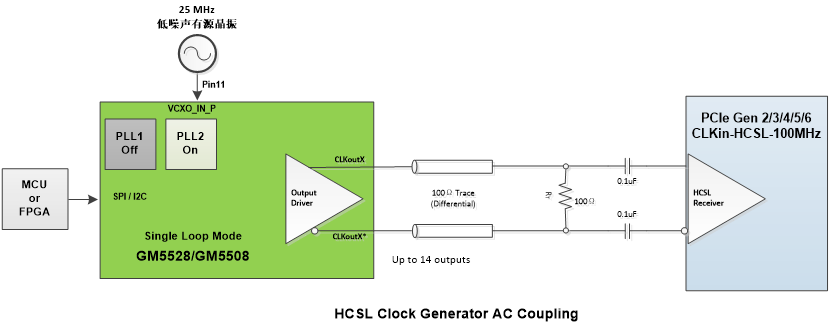

1.使用有容微GM5528或GM5508时钟清抖器/时钟产生器芯片输出HCSL 100MHz时钟

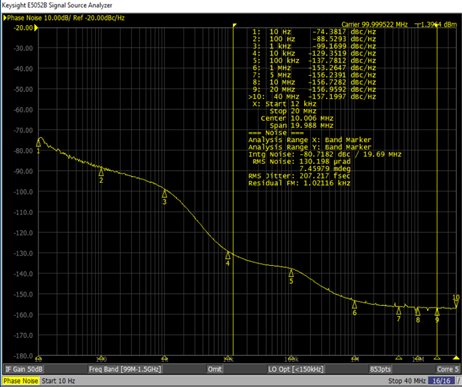

GM5528/GM5508输出HCSL 100MHz时钟的相噪/抖动测试

GM5528/GM5508输出HCSL 100MHz 抖动数据 vs PCIe时钟标准要求

可见:GM5528/GM5508输出的HCSL 100MHz时钟符合PCIe Gen1/2/3/4/5/6 (CC)标准

(*说明:GM5528支持多达14路输出,GM5508支持多达8路输出)

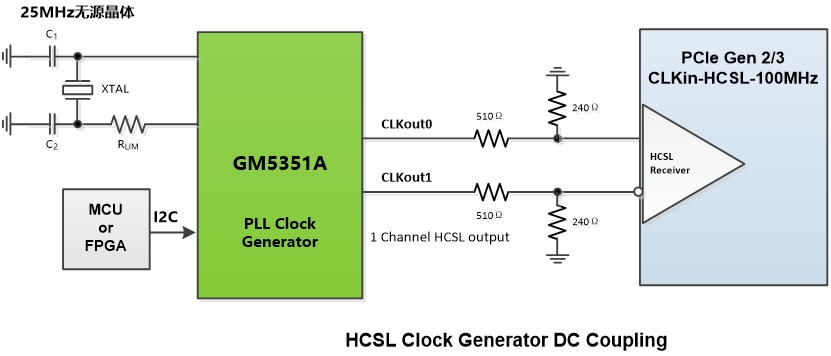

2.使用有容微GM5351A时钟产生器芯片输出HCSL 100MHz时钟

GM5351A时钟产生器芯片本身是3路2.5KHz-250MHz之间任意频率的单端输出,但是可以使用双通道(一般使用CLKout0和CLKout1,因为这两路输出PIN脚相邻便于设计)做反相配置实现HCSL的差分输出,且达到PCIe Gen2/Gen3标准:

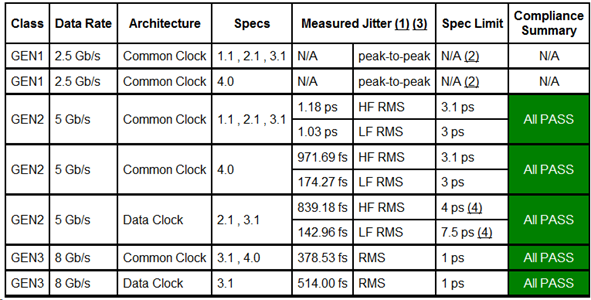

GM5351A输出HCSL 100MHz 抖动vs PCIe时钟标准要求

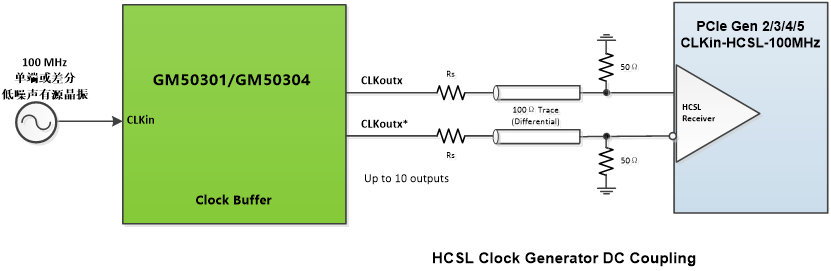

3.使用有容微GM50301/GM50304时钟缓冲器芯片输出HCSL 100MHz时钟

GM50301/GM50304输出HCSL 100MHz抖动测试

相关文章:

PCIE 参考时钟架构

一、PCIe架构组件 首先先看下PCIE架构组件,下图中主要包括: ROOT COMPLEX (RC) (CPU); PCIE PCI/PCI-X Bridge; PCIE SWITCH; PCIE ENDPOINT (EP) (pcie设备); BUFFER; 各个器件的时钟来源都是由100MHz经过Buffer后提供。一个PCIE树上最多可以有256…...

【开源】JAVA+Vue.js实现在线课程教学系统

目录 一、摘要1.1 系统介绍1.2 项目录屏 二、研究内容2.1 课程类型管理模块2.2 课程管理模块2.3 课时管理模块2.4 课程交互模块2.5 系统基础模块 三、系统设计3.1 用例设计3.2 数据库设计 四、系统展示4.1 管理后台4.2 用户网页 五、样例代码5.1 新增课程类型5.2 网站登录5.3 课…...

复习提纲29)

计算机网络(第六版)复习提纲29

第六章:应用层 SS6.1 域名系统DNS 1 DNS被设计为一个联机分布式数据库系统,并采用客户服务器方式(C/S) 2 域名的体系结构 3 域名服务器及其体系结构 A 域名服务器的分类 1 根域名服务器 2 顶级域名服务器(TLD服务器&a…...

有道ai写作,突破免费限制,无限制使用

预览效果 文末提供源码包及apk下载地址 有道ai写作python版 import hashlib import time import json import ssl import base64 import uuidfrom urllib.parse import quote import requests from requests_toolbelt.multipart.encoder import MultipartEncoder from Crypto…...

node.js 使用 elementtree 生成思维导图 Freemind 文件

请参阅: java : pdfbox 读取 PDF文件内书签 请注意:书的目录.txt 编码:UTF-8,推荐用 Notepad 转换编码。 npm install elementtree --save 编写 txt_etree_mm.js 如下 // 读目录.txt文件,使用 elementtree 生成思维导图 Free…...

Vue中路由守卫的详细应用

作为一名web前端开发者,我们肯定经常使用Vue框架来构建我们的项目。而在Vue中,路由是非常重要的一部分,它能够实现页面的跳转和导航,提供更好的用户体验。然而,有时我们需要在路由跳转前或跳转后执行一些特定的逻辑&am…...

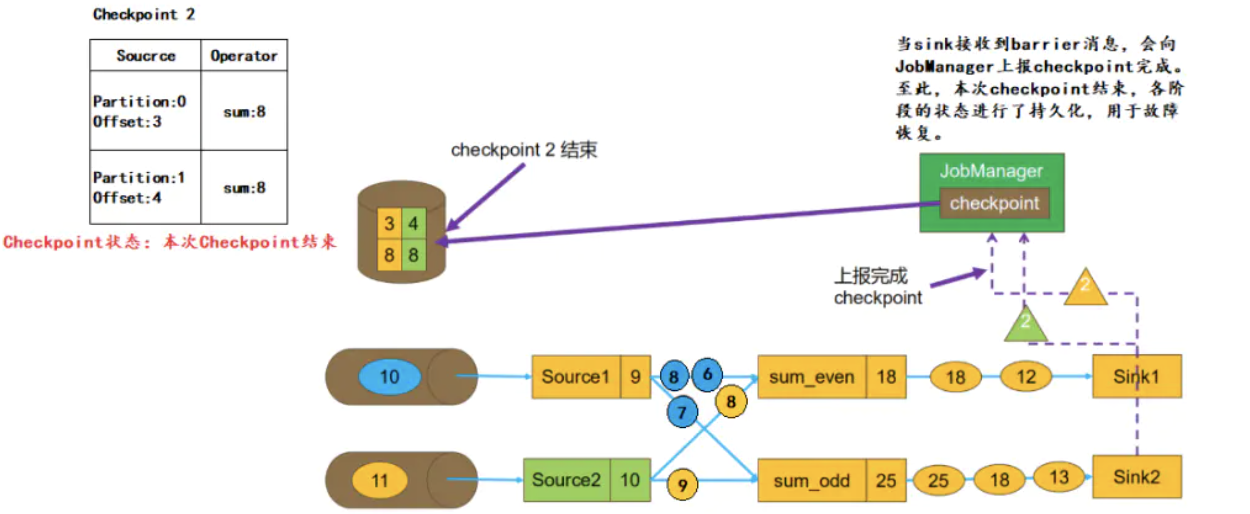

Flink Checkpoint过程

Checkpoint 使用了 Chandy-Lamport 算法 流程 1. 正常流式处理(尚未Checkpoint) 如下图,Topic 有两个分区,并行度也为 2,根据奇偶数 我们假设任务从 Kafka 的某个 Topic 中读取数据,该Topic 有 2 个 Pa…...

【Java程序代理与系统代理关系】Java程序代理与系统代理关系优先级及覆盖关系

前言 使用Apache HttpClient工具包中的HttpClients.createDefault()方法创建的默认HTTP客户端会根据操作系统当前的设置来决定是否使用代理。 具体来说,当创建默认HTTP客户端时,它会检查系统的代理设置。如果操作系统当前设置了系统级代理,…...

MQ,RabbitMQ,SpringAMQP的原理与实操

MQ 同步通信 异步通信 事件驱动优势: 服务解耦 性能提升,吞吐量提高 服务没有强依赖,不担心级联失败问题 流量消峰 小结: 大多情况对时效性要求较高,所有大多数时间用同步。而如果不需要对方的结果,且吞吐…...

Vue 3 + Koa2 + MySQL 开发和上线部署个人网站

Vue 3 Koa2 MySQL 开发和上线部署个人网站 记录个人的一个操作步骤, 顺序不分先后, 嫌啰嗦请出门右转! 环境说明: 服务器: 阿里云轻量应用服务器 服务器系统: CentOS8.2 本地环境: macOS 12.7.2 Node: 20.10.0 MySQL: 8.0.26 Vue: 3.3.11 Koa: 2.7.0 pm2: 5.3.1 Nginx: 1.1…...

uniapp踩坑之项目:简易版不同角色显示不一样的tabbar和页面

1. pages下创建三个不同用户身份的“我的”页面。 显示第几个tabbar,0是管理员 1是财务 2是司机 2. 在uni_modules文件夹创建底部导航cc-myTabbar文件夹,在cc-myTabbar文件夹创建components文件夹,在components文件夹创建cc-myTabbar.vue组件…...

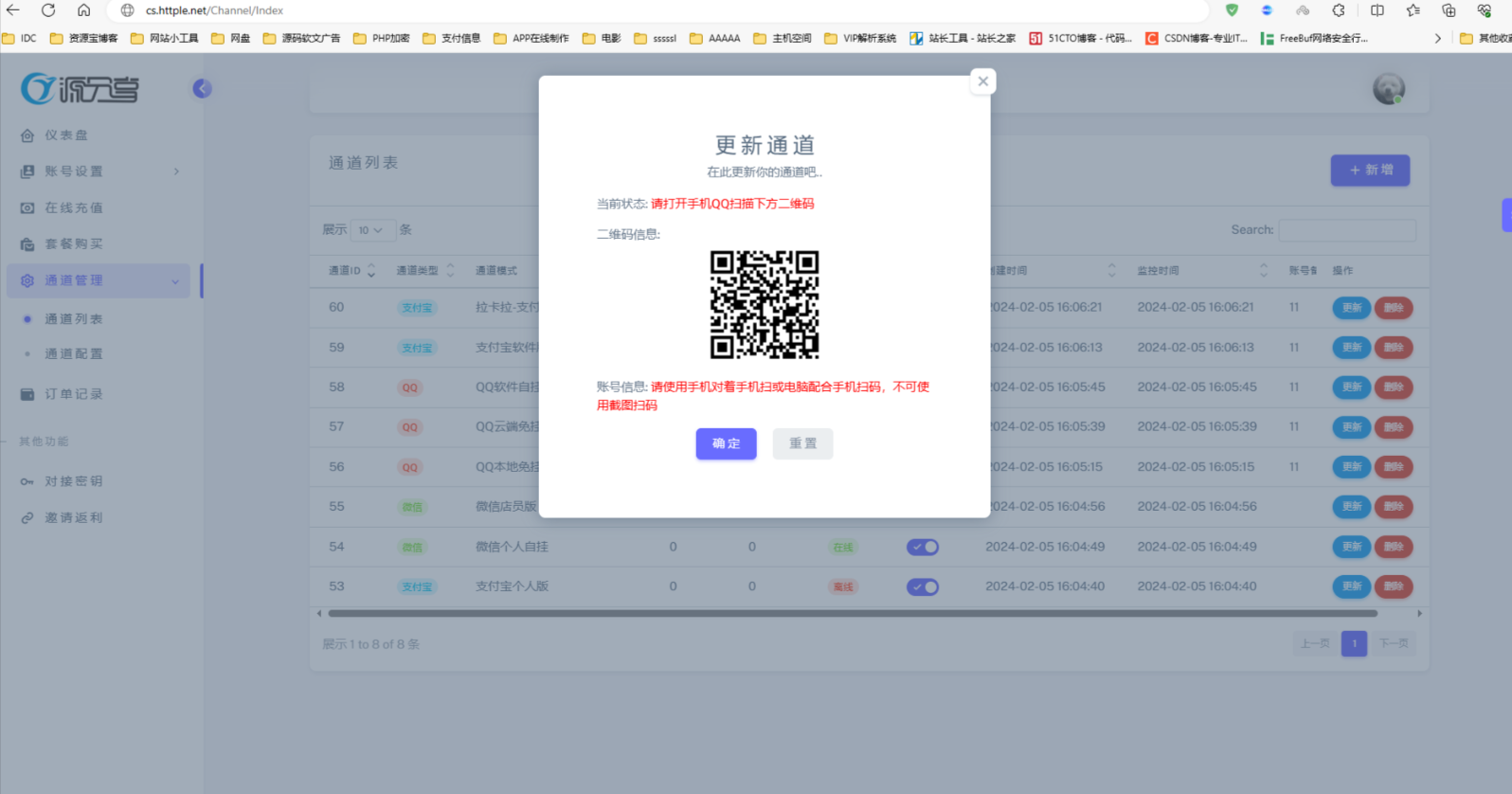

源支付V7开心1.9修复版,非网络上泛滥不能那种

源支付V7开心1.9修复版,非网络上泛滥不能那种 修复版源码,非网络泛滥版,防止源码泛滥,会员专属源码, 本站会员免费下载所有资源 注:开发不易,仅限交流学习使用,如商业使用,请支持正…...

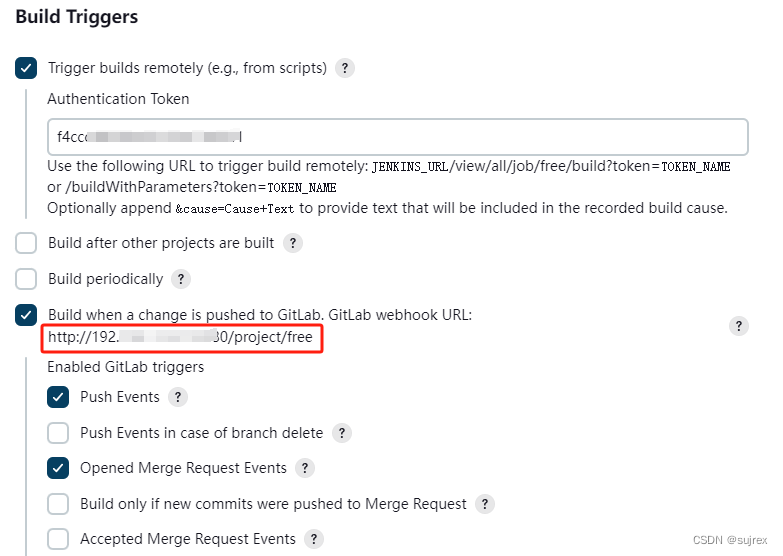

Gitlab和Jenkins集成 实现CI (二)

Gitlab和Jenkins集成 实现CI (一) Gitlab和Jenkins集成 实现CI (二) Gitlab和Jenkins集成 实现CI (三) 配置Gitlab api token 配置 Gitlab 进入gitlab #mermaid-svg-t84fR8wrT4sB4raQ {font-family:"trebuchet ms",verdana,arial,sans-serif;font-size:16px;fill:…...

Java:内部类、枚举、泛型以及常用API --黑马笔记

内部类 内部类是类中的五大成分之一(成员变量、方法、构造器、内部类、代码块),如果一个类定义在另一个类的内部,这个类就是内部类。 当一个类的内部,包含一个完整的事物,且这个事物没有必要单独设计时&a…...

【持续更新】2024牛客寒假算法基础集训营3 题解 | JorbanS

A - 智乃与瞩目狸猫、幸运水母、月宫龙虾 string solve() {string a, b; cin >> a >> b;if (isupper(a[0])) a[0] a - A;if (isupper(b[0])) b[0] a - A;return a[0] b[0] ? yes : no; }B - 智乃的数字手串 string solve() {cin >> n;int cnt 0;for (…...

Java基于微信小程序的驾校报名小程序,附源码

博主介绍:✌程序员徐师兄、7年大厂程序员经历。全网粉丝12w、csdn博客专家、掘金/华为云/阿里云/InfoQ等平台优质作者、专注于Java技术领域和毕业项目实战✌ 🍅文末获取源码联系🍅 👇🏻 精彩专栏推荐订阅👇…...

Android中AGP与Gradle、AS、JDK的版本关系

文章目录 AGP版本所要求的Gradle、JDK、SDK Build Tools最小版本Android Studio所要求的AGP最小版本 本文介绍了 在Android开发中由于AGP与gradle、JDK、AS等版本不匹配导致的编译失败问题屡见不鲜,尤其是对于新手而言更是叫苦不迭。新手经常遇到拿到别人的工程代码…...

web 前端实现一个根据域名的判断 来显示不同的logo 和不同的标题

1.需求 有可能我做一个后台 web端 我想实现一套代码的逻辑 显示不同的公司主题logo以及内容,但是实际上 业务逻辑一样 2.实现 建一个store oem.ts 这个名为是 oem系统 oem.ts import { defineStore } from pinia;import { store } from /store;const oemDataLis…...

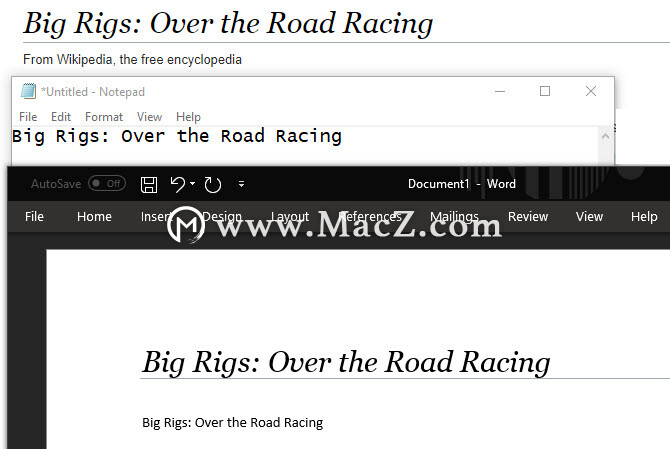

复制和粘贴文本时剥离格式的5种方法(MacWindows)

您可能每天复制和粘贴多次。虽然它是一个非常方便的功能,但最大的烦恼之一就是带来了特殊的格式。从网络上获取一些文本,您经常会发现粘贴到文档中时,它保持原始样式。 我们将展示如何使用一些简单的技巧在不格式化的情况下复制和粘贴。 1.…...

SpringBoot实现即时通讯

SpringBoot实现即时通讯 功能简述 好友管理群组管理聊天模式:私聊、群聊消息类型:系统消息、文本、语音、图片、视频会话列表、发送消息、接收消息 核心代码 package com.qiangesoft.im.core;import com.alibaba.fastjson2.JSONObject; import com.q…...

收藏!小白也能看懂大模型:从入门到实战的AI学习指南

2026年春招中,AI岗位激增12倍,平均月薪超6万元,成为企业争夺焦点。大模型算法、多模态技术等前沿领域人才需求暴涨,AI已从实验室概念进入规模化落地阶段。教育体系面临挑战,需提前培养AI启蒙能力,打破传统专…...

085、命令行工具开发:argparse模块实战笔记

085、命令行工具开发:argparse模块实战笔记 昨天帮同事调试一个数据清洗脚本,问题出在参数解析上。脚本接收三个输入路径,结果他少传了一个参数,程序直接崩溃报“IndexError”。这种体验太糟糕了——用户不知道哪里错了,也不知道该怎么用。这就是为什么我们需要专业的命令…...

3步快速上手:Windows电脑直接安装安卓应用的终极指南

3步快速上手:Windows电脑直接安装安卓应用的终极指南 【免费下载链接】APK-Installer An Android Application Installer for Windows 项目地址: https://gitcode.com/GitHub_Trending/ap/APK-Installer 你是否渴望在Windows电脑上直接运行安卓应用ÿ…...

(orm方式))

python访问sqlite(sqlalchemy)(orm方式)

文章目录sqlalchemy的理解Base declarative_base()的作用?__repr__方法查询db.query()并不是查询,query.count()和query.offset()才是查询?查询-拼接条件分组关联查询新增修改删除安装依赖开始接触sqlalchemy不太习惯,感觉有点抽象。后来换个视角瞬间…...

JAVA:类和对象完全解析

一、编程世界的乐高积木在面向对象编程(OOP)的宇宙中,类(Class)和对象(Object)如同乐高积木的基础模块。如果把程序看作一个虚拟城市,类就是建筑设计图,而对象则是根据图…...

基于MCP协议的学术成果商业化AI管道:从论文到商业机会的自动化桥梁

1. 项目概述:从象牙塔到市场的自动化桥梁看到apifyforge/academic-commercialization-pipeline-mcp这个项目标题,我的第一反应是:终于有人把学术界和产业界之间那道无形的墙,用代码给砌出了一条自动化通道。这个项目本质上是一个“…...

Book118文档下载器:3步免费获取完整PDF文档的终极指南

Book118文档下载器:3步免费获取完整PDF文档的终极指南 【免费下载链接】book118-downloader 基于java的book118文档下载器 项目地址: https://gitcode.com/gh_mirrors/bo/book118-downloader 你是否曾在Book118网站上找到急需的学习资料,却发现需…...

5分钟快速上手:FigmaCN免费中文界面插件终极指南

5分钟快速上手:FigmaCN免费中文界面插件终极指南 【免费下载链接】figmaCN 中文 Figma 插件,设计师人工翻译校验 项目地址: https://gitcode.com/gh_mirrors/fi/figmaCN 还在为Figma的英文界面而烦恼吗?想要专注于设计创意却被语言障碍…...

DeepSeek总结的DwarfStar 4:专为 DeepSeek V4 Flash 设计的小型原生推理引擎

来源:https://github.com/antirez/ds4 DwarfStar 4 DwarfStar 4 是一个为 DeepSeek V4 Flash 设计的小型原生推理引擎。它是有意限定了范围的:不是通用的 GGUF 运行器,不是其他运行时的封装器,也不是一个框架。其主要路径是一个…...

2026届必备的六大AI辅助写作网站横评

Ai论文网站排名(开题报告、文献综述、降aigc率、降重综合对比) TOP1. 千笔AI TOP2. aipasspaper TOP3. 清北论文 TOP4. 豆包 TOP5. kimi TOP6. deepseek 现今,各类数字化内容的AI生成痕迹核验标准不断持续迭代,多数内容创作…...