vivado RAM HDL Coding Guidelines

从编码示例下载编码示例文件。

块RAM读/写同步模式

您可以配置块RAM资源,为提供以下同步模式给定的读/写端口:

•先读取:在加载新内容之前先读取旧内容。

•先写:新内容立即可供阅读先写也是众所周知的如通读。

•无变化:数据输出不会随着新内容加载到RAM而变化。

Vivado合成为所有这些同步模式提供了推理支持。你可以描述了用于RAM的每个端口的不同同步模式。

分布式RAM示例

以下部分提供了分布式RAM的VHDL和Verilog编码示例。

具有异步读取编码的双端口RAM Verilog示例

单端口块RAM

以下部分提供了单端口块RAM的VHDL和Verilog编码示例。

带可重置数据输出的单端口块RAM(Verilog)

相关文章:

vivado RAM HDL Coding Guidelines

从编码示例下载编码示例文件。 块RAM读/写同步模式 您可以配置块RAM资源,为提供以下同步模式给定的读/写端口: •先读取:在加载新内容之前先读取旧内容。 •先写:新内容立即可供阅读先写也是众所周知的如通读。 •无变化&…...

springboot/ssm甘肃旅游服务平台Java在线旅游规划管理系统

springboot/ssm甘肃旅游服务平台Java在线旅游规划管理系统 开发语言:Java 框架:springboot(可改ssm) vue JDK版本:JDK1.8(或11) 服务器:tomcat 数据库:mysql 5.7&am…...

第三百五十四回

文章目录 1. 概念介绍2. 使用方法2.1 获取所有时区2.2 转换时区时间 3. 示例代码4. 内容总结 我们在上一章回中介绍了"分享一些好的Flutter站点"相关的内容,本章回中将介绍timezone包.闲话休提,让我们一起Talk Flutter吧。 1. 概念介绍 我们在…...

【Funny Game】 吃豆人

目录 【Funny Game】 吃豆人 吃豆人 文章所属专区 Funny Game 吃豆人 吃豆人,这款经典游戏如今依旧魅力四射。玩家需操控小精灵,在迷宫内吞噬所有豆子,同时避开狡猾的鬼怪。当吃完所有豆子后,便可消灭鬼怪,赢得胜利。…...

PyCharm - Run Debug 程序安全执行步骤

PyCharm - Run & Debug 程序安全执行步骤 1. Run2. DebugReferences 1. Run right click -> Run ‘simulation_data_gene…’ or Ctrl Shift F10 2. Debug right click -> Debug ‘simulation_data_gene…’ 在一个 PyCharm 工程下,存在多个 Pytho…...

作为一个程序员,最少要看过这几部电影吧?

计算机专业必看的几部电影 计算机专业必看的几部电影,就像一场精彩的编程盛宴!《黑客帝国》让你穿越虚拟世界,感受高科技的魅力;《社交网络》揭示了互联网巨头的创业之路,《源代码》带你穿越时间解救世界,…...

备战蓝桥杯 Day4

目录 注意:递推开long long 1140:验证子串 1131:基因相关性 1176:谁考了第k名 1177:奇数单增序列 1180:分数线划定 1184:明明的随机数 1185:单词排序 1186:出现…...

用HTML和CSS打造跨年烟花秀视觉盛宴

目录 一、程序代码 二、代码原理 三、运行效果 一、程序代码 <!DOCTYPE html> <html lang"en"><head><meta charset"UTF-8"><title>跨年烟花秀</title><meta name"viewport" content"widthdevi…...

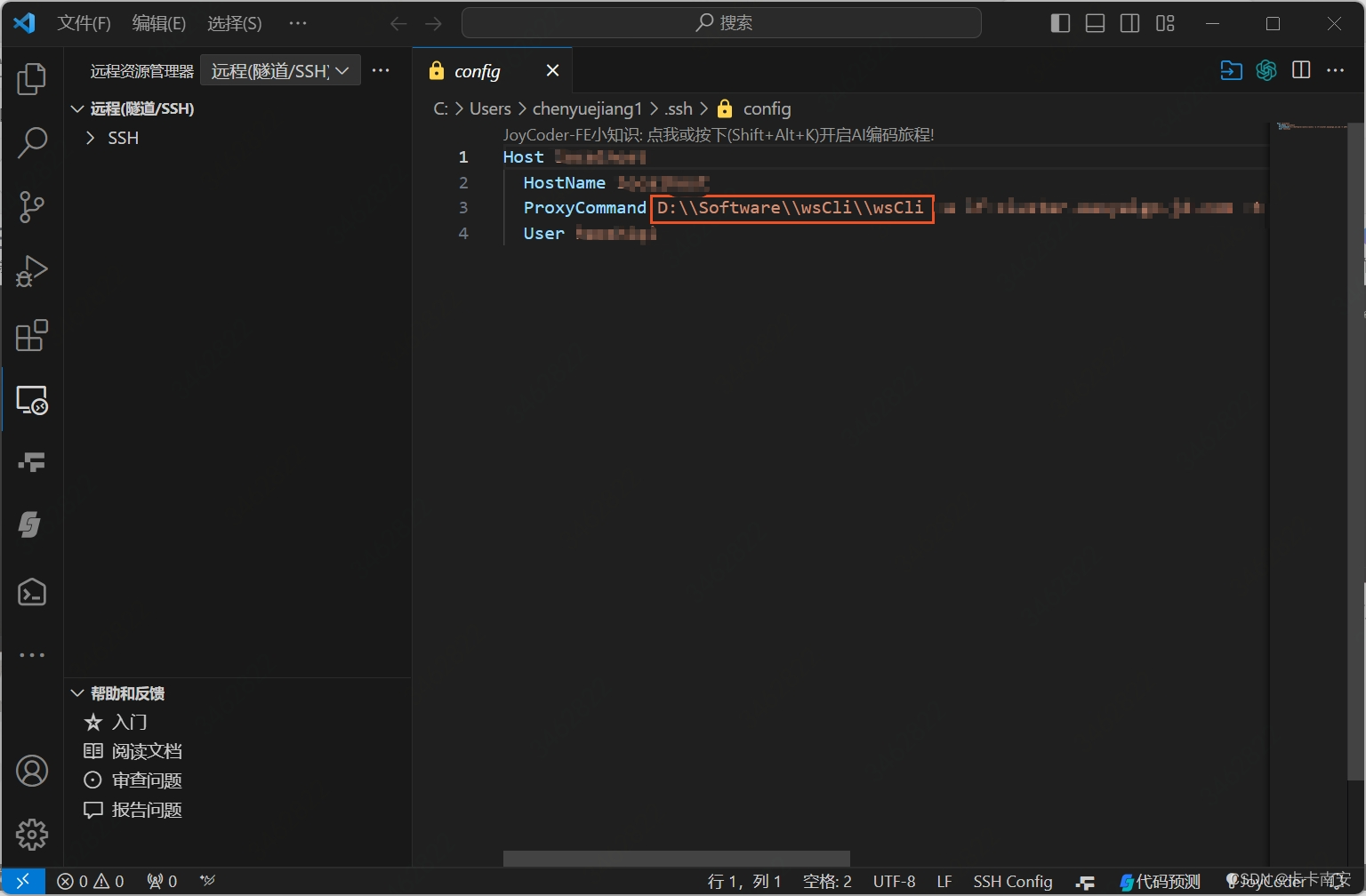

SSH密钥认证登陆流程(Vscode连接到远程)

目录 前言连接远程步骤1. 下载工具包wsCli到本地机器2. 本地机器上生成ssh密钥3. 在服务器上安装公钥4. vscode连接到远程 参考资料 前言 SSH(Secure Shell)是一种用于远程登录和安全传输数据的网络协议。它提供了两种主要的远程连接方式: 密…...

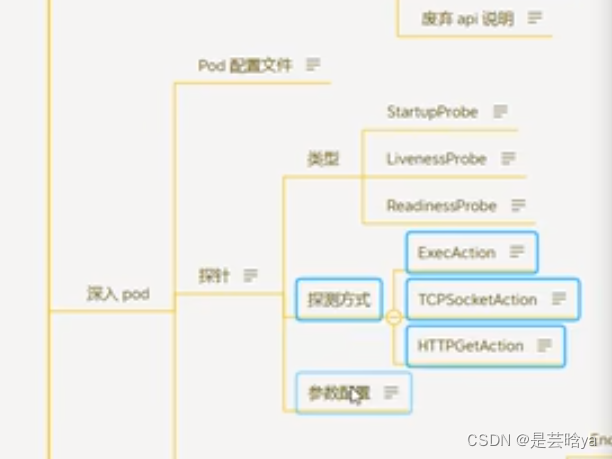

k8s进阶之路-pod探针:容器内的监控机制,检测应用是否存活

配合Pod重启策略: RestartPolicy 应用程序是否启动完成: 3.startupProbe启动探针1.16:排他性 如果三个都配置了,会优先启动,会禁用前两个反馈成功后,才会启动以下两个 应用启动成功后: 1.L…...

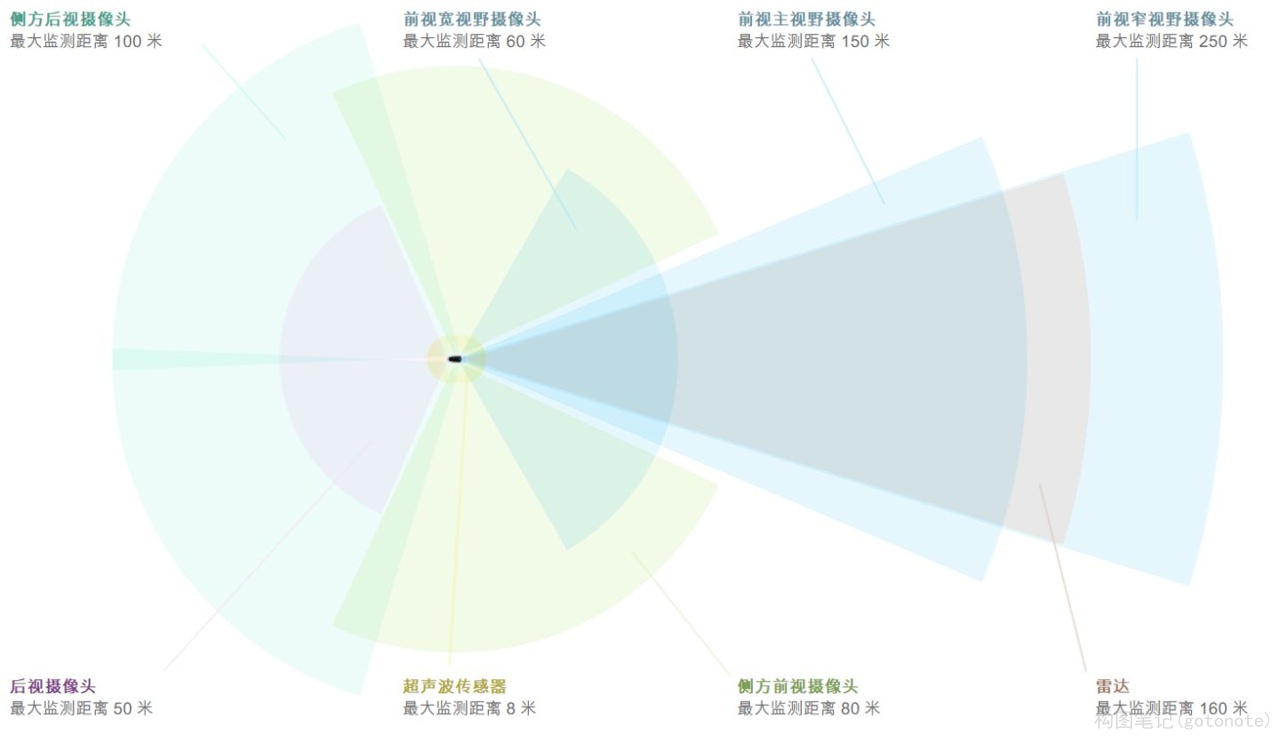

2.1.1 摄像头

摄像头 更多内容,请关注: github:https://github.com/gotonote/Autopilot-Notes.git 摄像头是目前自动驾驶车中应用和研究最广泛的传感器,其采集图像的过程最接近人类视觉系统。基于图像的物体检测和识别技术已经相当成熟&#…...

linux安装mysql8且初始化表名忽略大小写

mysql8下载地址 MySQL8.0安装步骤 1、把安装包上传到linux系统,解压、重命名并移动到/usr/local/目录: cd ~ tar -xvf mysql-8.0.32-linux-glibc2.12-x86_64.tar.xz mv mysql-8.0.32-linux-glibc2.12-x86_64/ mysql80/ mv mysql80/ /usr/local/2、在M…...

Java-长字符串加密

引言: 在数据安全领域,加密技术是保护信息不被未授权访问的重要手段。特别是在处理长字符串时,如何保证加密后的数据既安全又高效,是一个值得探讨的话题。本文将介绍几种常见的加密算法,并展示如何在Java中实现这些算法…...

使用pytest单元测试框架执行单元测试

Pytest 是一个功能强大且灵活的 Python 单元测试框架,它使编写、组织和运行测试变得更加简单。以下是 Pytest 的一些主要特点和优点: 简单易用:Pytest 提供了简洁而直观的语法,使编写测试用例变得非常容易。它支持使用 assert 语…...

Flutter 中 DraggableScrollableSheet 的属性介绍与使用

在 Flutter 中,DraggableScrollableSheet 是一个非常有用的小部件,它允许用户通过手势来拖动一个可滚动的区域,通常被用作底部弹出式面板或者随手势拖动的控件。本文将介绍 DraggableScrollableSheet 的属性以及如何在 Flutter 中使用它。 D…...

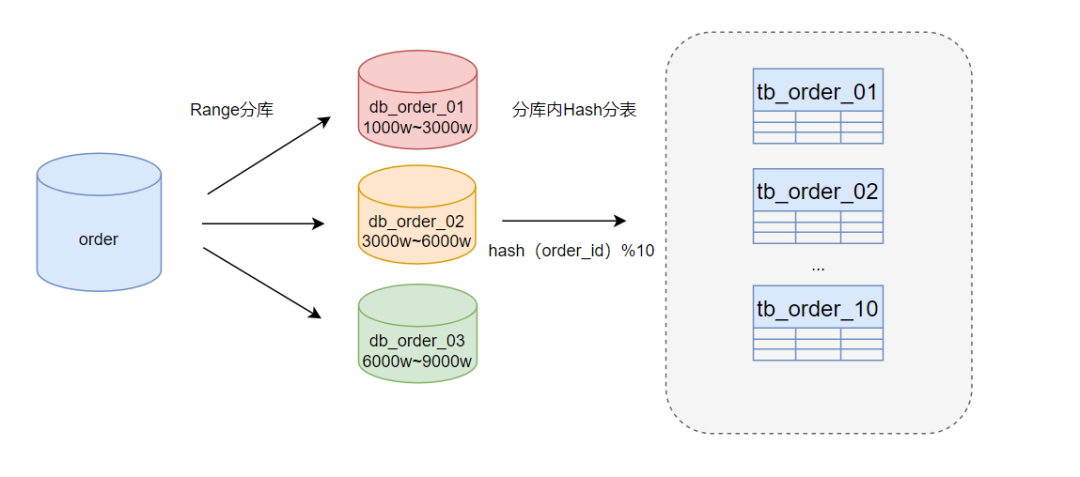

分库分表面试必背

一,背景 随着互联网的普及,使用人数和场景爆炸式增长,现在随便一个应用系统都可能达到数百万千万甚至更大数量级的数据。大量的数据带来了新的挑战,怎么快速完成增删改查的业务,是应用服务开发者最头痛的问题。面对这个…...

)

14个常见的Java课程设计/毕业设计合集(源码+文档)

从网上整理收集了14个常见的java系统设计源码,可以用于课程作业或者毕业设计。 1.基于java的家政预约网站系统 平台采用B/S结构,后端采用主流的Springboot框架进行开发,前端采用主流的Vue.js进行开发。 整个平台包括前台和后台两个部分。 …...

如何用 docker 部署程序?

如何用 docker 部署程序?这个问题有点笼统。 如果是MySQL、Redis这些,只需要拉取镜像,然后设置必要的配置,最终创建并运行实例即可。 如果你的应用是一个Java应用程序,使用Docker来部署它会涉及到Java特有的一些考虑…...

)

5G固定无线接入(FWA)

固定无线接入(FWA) 固定无线接入(Fixed Wireless Access)是使用两个固定点之间的无线电链路提供无线宽带的过程。换句话说,固定无线是一种为家庭或企业提供无线互联网接入的方式,无需铺设光纤和电缆来提供最…...

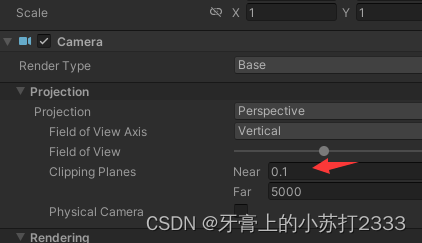

Unity ScreenPointToRay 获取到的坐标不准确

👾奇奇怪怪的 🥙问题描述🥪解决方案🍿验证代码 🥙问题描述 使用:Camera.main.ScreenPointToRay 将鼠标坐标转换成射线,然后通过:Physics.Raycast 获取到射线碰撞到的坐标࿰…...

5分钟部署阿里RexUniNLU:Web界面操作,无需编程基础

5分钟部署阿里RexUniNLU:Web界面操作,无需编程基础 1. 认识RexUniNLU:零样本理解的神器 想象一下,你刚接手一个新项目,老板丢给你一堆用户评论,要求你快速分析出大家对产品"屏幕"、"续航&…...

seo页面优化公司如何进行网站内容优化

SEO页面优化公司如何进行网站内容优化 在当今数字化时代,网站内容优化已经成为了每个企业在SEO(搜索引擎优化)中的关键步骤。SEO页面优化公司通过一系列策略和技术,帮助企业提高网站在搜索引擎中的排名,从而吸引更多的…...

Linux服务器日志爆满?5个实用命令快速定位并清理大日志文件

Linux服务器日志爆满?5个实用命令快速定位并清理大日志文件 当服务器磁盘空间告急时,日志文件往往是罪魁祸首。作为系统管理员,我们需要快速定位问题并安全清理,避免服务中断。本文将分享5个核心命令的组合使用技巧,帮…...

OpenClaw 入门完整教程:从零搭建自托管AI网关

OpenClaw入门到实战:自托管AI网关完整部署指南 作者:鲲鹏AI探索局 | 标签:OpenClaw, AI Agent, 自托管, 多平台聊天, 网关部署 摘要 本文详细介绍OpenClaw——一个开源自托管AI网关的安装、配置和实战部署全过程。通过实际案例演示如何连接T…...

Ubuntu22.04微信依赖冲突的终极解决方案

1. 问题现象与原因分析 最近在Ubuntu 22.04上安装微信时,很多朋友都遇到了依赖冲突的问题。具体表现是当你尝试通过命令行安装微信时,系统会提示类似这样的错误信息: 下列软件包有未满足的依赖关系: libldap-2.4-2 : 依赖: libsas…...

基于Spark+Hadoop+Hive大数据分析的城市街道路灯智能化点亮时间优化研究

前言随着城市化进程的加速,城市街道路灯系统在保障交通安全、提升城市形象与居民生活质量等方面发挥着关键作用。本研究聚焦于城市街道路灯智能化点亮时间的优化,依托大数据分析技术深入挖掘路灯照明需求与环境因素之间的复杂关联。 研究整合多源大数据&…...

毕业设计实战:基于SSM+JSP的家纺用品销售管理系统设计与实现全攻略

毕业设计实战:基于SSMJSP的家纺用品销售管理系统设计与实现全攻略 在开发“家纺用品销售管理系统”这套毕设时,我曾因“订单管理与商家库存脱节”踩过一个关键坑。初期设计时,我将“用户下单”和“商家库存扣减”视为两个独立操作,…...

从单张图片到动态世界:Depth-Anything-3如何重塑3D视觉的通用法则

1. 当单张图片学会"思考"深度 第一次看到Depth-Anything-3(DA3)处理一张普通照片时,我盯着屏幕足足愣了三分钟。它就像给二维世界突然装上了Z轴——原本平淡无奇的街景照片,在DA3的解构下,近处的咖啡杯轮廓清…...

AI赋能:让快马平台解析21届智能车赛规则并生成智能算法代码

最近在准备21届智能车比赛时,发现今年的赛道规则特别复杂,各种新加入的元素和评分标准让人有点头大。正好尝试用InsCode(快马)平台的AI辅助开发功能来帮忙解析规则并生成算法代码,整个过程意外地顺利,分享下具体实现思路。 规则文…...

平台,基于PC+松下伺服实战)

告别SpeedGoat:低成本搭建Simulink Real-Time硬件在环(HIL)平台,基于PC+松下伺服实战

低成本搭建Simulink实时控制平台:基于PC与松下伺服的硬件在环方案 在工业自动化与运动控制领域,实时硬件在环(HIL)测试是验证算法有效性的关键环节。传统方案如SpeedGoat等专用设备虽性能稳定,但动辄数十万的成本让许多…...