#FPGA(IRDA)

1.IDE:Quartus II

2.设备:Cyclone II EP2C8Q208C8N

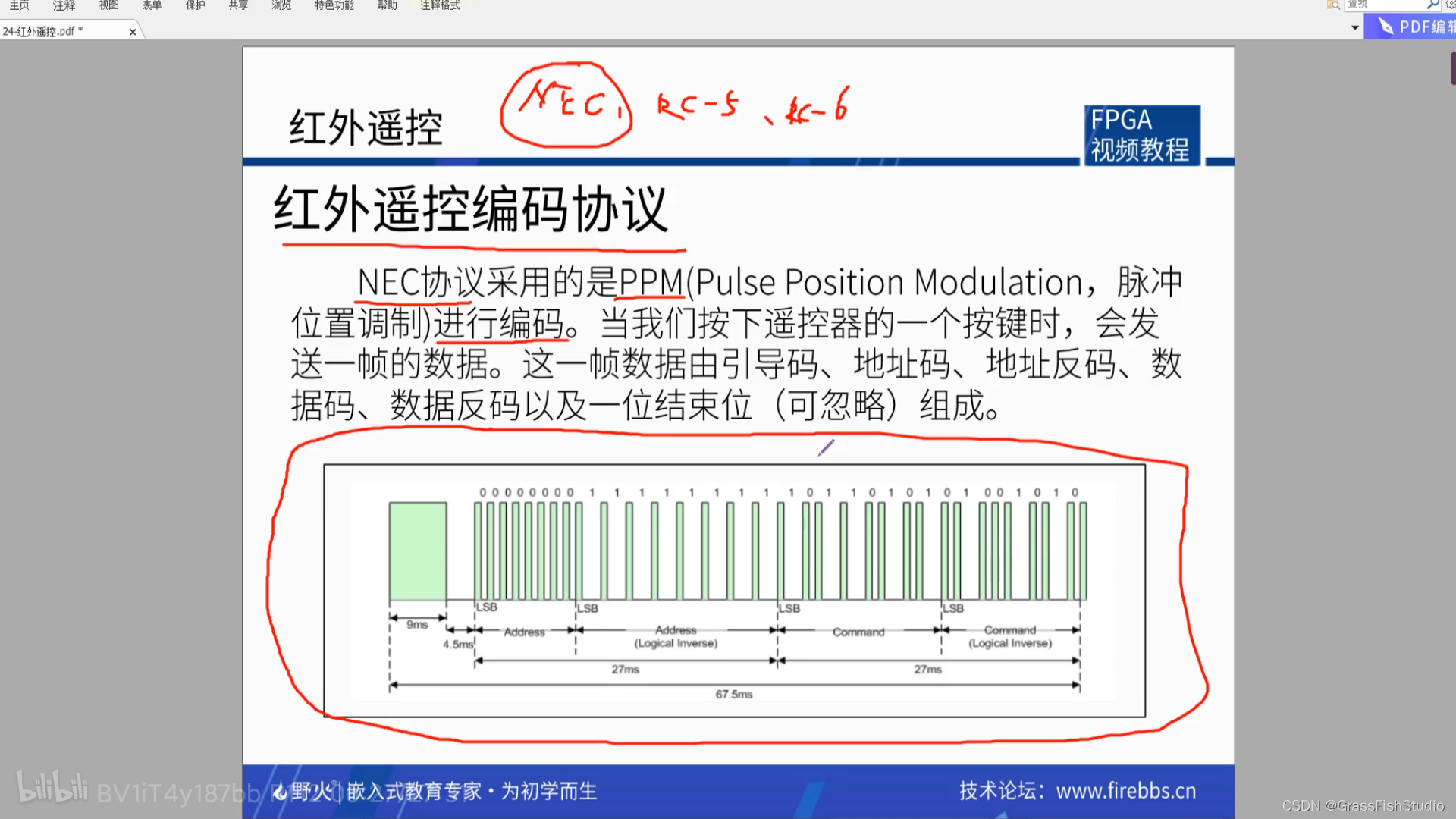

3.实验:IRDA(仿真接收一个来自0x57地址的数据0x22 (十进制34))

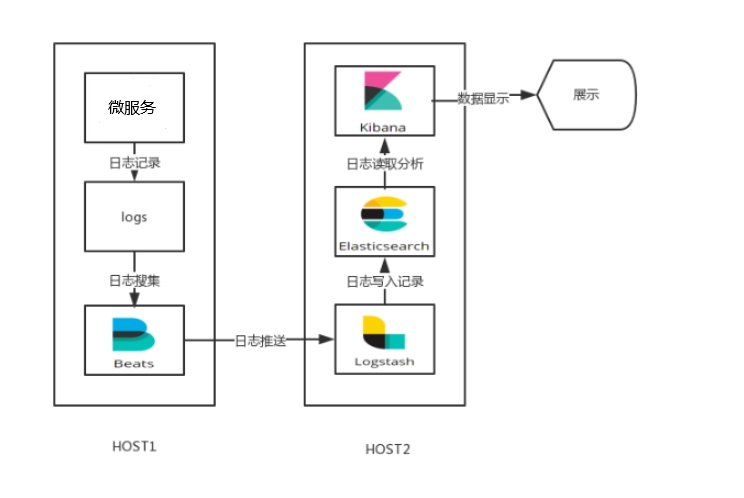

4.时序图:

5.步骤

6.代码:

irda_receive.v

module irda_receive

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire irda_in , //irda接收端引脚输入output reg [19:0] data , //数据输出

output reg repeat_en //重复使能

);/**状态*/

parameter IDLE = 5'b00001 ; //空闲

parameter TIME_9MS = 5'b00010 ; //引导或者重复的9ms低电平

parameter ARBIT = 5'b00100 ; //地址

parameter DATA = 5'b01000 ; //数据

parameter REPEAT = 5'b10000 ; //重复/**时间范围*/

parameter CNT_560US_MIN = 19'd20000 ;

parameter CNT_560US_MAX = 19'd35000 ;

parameter CNT_1_69MS_MIN = 19'd80000 ;

parameter CNT_1_69MS_MAX = 19'd90000 ;

parameter CNT_2_25MS_MIN = 19'd100000 ;

parameter CNT_2_25MS_MAX = 19'd125000 ;

parameter CNT_4_5MS_MIN = 19'd175000 ;

parameter CNT_4_5MS_MAX = 19'd275000 ;

parameter CNT_9MS_MIN = 19'd400000 ;

parameter CNT_9MS_MAX = 19'd490000 ; /**寄存器*/

reg [4:0] state ; //状态

reg inf_in_dly1 ; //用于电平跳转判断(下一时刻)

reg inf_in_dly2 ; //用于电平跳转判断(上一时刻)

wire inf_in_fall ; //下降沿标志位

wire inf_in_rise ; //上升沿标志位reg [18:0] cnt ; //计数器reg flag_9ms ; //9ms标志位

reg flag_4_5ms ; //4.5ms标志位

reg flag_560us ; //560us标志位

reg flag_1_69ms ; //1.69ms标志位

reg flag_2_25ms ; //2.25ms标志位reg [5:0] cnt_data ; //记录接收的数据个数

reg [31:0] data_reg ; //数据记录/**状态跳转*/

always @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)state <= IDLE;else case(state)IDLE :begin if(inf_in_fall == 1'b1) //引导信号下降沿到来state <= TIME_9MS;elsestate <= IDLE;endTIME_9MS:beginif((inf_in_rise == 1'b1)&&(flag_9ms == 1'b1)) //引导信号到来后持续低电平再拉高,低电平时间达到9ms(进入接收地址码状态)state <= ARBIT; else if((inf_in_rise == 1'b1)&&(flag_9ms == 1'b0)) //引导信号到来后持续低电平再拉高,低电平时间未达到9ms(恢复空闲状态)state <= IDLE;else //引导信号到来后持续低电平未检测到高电平时期(还未拉高,等待中,保持状态不变)state <= TIME_9MS;end ARBIT :beginif((inf_in_fall==1'b1)&&(flag_2_25ms == 1'b1)) //下降沿到来接收到重复码(高电平时间未2.25ms,则为重复码,高电平时间为4.5ms则为引导码)state <= REPEAT;else if((inf_in_fall==1'b1)&&(flag_4_5ms == 1'b1)) state <= DATA ;else if((inf_in_fall==1'b1)&&(flag_4_5ms == 1'b0)&&(flag_2_25ms == 1'b0)) //下降沿到来,高电平不满足2.25ms和4.5ms state <= IDLE;else //保持原状态state <= ARBIT;endDATA :beginif((inf_in_rise == 1'b1) && (flag_560us == 1'b0)) //数据信号低电平不满足“0”要求state <= IDLE;else if((inf_in_fall == 1'b1)&&(flag_560us == 1'b0)&&(flag_1_69ms == 1'b0)) //下降沿到来,但是高电平不足560usstate <= IDLE;else if((inf_in_rise == 1'b1)&&(cnt_data == 6'd32)) //结束信号是拉高,计数到32个数据state <= IDLE;elsestate <= DATA;end REPEAT :beginif(inf_in_rise == 1'b1)state <= IDLE;elsestate <= REPEAT;enddefault :beginstate <= IDLE; endendcase

end/**电平翻转记录*/

always @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)begininf_in_dly1 <= 1'b0;inf_in_dly2 <= 1'b0;endelsebegininf_in_dly1 <= irda_in; //记录当前电平inf_in_dly2 <= inf_in_dly1; //记录上一时刻电平end

end/**下降沿上升沿标志位赋值*/

assign inf_in_fall = ((inf_in_dly1 == 1'b0)&&(inf_in_dly2 == 1'b1)) ? 1'b1 : 1'b0; //上一时刻高电平,当前时刻低电平(下降沿标志位拉高)

assign inf_in_rise = ((inf_in_dly1 == 1'b1)&&(inf_in_dly2 == 1'b0)) ? 1'b1 : 1'b0; //上一时刻低电平,当前时刻高电平(上升沿标志位拉高)/**cnt控制*/

always @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)cnt <= 19'd0;else case(state)IDLE : cnt <= 19'd0;TIME_9MS :beginif((inf_in_rise == 1'b1)&&(flag_9ms == 1'b1))cnt <= 19'd0;elsecnt <= cnt + 1'b1;endARBIT :beginif((inf_in_fall == 1'b1) && ((flag_4_5ms == 1'b1)||(flag_2_25ms == 1'b1))) //仲裁(引导信号还是重复信号)cnt <= 19'd0;elsecnt <= cnt + 1'b1;endDATA :beginif((inf_in_rise == 1'b1)&&(flag_560us == 1'b1))cnt <= 19'd0;else if((inf_in_fall == 1'b1)&&((flag_560us == 1'b1)||(flag_1_69ms == 1'b1))) // 0/1cnt <= 19'd0;elsecnt <= cnt + 1'b1; enddefault : cnt <= 19'd0;endcase

end/**时间标志位控制*/

always @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)flag_9ms <= 1'b0;else if((state == TIME_9MS)&&(cnt >= CNT_9MS_MIN)&&(cnt <= CNT_9MS_MAX))flag_9ms <= 1'b1;elseflag_9ms <= 1'b0;

endalways @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)flag_4_5ms <= 1'b0;else if((state == ARBIT)&&(cnt >= CNT_4_5MS_MIN)&&(cnt <= CNT_4_5MS_MAX))flag_4_5ms <= 1'b1;elseflag_4_5ms <= 1'b0;

endalways @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)flag_560us <= 1'b0;else if((state == DATA)&&(cnt >= CNT_560US_MIN)&&(cnt <= CNT_560US_MAX))flag_560us <= 1'b1;elseflag_560us <= 1'b0;

endalways @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)flag_1_69ms <= 1'b0;else if((state == DATA)&&(cnt >= CNT_1_69MS_MIN)&&(cnt <= CNT_1_69MS_MAX))flag_1_69ms <= 1'b1;elseflag_1_69ms <= 1'b0;

endalways @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)flag_2_25ms <= 1'b0;else if((state == ARBIT)&&(cnt >= CNT_2_25MS_MIN)&&(cnt <= CNT_2_25MS_MAX))flag_2_25ms <= 1'b1;elseflag_2_25ms <= 1'b0;

end/**接收数据计数*/

always @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)cnt_data <= 6'd0;else if((inf_in_rise == 1'b1)&&(cnt_data == 6'd32))cnt_data <= 6'd0;else if((inf_in_fall == 1'b1)&&(state == DATA))cnt_data <= cnt_data + 1'b1;elsecnt_data <= cnt_data;

end/**接收的数据*/

always @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)data_reg <= 32'b0;else if((state == DATA)&&(inf_in_fall == 1'b1)&&(flag_560us == 1'b1))data_reg[cnt_data] <= 1'b0;else if((state == DATA)&&(inf_in_fall == 1'b1)&&(flag_1_69ms == 1'b1))data_reg[cnt_data] <= 1'b1;elsedata_reg <= data_reg;

end/**数据倒排(LSB)*/

always @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)data <= 20'b0;else if((cnt_data == 6'd32)&&(~data_reg[23:16] == data_reg[31:24])&&(~data_reg[15:8] == data_reg[7:0]))data <= {12'b0,data_reg[23:16]};elsedata <= data;

end/**重复信号使能控制*/

always @ (posedge sys_clk or negedge sys_rst_n) beginif(sys_rst_n == 1'b0)repeat_en <= 1'b0;else if((state ==REPEAT)&&(~data_reg[23:16] == data_reg[31:24]))repeat_en <= 1'b1;elserepeat_en <= 1'b0;

endendmodule

仿真代码:

`timescale 1ns/1ns

module tb_irda_receive();reg sys_clk ;

reg sys_rst_n ;

reg inf_in ;wire [19:0] data ;

wire repeat_en ;initial beginsys_clk = 1'b1;sys_rst_n = 1'b0;inf_in <= 1'b1;#30sys_rst_n <= 1'b1;#1000

//引导码 inf_in <= 1'b0;#9000_000inf_in <= 1'b1;#4500_000

//地址码(8'h57 0101_0111 1110_1010)inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0

//地址反码(1110_1010 0001_0101)inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1

//数据码(8'h22 0010_0010 0100_0100)inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0

//数据反码(0100_0100 1011_1011)inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #560_000 //逻辑0inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1inf_in <= 1'b0;#560_000inf_in <= 1'b1; #1690_000 //逻辑1

//结束位inf_in <= 1'b0;#560_000

//高电平保持 inf_in <= 1'b1;#4200_0000

//重复码inf_in <= 1'b0;#9000_000inf_in <= 1'b1;#2250_000

//结束位inf_in <= 1'b0;#560_000inf_in <= 1'b1; endalways #10 sys_clk = ~ sys_clk;/**实例化*/

irda_receive irda_receive_inst

(

.sys_clk (sys_clk ) ,

.sys_rst_n (sys_rst_n) ,

.irda_in (inf_in ) , //irda接收端引脚输入.data (data ) , //数据输出

.repeat_en (repeat_en) //重复使能

);endmodule

相关文章:

#FPGA(IRDA)

1.IDE:Quartus II 2.设备:Cyclone II EP2C8Q208C8N 3.实验:IRDA(仿真接收一个来自0x57地址的数据0x22 (十进制34)) 4.时序图: 5.步骤 6.代码: irda_receive.v module irda_receive ( input wire…...

Sora—openai最新大模型文字生成视频

这里没办法发视频,发几个图片感受感受吧 OpenAI发布了Sora,一种文字生成视频的技术,从演示看,效果还是相当不错的。 Sora的强大之处在于其能够根据文本描述,生成长达 60秒的视频,其中包含精细复杂的场景…...

介绍(网络电话、ip电话))

VoIP(Voice over Internet Protocol 基于IP的语音传输)介绍(网络电话、ip电话)

文章目录 VoIP(基于IP的语音传输)1. 引言2. VoIP基础2.1 VoIP工作原理2.2 VoIP协议 3. VoIP的优势和挑战3.1 优势3.2 挑战 4. VoIP的应用5. 总结 VoIP(基于IP的语音传输) 1. 引言 VoIP,全称Voice over Internet Prot…...

编程笔记 Golang基础 027 结构体

编程笔记 Golang基础 027 结构体 一、结构体的定义二、结构体的实例化1. 直接初始化2. 使用键值对初始化(即使字段顺序不一致也能正确赋值)3. 部分初始化(未指定的字段会得到它们类型的零值)4. 使用var声明和初始化5. 结构体字面量…...

opencascade15解析导出为step格式

#include "DisplayScene.h" // 包含显示场景的头文件 #include "Viewer.h" // 包含查看器的头文件// OpenCascade 包含 #include <BRepPrimAPI_MakeCylinder.hxx> // 创建圆柱体 #include <BinXCAFDrivers.hxx> // 二进制XCAF驱动程序 #includ…...

【软件设计模式之模板方法模式】

文章目录 前言一、什么是模板方法模式?二、模板方法模式的结构1. 抽象类定义2. 具体实现 三、模板方法模式的应用场景1. 算法重用2. 操作中的固定步骤3. 扩展框架的功能4. 提供回调方法5. 遵循开闭原则 四、模板方法模式的优缺点1. 优点代码复用扩展性好符合开闭原则…...

Spring Boot项目怎么对System.setProperty(key, value)设置的属性进行读取加解密

一、前言 之前我写过一篇文章使用SM4国密加密算法对Spring Boot项目数据库连接信息以及yaml文件配置属性进行加密配置(读取时自动解密),对Spring Boot项目的属性读取时进行加解密,但是没有说明对System.setProperty(key, value)设…...

Linux理解

VMware安装Linux安装 目录 VMware安装Linux安装 1.1 什么是Linux 1.2 为什么要学Linux 1.3 学完Linux能干什么 2.1 主流操作系统 2.2 Linux系统版本 VMware安装Linux安装 1.1 什么是Linux Linux是一套免费使用和自由传播的操作系统。 1.2 为什么要学Linux 1). 企业用人…...

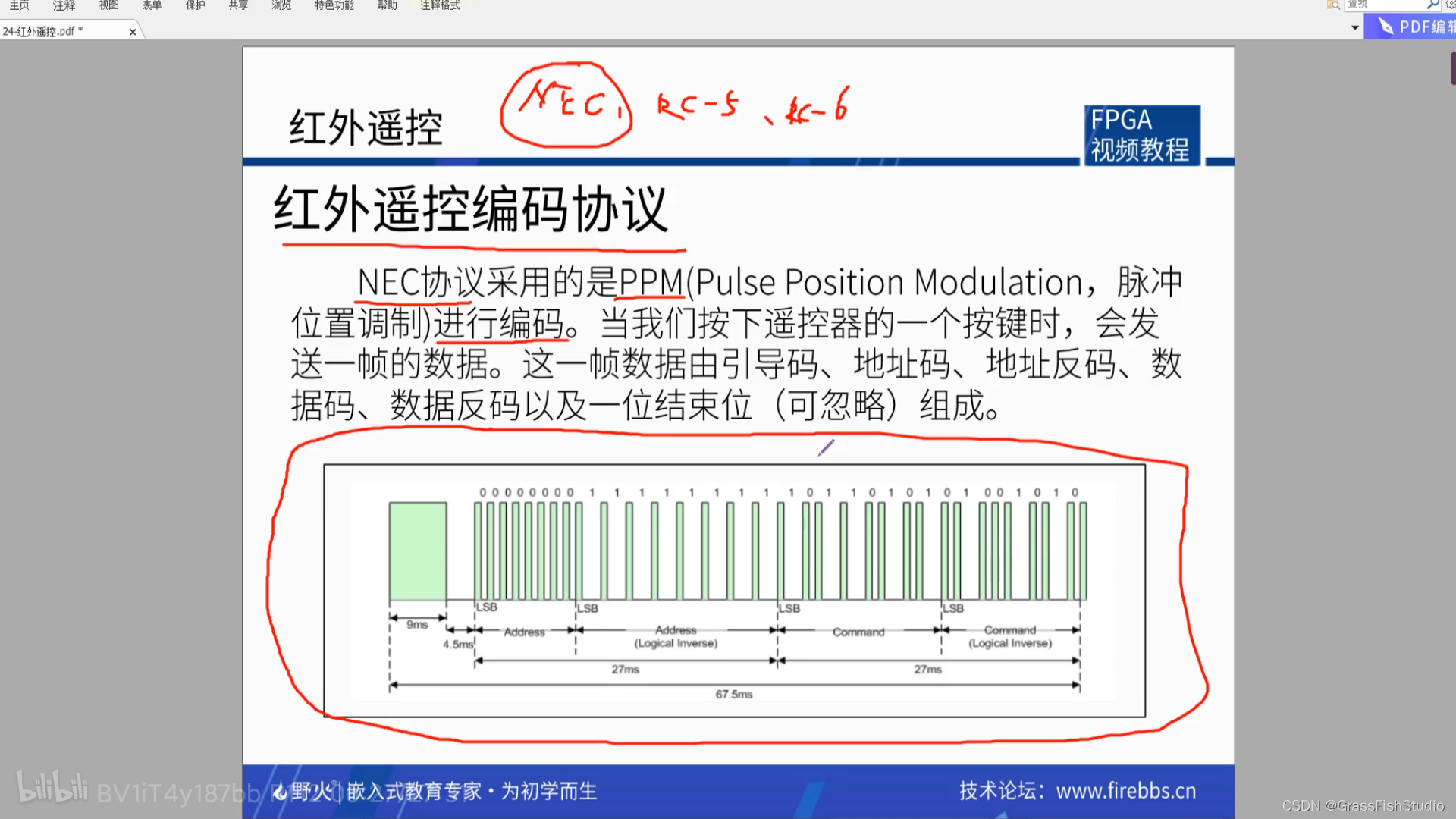

常用芯片学习——YC688语音芯片

YC688 广州语创公司语音芯片 使用说明 YC688是一款工业级的MP3语音芯片 ,完美的集成了MP3、WAV的硬解码。支持SPI-Flash、TF卡、U盘三种存储设备。可通过电脑直接更新SPI-Flash的内容,无需上位机软件。通过简单的串口指令即可完成三种存储设备的音频插…...

C语言:指针的进阶讲解

目录 1. 二级指针 1.1 二级指针是什么? 1.2 二级指针的作用 2. 一维数组和二维数组的本质 3. 指针数组 4. 数组指针 5. 函数指针 6. typedef的使用 7. 函数指针数组 7.1 转移表 1. 二级指针 如果了解了一级指针,那二级指针也是可以很好的理解…...

基于SSM的车位租赁系统(有报告)。Javaee项目。ssm项目。

演示视频: 基于SSM的车位租赁系统(有报告)。Javaee项目。ssm项目。 项目介绍: 采用M(model)V(view)C(controller)三层体系结构,通过Spring Spri…...

Java pyhon C C++ R JS 主流语言的区别-03

以下是对这几种语言的数据类型进行简要归纳: Java的数据类型: 基本数据类型:包括整数类型(byte、short、int、long)、浮点数类型(float、double)、字符类型(char)和布尔…...

5 buuctf解题

命令执行 [BJDCTF2020]EasySearch1 打开题目 尝试弱口令,发现没有用 扫描一下后台,最后用御剑扫描到了index.php.swp 访问一下得到源码 源码如下 <?phpob_start();function get_hash(){$chars ABCDEFGHIJKLMNOPQRSTUVWXYZabcdefghijklmnopqrstu…...

微服务三十五关

1.微服务有什么好处? 微服务优点很多,但是我们通常说一个东西好肯定会跟另一个东西比较, 通常说微服务好会和单体项目进行比较。以下是微服务相对于单体项目的一些显著好处: 首先,让我们讨论单体项目的一些主要缺点&a…...

第一个 Angular 项目 - 添加服务

第一个 Angular 项目 - 添加服务 这里主要用到的内容就是 [Angular 基础] - service 服务 提到的 前置项目在 第一个 Angular 项目 - 动态页面 这里查看 想要实现的功能是简化 shopping-list 和 recipe 之间的跨组件交流 回顾一下项目的结构: ❯ tree src/app/…...

红日靶场3

靶场链接:漏洞详情 在虚拟机的网络编辑器中添加两个仅主机网卡 信息搜集 端口扫描 外网机处于网端192.168.1.0/24中,扫描外网IP端口,开放了80 22 3306端口 80端口http服务,可以尝试登录网页 3306端口mysql服务,可…...

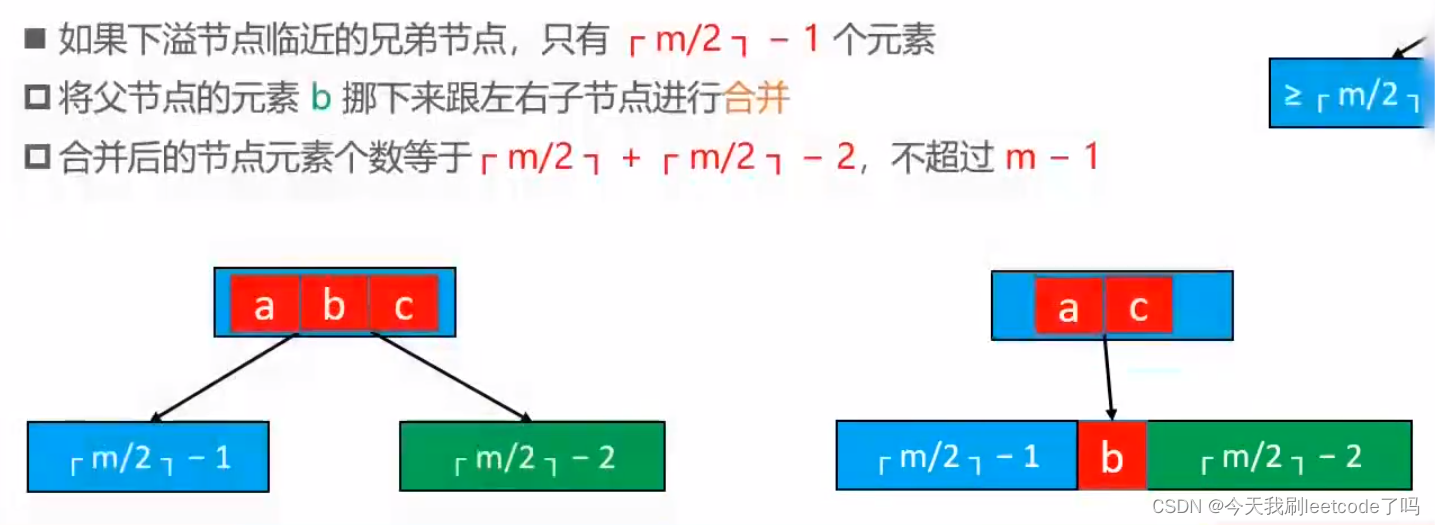

B树的介绍

R-B Tree 简介特性B树特性m阶B树的性质(这些性质是B树规定的) B树的搜索B树的添加B树的删除——非叶子结点 简介 R-B Tree又称为Red-Black Tree,红黑树。是一种特殊的二叉查找树,红黑树的每个节点上都有存储为表示结点的颜色&…...

)

《The Art of InnoDB》第二部分|第4章:深入结构-磁盘结构-撕裂的页面(doublewrite buffer)

4.5 撕裂的页面 目录 4.5 撕裂的页面 4.5.1 双写缓冲区的作用 4.5.2 双写缓冲区的结构 4.5.3 双写缓冲区与Redolog的协同工作流程 4.5.2 双写缓冲区写入时机 4.5.3 禁用双写缓冲区 4.5.4 小结 未完待续... 上文我们学习了redo log的结构和其工作原理,它是一个…...

提示工程(Prompt Engineering)、微调(Fine-tuning) 和 嵌入(Embedding)

主要参考资料: 还没搞懂嵌入(Embedding)、微调(Fine-tuning)和提示工程(Prompt Engineering)?: https://blog.csdn.net/DynmicResource/article/details/133638079 B站Up主Nenly同学…...

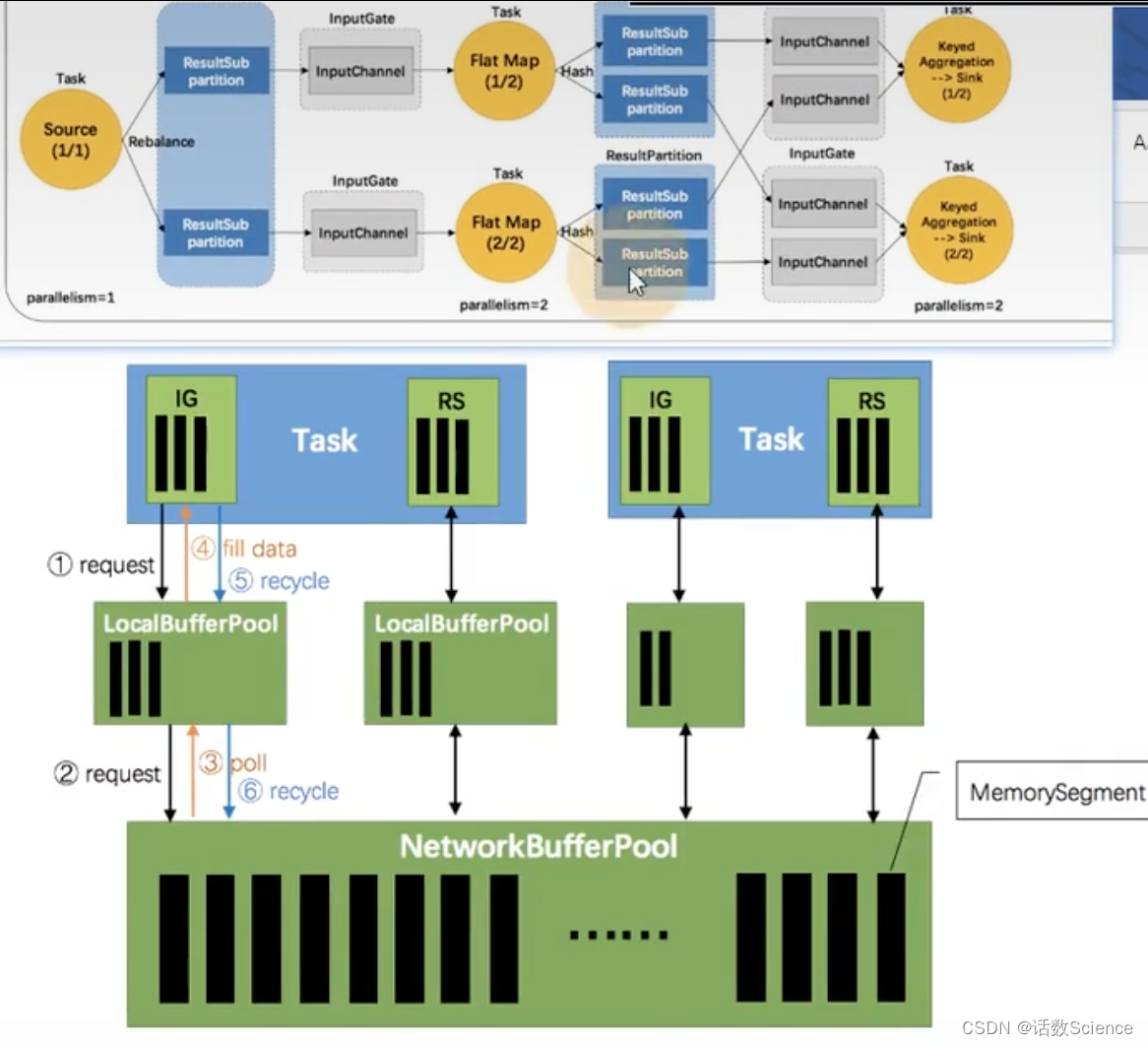

【Flink精讲】Flink 内存管理

面临的问题 目前, 大数据计算引擎主要用 Java 或是基于 JVM 的编程语言实现的,例如 Apache Hadoop、 Apache Spark、 Apache Drill、 Apache Flink 等。 Java 语言的好处在于程序员不需要太关注底层内存资源的管理,但同样会面临一个问题&…...

【Midjourney极简艺术风格终极指南】:20年视觉设计专家亲授3大构图法则、5类禁用提示词与1套可复用Prompt模板

更多请点击: https://intelliparadigm.com 第一章:极简艺术风格的本质与Midjourney适配原理 极简艺术风格并非简单地“减少元素”,而是通过精准的留白、克制的色彩、几何化的形态与高度凝练的视觉语法,实现信息密度与情绪张力的平…...

深度学习训练理论:初始化与梯度消失

深度学习训练理论:初始化与梯度消失 1. 技术分析 1.1 训练挑战概述 深度学习训练面临多种挑战: 训练挑战梯度消失: 梯度趋近于0梯度爆炸: 梯度过大参数初始化: 权重初始化影响激活函数选择: 影响梯度流动1.2 梯度消失原因 原因机制影响激活函数sigmoid/t…...

体育科学论文降AI工具免费推荐:2026年体育科学研究毕业论文知网AIGC超标4.8元亲测达标完整指南

体育科学论文降AI工具免费推荐:2026年体育科学研究毕业论文知网AIGC超标4.8元亲测达标完整指南 帮同学选过降AI工具,综合价格、效果、保障来看,推荐嘎嘎降AI(www.aigcleaner.com)。 4.8元,达标率99.26%&a…...

基于LLM与RAG构建智能问答系统:架构、实现与优化指南

1. 项目概述:当RAG遇上LLM,构建你的智能知识问答引擎最近在GitHub上看到一个挺有意思的项目,叫“Jenqyang/LLM-Powered-RAG-System”。光看名字,圈内人大概就能猜到个七七八八:这是一个基于大语言模型(LLM&…...

CFETR重载机械臂精确运动控制验证【附仿真】

✨ 长期致力于中国聚变工程实验堆、遥操作、多功能重载机械臂、路径规划、精确控制、数据融合控制研究工作,擅长数据搜集与处理、建模仿真、程序编写、仿真设计。 ✅ 专业定制毕设、代码 ✅ 如需沟通交流,点击《获取方式》 (1)刚柔…...

2025届毕业生推荐的AI学术平台推荐榜单

Ai论文网站排名(开题报告、文献综述、降aigc率、降重综合对比) TOP1. 千笔AI TOP2. aipasspaper TOP3. 清北论文 TOP4. 豆包 TOP5. kimi TOP6. deepseek 在学术写作范畴之内,怎样迅速、精确地给论文确定一个既契合规范又能够切实有效吸…...

告别手写代码:用达芬奇Configurator+DBC文件,5分钟搞定AUTOSAR CAN控制器配置

达芬奇ConfiguratorDBC文件:5分钟完成AUTOSAR CAN控制器高效配置指南 在汽车电子开发领域,AUTOSAR架构的普及使得嵌入式软件开发流程日益标准化,但随之而来的配置复杂度也让许多工程师头疼。特别是在CAN通信配置环节,传统的手动逐…...

电商运营数字密码解析:0.01、50、0、8.8背后的用户增长与转化逻辑

1. 项目概述:一次电商运营的“数字密码”破译最近在复盘一些头部品牌的电商运营案例时,CYPRESS天猫旗舰店的一组数字引起了我的注意:0.01、50、0、8.8。乍一看,这像是几个毫无关联的随机数,但当你把它们放在电商运营的…...

揭秘开源驾驶辅助系统openpilot:如何用代码重新定义汽车智能化体验

揭秘开源驾驶辅助系统openpilot:如何用代码重新定义汽车智能化体验 【免费下载链接】openpilot openpilot is an operating system for robotics. Currently, it upgrades the driver assistance system on 300 supported cars. 项目地址: https://gitcode.com/Gi…...

推理服务为什么一做对话状态复用就开始省 Token 却更容易答偏:从 Decoder State Reuse 到 Constraint Replay 的工程实战

一、状态复用一上线,省下 Token 却先丢了约束 很多团队把多轮对话做成“首轮完整 prefill,后续直接复用 decoder state”。📉 账面收益很好:TTFT 下降,输入 token 费用也明显收缩。但线上很快出现另一类故障࿱…...