FPGA高端项目:FPGA基于GS2971的SDI视频接收转HDMI输出,提供3套工程源码和技术支持

目录

- 1、前言

- 免责声明

- 2、相关方案推荐

- 本博已有的 SDI 编解码方案

- 本方案的SDI图像缩放应用

- 本方案的SDI纯verilog图像缩放+视频拼接应用

- 本方案的SDI HLS图像缩放+视频拼接应用

- 本方案的SDI视频编码+动态字符叠加输出应用

- 本方案的SDI视频编码多路视频融合+视频叠加应用

- 本方案的SDI视频编码GTX 8b/10b编解码SFP光口传输

- FPGA的SDI视频编解码项目培训

- 3、详细设计方案

- 设计原理框图

- SDI 相机

- GS2971

- BT1120转RGB

- 图像缓存

- HDMI输出

- 工程1-->源码架构

- 工程2-->源码架构

- 工程3-->源码架构

- 4、工程源码1详解-->SDI转HDMI--FDMA缓存PL端DDR3

- 5、工程源码2详解-->SDI转HDMI--FDMA缓存PS端DDR3

- 6、工程源码3详解-->SDI转HDMI--VDMA缓存PS端DDR3

- 7、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 8、上板调试验证

- 准备工作

- 输出视频演示

- 9、福利:工程代码的获取

FPGA高端项目:FPGA基于GS2971的SDI视频接收转HDMI输出,提供3套工程源码和技术支持

1、前言

目前FPGA实现SDI视频编解码有两种方案:一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,利用Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。有意思的是,这两种方案在本博这里都有对应的解决方案,包括硬件的FPGA开发板、工程源码等等。

本设计基于Xilinx的Zynq7100-xc7z100ffg900-2中端FPGA开发板使用GS2971实现SDI视频接收转HDMI输出,输入源为一个HD-SDI相机,也可以使用SD-SDI或者3G-SDI相机,因为本设计是三种SDI视频自适应的;同轴的SDI视频通过同轴线连接到GS2971转接板,GS2971解码芯片将同轴的串行的SDI视频解码为并行的BT1120格式视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;本设计的目的是做图像缩放后输出解码的SDI视频,针对目前市面上的主流项目需求,本博设计了HDMI输出方式,需要对解码BT1120视频进行转RGB+图像缩放图像缓存操作;图像缓存使用两种架构,一种是FDMA架构,该架构简单灵活,输入接口为VGA视频时序,即用VS、DE、RGB数据,另一种是VDMA架构,该架构是Xilinx官方力推的架构,输入接口为AXI4-Stream;另外,FDMA架构的视频既可以缓存到PL端DDR,也可以缓存到PS端DDR,针对不同的项目需求;本设计使用BT1120转RGB模块实现视频格式转换;使用本博常用的FDMA图像缓存架构和VDMA图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR3;图像从DDR3读出后,进入HDMI发送模块输出HDMI显示器;本博客提供3套工程源码,具体如下:

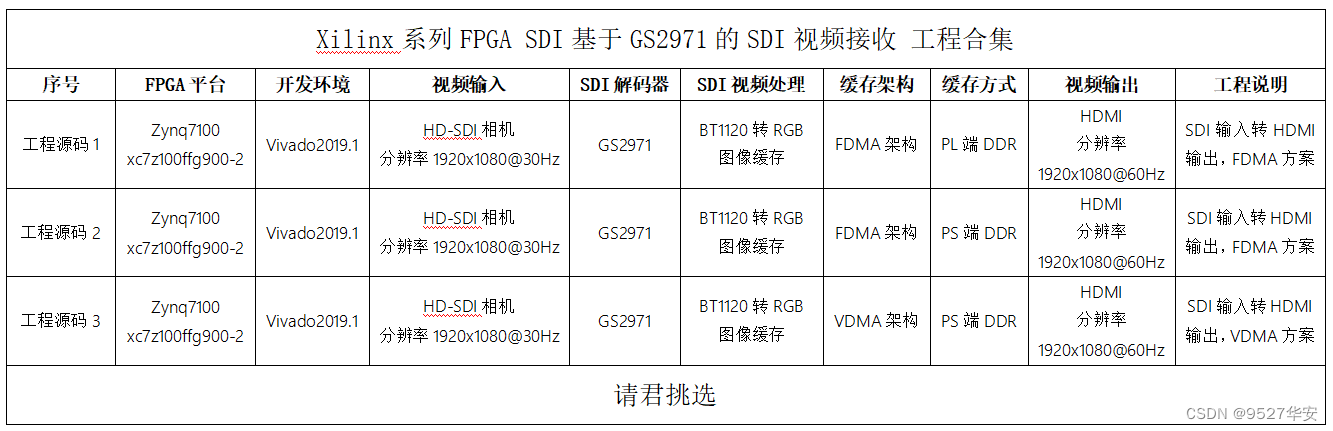

现对上述三套工程源码做如下解释,方便读者理解:

工程源码1:

输入视频为HD-SDI相机,输入分辨率为1920x1080@30Hz,经过GS2971解码+BT1120转RGB+FDMA图像缓存+HDMI输出模块后,以HDMI接口方式输出,输出分辨率为1920x1080@60Hz;此工程的FDMA图像缓存架构将视频缓存到PL端DDR3,适应于纯FPGA项目,比如可用于Xilinx的Artix7、Kintex7、Virtex7等FPGA;

工程源码2:

输入视频为HD-SDI相机,输入分辨率为1920x1080@30Hz,经过GS2971解码+BT1120转RGB+FDMA图像缓存+HDMI输出模块后,以HDMI接口方式输出,输出分辨率为1920x1080@60Hz;此工程的FDMA图像缓存架构将视频缓存到PS端DDR3,适应于Zynq系列FPGA项目,比如可用于Xilinx的Zynq7000系列、Zynq7000、Zynq UltraScale等FPGA;

工程源码3:

输入视频为HD-SDI相机,输入分辨率为1920x1080@30Hz,经过GS2971解码+BT1120转RGB+VDMA图像缓存+HDMI输出模块后,以HDMI接口方式输出,输出分辨率为1920x1080@60Hz;此工程的VDMA图像缓存架构将视频缓存到PS端DDR3,即可用于纯FPGA项目,比如可用于Xilinx的Artix7、Kintex7、Virtex7等FPGA,配合MicroBlaze;也可用于Zynq系列FPGA项目,比如可用于Xilinx的Zynq7000系列、Zynq7000、Zynq UltraScale等FPGA;

本文详细描述了Xilinx的Zynq7100-xc7z100ffg900-2中端FPGA开发板使用GS2971实现SDI视频接收转HDMI输出,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

关于MIPI协议,请自行搜索,csdn就有很多大佬讲得很详细,我就不多写这块了;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接:点击直接前往

本方案的SDI图像缩放应用

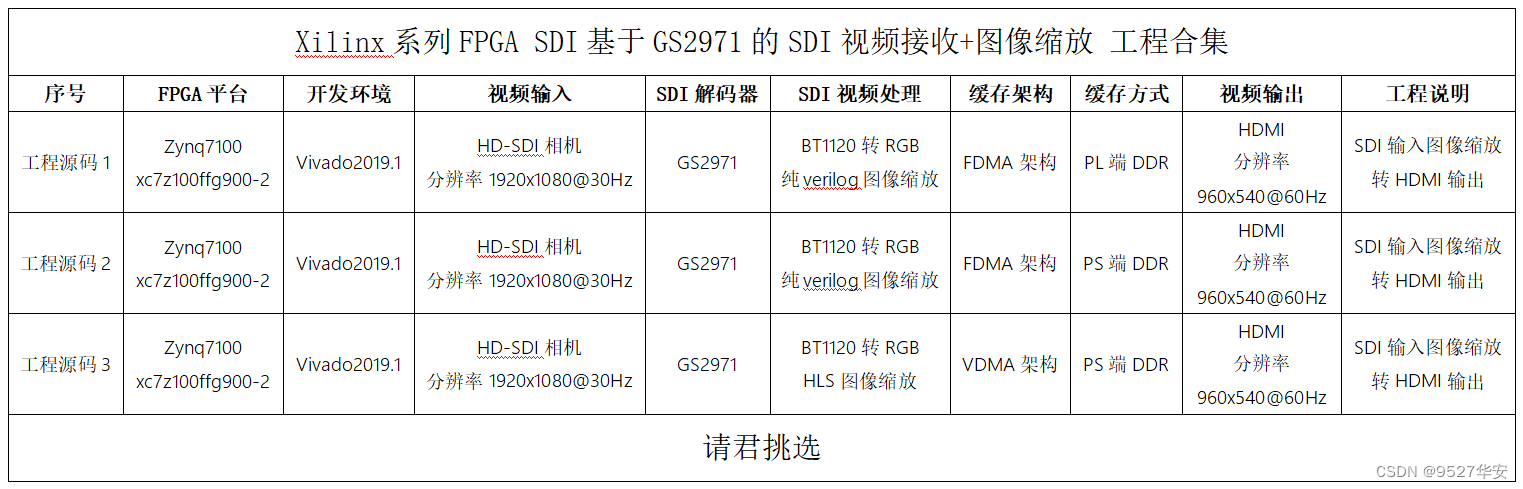

SDI视频解码后,可以进行多种图像处理,本应用就是图像缩放,有的项目需要对SDI图像进行缩放,本应用高度符合项目需求,提供3套工程源码,具体如下:

上述所有工程源码均已上板调试通过,详细设计说明等待本博更新对用的博客。。。

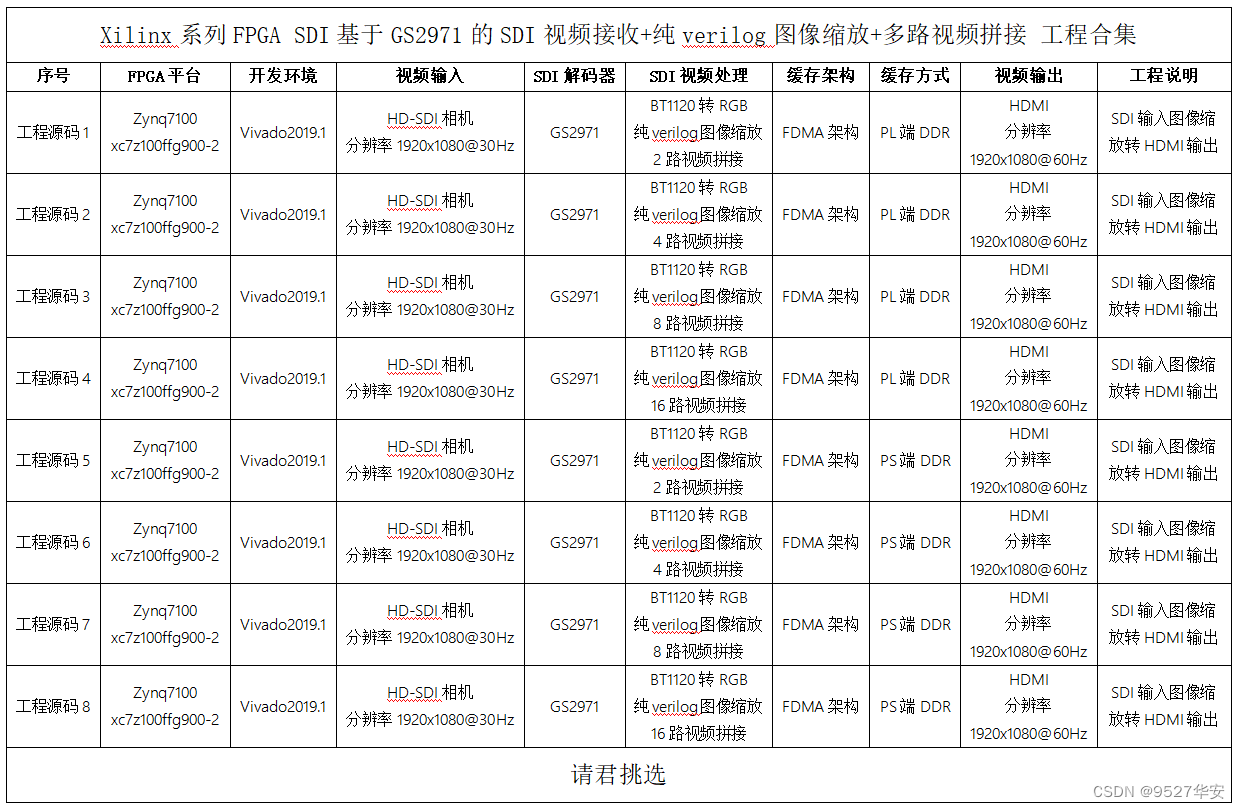

本方案的SDI纯verilog图像缩放+视频拼接应用

SDI视频解码后,可以进行多种图像处理,本应用就是纯verilog图像缩放+视频拼接,有的项目需要对SDI图像进行缩放拼接,本应用高度符合项目需求,提供8套工程源码,具体如下:

上述所有工程源码均已上板调试通过,详细设计说明等待本博更新对用的博客。。。

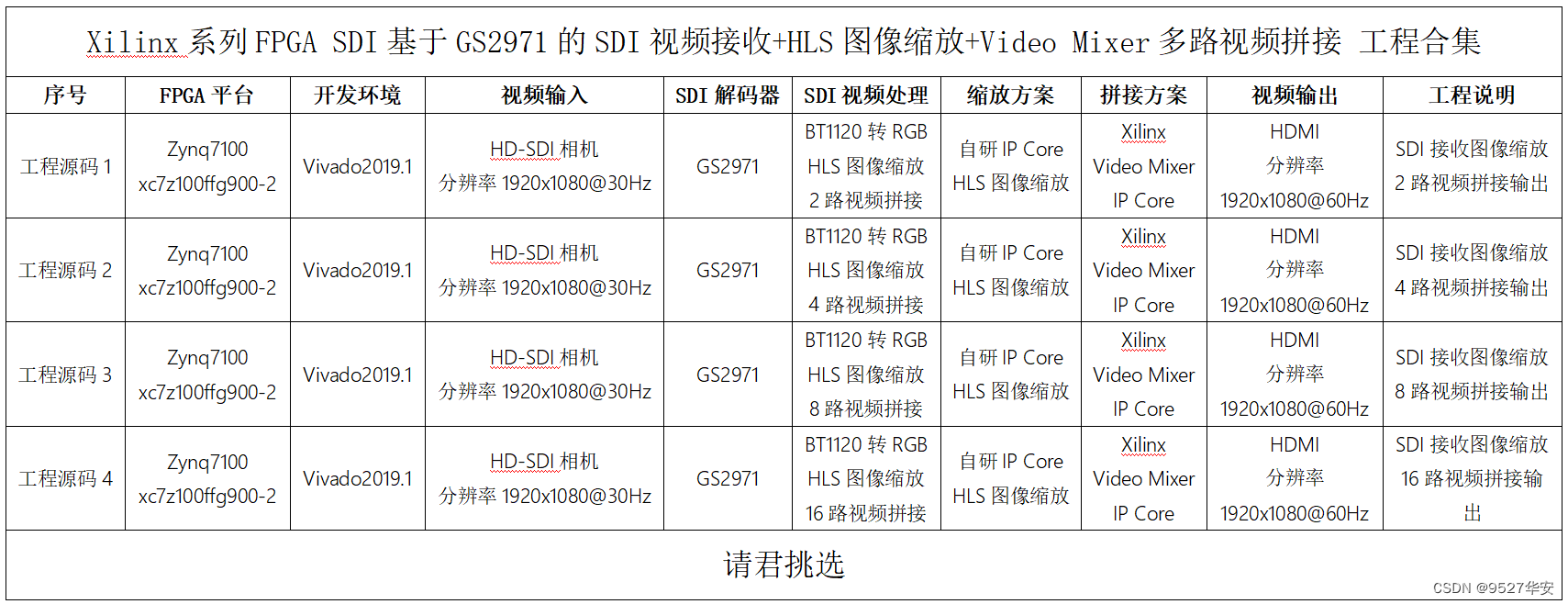

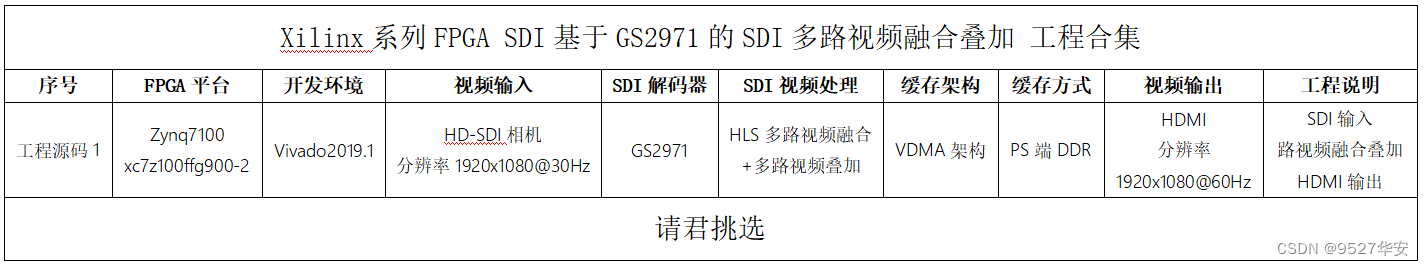

本方案的SDI HLS图像缩放+视频拼接应用

SDI视频解码后,可以进行多种图像处理,本应用就是HLS图像缩放+Video Mixer视频拼接,有的项目需要对SDI图像进行缩放拼接,本应用高度符合项目需求,提供4套工程源码,具体如下:

本方案的SDI视频编码+动态字符叠加输出应用

SDI视频解码后,可以进行动态字符叠加处理,该方案广泛应用于医疗和军工,本应用高度符合项目需求,提供1套工程源码,具体如下:

上述所有工程源码均已上板调试通过,详细设计说明等待本博更新对用的博客。。。

本方案的SDI视频编码多路视频融合+视频叠加应用

SDI视频解码后,可以进行多路视频融合+视频叠加处理,该方案广泛应用于医疗和军工,本应用高度符合项目需求,提供1套工程源码,具体如下:

上述所有工程源码均已上板调试通过,详细设计说明等待本博更新对用的博客。。。

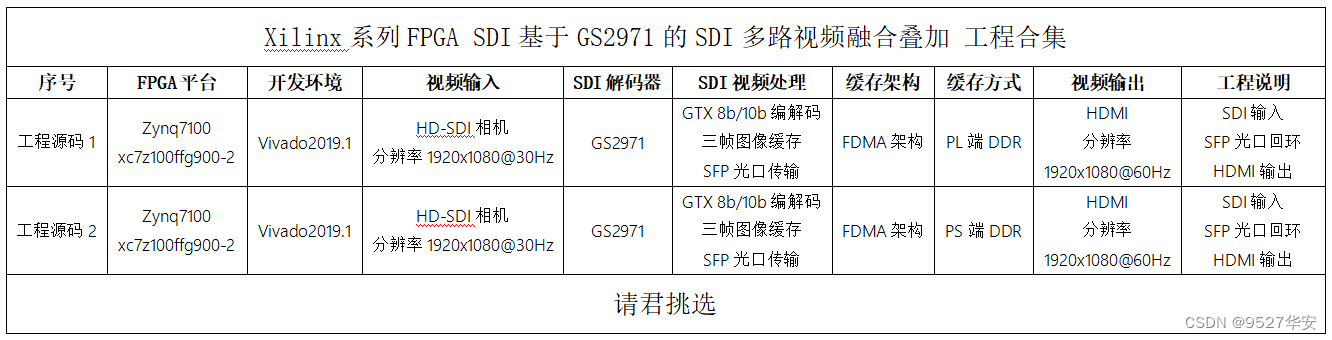

本方案的SDI视频编码GTX 8b/10b编解码SFP光口传输

SDI视频解码后,可以进行GTX 8b/10b编解码SFP光口传输,该方案广泛应用于医疗和军工,本应用高度符合项目需求,提供1套工程源码,具体如下:

上述所有工程源码均已上板调试通过,详细设计说明等待本博更新对用的博客。。。

FPGA的SDI视频编解码项目培训

基于目前市面上FPGA的SDI视频编解码项目培训较少的特点,本博专门开设了FPGA的SDI视频编解码高级项目培训班,专门培训SDI视频的编解码,具体培训计划细节如下:

1、我发你上述全套工程源码和对应的工程设计文档网盘链接,你保存下载,作为培训的核心资料;

2、你根据自己的实际情况安装好对应的开发环境,然后对着设计文档进行浅层次的学习;

3、遇到不懂的随时问我,包括代码、职业规划、就业咨询、人生规划、战略规划等等;

4、每周末进行一次腾讯会议,我会检查你的学习情况和面对面沟通交流;

5、你可以移植代码到你自己的FPGA开发板上跑,如果你没有板子,你根据你自己的需求修改代码后,编译工程,把bit发我,我帮你下载到我的板子上验证;或者你可以买我的开发板;

3、详细设计方案

设计原理框图

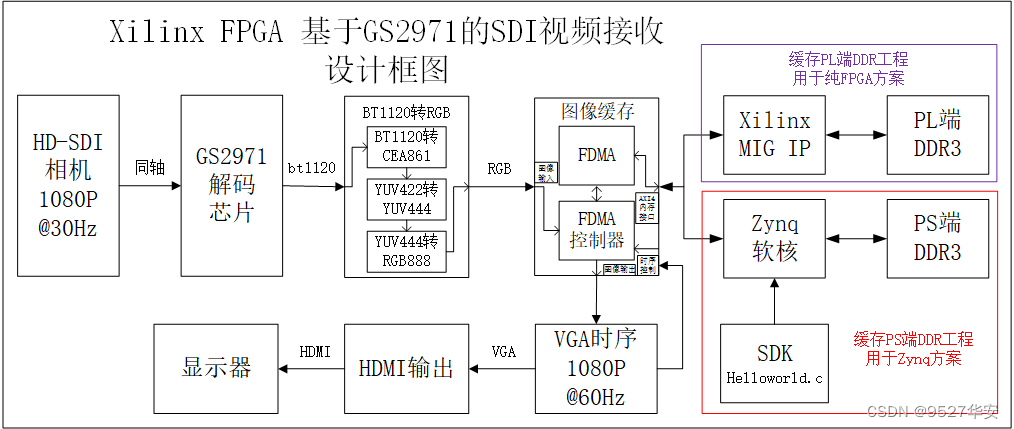

工程源码1、2的设计原理框图如下,该设计采用FDMA图像缓存方案:

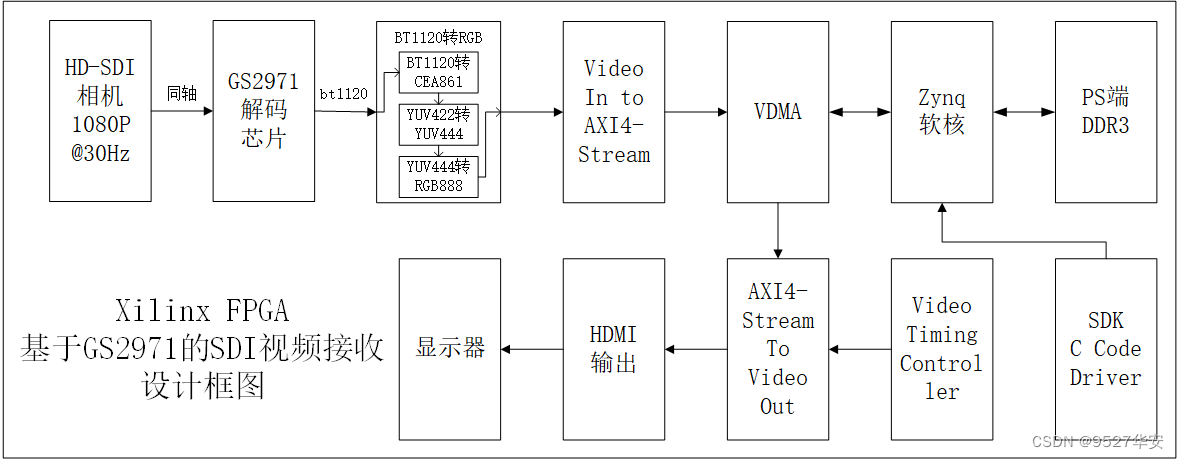

工程源码3的设计原理框图如下,该设计采用VDMA图像缓存方案:

SDI 相机

我用到的是SDI相机为HD-SDI相机,输出分辨率为1920x1080@30Hz,本工程对SDI相机的选择要求范围很宽,可以是SD-SDI、HD-SDI、3G-SDI,因为很设计对这三种SDI视频是自动识别并自适应的;如果你的手里没有SDI相机,也可以去某宝买HDMI转SDI盒子,一百多块钱就可以搞定,使用笔记本电脑模拟视频源,用HDMI线连接HDMI转SDI盒子,输出SDI视频做事视频源,可以模拟SDI相机;

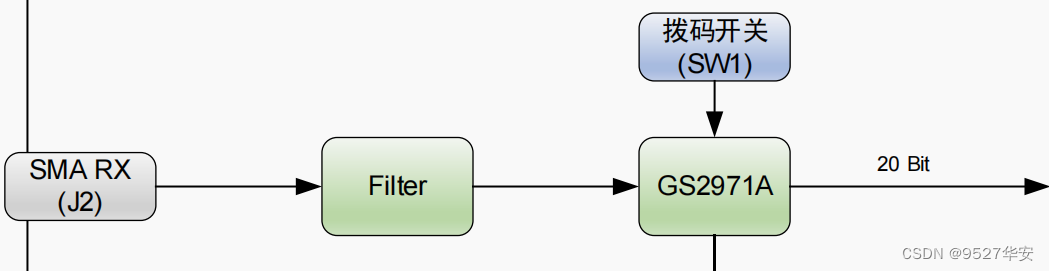

GS2971

本设计采用GS2971芯片解码SDI,GS2971不需要软件配置,硬件电阻上下拉即可完成配置,本设计配置为输出BT1120格式视频,当然,你在设计电路时也可以配置为输出CEA861格式视频;GS2971硬件架构如下,提供PDF格式原理图:

BT1120转RGB

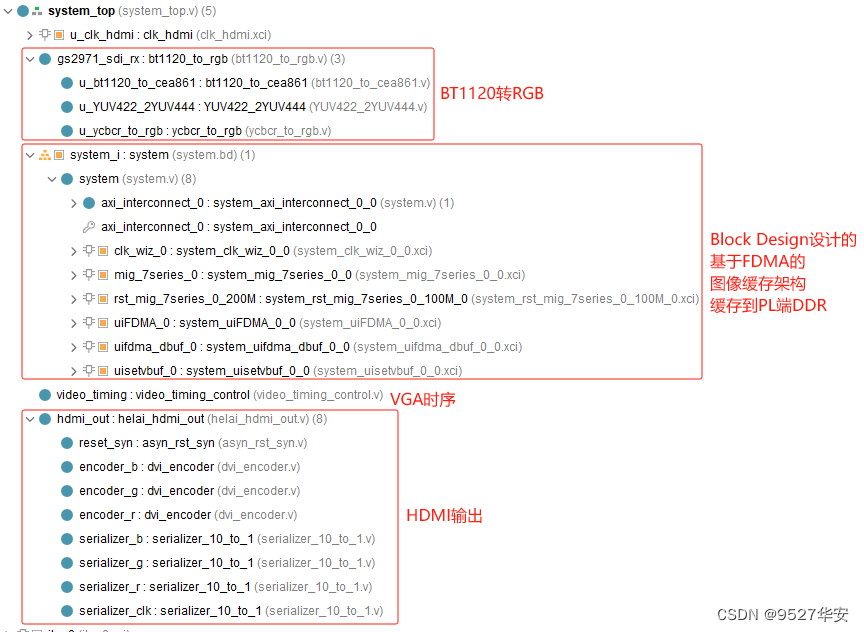

BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

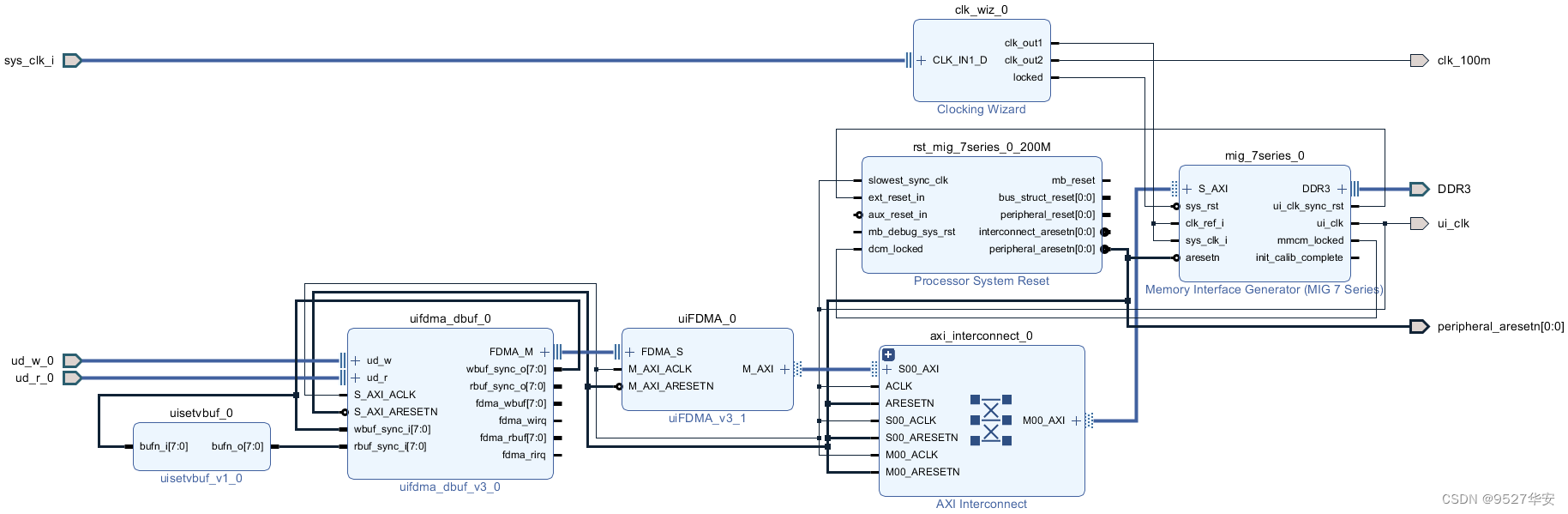

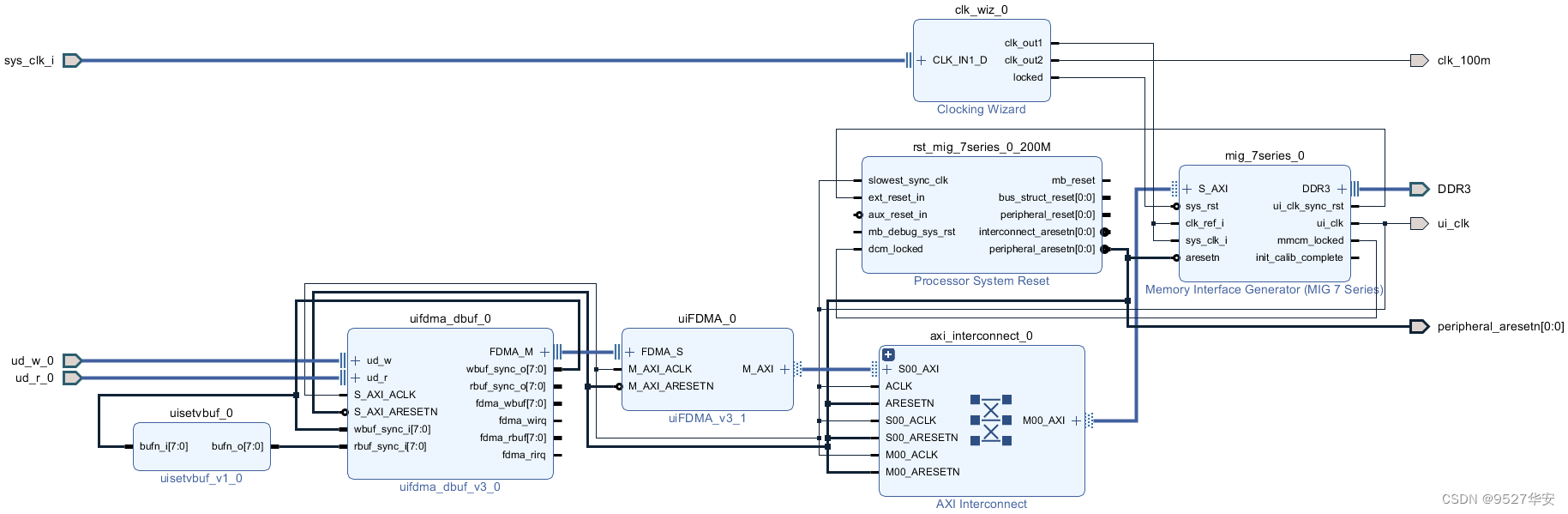

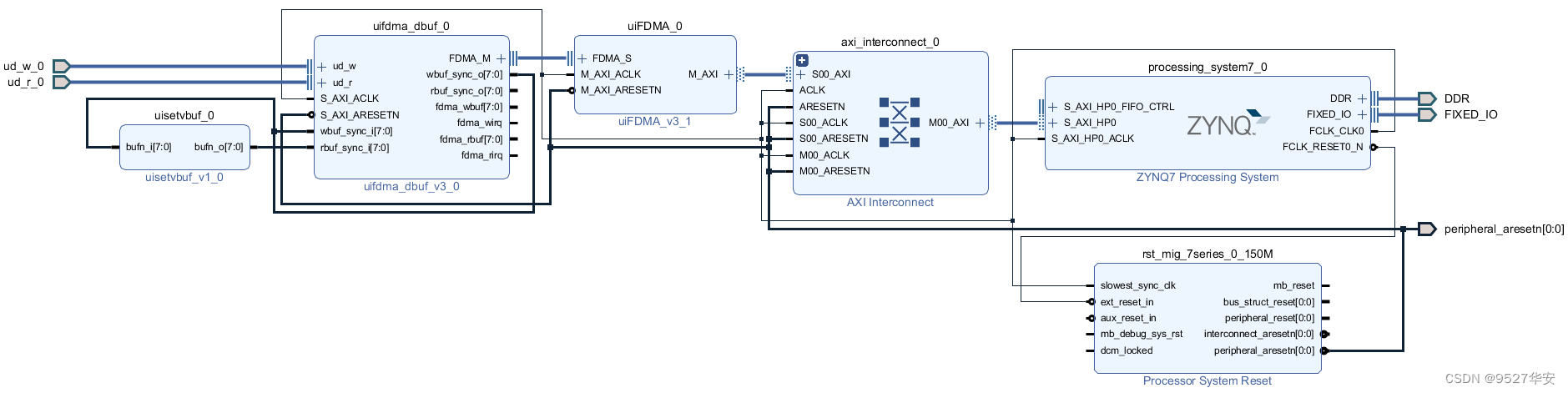

图像缓存

FDMA架构使用本博常用的FDMA图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR3;FDMA图像缓存架构由FDMA、FDMA控制器、缓存帧选择器构成、Xilinx MIG IP核(PL端)、Zynq软核(PS端)构成;图像缓存使用Xilinx vivado的Block Design设计,以工程源码1为例如下图:

关于FDMA更详细的介绍,请参考我之前的博客,博文链接如下:

点击直接前往

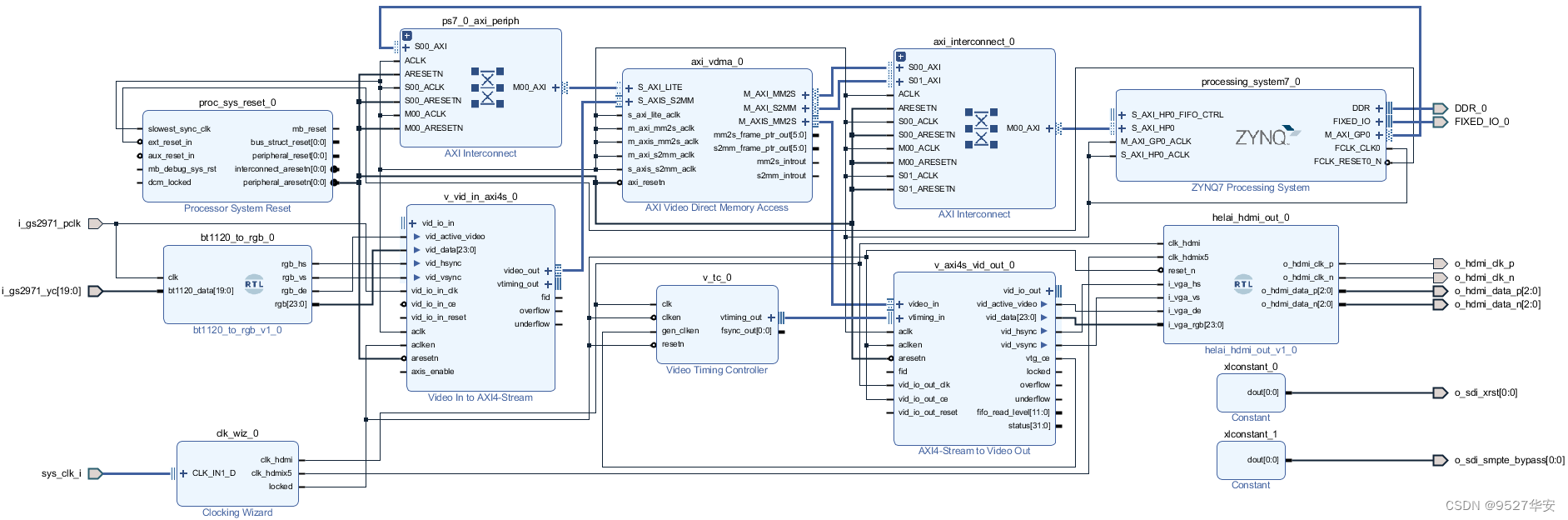

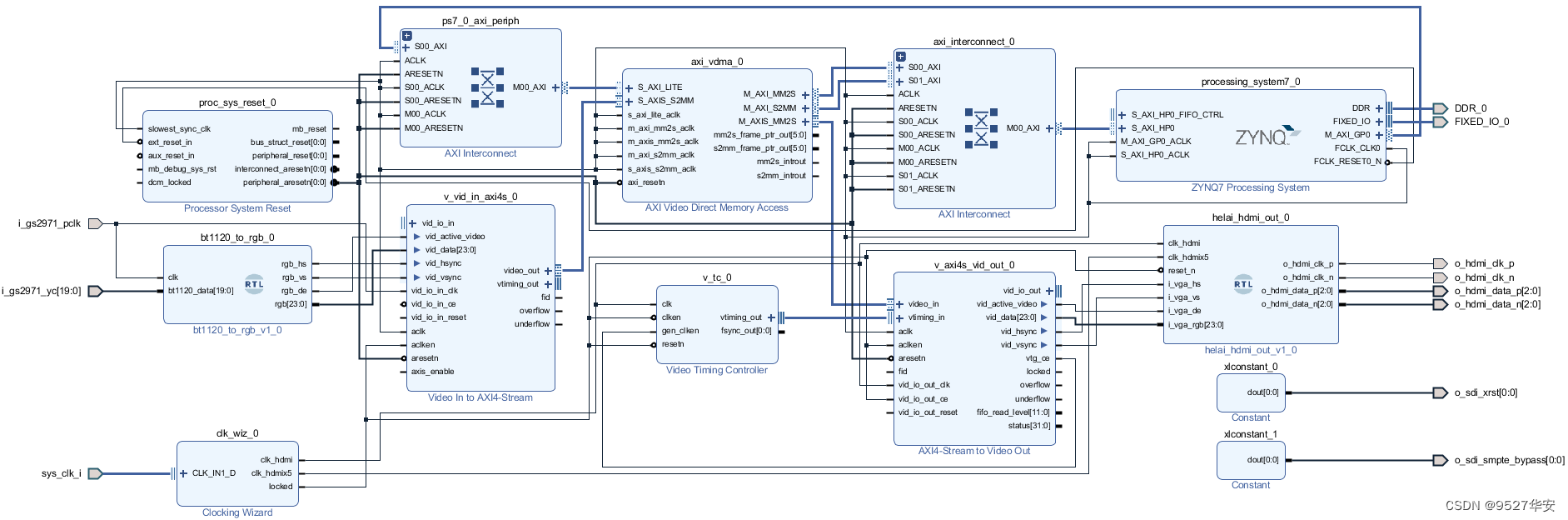

VDMA架构使用Xilinx官方力推的VDMA图像缓存架构实现图像3帧缓存,缓存介质为板载的PS端DDR3;VDMA图像缓存架构由Video In to AXI4-Stream、VDMA、Zynq软核、Video Timing Controller、AXI4-Stream To Video Out构成;图像缓存使用Xilinx vivado的Block Design设计,如下图:

HDMI输出

HDMI输出架构由VGA时序和HDMI输出模块构成,VGA时序负责产生输出的1920x1080@60Hz的时序,并控制FDMA数据读出,HDMI输出模块负责将VGA的RGB视频转换为差分的TMDS视频,代码架构如下:

HDMI输出模块采用verilog代码手写,可以用于FPGA的HDMI发送应用,关于这个模块,请参考我之前的博客,博客地址:点击直接前往

工程1–>源码架构

工程源码1使用FDMA图像缓存架构,Block Design和源码架构如下,Block Design设计为图像缓存架构的部分,缓存PL端DDR3:

工程2–>源码架构

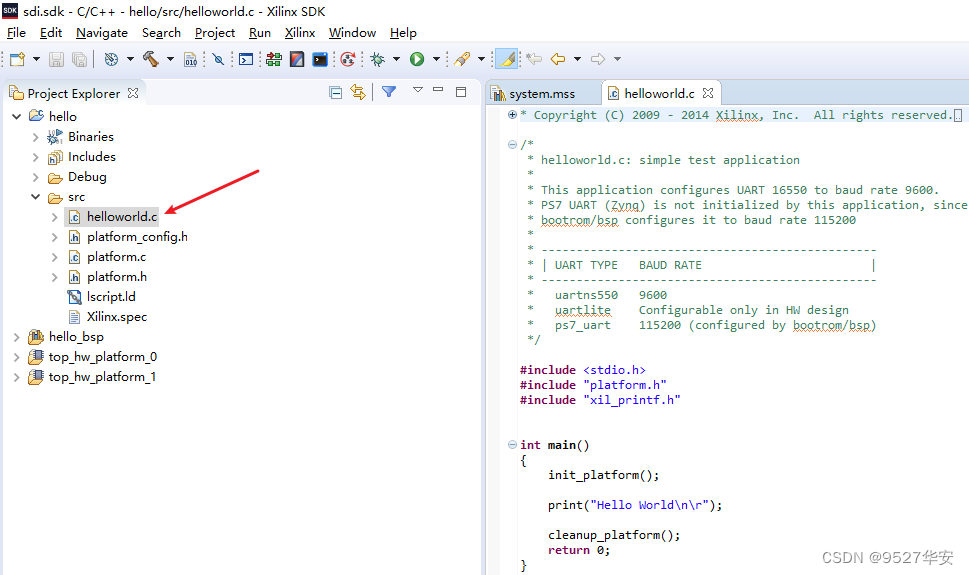

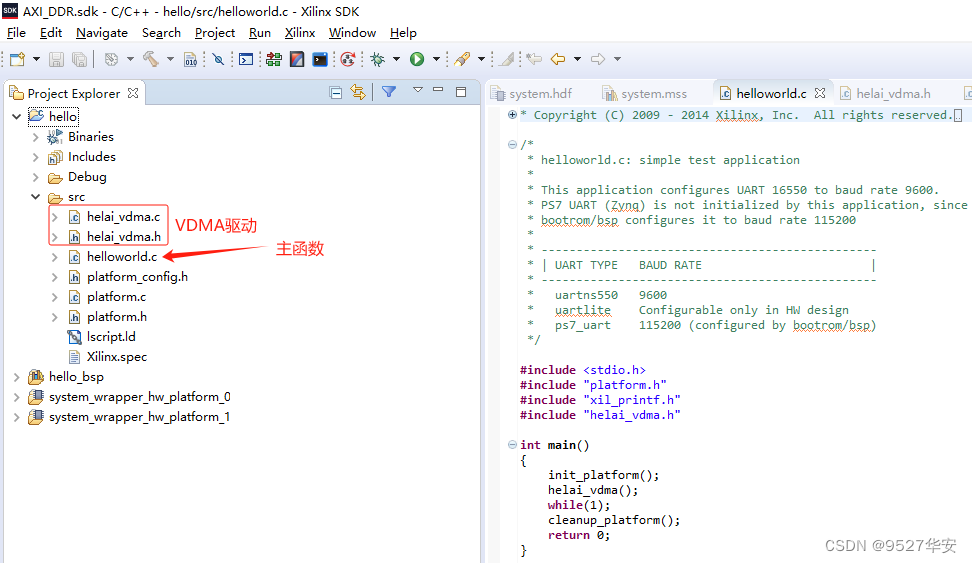

工程源码2使用FDMA图像缓存架构,Block Design和源码架构如下,Block Design设计为图像缓存架构的部分,缓存PS端DDR3,因此,需要运行SDK才能启动Zynq软核,但SDK仅需运行一个简单的helloworld.c即可:

工程2使用了自定义的FDMA方案,虽然不需要SDK配置,但FDMA的AXI4接口时钟由Zynq提供,所以需要运行SDK程序才能启动Zynq,从而为PL端逻辑提供时钟;由于不需要SDK配置,所以SDK软件代码就变得极度简单,只需运行一个“Hello World”即可,如下:

工程3–>源码架构

工程源码3使用VDMA图像缓存架构,Block Design和源码架构如下,Block Design设计为图像缓存架构的部分,缓存PS端DDR3,因此,需要运行SDK才能启动Zynq软核,SDK需运行VDMA的驱动:

SDK代码架构如下:

4、工程源码1详解–>SDI转HDMI–FDMA缓存PL端DDR3

开发板FPGA型号:Xilinx–Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:HD-SDI相机,分辨率1920x1080@30Hz;

输出:HDMI ,分辨率1920x1080@60Hz;

图像缓存方案:FDMA方案;

图像缓存路径:PL端DDR3;

工程作用:此工程目的是让读者掌握FPGA实现SDI转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节“工程1–>源码架构“小节内容;

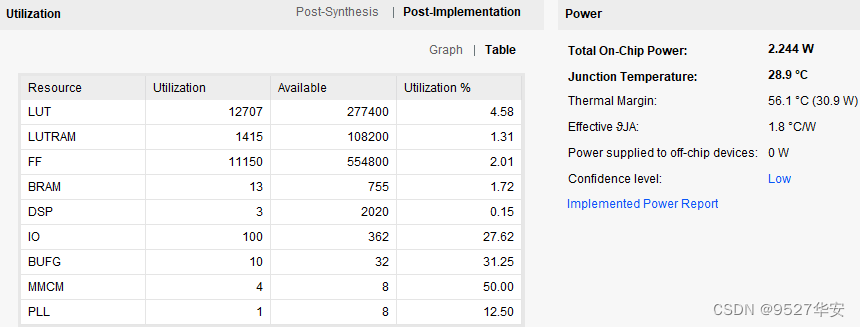

工程的资源消耗和功耗如下:

5、工程源码2详解–>SDI转HDMI–FDMA缓存PS端DDR3

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:HD-SDI相机,分辨率1920x1080@30Hz;

输出:HDMI ,分辨率1920x1080@60Hz;

图像缓存方案:FDMA方案;

图像缓存路径:PS端DDR3;

工程作用:此工程目的是让读者掌握FPGA实现SDI转SDI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节“工程2–>源码架构“小节内容;

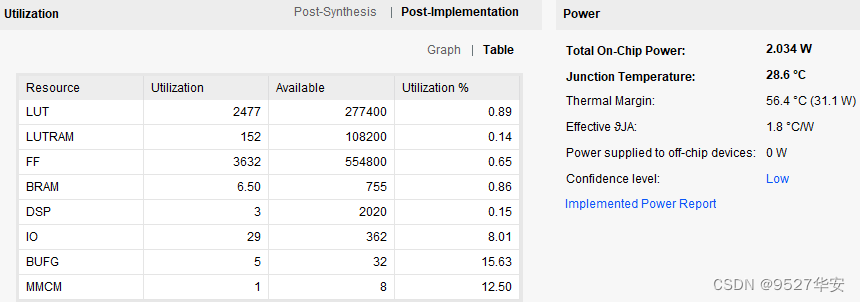

工程的资源消耗和功耗如下:

6、工程源码3详解–>SDI转HDMI–VDMA缓存PS端DDR3

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:HD-SDI相机,分辨率1920x1080@30Hz;

输出:HDMI ,分辨率1920x1080@60Hz;

图像缓存方案:VDMA方案;

图像缓存路径:PS端DDR3;

工程作用:此工程目的是让读者掌握FPGA实现SDI转SDI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节“工程3 -->源码架构“小节内容;

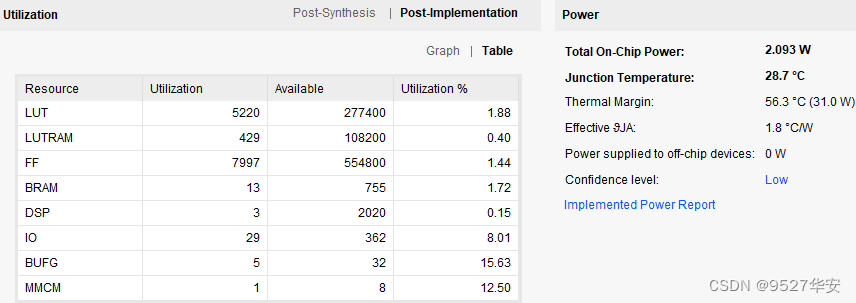

工程的资源消耗和功耗如下:

7、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

8、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板;

SDI摄像头;

HDMI显示器;

我的开发板了连接如下:

输出视频演示

以工程1为例,输出如下,工程2、3输出效果与之一样:

GS2971接收SDI视频HDMI输出

9、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA高端项目:FPGA基于GS2971的SDI视频接收转HDMI输出,提供3套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐本博已有的 SDI 编解码方案本方案的SDI图像缩放应用本方案的SDI纯verilog图像缩放视频拼接应用本方案的SDI HLS图像缩放视频拼接应用本方案的SDI视频编码动态字符叠加输出应用本方案的SDI视频编码多路视频融合视频叠加应用本方案的SDI视频…...

java 锁

在Java中,有多种类型的锁,用于处理多线程编程中的同步和并发问题。以下是Java中常见的锁类型:互斥同步锁(悲观锁) :Synchronized : Java中最基本的同步机制,它提供了一种简单且透明的方式来同步代码块或方法。Synchronized是基于进入和退出监视器对象(monitor)来实现方…...

该类型的 CollectionView 不支持从调度程序线程以外的线程对其 SourceCollection 进行的更改。

报错原因 在异步的时候,调用了其他异步,导致UI工程线程该变了数据源,所以只需要将线程变为原始的UI线程。 解决方案 await QueuedTask.Run(() > { Application.Current.Dispatcher.Invoke(() >{报错的代码,…...

Mybatis学习笔记:延迟加载

本文是自己的学习笔记,主要参考以下资料 - 马士兵教育 1、延迟加载2、开启延迟加载2.1、配置信息2.2、查询语法2.2.1、前置条件2.2.2、xml语法2.2.3、总结 1、延迟加载 延迟加载是用于优化一对多或者多对多的查询。 比如员工表和部门表,员工表left jo…...

蓝桥杯题练习:平地起高楼

题目要求 function convertToTree(regions, rootId "0") {// TODO: 在这里写入具体的实现逻辑// 将平铺的结构转化为树状结构,并将 rootId 下的所有子节点数组返回// 如果不存在 rootId 下的子节点,则返回一个空数组}module.exports convert…...

我愿意启动价值流

如前文Flow近佛,人生就是一个价值流。让价值流动起来,Get Things Flow是我们的方法论。然而,还欠上帝的一脚,让价值流启动起来。这个启动,就是我愿意。 我愿意的反面是被烦恼包裹、裹挟、包围、无法摆脱。乐莹离家前就…...

排序算法1:冒泡排序、快速排序、插入排序

排序算法:交换类排序,插入类排序、选择类排序、归并类排序 交换类排序:冒泡排序、快速排序 一、冒泡排序 #include <stdio.h> #include <stdlib.h> #include <time.h> typedef int ElemType; typedef struct{ElemType *e…...

Vant Weapp

Vant Weapp - 轻量、可靠的小程序 UI 组件库 van-radio name 是一个字符串,无法传对象的处理 以及 mpx 多层嵌套 for 循环处理 <viewwx:for"{{questionList}}"wx:for-item"question" // item 重命名wx:for-index"questionIndex"…...

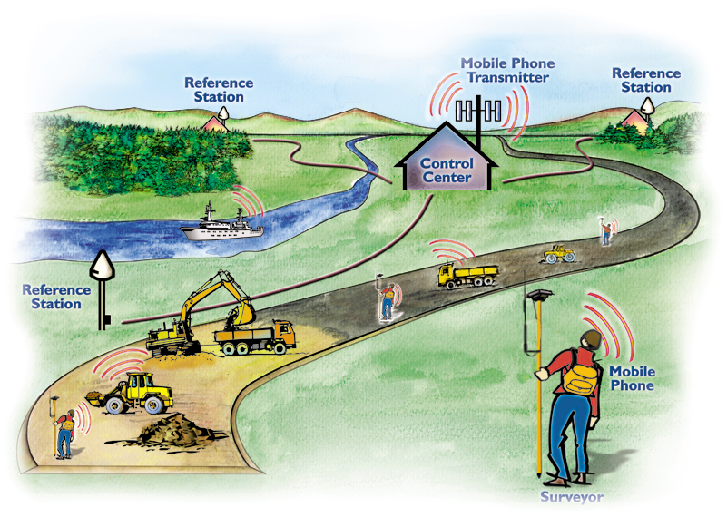

无人机精准定位技术,GPS差分技术基础,RTK原理技术详解

差分GPS的基本原理 差分GPS(Differential GPS,简称DGPS)的基本原理是利用一个或多个已知精确坐标的基准站,与用户(移动站)同时接收相同的GPS卫星信号。由于GPS定位时会受到诸如卫星星历误差、卫星钟差、大…...

java面试:elasticsearch

文章目录 引言I 索引1.1 覆盖索引1.2 elasticsearch 面试题1.3 Google的搜索本质II elasticsearch的倒叙索引2.1 发展历史2.2 倒排索引2.3 倒排序的搜索流程III elasticsearch的基础概念IV 创建索引库4.1 步骤4.2 mapping映射4.3 ik分词器...

(三))

GO语言学习笔记(与Java的比较学习)(三)

函数 按值传递(call by value) 按引用传递(call by reference) Go 默认使用按值传递来传递参数,也就是传递参数的副本。函数接收参数副本之后,在使用变量的过程中可能对副本的值进行更改,但不…...

如何用Python3自撰一个简单的后端框架

不使用任何现有的后端框架来创建一个Python 3的后端框架是一个相当复杂的任务,因为它涉及到许多Web开发的基础知识,比如HTTP协议处理、路由、中间件、请求和响应处理等。然而,我们可以从最基本的概念开始,逐步构建一个简单的后端框架。 以下是一个非常基础的指南,用于创建…...

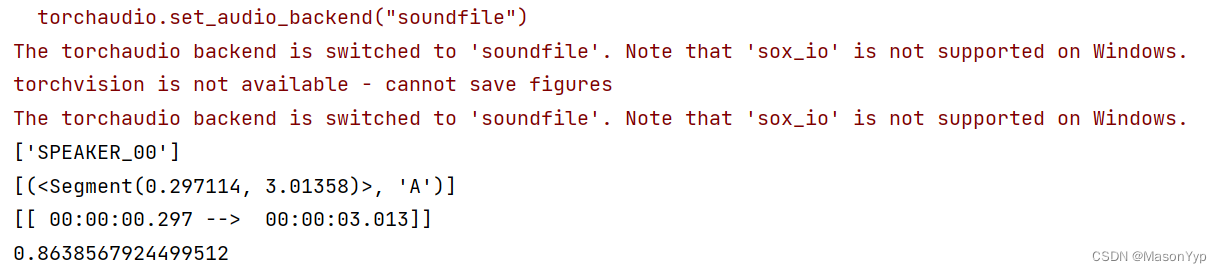

使用pyannote-audio实现声纹分割聚类

使用pyannote-audio实现声纹分割聚类 # GitHub地址 https://github.com/MasonYyp/audio1 简单介绍 pyannote.audio是用Python编写的用于声纹分割聚类的开源工具包。在PyTorch机器学习基础上,不仅可以借助性能优越的预训练模型和管道实现声纹分割聚类,还…...

防御保护:防火墙内容安全

一、IAE(Intelligent Awareness Engine)引擎 二、深度检测技术(DFI和DPI) 1.DPI – 深度包检测技术 DPI主要针对完整的数据包(数据包分片,分段需要重组),之后对数据包的内容进行识别。&#x…...

uni-app webview 打开baidu.com

在uni-app中,你可以使用web-view组件来打开外部网页,比如百度首页。以下是一个简单的示例代码,展示了如何在uni-app中使用web-view组件打开百度首页: <template> <view> <web-view :src"baiduUrl">&l…...

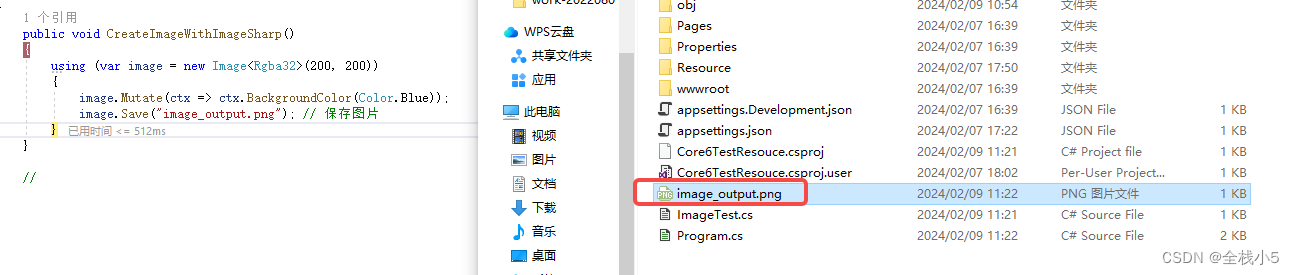

【C#】SixLabors.ImageSharp和System.Drawing两者知多少

欢迎来到《小5讲堂》 大家好,我是全栈小5。 这是《C#》系列文章,每篇文章将以博主理解的角度展开讲解, 特别是针对知识点的概念进行叙说,大部分文章将会对这些概念进行实际例子验证,以此达到加深对知识点的理解和掌握。…...

总是 -bash: gomobile: 命令未找到

总是 -bash: gomobile: 命令未找到 问题描述 我的项目是/Users/$user/go/src/abc.com/project 当我尝试在 /Users/GaryChan/go/src/abc.com/project/sdk 并运行: export ANDROID_HOME/Users/$user/Library/Android/sdk/ndk-bundle/gomobile bind -targetandroid abc.com/p…...

day27【LeetCode】454. 四数相加 II

day27【LeetCode】454. 四数相加 II 1.题目描述 附上题目链接:四数相加 II 给你四个整数数组 nums1、nums2、nums3 和 nums4 ,数组长度都是 n ,请你计算有多少个元组 (i, j, k, l) 能满足: 0 < i, j, k, l < nnums1[i] …...

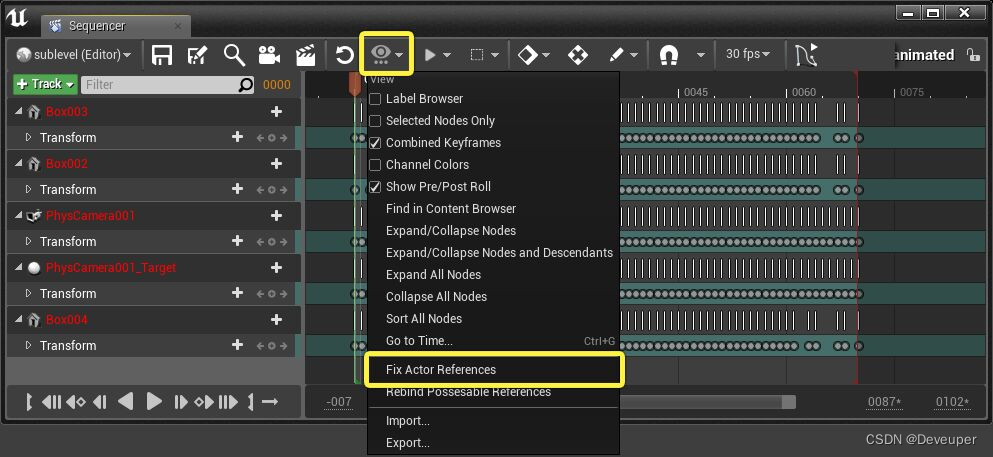

UE5 UE4 不同关卡使用Sequence动画

参考自:关于Datasmith导入流程 | 虚幻引擎文档 (unrealengine.com) 关卡中的Sequence动画序列,包含特定关卡中的Actor的引用。 将同一个Sequcen动画资源放入其他关卡,Sequence无法在新关卡中找到相同的Actor,导致报错。 Sequen…...

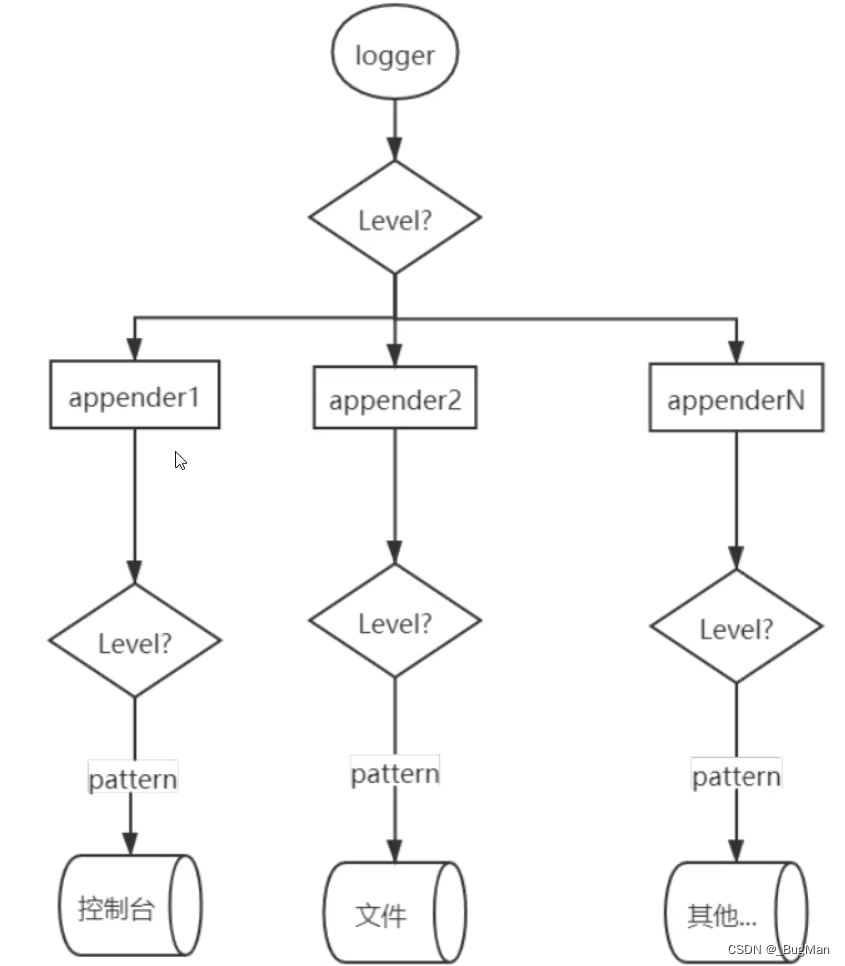

【JAVA日志】关于日志系统的架构讨论

目录 1.日志系统概述 2.环境搭建 3.应用如何推日志到MQ 4.logstash如何去MQ中取日志 5.如何兼顾分布式链路追踪 1.日志系统概述 关于日志系统,其要支撑的核心能力无非是日志的存储以及查看,最好的查看方式当然是实现可视化。目前市面上有成熟的解决…...

)

ENVI 5.3 实战:手把手教你用Landsat 7数据反演城市热岛效应(附完整Band Math公式)

ENVI 5.3实战:城市热岛效应分析的完整技术路线与创新应用 城市热岛效应是当代城市规划与环境监测领域的重要课题。当我们在ENVI软件中打开一张Landsat 7影像时,那些看似普通的像素值背后隐藏着城市热环境的秘密。本文将带您走完从原始数据到热岛分析的全…...

实现更灵活的图片拼接(附完整代码))

别再只会用cv2.warpPerspective了!用OpenCV-Python的cv2.remap()实现更灵活的图片拼接(附完整代码)

解锁OpenCV图像拼接新姿势:cv2.remap()的进阶实战指南 在计算机视觉项目中,图像拼接是最基础却又最考验功底的环节。许多开发者习惯性地使用cv2.warpPerspective完成透视变换,但当遇到非矩形区域拼接、复杂边界融合等场景时,这种标…...

互联网大厂 Java 求职面试:音视频场景中的开发与挑战

互联网大厂 Java 求职面试:音视频场景中的开发与挑战第一轮提问面试官: 燕双非,首先让我们讨论一下在音视频场景中的架构设计,你认为使用 Spring Boot 和 Kafka 来构建一个实时音视频服务的优势是什么? 燕双非…...

Bilibili-Evolved终极指南:简单三步打造你的专属B站体验

Bilibili-Evolved终极指南:简单三步打造你的专属B站体验 【免费下载链接】Bilibili-Evolved 强大的哔哩哔哩增强脚本 项目地址: https://gitcode.com/gh_mirrors/bi/Bilibili-Evolved Bilibili-Evolved是一款强大的哔哩哔哩增强脚本,专为提升B站用…...

从LLM到CodeSummarizer:2026奇点大会公布的3层抽象蒸馏模型,如何将PR评审效率提升400%?

第一章:2026奇点智能技术大会:AI代码摘要 2026奇点智能技术大会(https://ml-summit.org) 核心发布:CodeLens-7 智能摘要引擎 大会首次开源 CodeLens-7,一款面向多语言、跨上下文的轻量级代码语义摘要模型。它支持 Python、Go、R…...

DAMO-YOLO实战教程:拖拽上传+实时统计,工业级视觉系统轻松上手

DAMO-YOLO实战教程:拖拽上传实时统计,工业级视觉系统轻松上手 1. 五分钟部署工业级视觉系统 你是否厌倦了复杂的模型部署流程?DAMO-YOLO智能视觉探测系统彻底改变了传统目标检测的使用体验。这套由阿里达摩院开发的系统,将高性能…...

Phi-3-mini-4k-instruct-gguf详细步骤:GGUF模型加载、CUDA推理加速与响应延迟优化

Phi-3-mini-4k-instruct-gguf详细步骤:GGUF模型加载、CUDA推理加速与响应延迟优化 1. 模型简介与环境准备 Phi-3-mini-4k-instruct-gguf是微软推出的轻量级文本生成模型,特别适合问答、文本改写和摘要生成等场景。这个GGUF格式的版本经过优化ÿ…...

零基础玩转intv_ai_mk11:手把手教你搭建个人AI问答助手

零基础玩转intv_ai_mk11:手把手教你搭建个人AI问答助手 1. 前言:为什么选择intv_ai_mk11 在人工智能技术快速发展的今天,拥有一个属于自己的AI问答助手变得越来越简单。intv_ai_mk11作为一款基于Llama架构的中等规模文本生成模型࿰…...

Windows右键菜单终极清理指南:ContextMenuManager五分钟快速上手

Windows右键菜单终极清理指南:ContextMenuManager五分钟快速上手 【免费下载链接】ContextMenuManager 🖱️ 纯粹的Windows右键菜单管理程序 项目地址: https://gitcode.com/gh_mirrors/co/ContextMenuManager 你是否曾经因为右键菜单过于臃肿而感…...

Stable Yogi Leather-Dress-Collection自动化流程:使用Python脚本批量生成商品图

Stable Yogi Leather-Dress-Collection自动化流程:使用Python脚本批量生成商品图 每次上新都要找设计师做几十张商品图,费时又费钱?产品图风格不统一,影响品牌形象?如果你在电商或内容创作团队,这些问题肯…...