Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(二)

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(前导)

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(一)

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(三)

五、实验目的

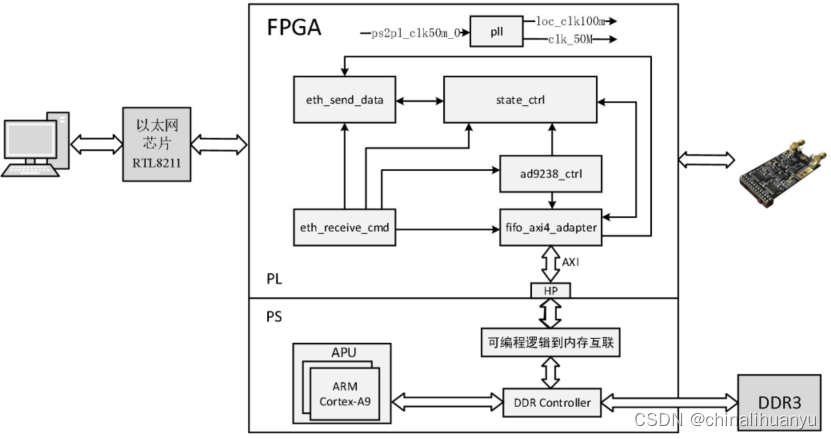

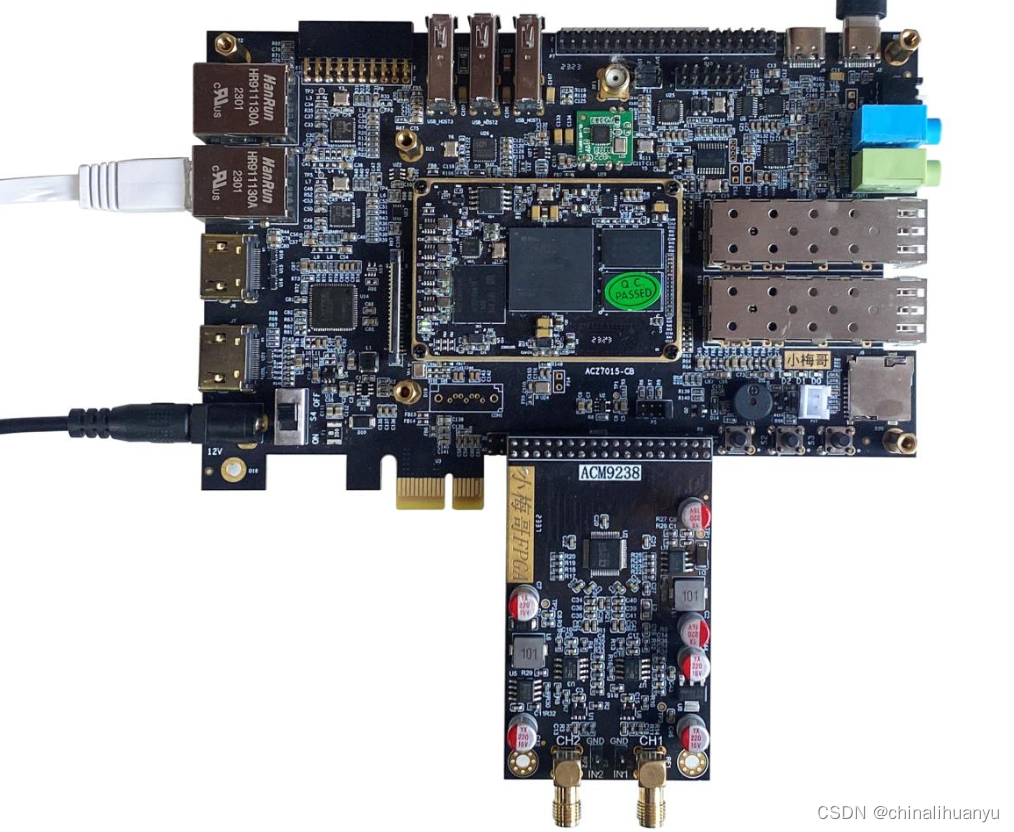

本次实验使用电脑上的网络调试助手,将命令帧通过以太网芯片RTL8211(RGMII接口)发送至ACZ7015开发板,提取UDP报文内容转换成控制命令,从而实现对ACM9238模块采样频率、数据采样个数以及采样通道的配置。

配置完成之后,ACM9238模块开始采集数据,将采集的数据存储至DDR3中,然后通过网口以UDP协议传输到电脑。用户可以在电脑上通过网口调试工具进行指令的下发,并以文件的形式保存接收到的数据,然后使用MATLAB软件进行进一步的数据处理分析。

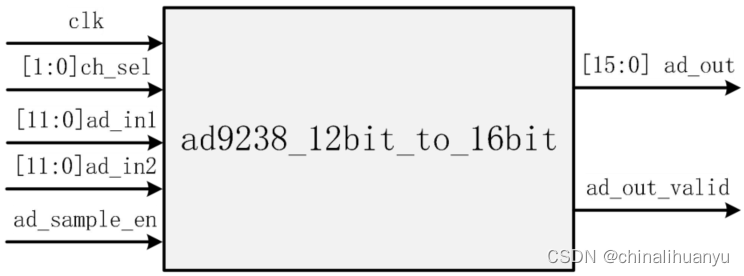

PL 部分的模块说明如下:

- pll 模块: 锁相环模块, 输入时钟 50M, 由 PS 输出给 PL; 输出 100M 的时钟给到 DDR3 控制器使用; 输出 50M 的时钟给其它模块使用。

- eth_receive_cmd 模块: 以太网接收命令模块, 对以太网接收到的数据进行分析, 将接收的数据转换成相应的控制数据并输出到对应的模块。

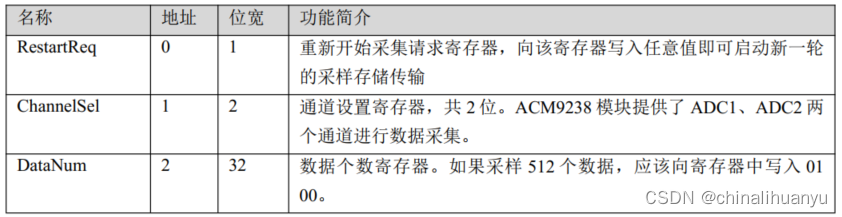

- ad9238_ctrl 模块: ACM9238 控制器模块, 该模块内部包含速度控制模块,以及数据位宽转换模块。

- state_ctrl 模块: ADC 采集数据 DDR3 缓存以太网发送状态控制模块, 协调各个模块的信号控制, 程序状态的总控制模块。

- fifo_axi4_adapter 模块: fifo 接口到 AXI4 接口的转换模块(含 2 个 FIFO)。

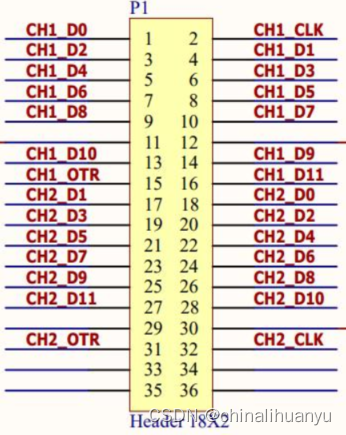

六、ACM9238模块

两路,

采样上限50Msps,如果期望以1Msps 的采样速率采样, 则只需要每间隔 50 个采样数据取一个结果存储或使用, 其他 49 个数据直接舍弃。不建议降低ADC芯片的时钟信号。

七、设计实例

7.1模块设计

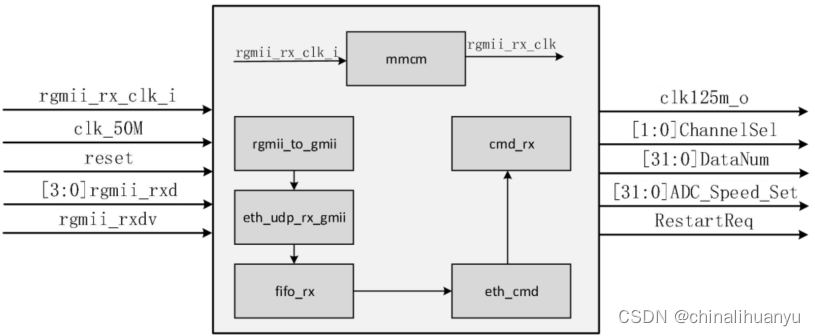

7.1.1 eth_receive_cmd模块

将以太网接收到的数据进行解析, 得到控制命令。

(1)eth_udp_rx_gmii模块和rgmii_to_gmii模块

(2)mmcm模块

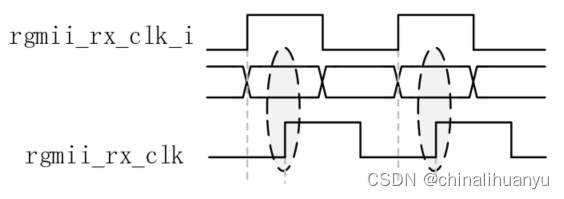

锁相环模块,将 rgmii 接口时钟信号 rgmii_rx_clk_i 偏移90 °得到 rgmii_rx_clk 时钟信号。(为了在时钟信号的上升沿/下降沿取数据时,取得数据刚好是数据信号 rgmii_rxd 的正中间, 使得采样的数据处于最稳定的状态。)

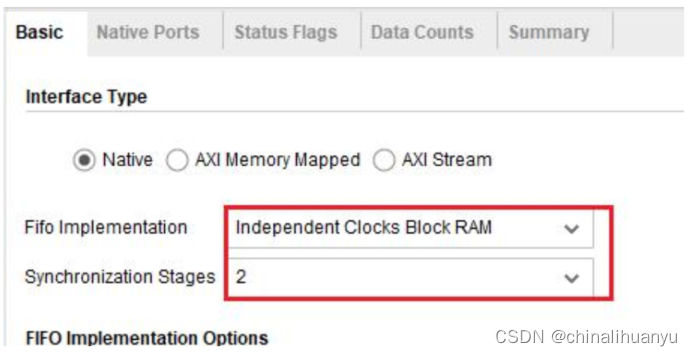

锁相环IP配置

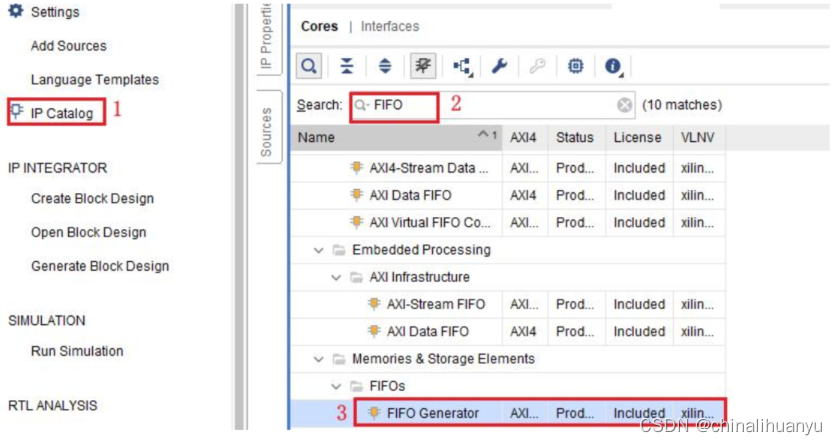

(3)fifo_rx模块

使用该 IP 核解决采集过程中会出现的跨时钟域数据交互问题(以太网125MHz,ACM9238-50MHz)。

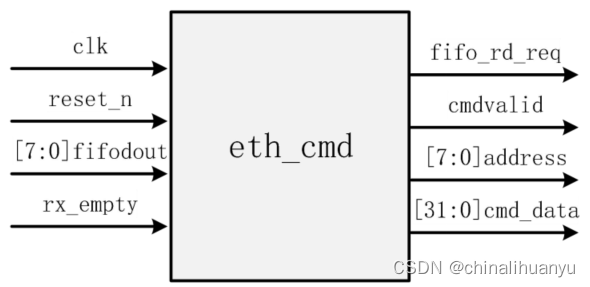

(4)eth_cmd模块

接收转命令模块。

//非空时产生FIFO读请求信号

always@(posedge clk or negedge reset_n)

if(!reset_n)fifo_rd_req <= 1'b0;

else if(!rx_empty)fifo_rd_req <= 1'b1;

elsefifo_rd_req <= 1'b0;//获得帧命令数据

always@(posedge clk)

if(fifo_rd_req)begindata_0[7] <= #1 fifodout;data_0[6] <= #1 data_0[7];data_0[5] <= #1 data_0[6];data_0[4] <= #1 data_0[5];data_0[3] <= #1 data_0[4];data_0[2] <= #1 data_0[3];data_0[1] <= #1 data_0[2];data_0[0] <= #1 data_0[1];

end//判断帧命令数据

always@(posedge clk or negedge reset_n)

if(!reset_n)beginaddress <= 0;cmd_data <= 32'd0;cmdvalid <= 1'b0;

end

else if(fifo_rx_done)beginif((data_0[0]==8'h55)&&(data_0[1]==8'hA5)&&(data_0[7]==8'hF0))begincmd_data[7:0] <= #1 data_0[6];cmd_data[15:8] <= #1 data_0[5];cmd_data[23:16] <= #1 data_0[4];cmd_data[31:24] <= #1 data_0[3];address <= #1 data_0[2];cmdvalid <= #1 1;endelsecmdvalid <= #1 0;

end

else

cmdvalid <= #1 0;(5)cmd_rx模块

接收数据转换为控制数据。

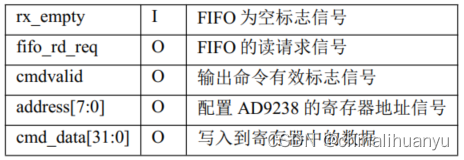

寄存器说明:

always@(posedge clk or negedge reset_n)

if(!reset_n)beginChannelSel <= 2'b00;DataNum <= 32'd0;ADC_Speed_Set <= 32'd0;RestartReq <= 1'b0;

end

else if(cmdvalid)begincase(cmd_addr)0: RestartReq <= 1'b1;1: ChannelSel <= cmd_data[1:0];2: DataNum <= cmd_data[31:0];3: ADC_Speed_Set <= cmd_data[31:0];default:;endcase

end

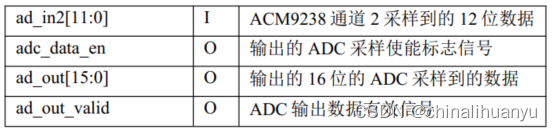

elseRestartReq <= 1'b0;7.1.2 ad9238_ctrl 模块

控制ADC的采样速率,将12位数据转换为16位数据。

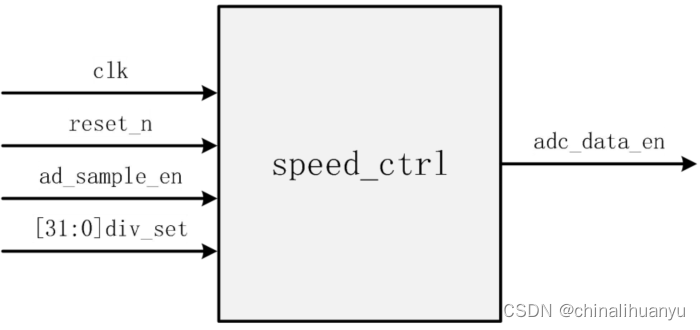

(1)speed_ctrl模块

always@(posedge clk or negedge reset_n)

if(!reset_n)div_cnt <= 0;

else if(ad_sample_en)beginif(div_cnt >= div_set)div_cnt <= 0;elsediv_cnt <= div_cnt + 1'd1;

end

elsediv_cnt <= 0;always@(posedge clk or negedge reset_n)

if(!reset_n)adc_data_en <= 0;

else if(div_cnt == div_set)adc_data_en <= 1;

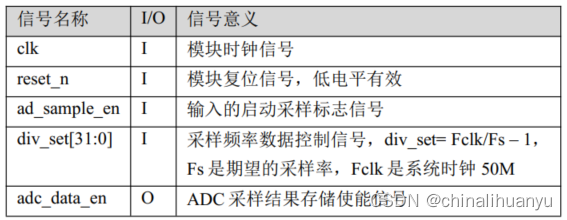

elseadc_data_en <= 0;(2)ad_12bit_to_16bit模块

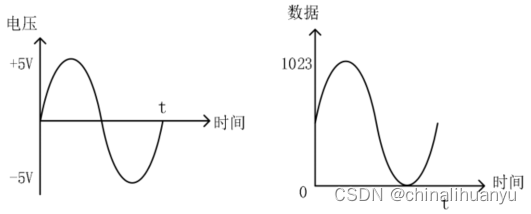

always @(posedge clk)ad_out_valid <= ad_sample_en;assign s_ad_in1 = ad_in1 + 12'd2048;

assign s_ad_in2 = ad_in2 + 12'd2048;always @(posedge clk)

if(ad_sample_en && ch_sel == 2'b01)ad_out<={4'd0,s_ad_in1};//这样补 0 为了适应上位机

else if(ad_sample_en && ch_sel == 2'b10)ad_out<={4'd0,s_ad_in2};//

else if(ad_sample_en && ch_sel == 2'b00)ad_out<={4'd0,adc_test_data};

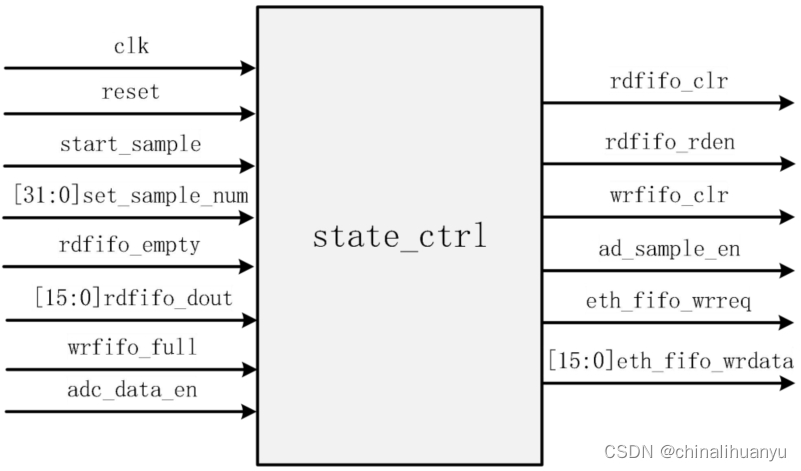

elsead_out <= 16'd0;7.1.3 state_ctrl 模块

控制信号的产生以及 ADC 何时启动数据传输。

localparam IDLE = 4'd0; //空闲状态

localparam DDR_WR_FIFO_CLEAR = 4'd1; //DDR 写 FIFO 清除状态

localparam ADC_SAMPLE = 4'd2; //ADC 采样数据状态

localparam DDR_RD_FIFO_CLEAR = 4'd3; //DDR 读 FIFO 清除状态

localparam DATA_SEND_START = 4'd4; //数据发送状态

localparam DATA_SEND_WORKING = 4'd5; //数据发送完成状态(1)IDLE

//ADC 模块开始采样标志信号寄存

always@(posedge clk or posedge reset)begin

if(reset)start_sample_rm <= 1'b0;

else if(state==IDLE)start_sample_rm <= start_sample;

elsestart_sample_rm <= 1'b0;

end/*状态切换IDLE->DDR_WR_FIFO_CLEAR

beginif(start_sample_rm) begin //DDR 初始化完成并且产生启动采样信号state <= DDR_WR_FIFO_CLEAR; //进入写 FIFO 清除状态endelse beginstate <= state;end

end

*/(2)DDR_WR_FIFO_CLEAR

//延时10个节拍

always@(posedge clk or posedge reset)begin

if(reset)wrfifo_clr_cnt<=0;

else if(state==DDR_WR_FIFO_CLEAR)//如果进入了清 fifo 状态

beginif(wrfifo_clr_cnt==9)wrfifo_clr_cnt<=5'd9;elsewrfifo_clr_cnt<=wrfifo_clr_cnt+1'b1;

end

elsewrfifo_clr_cnt<=5'd0;

end//给清FIFO信号足够的拉高时间

always@(posedge clk or posedge reset)begin

if (reset)wrfifo_clr<=0;

else if(state==DDR_WR_FIFO_CLEAR)beginif(wrfifo_clr_cnt==0||wrfifo_clr_cnt==1||wrfifo_clr_cnt==2)wrfifo_clr<=1'b1;elsewrfifo_clr<=1'b0;end

elsewrfifo_clr<=1'b0;

end/*状态切换DDR_WR_FIFO_CLEAR->ADC_SAMPLE

beginif(!wrfifo_full && (wrfifo_clr_cnt==9))state<=ADC_SAMPLE;elsestate<=DDR_WR_FIFO_CLEAR;

end

*/(3)ADC_SAMPLE

//根据ADC输出使能信号计数

always@(posedge clk or posedge reset)begin

if(reset)adc_sample_cnt<=1'b0;

else if(state==ADC_SAMPLE)beginif(adc_data_en)adc_sample_cnt<=adc_sample_cnt+1'b1;elseadc_sample_cnt<=adc_sample_cnt;

end

elseadc_sample_cnt<=1'b0;

end//产生采样使能信号给其他模块

always@(posedge clk or posedge reset)begin

if(reset)ad_sample_en<=0;

else if(state==ADC_SAMPLE)ad_sample_en<=1;

elsead_sample_en<=0;

end/*状态切换ADC_SAMPLE->DDR_RD_FIFO_CLEAR

beginif((adc_sample_cnt>=set_sample_num-1'b1)&& adc_data_en)state<=DDR_RD_FIFO_CLEAR;elsestate<=state;

end

*/(4)DDR_RD_FIFO_CLEAR

//延时10个节拍

always@(posedge clk or posedge reset)begin

if(reset)rdfifo_clr_cnt<=0;

else if(state==DDR_RD_FIFO_CLEAR)//如果进入了清 fifo 状态

beginif(rdfifo_clr_cnt==9)rdfifo_clr_cnt<=5'd9;elserdfifo_clr_cnt<=rdfifo_clr_cnt+1'b1;

end

elserdfifo_clr_cnt<=5'd0;

end//给清FIFO信号足够的拉高时间

always@(posedge clk or posedge reset)begin

if (reset)rdfifo_clr<=0;

else if(state==DDR_RD_FIFO_CLEAR)

beginif(rdfifo_clr_cnt==0||rdfifo_clr_cnt==1||rdfifo_clr_cnt==2)rdfifo_clr<=1'b1;

elserdfifo_clr<=1'b0;

end

elserdfifo_clr<=1'b0;

end/*状态切换DDR_RD_FIFO_CLEAR->DATA_SEND_START

beginif(!rdfifo_empty && (rdfifo_clr_cnt==9))beginstate<=DATA_SEND_START;endelsestate<=state;

end

*/(5)DATA_SEND_START

/*状态切换DATA_SEND_START->DATA_SEND_WORKING

beginstate <= DATA_SEND_WORKING;

end

*/(6)DATA_SEND_WORKING

//发送数据计数

always@(posedge clk or posedge reset)begin

if(reset)send_data_cnt<=32'd0;

else if(state==IDLE)send_data_cnt<=32'd0;

else if(rdfifo_rden)send_data_cnt<=send_data_cnt+1;

elsesend_data_cnt<=send_data_cnt;

end//DDR数据存到以太网缓存

always@(posedge clk or posedge reset)

if(reset) begineth_fifo_wrreq <= 1'b0;eth_fifo_wrdata <= 'd0;

end

else if(rdfifo_rden) begineth_fifo_wrreq <= 1'b1;eth_fifo_wrdata <= rdfifo_dout;

end

else begineth_fifo_wrreq <= 1'b0;eth_fifo_wrdata <= 'd0;

end/*状态切换DATA_SEND_WORKING->IDLE、DATA_SEND_WORKING->DATA_SEND_WORKING

beginif(send_data_cnt >= set_sample_num-1'b1) beginrdfifo_rden <= 1'b0;state <= IDLE;endelse beginrdfifo_rden <= 1'b1;state <= DATA_SEND_WORKING;end

end

*/7.1.4 fifo_axi_adapter模块

看文章开头:Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(一)。

S_IDLE:

beginif(start)next_state = S_ARB;elsenext_state = S_IDLE;

endmodule fifo_axi4_adapter #(parameter FIFO_DW = 16 ,parameter WR_AXI_BYTE_ADDR_BEGIN = 0 ,parameter WR_AXI_BYTE_ADDR_END = 1023 ,parameter RD_AXI_BYTE_ADDR_BEGIN = 0 ,parameter RD_AXI_BYTE_ADDR_END = 1023 ,parameter AXI_DATA_WIDTH = 128 ,parameter AXI_ADDR_WIDTH = 28 ,parameter AXI_ID = 4'b0000,parameter AXI_BURST_LEN = 8'd31 //burst length = 32

)

(input start ,// clock resetinput clk ,input reset ,// wr_fifo wr Interfaceinput wrfifo_clr ,input wrfifo_clk ,input wrfifo_wren ,input [FIFO_DW-1:0] wrfifo_din ,output wrfifo_full ,output [15:0] wrfifo_wr_cnt ,// rd_fifo rd Interfaceinput rdfifo_clr ,input rdfifo_clk ,input rdfifo_rden ,output [FIFO_DW-1:0] rdfifo_dout ,output rdfifo_empty ,output [15:0] rdfifo_rd_cnt ,// Master Interface Write Address Portsoutput [3:0] m_axi_awid ,output [AXI_ADDR_WIDTH-1:0] m_axi_awaddr ,output [7:0] m_axi_awlen ,output [2:0] m_axi_awsize ,output [1:0] m_axi_awburst ,output [0:0] m_axi_awlock ,output [3:0] m_axi_awcache ,output [2:0] m_axi_awprot ,output [3:0] m_axi_awqos ,output [3:0] m_axi_awregion,output m_axi_awvalid ,input m_axi_awready ,// Master Interface Write Data Portsoutput [AXI_DATA_WIDTH-1:0] m_axi_wdata ,output [AXI_DATA_WIDTH/8-1:0] m_axi_wstrb ,output m_axi_wlast ,output m_axi_wvalid ,input m_axi_wready ,// Master Interface Write Response Portsinput [3:0] m_axi_bid ,input [1:0] m_axi_bresp ,input m_axi_bvalid ,output m_axi_bready ,// Master Interface Read Address Portsoutput [3:0] m_axi_arid ,output [AXI_ADDR_WIDTH-1:0] m_axi_araddr ,output [7:0] m_axi_arlen ,output [2:0] m_axi_arsize ,output [1:0] m_axi_arburst ,output [0:0] m_axi_arlock ,output [3:0] m_axi_arcache ,output [2:0] m_axi_arprot ,output [3:0] m_axi_arqos ,output [3:0] m_axi_arregion,output m_axi_arvalid ,input m_axi_arready ,// Master Interface Read Data Portsinput [3:0] m_axi_rid ,input [AXI_DATA_WIDTH-1:0] m_axi_rdata ,input [1:0] m_axi_rresp ,input m_axi_rlast ,input m_axi_rvalid ,output m_axi_rready

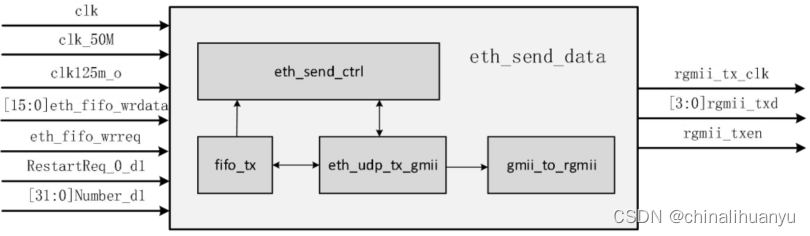

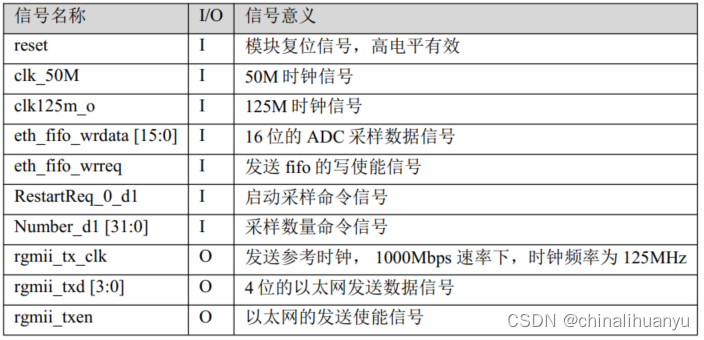

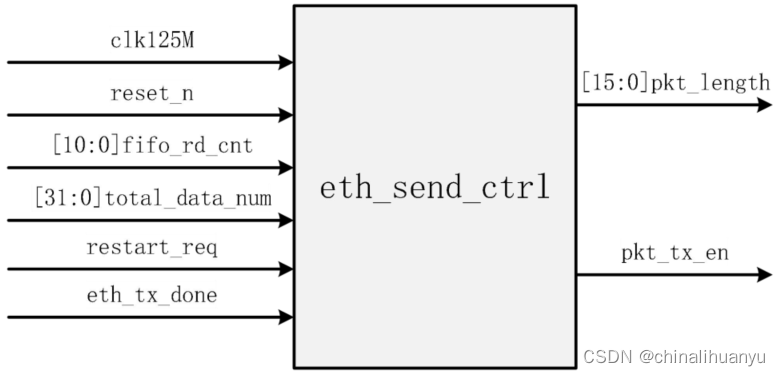

);7.1.5 eth_send_data 模块

将DDR读出的ADC数据发送到电脑端。

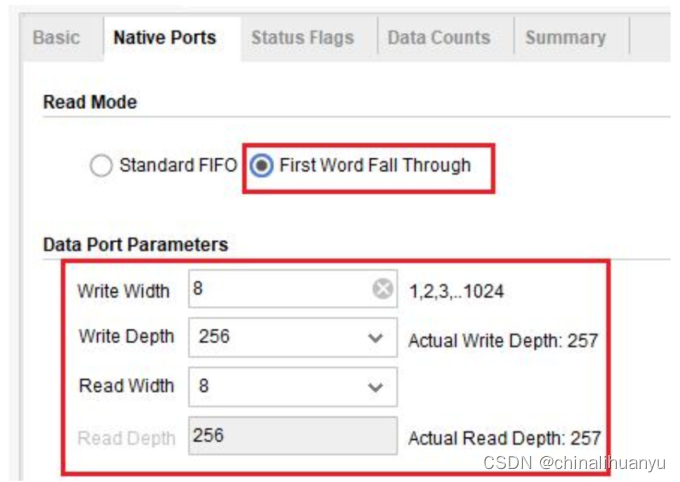

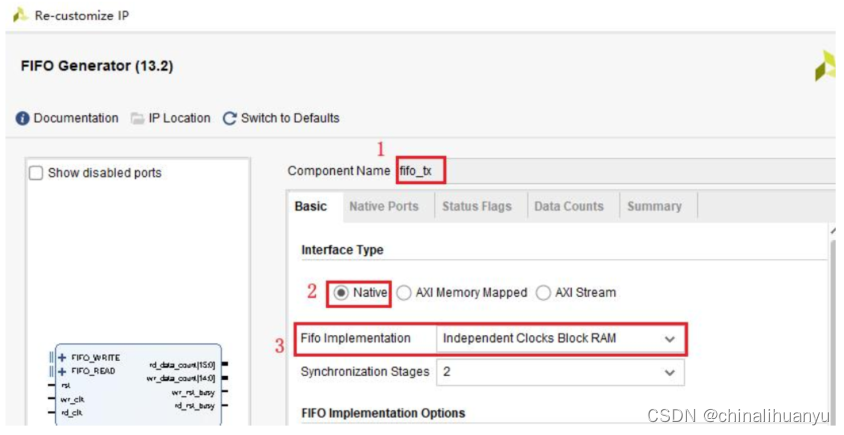

(1)fifo_tx模块

First Word Fall Through( FWFT)可以不需要读命令, 自动将最新的数据放在 dout 上。

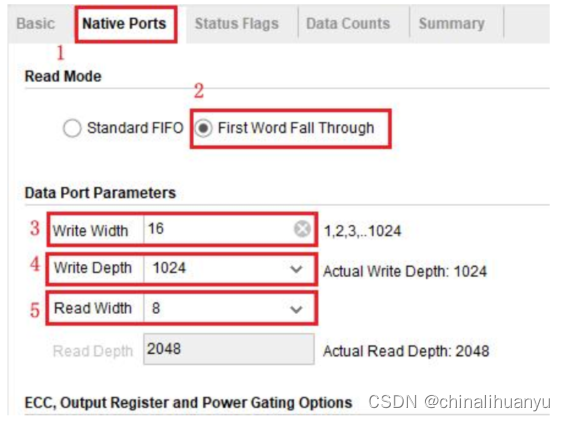

(2)eth_send_ctrl模块

以太网帧最大长度 1518 字节(数据段 1500 字节) , 其中数据段 1500 字节还包括 20 字节 IP 报文头部和 8 字节 UDP 报文头部, 所以数据帧发送的ACM9238 采集的数据最大长度为 1472 字节。

always@(posedge clk125M or negedge reset_n)if(!reset_n) beginpkt_tx_en <= 1'd0;pkt_length <= 16'd0;data_num <= 32'd0;state <= 0;cnt_dly_time <= 28'd0;endelse begincase(state)0://得到 pkt_length 信号的初始值beginif(restart_req)begindata_num <= total_data_num;if((total_data_num << 1) >= 16'd1472)beginpkt_length <= 16'd1472; //一个数据2个字节state <= 1;endelse if((total_data_num << 1) > 0)beginpkt_length <= total_data_num << 1; //一个数据2个字节state <= 1;endelse beginstate <= 0;endendend1: beginif(fifo_rd_cnt >= (pkt_length -2)) beginpkt_tx_en <= 1'd1;state <= 2;endelse beginstate <= 1;pkt_tx_en <= 1'd0;endend2:beginpkt_tx_en <= 1'd0;if(eth_tx_done)begindata_num <= data_num - pkt_length/2;state <= 3;endend3:if(cnt_dly_time >= cnt_dly_min)beginstate <= 4;cnt_dly_time <= 28'd0;endelse begincnt_dly_time <= cnt_dly_time + 1'b1;state <= 3;end4:beginif(data_num * 2 >= 16'd1472)beginpkt_length <= 16'd1472;state <= 1;endelse if(data_num * 2 > 0)beginpkt_length <= data_num * 2;state <= 1;endelse beginstate <= 0;endenddefault:state <= 0;endcaseend

相关文章:

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(二)

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(前导) Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(一) Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(三) 五、实验目的 本次实验使用电脑上的…...

高级语言讲义2010计专(仅高级语言部分)

1.编写一程序,对输入的正整数,求他的约数和。 如:18的约数和为1236939 #include <stdio.h>int getsum(int n){int i,sum0;for(i1;i<n;i)if(n%i0)sumi;return sum; } int main(){int sum getsum(18);printf("%d",sum); …...

你喜欢那种舞者呢?

迷宫中的舞者:程序员职业赛道的探索与魅力 在数字世界的深处,程序员的职业赛道宛如一座神秘而迷人的迷宫。这个迷宫中,每个转角都隐藏着无限的可能,每个领域都散发着独特的魅力。前端开发者如同花园中的精灵,后端工程师…...

LeetCode每日一题之 快乐数

目录 题目介绍: 算法原理: 鸽巢原理: 如何找到环里元素: 代码实现: 题目介绍: 题目链接:. - 力扣(LeetCode) 算法原理: 我先简单举两个例子ÿ…...

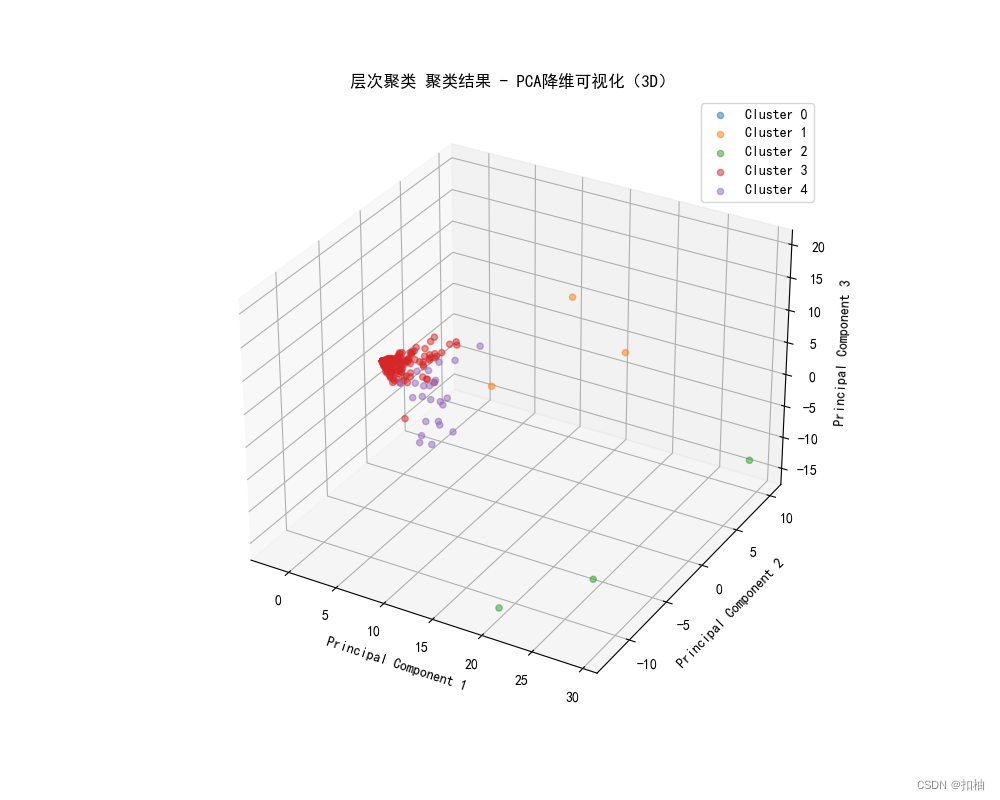

【机器学习】在Python中进行K-Means聚类和层次聚类

Python中聚类算法API的使用指南 聚类分析是数据分析中一种常见的无监督学习方法,通过将相似的对象分组在一起,我们能够识别出数据集中的自然分群。本文将介绍如何使用Python中的聚类算法接口,KMeans和层次聚类方法。 K-Means 聚类 K-Means…...

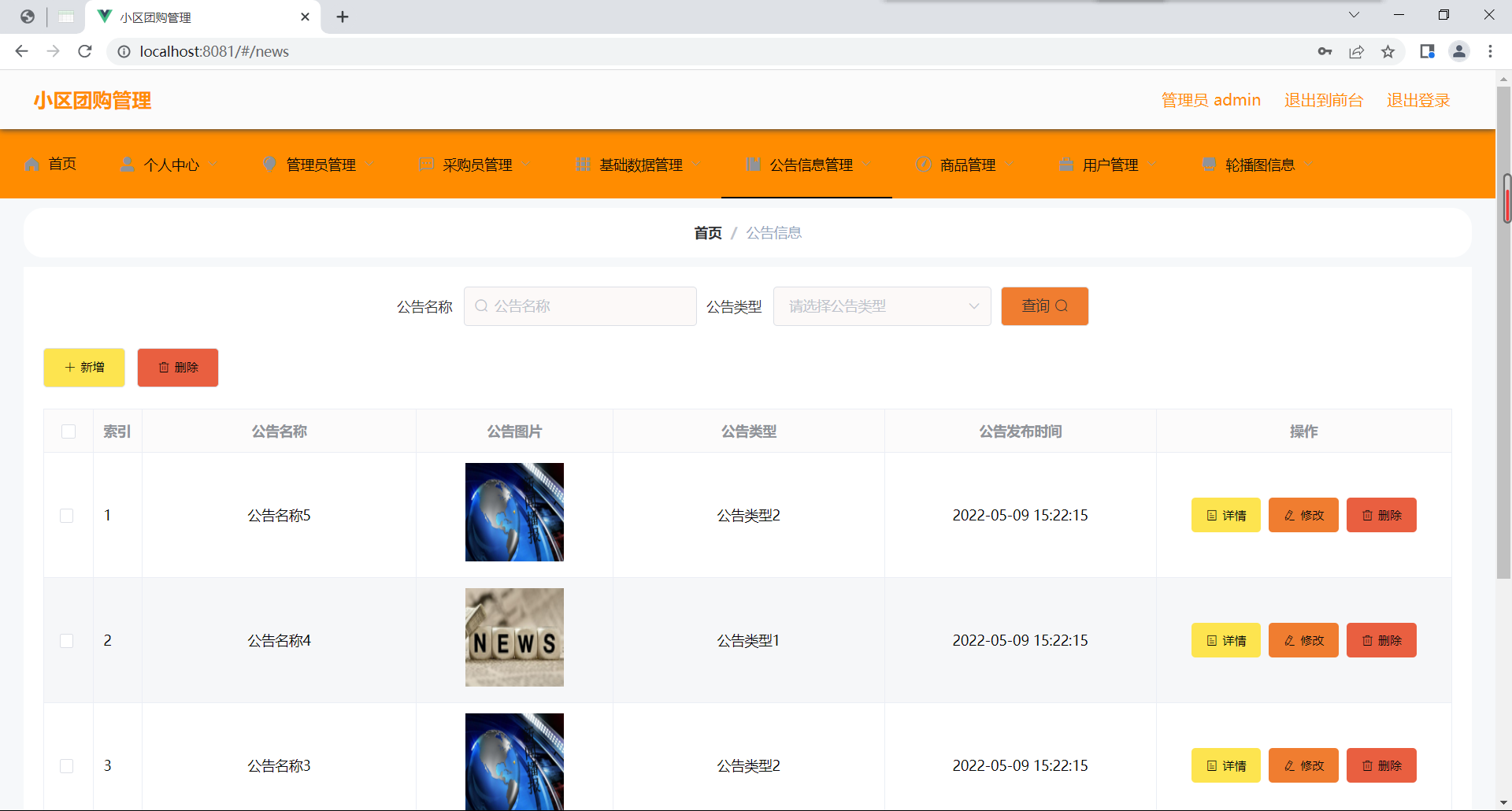

springboot254小区团购管理

小区团购管理设计与实现 摘 要 传统办法管理信息首先需要花费的时间比较多,其次数据出错率比较高,而且对错误的数据进行更改也比较困难,最后,检索数据费事费力。因此,在计算机上安装小区团购管理软件来发挥其高效地信…...

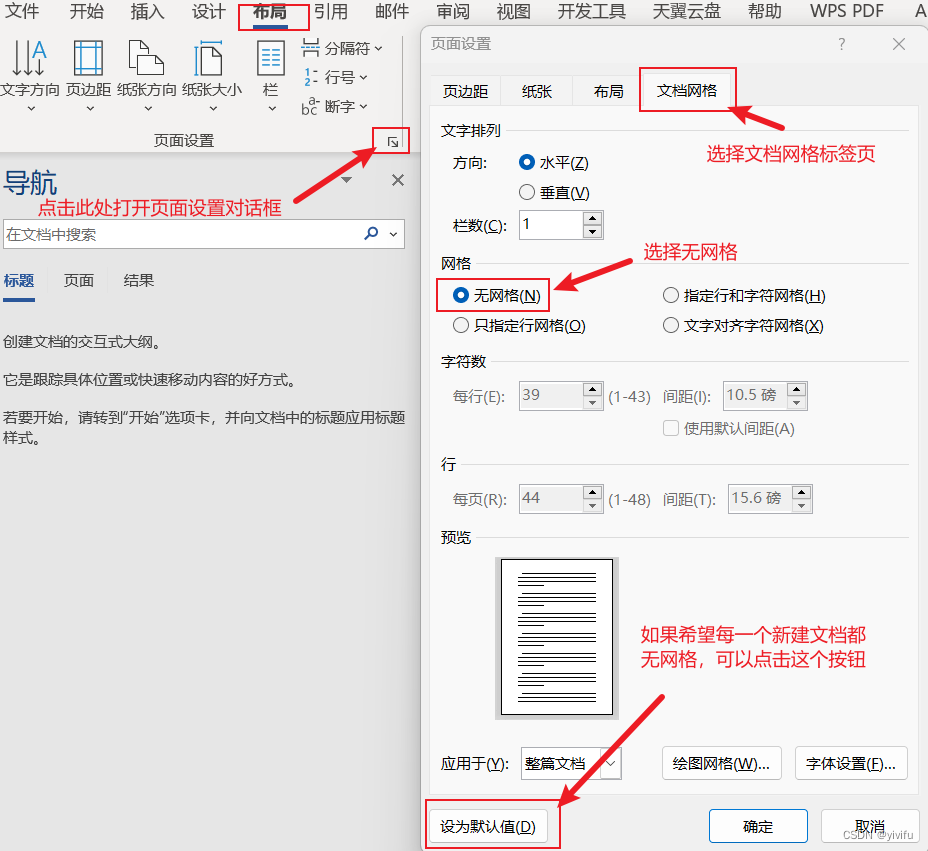

Word中的文档网格线与行距问题

在使用Word编辑文档时,经常会发生以下动图展示的这种情况: 上面的动图里,将文字大小放大到某个字号时,单倍行距的间距突然增加很多。造成这种情况的原因是文档中定义了网格线,并且设置了对齐到网格线。如果取消文档中…...

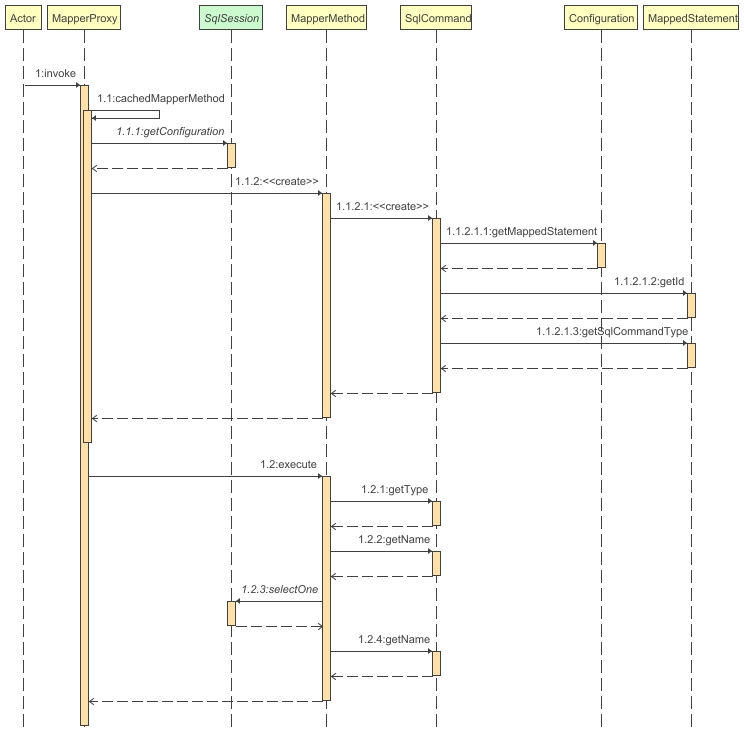

【简写Mybatis】03-Mapper xml的注册和使用

前言 在学习MyBatis源码文章中,斗胆想将其讲明白;故有此文章,如有问题,不吝指教! 注意: 学习源码一定一定不要太关注代码的编写,而是注意代码实现思想; 通过设问方式来体现代码中的…...

)

Vue源码系列讲解——指令篇【一】(自定义指令)

目录 1. 前言 2. 何时生效 3. 指令钩子函数 4. 如何生效 5. 总结 1. 前言 在Vue中,除了Vue本身为我们提供的一些内置指令之外,Vue还支持用户自定义指令。并且用户有两种定义指令的方式:一种是使用全局API——Vue.directive来定义全局指令…...

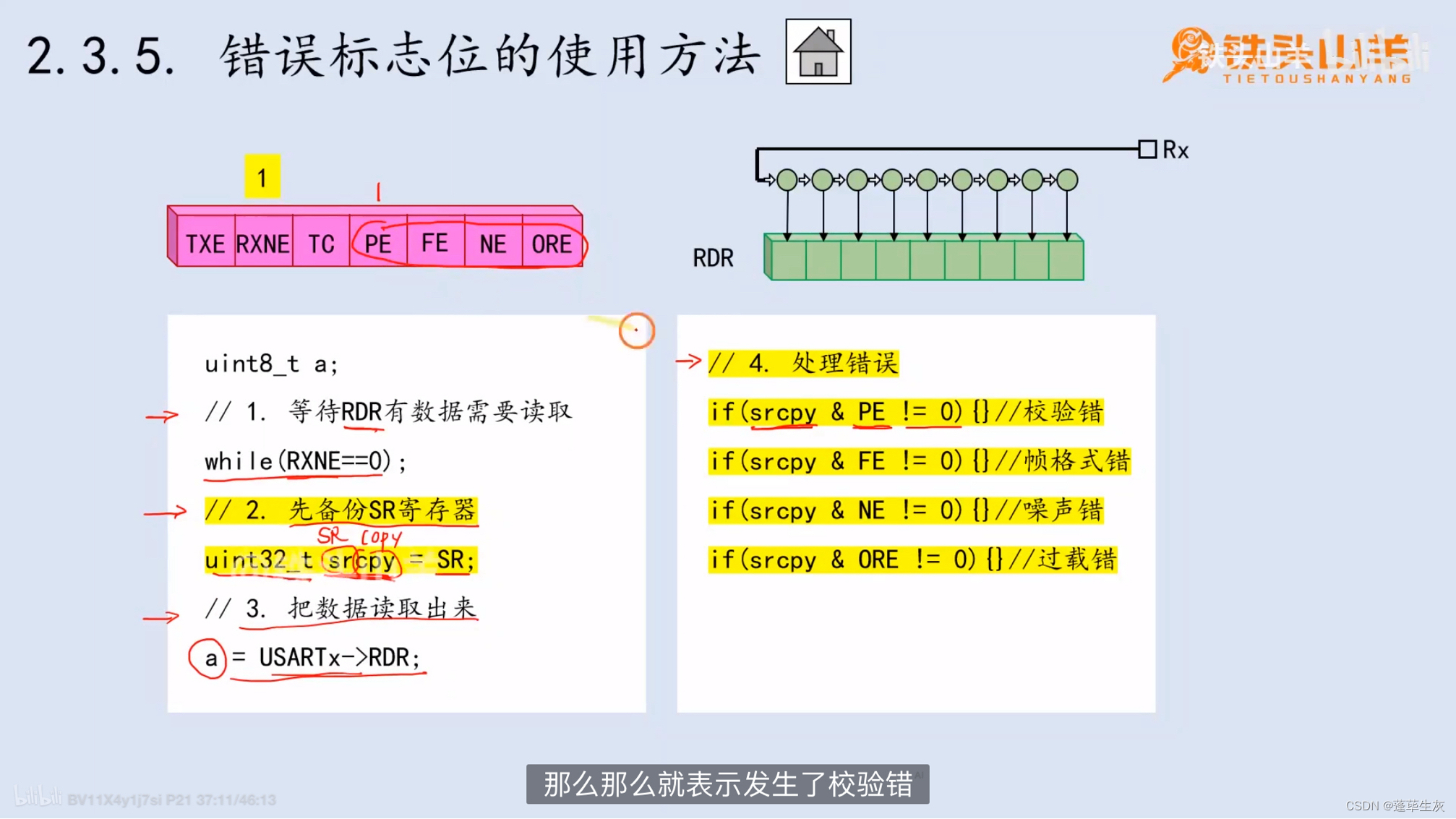

STM32(14)USART

USART:一种片上外设,用来实现串口通信,就是stm32内部的串口 USART简介 串并转换电路 串行通信和并行通信 串行:一根数据线,逐个比特位发送 为什么要串并转换 移位寄存器 USART的基本模型 通过查询SR(状态寄存器&…...

作业 字符数组-统计和加密

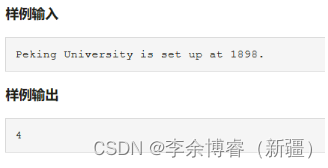

字串中数字个数 描述 输入一行字符,统计出其中数字字符的个数。 输入 一行字符串,总长度不超过255。 输出 输出为1行,输出字符串里面数字字符的个数。 样例 #include <iostream> #include<string.h> using namespace std; int m…...

除F2题外补题报告)

Codeforces Round 719 (Div. 3)除F2题外补题报告

Codeforces Round 719 Div. 3 除F2题外补题报告 得分情况补题情况错题分析C题题目大意初次思路正解思路正解代码错误原因 D题题目大意初次思路正解思路正解代码错误原因 E题题目大意初次思路正解思路正解代码 F1题题目大意正解思路正解代码 G题题目大意正解思路正解代码 得分情…...

docker本地搭建spark yarn hive环境

docker本地搭建spark yarn hive环境 前言软件版本准备工作使用说明构建基础镜像spark on yarn模式构建on-yarn镜像启动on-yarn集群手动方式自动方式 spark on yarn with hive(derby server)模式构建on-yarn-hive镜像启动on-yarn-hive集群手动方式自动方式 常用示例spark执行sh脚…...

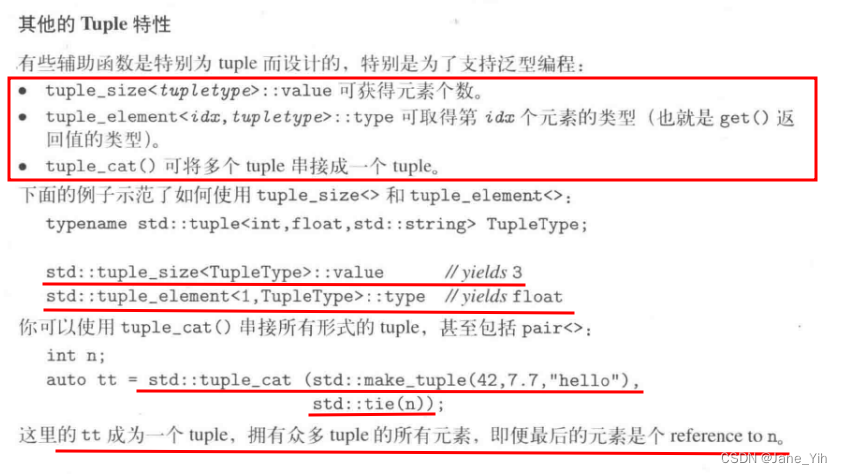

每日学习笔记:C++ 11的Tuple

#include <tuple> Tuple介绍(不定数的值组--可理解为pair的升级版) 定义 创建 取值 初始化 获取tuple元素个数、获取tuple某元素类型、将2个tuple类型串接为1个新tuple类型...

MongoDB聚合运算符;$dateToParts

$dateToParts聚合运算符将日期表达式拆分成多个字段放在一个文档返回,属性有year、month、day、hour、minute、second和millisecond。如果iso8601属性设置为true,返回的各部分用ISO周日期返回,属性分别是:isoWeekYear、isoWeek、i…...

Spring MVC RequestMappingHandlerAdapter原理解析

在Spring MVC框架中,RequestMappingHandlerAdapter是一个核心的组件,负责将请求映射到具体的处理器方法上,并调用这些方法来处理请求。其中,invokeHandlerMethod方法是这个适配器中的一个关键方法,它负责实际调用处理器…...

反射整理学习

目录 1、反射介绍 2、反射API 2.1 获取类对应的字节码的对象(三种) 2.2 常用方法 3、反射的应用 3.1 创建 : 测试物料类 3.2 获取类对象 3.3 获取成员变量 3.4 通过字节码对象获取类的成员方法 3.5 通过字节码对象获取类的构造方法 4、创建对象…...

JavaScript 运算规则详解

在 JavaScript 中,运算规则是非常重要的基础知识,了解这些规则可以帮助我们正确地编写代码并避免一些常见的错误。本教程将详细介绍 JavaScript 中的各种运算规则,包括基本运算符、类型转换、运算优先级等内容。 1. 基本运算符 JavaScript …...

C++篇 语 句

到目前为止,我们只见过两种语句: return 语句和表达式语句。根据语句对执行顺 序的影响,C 语言其余语句大多属于以下 3 大类。 选择语句: if 语句和 switch 语句。循环语句: while 语句, do...while 语句和…...

简洁的在线观影开源项目

公众号:【可乐前端】,每天3分钟学习一个优秀的开源项目,分享web面试与实战知识。 每天3分钟开源 hi,这里是每天3分钟开源,很高兴又跟大家见面了,今天介绍的开源项目简介如下: 仓库名࿱…...

OpenPLC Editor:开源PLC编程工具的终极指南

OpenPLC Editor:开源PLC编程工具的终极指南 【免费下载链接】OpenPLC_Editor 项目地址: https://gitcode.com/gh_mirrors/ope/OpenPLC_Editor 在工业自动化领域,寻找一款功能强大、易于使用且完全免费的开源PLC编程工具一直是工程师们的核心需求…...

如何用AntiDupl.NET高效清理重复图片:从入门到精通

如何用AntiDupl.NET高效清理重复图片:从入门到精通 【免费下载链接】AntiDupl A program to search similar and defect pictures on the disk 项目地址: https://gitcode.com/gh_mirrors/an/AntiDupl 你是否曾为电脑中堆积如山的重复照片而烦恼?…...

如何用Snap.Hutao轻松管理你的原神游戏数据:终极桌面工具箱完全指南

如何用Snap.Hutao轻松管理你的原神游戏数据:终极桌面工具箱完全指南 【免费下载链接】Snap.Hutao 实用的开源多功能原神工具箱 🧰 / Multifunctional Open-Source Genshin Impact Toolkit 🧰 项目地址: https://gitcode.com/GitHub_Trendin…...

5个DistroAV高级应用场景:企业视频制作与远程协作的终极指南

5个DistroAV高级应用场景:企业视频制作与远程协作的终极指南 【免费下载链接】obs-ndi DistroAV (formerly OBS-NDI): NDI integration for OBS Studio 项目地址: https://gitcode.com/gh_mirrors/ob/obs-ndi DistroAV(前身为OBS-NDI)…...

)

从考研到面试:线性代数高频术语中英对照速查手册(含易混点解析)

从考研到面试:线性代数高频术语中英对照速查手册(含易混点解析) 线性代数是理工科学生绕不开的核心课程,无论是研究生入学考试还是技术岗位面试,扎实的线性代数基础往往是区分优秀候选人的关键指标。尤其在涉及英文文献…...

技术深度解析:OneNote-MD-Exporter 架构设计与无损迁移实战

技术深度解析:OneNote-MD-Exporter 架构设计与无损迁移实战 【免费下载链接】onenote-md-exporter ConsoleApp to export OneNote notebooks to Markdown formats 项目地址: https://gitcode.com/gh_mirrors/on/onenote-md-exporter 在数字化笔记管理领域&am…...

5分钟快速上手FF14动画跳过插件:告别冗长副本动画

5分钟快速上手FF14动画跳过插件:告别冗长副本动画 【免费下载链接】FFXIV_ACT_CutsceneSkip 项目地址: https://gitcode.com/gh_mirrors/ff/FFXIV_ACT_CutsceneSkip 还在为《最终幻想14》副本中冗长的动画而烦恼吗?这款专为CN服务器设计的智能跳…...

算法搞定数独和八皇后:从理论到C++实战避坑)

用舞蹈链(DLX)算法搞定数独和八皇后:从理论到C++实战避坑

舞蹈链算法实战:用DLX高效解决数独与八皇后问题 第一次接触精确覆盖问题时,我正被一道"魔鬼级"数独题折磨得焦头烂额。传统回溯算法在9x9的网格中显得力不从心,直到发现了Donald Knuth提出的舞蹈链(Dancing Links&#…...

)

高速ADC时序收不稳?聊聊用FPGA的IDELAY和IODELAYCTRL做数据对齐的那些事儿(以ADS42LB69为例)

高速ADC时序收不稳?聊聊用FPGA的IDELAY和IODELAYCTRL做数据对齐的那些事儿(以ADS42LB69为例) 在高速数据采集系统的设计中,ADC与FPGA的接口时序问题往往是工程师们最头疼的"拦路虎"。特别是当采样率突破200MSPS时&#…...

)

Lovable开发平台,生成安卓和iOS都能运行的原生App方案(用Kotlin或者Switf编写)

Lovable 核心生成的是 Web 应用(React Supabase),它本身不直接编写纯原生的 Kotlin 或 Swift 代码。 不过,它通过 Capacitor 这个桥接框架实现了"一套代码,两端运行"的折中方案: 🛠️…...