华为海思校园招聘-芯片-数字 IC 方向 题目分享——第二套

华为海思校园招聘-芯片-数字 IC 方向 题目分享(共9套,有答案和解析,答案非官方,未仔细校正,仅供参考)——第二套(共九套,每套四十个选择题)

部分题目分享,完整版获取(WX:didadidadidida313,加我备注:CSDN huawei数字芯片题目,谢绝白嫖哈)

-

表示任意两位无符号十进制数需要(7)位二进制数。

-

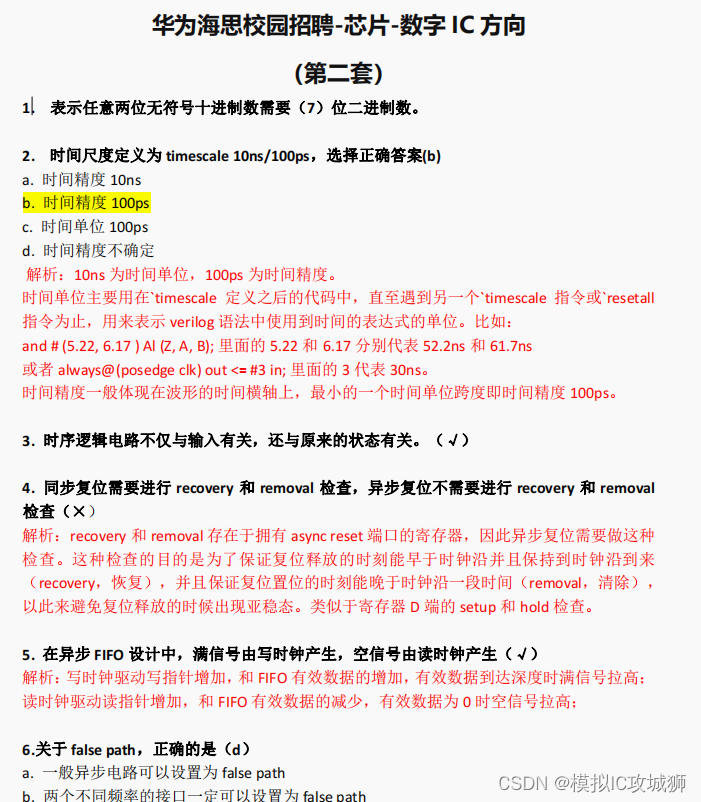

时间尺度定义为 timescale 10ns/100ps,选择正确答案(b)

a. 时间精度 10ns

(recovery,恢复),并且保证复位置位的时刻能晚于时钟沿一段时间(removal,清除),

以此来避免复位释放的时候出现亚稳态。类似于寄存器 D 端的 setup 和 hold 检查。 -

在异步 FIFO 设计中,满信号由写时钟产生,空信号由读时钟产生(√)

解析:写时钟驱动写指针增加,和 FIFO 有效数据的增加,有效数据到达深度时满信号拉高;

读时钟驱动读指针增加,和 FIFO 有效数据的减少,有效数据为 0 时空信号拉高;

b. 时间精度 100ps

c. 时间单位 100ps

d. 时间精度不确定

解析:10ns 为时间单位,100ps 为时间精度。

时间单位主要用在timescale 定义之后的代码中,直至遇到另一个timescale 指令或`resetall

指令为止,用来表示 verilog 语法中使用到时间的表达式的单位。比如:

and # (5.22, 6.17 ) Al (Z, A, B); 里面的 5.22 和 6.17 分别代表 52.2ns 和 61.7ns

或者 always@(posedge clk) out <= #3 in; 里面的 3 代表 30ns。

时间精度一般体现在波形的时间横轴上,最小的一个时间单位跨度即时间精度 100ps。 -

时序逻辑电路不仅与输入有关,还与原来的状态有关。(√)

-

同步复位需要进行 recovery 和 removal 检查,异步复位不需要进行 recovery 和 removal

检查(×)

解析:recovery 和 removal 存在于拥有 async reset 端口的寄存器,因此异步复位需要做这种

检查。这种检查的目的是为了保证复位释放的时刻能早于时钟沿并且保持到时钟沿到来

6.关于 false path,正确的是(d)

a. 一般异步电路可以设置为 false path

b. 两个不同频率的接口一定可以设置为 false path

c. 一般异步复位可以设置为 false path

d. 一般模拟 ip 和系统的互联接口都可以设置为 false path

解析:

a 是错误的。设置 false path 的原因是该路径没必要满足特定时序(比如

setup/hold,recovery/removal,clock gating,max delay 等特定时序)。虽然异步电路时钟之间

没有固定的相位关系,工具没法直接做 reg‐reg 的 setup/hold 检查,但是可以设置 max delay

等特殊约束对需要满足一定时序关系的异步电路做检查,需要看具体的场景。

b 是错误的。频率不同和 false path 没有任何关系。而异步电路的频率可能不同,但是频率

不同不等于异步电路,异步电路的本质是来自不同晶振的时钟源驱动的电路,他们频率甚至

也可以相同。

c 是错误的。对于异步复位,指的只是寄存器使用了异步复位端口 async_reset,在复位的时

候复位信号可以是异步的。但它在释放的时候是需要满足 recovery‐removal 时序检查的,需

要做同步释放,因为做了同步,所以 STA 工具有能力做检查。所以异步复位不能设为 false

path,需要检查 recovery‐removal 时序。

d 是正确的。模拟 ip 的时钟频率一般远小于数字电路,因此对数字电路的时序不敏感,互联

接口可以设置 false path。

7.下面是一个什么电路:©

always@(posedge clk or negedge rst_n) begin

If(rst_n == 1’b0)

a<=2’b0;

elseif(b>2’b0)

a<= b

end

a. 综合为 latch

b. 带同步复位的 d 触发器

c. 带异步复位的 d 触发器

d. 组合逻辑

解析:posedge clk 决定了这是一个触发器,if(rst_n == 1’b0)和 negedge rst_n 决定了这是一个

异步复位的 d 触发器,复位和时钟无关(异步)。

-

对于信号定于语句:reg[0:4] always,a;说法错误的是(b)

a. 不能使用关键字定义信号名

b. 信号定义为 reg 型,只能使用在时序电路的赋值中

c. bit 定义顺序应该从高到低

d. 每个信号应单独用一行来声明

解析:a 和 c 违背 verilog 语法,是错的。d 只是建议,并不违背 verilog 语法。相比之下,b

是绝对错的,因为 reg 型可以用于组合逻辑赋值,比如 always(*)。 -

下列说法错误的是(d)

a. 条件语句,如果无优先级关系,尽量采用 case,避免多级 else if,影响时序;

b. If/else 语句配对使用,case 语句加 default 项;组合逻辑中在所有条件下都要对信号幅值,

如果要保持步便用 a=a 方式赋值;

c. 两个向量进行比较操作或加减操作或赋值操作时,两个向量的位宽要相等,避免隐式扩

展。

d. 可综合代码中,除了 for 语句中的循环变量可以定义为 integer 型以外,所有变量和信号

都只能为 wire 或 reg 型,不能定义为整型,实数型,无符号型,realtime 型和 time 型。

解析:

a 是正确的,优先级条件语句会综合成串联的选择逻辑,时序较差,而 case 可以综合成并行

的选择逻辑,n 个条件逻辑级数为 log2n。

b 是正确的,但不严谨。if/else 可以不配对使用,在时序逻辑下,可以只有 if 没有 else,这

时候 else 分支保持寄存器原值,当然有 else 使代码更清晰。有 case 语句,如果是组合逻辑,

只要有条件没给赋值,会综合出 latch。

c 是正确的。两个向量位宽不匹配会隐式拓展高位,如果有操作数定义为 wire 类型但是作为

有符号数使用,隐式拓展会错误高位补 0,拓展成无符号数,功能出错。

d 是错误的,integer 可以被定义成信号,会综合出 32bit 的 register。但因为位宽固定,一般

不这么使用。另外在 verilog‐2001 中加入了无符号型和有符号型的 reg/wire 定义,也属于可

综合类型。其他类型不可综合。

10.关于异步设计的危害,下面说法错误的是:(b)

a. 信号的时延随着每次布局布线的不同而不同,随着 pvt 的改变而改变,因此可靠性很差,

而且不容易移植

b. 异步设计会产生毛刺

c. 异步设计不能做静态时序分析

d. 异步设计会带来很大的同步翻转噪声

解析:

a 是正确的。现在大部分的设计都是同步设计,小部分高性能低功耗电路可能会考虑使用异

步设计。异步设计的好处之一便是可以最大限度利用时间窗的 margin。有点类似 latch 的

timeborrow,无需等待同步打拍,并且没有了时钟信号,功耗可以大大降低。坏处是需要特

殊的握手机制来保证时序,而握手机制又很大程度上依赖于信号的时延,像 a 所说,时延不

可控型较强,因此可靠性较差,而且不容易移植。

b 是错的,毛刺并非异步设计导致,即便是同步设计,只要信号传递过程中中间结果和最终

输出不同(卡诺图可以清楚看到),也会有毛刺,只不过异步设计的毛刺比较容易导致功能

错误,因为没有时序检查,没有 setup/hold 来保证毛刺消除。

c 是对的。现在的静态时序分析都是基于同步设计,异步设计没有时钟的概念,所有信号没

有固定的相位关系,工具无法建模分析。

d 是对的。这里的翻转噪声主要来自于信号线之间的耦合电容。如果两个异步信号之间有耦

合电容,那么他们的噪声比同步信号之间大得多,因为他们的电平跳变相互影响的时间窗口

更大。 -

多 bit 总线信号可以通过格雷码转换进行异步处理,例如:8bit 的数据总线进行格雷码

转换,然后通过双触发器法实现异步处理(√)

解析:格雷码将多 bit 的翻转转化为单 bit 的翻转,解决了多 bit 异步信号传播过程中因时延

不同而导致的数据采集端采集信号错误的问题。 -

System Verilog 中,下面哪种数组在使用前需要执行 new 操作(c)

a. 压缩数组

b. 联合数组

c. 动态数组

d. 多维数组

解析:动态数组通过 new()函数预先分配存储空间。 -

电路设计中,只要采用静态时序分析就可以保证电路设计的准确性,不需要再进行动态

时序分析了。(×)

解析:现在大部分的同步电路设计流程都是 rtl 验证+formality 形式验证+sta 静态时序分析。

通过 rtl 验证保证功能完备,通过 formality 保证 rtl 和网表一致性。因为有了 formality 保证

网表和 rtl 的一致性,因此如果 rtl 验证完备,一般情况下就可以保证网表功能验证完备。然

后通过对网表进行静态时序分析(sta)来保证没有时序风险。动态时序分析(后仿)主要是

跑一些典型场景,保证在典型场景下不会有时序问题,增强设计信心,对于同步电路,只要

sta 阶段检查仔细,问题一般不大。但是设计中难免会有一小部分异步电路无法进行静态时

序分析,因此必须需要通过后仿来进行排查。

相关文章:

华为海思校园招聘-芯片-数字 IC 方向 题目分享——第二套

华为海思校园招聘-芯片-数字 IC 方向 题目分享(共9套,有答案和解析,答案非官方,未仔细校正,仅供参考)——第二套(共九套,每套四十个选择题) 部分题目分享,完整版获取&am…...

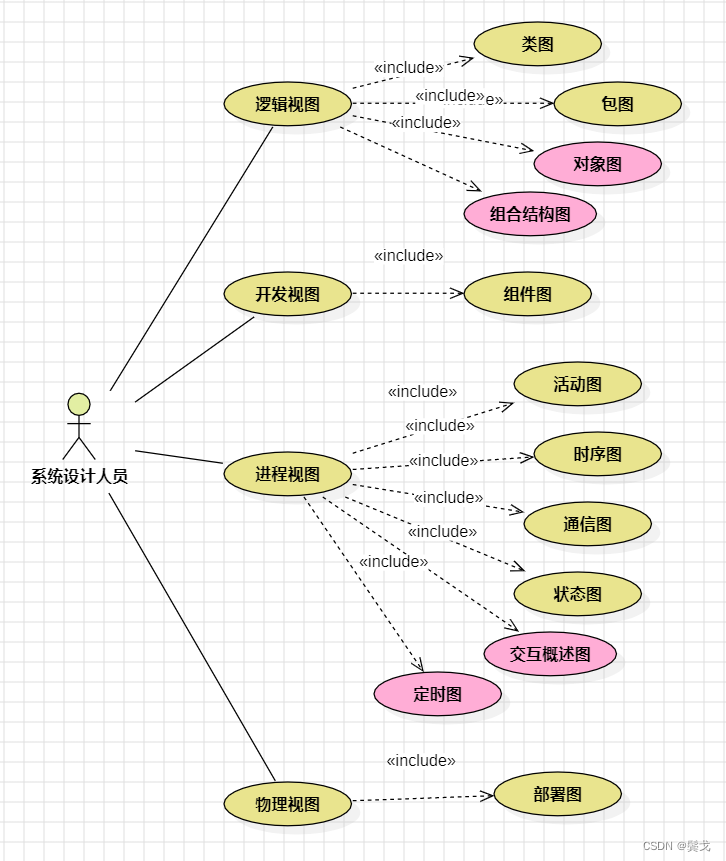

UML2.0在系统设计中的实际使用情况

目前我在系统分析设计过程中主要使用UML2.0来表达,使用StarUML软件做实际设计,操作起来基本很顺手,下面整理一下自己的使用情况。 1. UML2.0之十三张图 UML2.0一共13张图,可以分为两大类:结构图-静态图,行…...

django celery 异步任务 异步存储

环境:win11、python 3.9.2、django 4.2.11、celery 4.4.7、MySQL 8.1、redis 3.0 背景:基于django框架的大量任务实现,并且需要保存数据库 时间:20240409 说明:异步爬取小说,并将其保存到数据库 1、创建…...

apex0.1版本安装踩坑指南

踩了无数坑,发现只需要三行命令就可以成功安装apex0.1. 由于pip命令下只能找到0.9的版本,所以需要git clone的方式安装。 1. git clone https://www.github.com/nvidia/apex 这个命令的意思是下载apex到本地。注意,这里需要稳定的环境…...

)

HTML — 弹性布局(2)

弹性布局的其他属性 1. order 决定弹性项目(flex item)的排列顺序,使用较少,默认为0 。 order 的值可以为任意整数(正整数或负整数均可,也可为0),数值越小越排在前面。 2. align-s…...

MYSQL 8.0版本修改用户密码(知道登录密码)和Sqlyog错误码2058一案

今天准备使用sqlyog连接一下我Linux上面的mysql数据库,然后就报如下错误 有一个简单的办法就是修改密码为password就完事!然后我就开始查找如何修改密码! 如果是需要解决Sqlyog错误码2058的话,执行以下命令,但是注意root对应host是不是loca…...

Linux中磁盘管理

一.磁盘管理的概括和简要说明 磁盘空间的管理,使用硬盘三步: (1)分区: (2)安装文件系统格式化 (3)挂载: 硬盘的分类: (1&#x…...

tailwindcss在manoca在线编辑智能感知

推荐一下monaco-tailwindcss库,它实现在monaco-editor网页在线编辑器中对tailwindcss的智能感知提示,在利用tailwindcss实现html效果布局。非常的方便。 生成CSS...

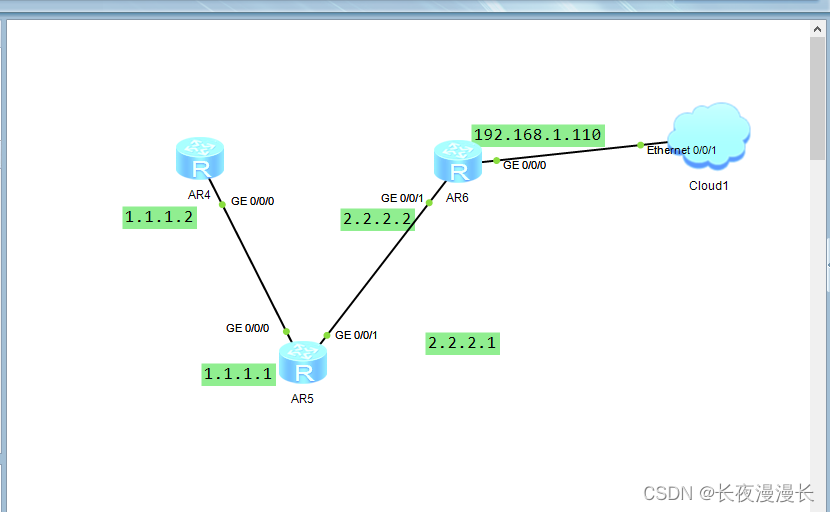

通过本机调试远端路由器非直连路由

实验目的:如图拓扑,通过本机电脑发,telnet调试远程AR4设备。 重点1:通过ospf路由协议配置拓扑网络,知识点:ospf配置路由器协议语法格式,area区域的定义,区域内网络的配置࿰…...

React路由快速入门:Class组件和函数式组件的使用

1. 介绍 在开始学习React路由之前,先了解一下什么是React路由。React Router是一个为React应用程序提供声明式路由的库。它可以帮助您在应用程序中管理不同的URL,并在这些URL上呈现相应的组件。 2. 安装 要在React应用程序中使用React路由,…...

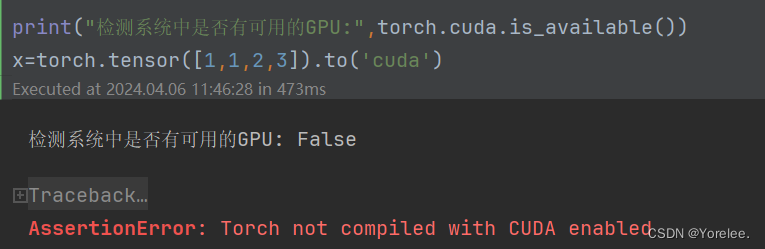

Pytorch数据结构:GPU加速

文章目录 一、GPU加速1. 检查GPU可用性:2. GPU不可用需要具体查看问题3. 指定设备4.将张量和模型转移到GPU5.执行计算:6.将结果转移回CPU 二、转移原理1. 数据和模型的存储2. 数据传输3. 计算执行4. 设备管理5.小结 三、to方法的参数类型 一、GPU加速 .…...

OpenHarmony开发-连接开发板调试应用

在 OpenHarmony 开发过程中,连接开发板进行应用调试是一个关键步骤,只有在真实的硬件环境下,我们才能测试出应用更多的潜在问题,以便后续我们进行优化。本文详细介绍了连接开发板调试 OpenHarmony 应用的操作步骤。 首先…...

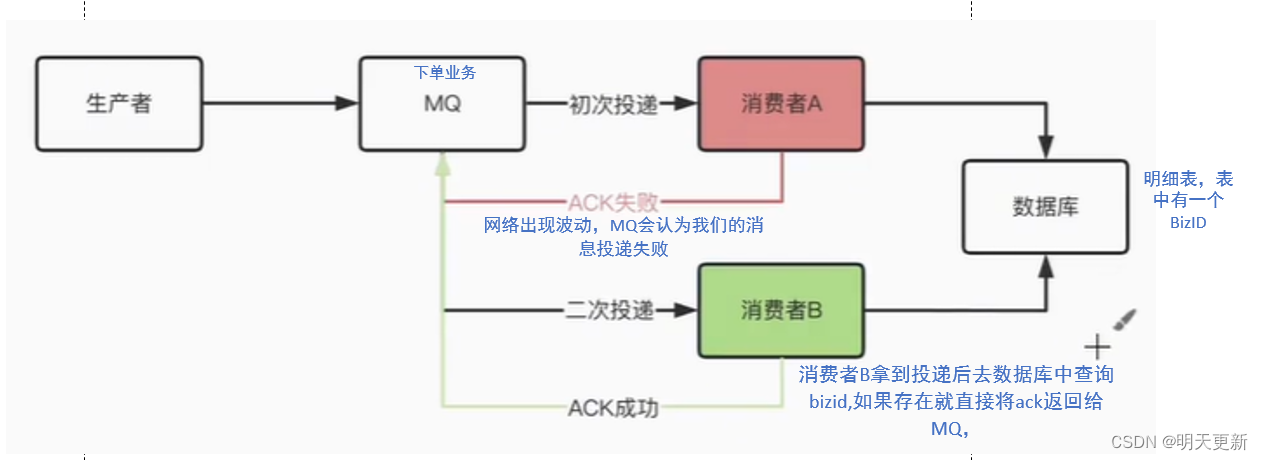

RabbitMQ如何保证消息的幂等性???

在RabbitMQ中,保证消费者的幂等性主要依赖于业务设计和实现,而非RabbitMQ本身提供的一种直接功能。 在基于Spring Boot整合RabbitMQ的场景下,要保证消费者的幂等性,通常需要结合业务逻辑设计以及额外的技术手段来实现。以下是一个…...

【QT】Qt Charts的实际使用中的一些小细节完善如:resetZoom、fitInView

在Qt中, 使用 Qt Charts来创建和操作图表,重置图表缩放状态的功能可以通过调整图表视图的缩放比例来实现。Qt Charts中的QChartView提供了相关的方法来控制图表的缩放和平移。 示例代码,以及如何对此功能进行扩展: #include <…...

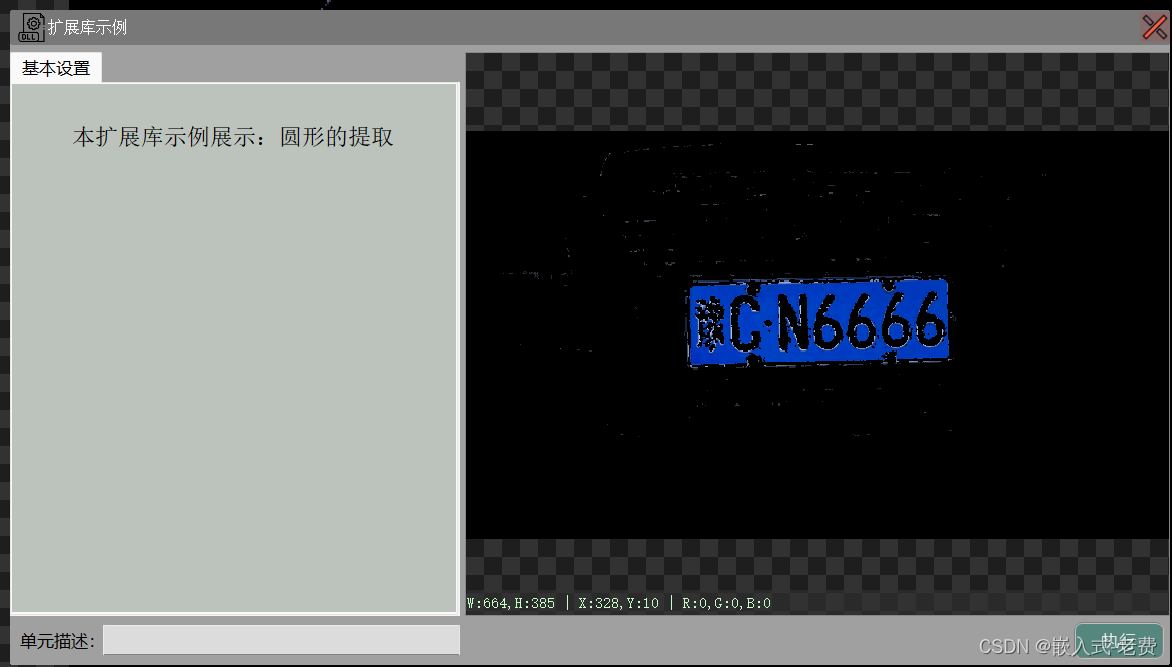

上位机图像处理和嵌入式模块部署(qmacvisual缺失的颜色检测)

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing 163.com】 在图像处理当中,对颜色的处理是非常重要的。当然,这要建立在拍摄图片是彩色图片的基础之上。工业上面,虽然是黑…...

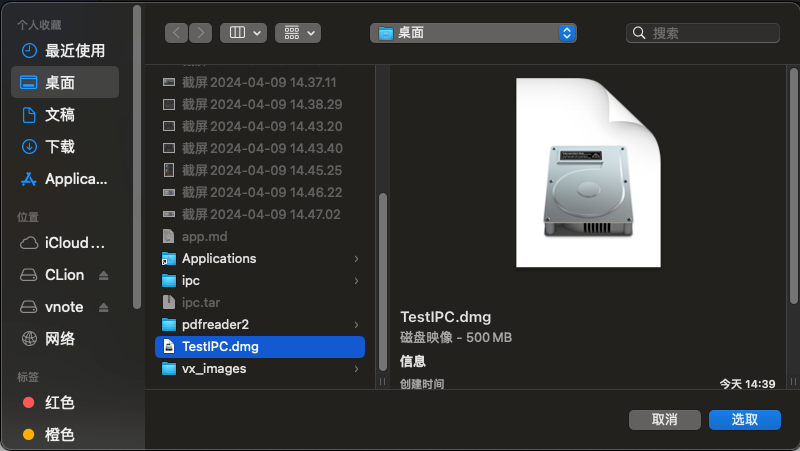

macOS制作C/C++ app

C/C制作macOS .app 一、 .app APP其实是一个文件夹结构,只不过mac的界面中让它看起来像一个单独的文件。 在shell终端或者右键查看包结构即可看到APP的目录结构。 通常的app目录结构如下: _CodeSignature, CodeResources 一般为Mac APP Store上架程序…...

)

学习笔记——C语言基本概念链表——(12)

在介绍链表之前先介绍一下数据结构的分类: 线性结构:数组,链表,栈,队列 顺序结构:数组 链式结构:链表 非线性结构:树,二叉树 1、链表 特点:利用碎片化空…...

开发环境解决跨域问题

跨域 为什么? 浏览器的同源策略(协议,域名,端口必须相等) http://localhost:9528/ (前端页面) ---------------------》后端接口(https://heimahr.itheima.net/api) 后端没有开启CORS 在后端没有开启CO…...

物理服务器与云服务器的租用对比

物理服务器:每个基于 Web 的应用程序都依赖于一个服务器,该服务器提供网络中的数据存储,并可根据请求提供给客户端。例如,用户使用浏览器访问 Web 应用程序。服务器可确保托管客户端可以使用该硬件组件。与其他托管可能性相比&…...

Ubuntu Desktop Server - Resource temporarily unavailable

Ubuntu Desktop Server - Resource temporarily unavailable 1. 问题2. 解决方案References 1. 问题 foreverstrongubuntu:~$ sudo apt-get install libatlas-base-dev [sudo] password for foreverstrong: E: Could not get lock /var/lib/dpkg/lock - open (11: Resource t…...

【人生底稿 28】新疆出差终章:几番波折终汇报,尽兴踏归津门路

三日游玩尽数落幕,忙碌工作正式回归。轻松的闲暇时光悄然收尾,紧绷的工作状态再次上线。整趟新疆之行,在起伏辗转中迎来最终收尾。一、深夜复盘材料,彻夜待汇报游玩结束回到酒店,我没有松懈休息,静下心重新…...

终极免费Switch模拟器yuzu:解决电脑玩任天堂游戏的5大痛点

终极免费Switch模拟器yuzu:解决电脑玩任天堂游戏的5大痛点 【免费下载链接】yuzu 任天堂 Switch 模拟器 项目地址: https://gitcode.com/GitHub_Trending/yu/yuzu 想在电脑上畅玩Switch游戏却总是遇到各种问题?yuzu模拟器作为全球最受欢迎的开源任…...

终极解密指南:Windows平台NCM音频文件一键转换实战

终极解密指南:Windows平台NCM音频文件一键转换实战 【免费下载链接】ncmdumpGUI C#版本网易云音乐ncm文件格式转换,Windows图形界面版本 项目地址: https://gitcode.com/gh_mirrors/nc/ncmdumpGUI 你是否曾因网易云音乐的NCM加密格式而烦恼&…...

基于大语言模型的本地语义搜索工具LLocalSearch部署与应用指南

1. 项目概述:一个能“读懂”你电脑的本地搜索工具 如果你和我一样,电脑里塞满了各种文档、邮件、聊天记录和代码片段,那么“找东西”这件事,绝对能排进日常最耗时的任务前三。传统的文件搜索,比如Windows自带的搜索或者…...

UEFITool终极指南:轻松解析和编辑UEFI固件的开源利器

UEFITool终极指南:轻松解析和编辑UEFI固件的开源利器 【免费下载链接】UEFITool UEFI firmware image viewer and editor 项目地址: https://gitcode.com/gh_mirrors/ue/UEFITool 你是否曾好奇计算机启动时底层发生了什么?想要深入了解UEFI固件的…...

3D打印乐高手机支架:低成本打造高清视频会议摄像头方案

1. 项目概述与核心思路如果你和我一样,对视频会议、直播时笔记本自带摄像头那“感人”的画质感到无奈,同时又觉得单独购买一个高品质的网络摄像头是一笔不小的开销,那么这个项目绝对值得你花上一个周末的时间来折腾。它的核心思路非常巧妙&am…...

构建高可用AI模型代理服务:统一接口、智能路由与生产级部署

1. 项目概述:一个无处不在的AI助手接口最近在折腾AI应用开发的朋友,可能都遇到过这样一个痛点:想在自己的项目里快速接入一个靠谱的、能处理复杂对话的AI模型,但要么被OpenAI的API调用限制和网络问题搞得焦头烂额,要么…...

品牌声音技能化:从模糊概念到可执行AI内容策略

1. 项目概述:品牌声音的“技能化”构建最近在和一些做品牌营销、内容运营的朋友聊天,发现一个挺普遍的现象:大家手里都有一堆品牌手册、VI规范,但一到具体执行,比如写一篇公众号推文、拍一条短视频,或者回复…...

AI编程助手安全规则实战:从SQL注入防御到团队安全基线构建

1. 项目概述:当AI编程助手遇上安全红线最近在GitHub上看到一个挺有意思的项目,叫“cursor-security-rules”。光看名字,你大概能猜到它和Cursor这个AI编程工具有关,而且重点是“安全规则”。没错,这个项目本质上是一个…...

Arm Iris组件参数化建模与调试实践

1. Arm Iris组件概述与核心价值Arm Iris组件是Fast Models仿真平台中的关键模块,它为芯片设计验证和软件开发提供了高度参数化的虚拟原型环境。作为一名长期从事Arm架构开发的工程师,我发现Iris组件的设计理念完美体现了"配置即硬件"的思想——…...