跨时钟域CDC

https://www.cnblogs.com/icparadigm/p/12794483.html

https://www.cnblogs.com/icparadigm/p/12794422.html

亚稳态

是什么

时序逻辑在跳变时,由于异步信号、跨时钟域等原因,不满足setup或hold条件,输出在0和1之间产生振荡。

原因

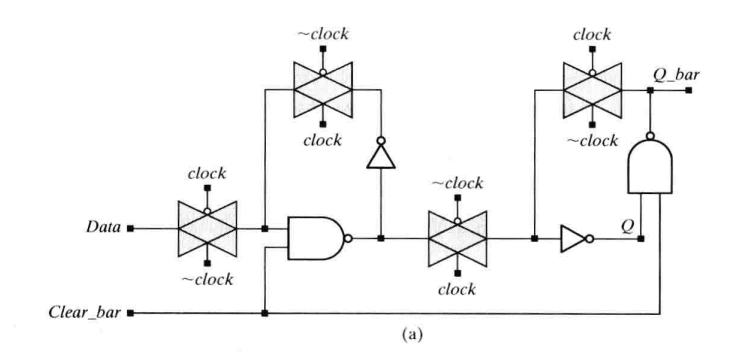

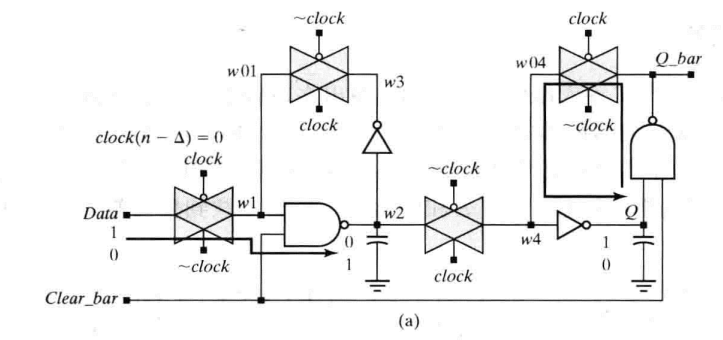

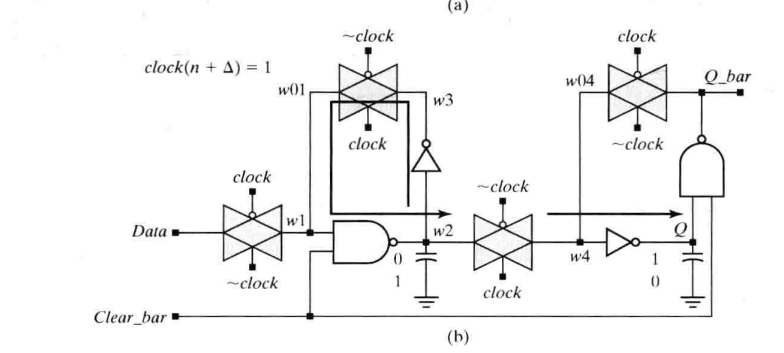

D触发器的内部是一个主从锁存器(master-slave latch),依靠背靠背的反相器锁存数据。

时钟为低电平时,主锁存器更新输入值,从锁存器保持上一个输出值不变。

时钟为高电平时,主锁存器保持上一个输出值不变,从锁存器更新输入。

由于反相器需要一定时间才能锁定,若时钟跳变前后,未完成锁存时钟就改变,最后输出的电平高低会不稳定,这就是亚稳态。

危害

错误的逻辑会一直传递下去导致系统错误。

指标

MTBF-- mean time between failure. 两次失效之间的平均时间。

MTBF(TMET)=eTMETC1∗1C2∗fclk∗fdataMTBF(T_{MET})=\frac{e^{T_{MET}}}{C_1} * \frac{1}{C_2*f_{clk}*f_{data}} MTBF(TMET)=C1eTMET∗C2∗fclk∗fdata1

C1 和C2 是常数,依赖于器件工艺和操作环境。

fCLK 和fDATA 参数取决于设计规格:fCLK 是接收异步信号的时钟域的时钟频率,fDATA 是异步数据的翻转频率(toggling frequency)。

TMET 参数是亚稳态转稳定的时间(Metastability setting time),或者说时序裕量大于寄存器Tco可以让潜在的亚稳态信号达到稳定的值的时间。TMET 对同步链来说就是链中每个寄存器输出时序裕量的和。

减少亚稳态的方法

1. 改善工艺

2. 降低时钟速率和数据翻转。

3. 增大时序裕量(使用多级同步器打拍)

单bit情况

1.慢时钟域到快时钟域(目标时钟频率必须是源时钟频率1.5倍或者以上)

电平同步,直接打拍。

/*+---------+ +---------+ +---------+asynch_in | | meta1 | | meta2 | | synch_out+----------+ D Q +--------+ D Q +-------+ D Q +-------+| | | | | |clk_b | | clk_b | | clk_b| |+----------+ CLK | +------+ CLK | +-----+ CLK || R | | | R | | | |+----+----+ | +-----+---+ | +----+----+| + | + || | || | |+--------------+-------------------+----------------+*/always @(posedge clk_b or posedge rst) beginif(rst) beginmeta1<=0;meta2<=0;synch_out<=0;endelse beginmeta1<=asynch_in;meta2<=meta1;synch_out<=meta2;endendassign pos_out_b=synch_out&~meta2;//高电平跳变沿assign neg_out_b=~synch_out&meta2;//低电平跳变沿

2.快时钟域到慢时钟域

脉冲同步器,即加握手信号,通过组合逻辑把脉冲展宽为电平信号,再向clkb传递,当确认clkb已经“看见”信号同步过去之后,再清掉clka下的电平信号。在应答信号到来之前,不允许源信号改变,可能漏采。

module pluse_sync(input rst_n,input clk_a,input clk_b,input pulse_a_in,output pulse_b_out,output level_b_out);reg q;//展宽脉冲信号reg q1_a2b,q2_a2b,sync_out;//a向b同步信号reg q1_b2a,q2_b2a;//b向a同步信号//q的置位与清零always @(posedge clk_a or negedge rst_n) beginif(~rst_n)q<=0;else if(pulse_a_in)q<=1;else if(q2_b2a)q<=0; end//always@ (posedge clk_b or negedge rst_n) beginif(~rst_n) beginq1_a2b<=0;q2_a2b<=0;sync_out<=0;endelse beginq1_a2b<=q;q2_a2b<=q1_a2b;sync_out<=q2_a2b;endend//always@(posedge clk_a or negedge rst_n) beginif(~rst_n) beginq1_b2a<=0;q2_b2a<=0;endelse beginq1_b2a<=sync_out;q2_b2a<=q1_b2a;endassign pulse_b_out=sync_out&(~q2_a2b);assign level_b_out=sync_out;endmodule

-

在使用同步器同步信号时,要求输入信号必须是源时钟域的寄存输出。即Asynch_in必须是clk_a的DFF信号,中间不能经过组合逻辑。

- 原因:根据FF的特性,输出在一个时钟周期内是不会改变的,数据的变化频率不会超过时钟频率,这样就能降低跨时钟信号变化的频率,减小亚稳态发生的概率

-

应用

-

输入去抖debounce

//可以滤掉的宽度是两个clk的cycle,对于大于两个cycle而小于三个cycle的信号,有些可以滤掉,有些不能滤掉,这与signal_i相对clk的相位有关。 parameter BIT_NUM = 4 ; reg [BIT_NUM-1 : 0] signal_deb ; always @ (posedge clk or negedge rst_n) beginif (rst_n == 1'b0)signal_deb <= {BIT_NUM{1'b0}} ;elsesignal_deb <= # DLY {signal_deb[BIT_NUM-2:0],signal_i} ; endalways @ (posedge clk or negedge rst_n) beginif (rst_n == 1'b0)signal_o <= 1'b1 ;else if (signal_deb[3:1]==3'b111) signal_o <= # DLY 1'b1 ;else if (signal_deb[3:1]==3'b000)signal_o <= # DLY 1'b0 ;else ; end根据希望滤除的宽度,换算到clk下是多少个cycle数,从而决定使用多少级DFF。

如果希望滤除的宽度相对cycle数而言较大,可以先在clk下做一个计数器,产生固定间隔的脉冲,再在脉冲信号有效时使用多级DFF去抓signal_i;或者直接将clk分频后再使用。

也不一定全为1或0才判断有效/无效,见project/uart_tx 输入去抖。

-

多bit情况

-

多个信号合并

如果可能,将多个信号合为一个传递。

-

多周期路径法

(常见于单bit同步,多bit一般用AFIFO)

-

使用格雷码传递多个CDC位

格雷码最常见的应用是在异步FIFO中,相邻的状态只变化一位,转化为单bit情况。

**格雷码必须是计数到2n才是每次改变一个bit。**如果计数器是从0~5计数,那么从5->0的计数,不止一个bit改变,就失去了只改变一个bit的初衷。所以就算浪费面积,也需要把FIFO深度设置为2N。

-

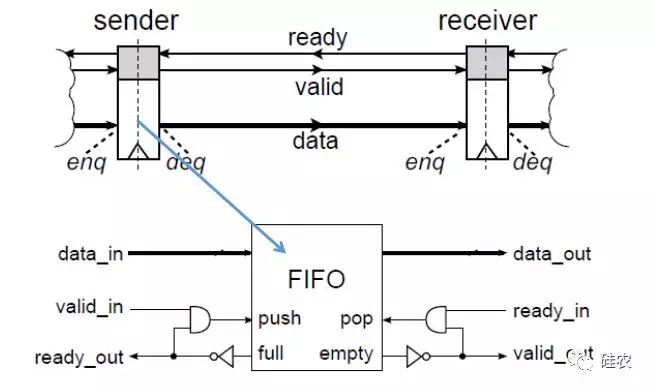

使用异步FIFO来传递多位信号

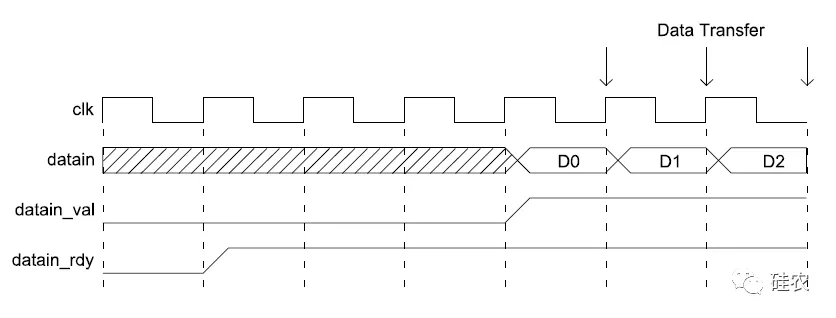

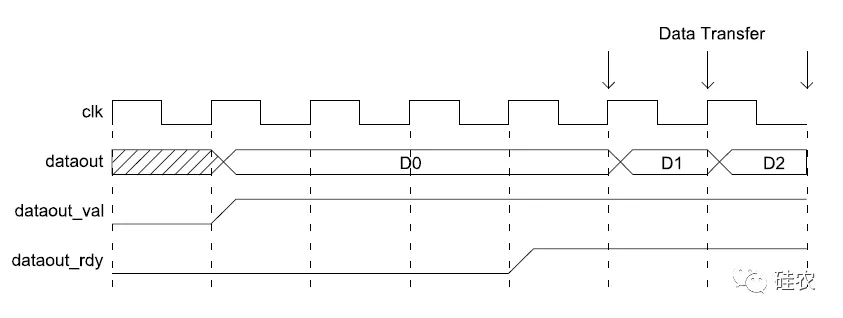

Valid-Ready握手协议

https://blog.csdn.net/maowang1234588/article/details/100065072

VALID信号由源设备控制,READY信号由宿设备控制。源设备拉起VALID信号表示其把数据(或地址等信号)放上了总线,等待宿设备接收;在宿设备接收数据以前,源设备必须要保持住总线上的数据不变。宿设备只有在可以接收数据时,才可以拉起READY信号,否则只能拉低READY信号。只有当VALID和READY信号同时有效时,一次数据传输才算完成。

AXI协议保障数据正确传输使用了该握手协议,所有的通道都采用同样的握手协议。

Valid-Ready信号产生有两种情况。

-

Ready-Before-Valid

Ready-Before-Valid是Ready信号在Valid信号之前有效。在数据来临之前,通道已准备好接收数据,可以保持通道的最大吞吐量,因为Ready先产生,这个通道保持刷新等待数据。通道作为接受数据端采用这样的设计。

-

Valid-before-Ready

Valid-before-Ready是Valid信号在Ready信号之前有效。通道作为数据输出端采用这样的设计。收到下游接收端的准备接收信号,才开始传输数据。

-

Stalemate 死锁

输出端用Ready-Before-Valid而接受端使用Valid-before-Ready,就会出现输出端等待接受端给出的Ready来输出数据,但是接收端也在等待输出端给出Valid信号来接受数据。两者都在等待却没有一方先给,所以这个时候这个通道就是无效的,被“锁住”了。

-

verilog实现

-

无缓存(见典型电路)

-

带缓存(用同步FIFO实现)

assign valid_o = ~fifo_empty; assign ready_o = ~fifo_full; assign wr_en = ready_o & valid_i; assign rd_en = ready_i & valid_o;

-

相关文章:

跨时钟域CDC

https://www.cnblogs.com/icparadigm/p/12794483.html https://www.cnblogs.com/icparadigm/p/12794422.html 亚稳态 是什么 时序逻辑在跳变时,由于异步信号、跨时钟域等原因,不满足setup或hold条件,输出在0和1之间产生振荡。 原因 D触发…...

JavaEE简单示例——Spring的控制反转

简单介绍: 在之前的入门程序中,我们简单的介绍了关于Spring框架中的控制反转的概念,这次我们就来详细的介绍和体验一下Spring中的控制反转的理论和实操。 使用方法: 控制反转(IoC)是面向对象编程中的一个…...

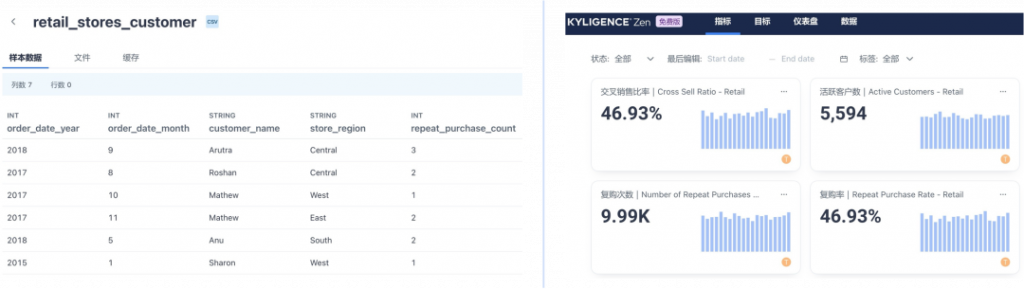

DBT 收购 Transform,指标平台已成现代数据栈关键拼图

今年 2 月初,现代数据技术栈独角兽 DBT 宣布完成对 Transform 的并购。在现代数据栈的体系中,DBT 和 Transform 都扮演着重要角色,DBT 侧重于整个分析链路上的数据转换处理,而 Transform 则聚焦在以指标为中心搭建业务分析应用。 …...

@Value注解取不到值的几种错误

在程序中使用了yml文件,然后把有些参数写在里面作为全局变量,在定时器里面使用,但是后来发现取不到: @Value("${spring.datasource.druid.master.url}") private String url; @Value("${spring.datasource.druid.master.driver-class-name}") private …...

听客户说|东台农商银行:建立健全数据安全管理制度的探索与实践

夯实银行数据安全,需“规划先行、谋定后动”,首要工作是确立管理工作的行动纲要,并据此建立制度保障体系以贯彻纲要,而后才是具体的行动措施和日常检查、监测。从银行数据安全建设实践路径来说,我认为可以用“盘现状、…...

Benchbot环境安装记录

https://github.com/qcr/benchbot 第一次安装这种复合型的环境,包括了各种CUDA/NVIDA驱动、Docker环境、python环境等等。因此,遇到了一大堆的问题,在此记录一下亲测有效的博客: https://zhuanlan.zhihu.com/p/378894743 https:/…...

Barrett模乘与蒙哥马利模乘算法

一、背景 公钥密码学(Public-Key Cryptography, PKC)由Diffie与Hellman于1970年代提出,在现代信息社会中得到了广泛应用。此后基于各种数学困难问题,越来越多的公钥密码算法被设计出来,比如RSA、ElGamal、椭圆曲线ECC算法等。在RSA算法中,模幂(modular exponentiation)…...

slice方法

slice方法与splice方法相比slice方法不会修改原数组一、语法以及描述说明:通过start 和 end对原数组进行浅拷贝(提取 start 至 end 索引的数组元素)语法:Array.slice([start[, end])参数:start : 开始索引end : 结束索…...

DevOps工具集合

简介 DevOps(Development和Operations的组合词)是一组过程、方法与系统的统称,用于促进开发(应用程序/软件工程)、技术运营和质量保障(QA)部门之间的沟通、协作与整合。 它是一种重视“软件开…...

手把手教你安装Linux!!!

文章目录Linux简述它们的区别安装CentOS①下载CentOS②安装Linux有两种方式③下载模拟软件④安装vmware⑤创建虚拟机⑥安装操作系统Linux简述 在国内比较流行的两款Linux发行版本CentOS和ubuntu 它们的区别 ubuntu:页面更加的华丽比较漂亮,它对计算机…...

图像分割(Unet算法学习笔记)

知识提要 数据集使用VOC2012 CNN 卷积神经网络Convolutional Neural Network GPU图像处理单元Graphic Processing Unit)图形处理器 convolution 卷积 ReLU全名Rectified Linear Unit,意思是修正线性单元 bn全称Batch Normalization批标准化 FC全连接神经网络是一种…...

Fortinet 发布《2022下半年度全球威胁态势研究报告》,七大发现值得关注

全球网络与安全融合领域领导者Fortinet(NASDAQ:FTNT),近日发布《2022 下半年度全球威胁态势研究报告》。报告指出,相对于组织攻击面的不断扩大以及全球威胁态势的持续演进,网络犯罪分子设计、优化技术与战术…...

ThinkPHP 6.1 模板篇之循环和选择标签

本文主要介绍在视图模板中,如何使用循环和选择标签去渲染变量及常用循环和选择标签。 目录 循环标签 foreach 标签 for 标签 volist 标签 选择标签 switch 标签 if 标签 范围标签 原生标签 总结 循环标签 foreach 标签 将查找到的数组或数据集ÿ…...

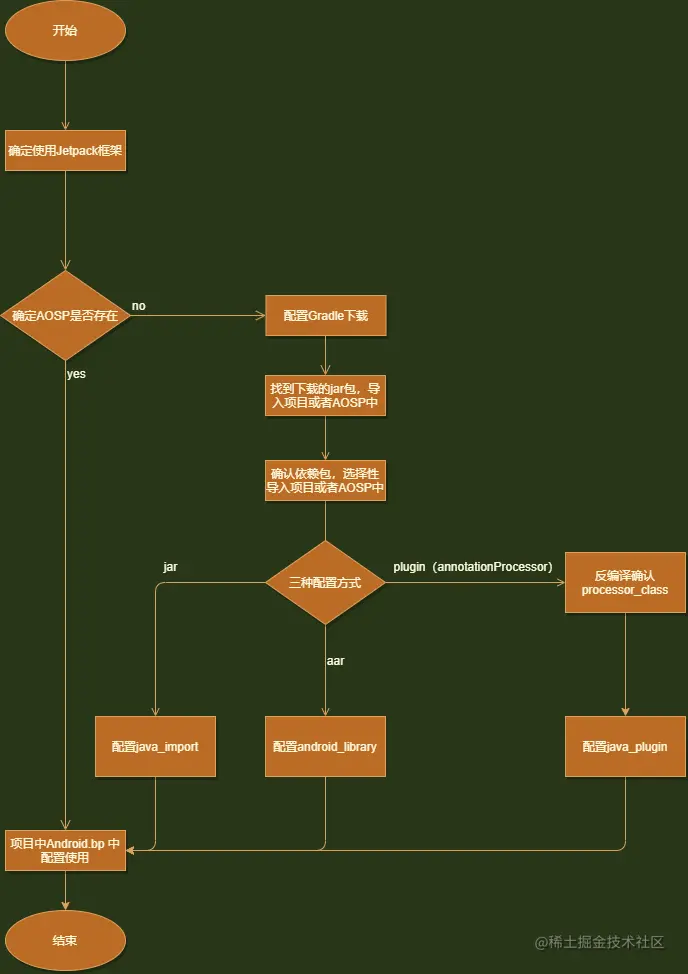

Jetpack太香了,让开发效率提升了不少

作者:Jingle_zhang 第三方App使用Jetpack等开源框架非常流行,在Gradle文件简单指定即可。然而ROM内置的系统App在源码环境下进行开发,与第三方App脱节严重,采用开源框架的情况并不常见。但如果系统App也集成了Jetpack或第三方框架…...

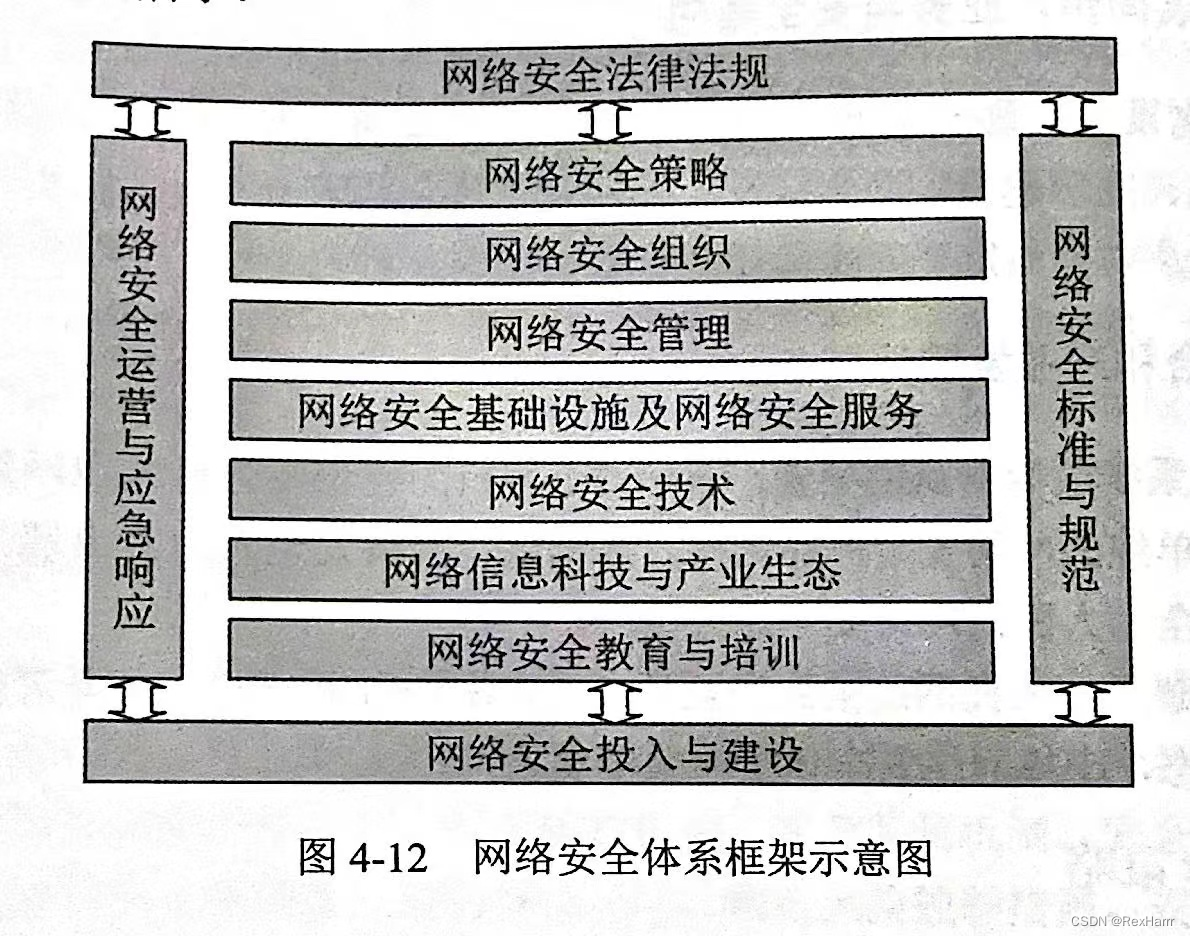

【软考中级信安】第四章--网络安全体系与网络安全模型

1.网络安全体系概述1.1 网络安全体系概念网络安全体系:是网络安全保障系统的最高层概念抽象,是由各种网络安全单元按照一定的规则组成的,共同实现网络安全的目标。1.2 网络安全体系特性整体性:网络安全单元按照一定规则࿰…...

四、GC分析内存调优

文章目录(持续更新中... ...)GC分析&内存调优工具篇JDK自带的工具jconsolejvisualvm第三方工具arthas(重要)jprofiler(收费的)MAT、GChisto、gcviewer、GC Easy(待完善)参数、命…...

如何快速开发一套分布式IM系统

架构说明: 1)CIM 中的各个组件均采用 SpringBoot 构建;2)采用 Netty Google Protocol Buffer 构建底层通信;3)Redis 存放各个客户端的路由信息、账号信息、在线状态等;4)Zookeeper …...

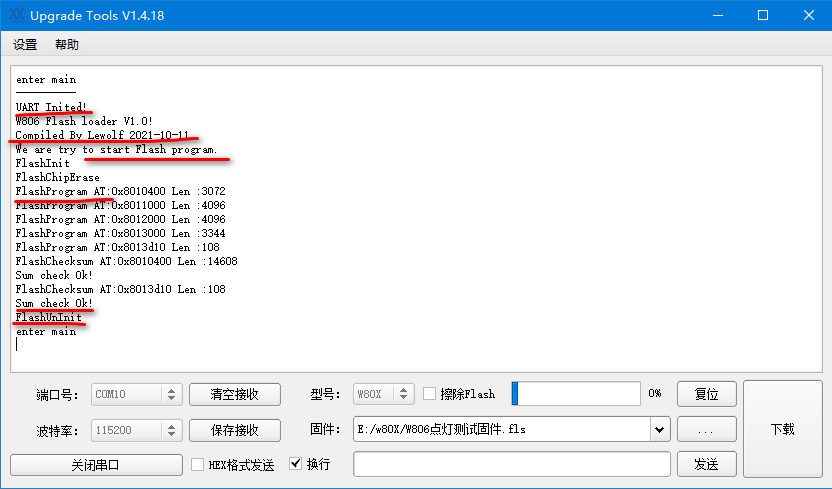

W806|CKLINK LITE|调试|elf文件模板|CSDK|Debug|学习(4):CKLINK调试W806

一、硬件连接 接线方式 (连线颜色供参考,本例中采用图示颜色): 注意:CKLINK LITE的3V3须与W806的3V3相连,或者给W806开发板单独供电,两种方式均可。 否则,会提示“the referenc…...

【100个 Unity实用技能】 ☀️ | 脚本无需挂载到游戏对象上也可执行的方法

Unity 小科普 老规矩,先介绍一下 Unity 的科普小知识: Unity是 实时3D互动内容创作和运营平台 。包括游戏开发、美术、建筑、汽车设计、影视在内的所有创作者,借助 Unity 将创意变成现实。Unity 平台提供一整套完善的软件解决方案ÿ…...

「IT女神勋章」挑战赛#

缓存 本地缓存 本地缓存为了保证线程安全问题,一般使用ConcurrentMap的方式保存在内存之中 分布式缓存。 常见的分布式缓存则有Redis,MongoDB等。 一致性:本地缓存由于数据存储于内存之中,每个实例都有自己的副本,…...

QT----集成onnxRuntime实现图像分类应用实战

1. 环境准备与工具链搭建 在开始构建QTonnxRuntime图像分类应用之前,我们需要先准备好开发环境。这里我推荐使用Windows系统作为开发平台,因为大多数QT开发者都习惯在这个环境下工作。首先需要安装Visual Studio 2019或更高版本,这是编译QT应…...

借助aibye智能工具高效完善毕业论文任务书范文,整合7大优质平台的AI修改功能提升学术写作质量

工具名称 核心功能 生成速度 适用场景 独特优势 aibiye 论文初稿生成 20-30分钟 全学科通用 自动插入图表公式 aicheck 初稿查重 20-30分钟 急需查重场景 独创降AIGC算法 askpaper 初稿生成 20-30分钟 理工科专业 支持代码片段 秒篇 快速生成 10-15分钟 …...

Win11Debloat:Windows系统轻量优化解决方案

Win11Debloat:Windows系统轻量优化解决方案 【免费下载链接】Win11Debloat 一个简单的PowerShell脚本,用于从Windows中移除预装的无用软件,禁用遥测,从Windows搜索中移除Bing,以及执行各种其他更改以简化和改善你的Win…...

网络安全这个技能学会了,不考研也能迅速找到高薪工作

网络安全这个技能学会了,不考研也能迅速找到高薪工作 近几年“考研热”持续升温,报名人数和报录比屡创新高。据数据显示:2003年全国考研人数仅仅才70万,直至2017年考研人数才刚刚突破200万。而今年考研人数居高达457万࿰…...

Newtonsoft.Json-for-Unity:Unity开发者的终极JSON解决方案指南

Newtonsoft.Json-for-Unity:Unity开发者的终极JSON解决方案指南 【免费下载链接】Newtonsoft.Json-for-Unity Newtonsoft.Json (Json.NET) 10.0.3, 11.0.2, 12.0.3, & 13.0.1 for Unity IL2CPP builds, available via Unity Package Manager 项目地址: https:…...

无线通信入门:为什么说DFT是提升OFDM信道估计性能的“降噪神器”?

无线通信中的降噪艺术:DFT如何让OFDM信道估计更精准 想象一下,你正试图在嘈杂的咖啡馆里听清朋友的谈话。背景音乐、周围人的聊天声、杯盘碰撞声都在干扰你获取清晰的信息。无线通信中的信道估计面临类似的挑战——如何在充满噪声的传输环境中࿰…...

告别手动调参!模糊PID如何让直流电机在负载突变时稳如泰山?

模糊PID控制:让直流电机在负载突变时稳如泰山的实战指南 引言:工业自动化中的电机控制痛点 在自动化产线上,直流电机突然遭遇负载变化时,你是否也经历过这样的场景?——机械臂正在精准抓取工件,突然因为物料…...

大小写转换实战:批量处理表名与字段名的自动化方案)

PostgreSQL(OpenGauss/MogDB) 大小写转换实战:批量处理表名与字段名的自动化方案

1. 为什么PostgreSQL的大小写问题让人头疼? 第一次用PostgreSQL的时候,我就被它的大小写规则坑惨了。明明在Oracle里运行好好的SQL语句,搬到PostgreSQL就报"relation does not exist"错误。后来才发现,原来PostgreSQL对…...

)

Python实战:用Statsmodels搞定简单线性回归(附NO浓度预测案例)

Python实战:用Statsmodels搞定简单线性回归(附NO浓度预测案例) 在数据分析领域,线性回归是最基础却最实用的统计方法之一。无论你是市场分析师预测销售额,还是环境科学家研究污染物分布,掌握线性回归都能让…...

3步搞定Windows 11优化:用Win11Debloat让你的电脑更快更干净

3步搞定Windows 11优化:用Win11Debloat让你的电脑更快更干净 【免费下载链接】Win11Debloat 一个简单的PowerShell脚本,用于从Windows中移除预装的无用软件,禁用遥测,从Windows搜索中移除Bing,以及执行各种其他更改以简…...