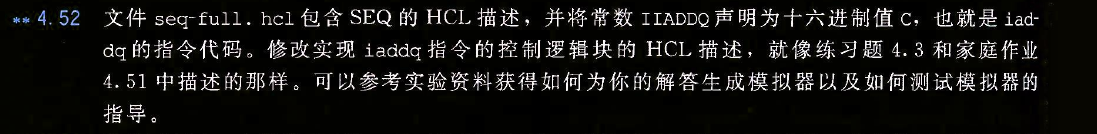

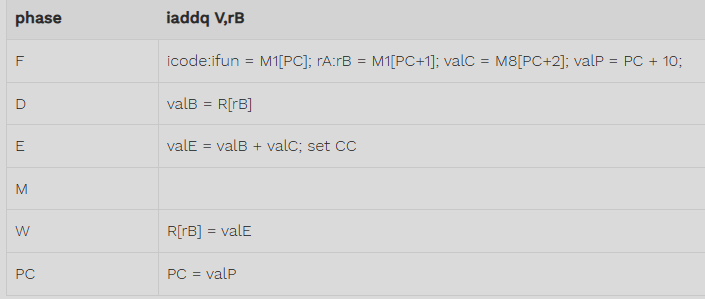

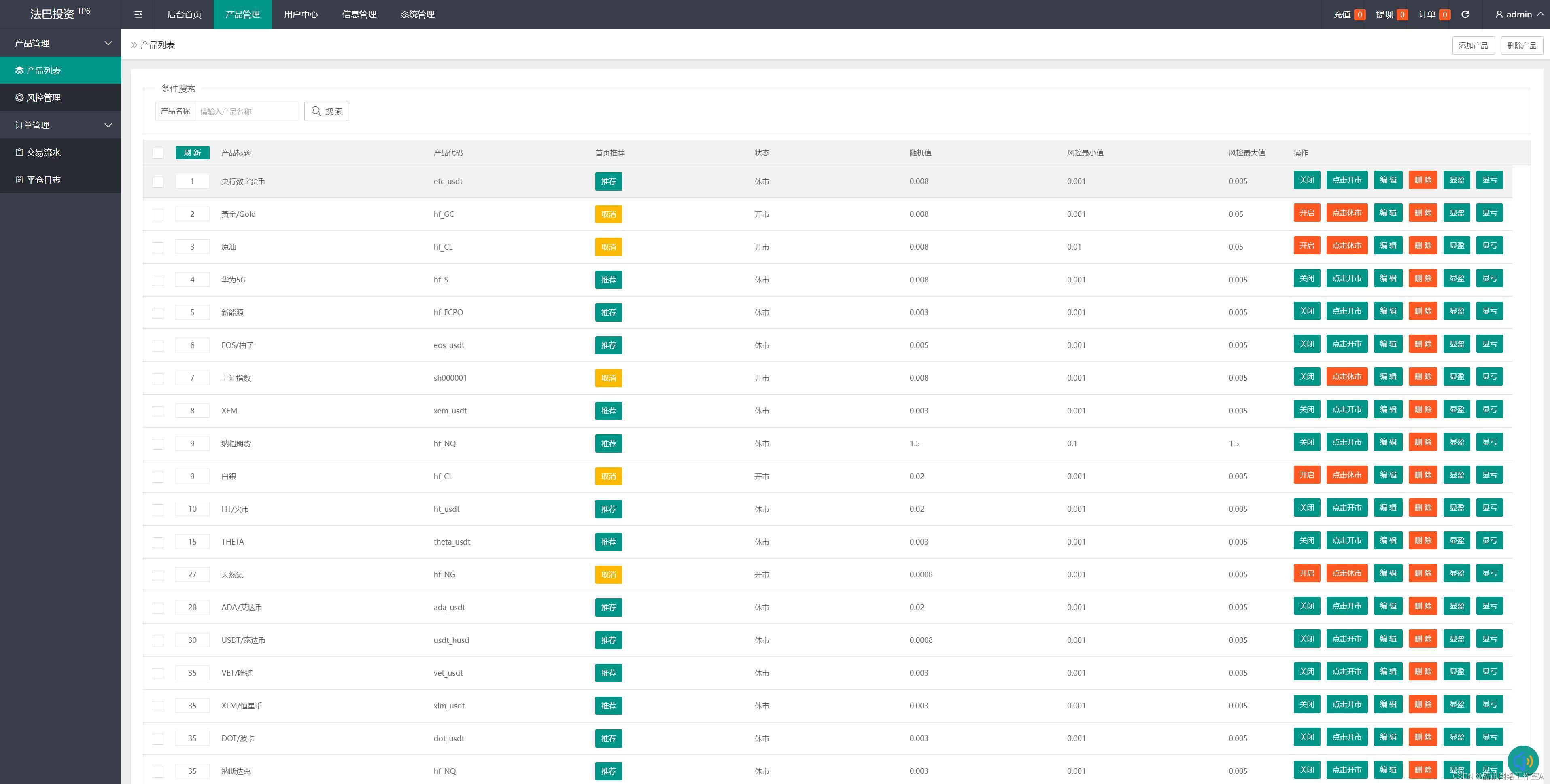

深入理解计算机系统 家庭作业4.52

练习题4.3 p.254

\sim\seq\seq-full.hcl文件内已经说的很清楚了哪些不能更改,哪些是题目要求更改的控制逻辑块.

依据家庭作业4.51的答案,在seq-full.hcl文件内更改对应的HCL描述即可 以下答案注释了#changed的就是更改部分

#/* $begin seq-all-hcl */

####################################################################

# HCL Description of Control for Single Cycle Y86-64 Processor SEQ #

# Copyright (C) Randal E. Bryant, David R. O'Hallaron, 2010 #

###################################################################### Your task is to implement the iaddq instruction

## The file contains a declaration of the icodes

## for iaddq (IIADDQ)

## Your job is to add the rest of the logic to make it work####################################################################

# C Include's. Don't alter these #

####################################################################quote '#include <stdio.h>'

quote '#include "isa.h"'

quote '#include "sim.h"'

quote 'int sim_main(int argc, char *argv[]);'

quote 'word_t gen_pc(){return 0;}'

quote 'int main(int argc, char *argv[])'

quote ' {plusmode=0;return sim_main(argc,argv);}'####################################################################

# Declarations. Do not change/remove/delete any of these #

######################################################################### Symbolic representation of Y86-64 Instruction Codes #############

wordsig INOP 'I_NOP'

wordsig IHALT 'I_HALT'

wordsig IRRMOVQ 'I_RRMOVQ'

wordsig IIRMOVQ 'I_IRMOVQ'

wordsig IRMMOVQ 'I_RMMOVQ'

wordsig IMRMOVQ 'I_MRMOVQ'

wordsig IOPQ 'I_ALU'

wordsig IJXX 'I_JMP'

wordsig ICALL 'I_CALL'

wordsig IRET 'I_RET'

wordsig IPUSHQ 'I_PUSHQ'

wordsig IPOPQ 'I_POPQ'

# Instruction code for iaddq instruction

wordsig IIADDQ 'I_IADDQ'

##### Symbolic represenations of Y86-64 function codes #####

wordsig FNONE 'F_NONE' # Default function code##### Symbolic representation of Y86-64 Registers referenced explicitly #####

wordsig RRSP 'REG_RSP' # Stack Pointer

wordsig RNONE 'REG_NONE' # Special value indicating "no register"##### ALU Functions referenced explicitly #####

wordsig ALUADD 'A_ADD' # ALU should add its arguments##### Possible instruction status values #####

wordsig SAOK 'STAT_AOK' # Normal execution

wordsig SADR 'STAT_ADR' # Invalid memory address

wordsig SINS 'STAT_INS' # Invalid instruction

wordsig SHLT 'STAT_HLT' # Halt instruction encountered##### Signals that can be referenced by control logic ####################

##### Fetch stage inputs #####

wordsig pc 'pc' # Program counter

##### Fetch stage computations #####

wordsig imem_icode 'imem_icode' # icode field from instruction memory

wordsig imem_ifun 'imem_ifun' # ifun field from instruction memory

wordsig icode 'icode' # Instruction control code

wordsig ifun 'ifun' # Instruction function

wordsig rA 'ra' # rA field from instruction

wordsig rB 'rb' # rB field from instruction

wordsig valC 'valc' # Constant from instruction

wordsig valP 'valp' # Address of following instruction

boolsig imem_error 'imem_error' # Error signal from instruction memory

boolsig instr_valid 'instr_valid' # Is fetched instruction valid?##### Decode stage computations #####

wordsig valA 'vala' # Value from register A port

wordsig valB 'valb' # Value from register B port##### Execute stage computations #####

wordsig valE 'vale' # Value computed by ALU

boolsig Cnd 'cond' # Branch test##### Memory stage computations #####

wordsig valM 'valm' # Value read from memory

boolsig dmem_error 'dmem_error' # Error signal from data memory####################################################################

# Control Signal Definitions. #

#################################################################################### Fetch Stage #################################### Determine instruction code

word icode = [imem_error: INOP;1: imem_icode; # Default: get from instruction memory

];# Determine instruction function

word ifun = [imem_error: FNONE;1: imem_ifun; # Default: get from instruction memory

];bool instr_valid = icode in { INOP, IHALT, IRRMOVQ, IIRMOVQ, IRMMOVQ, IMRMOVQ,IOPQ, IJXX, ICALL, IRET, IPUSHQ, IPOPQ, IIADDQ};#changed# Does fetched instruction require a regid byte?

bool need_regids =icode in { IRRMOVQ, IOPQ, IPUSHQ, IPOPQ, IIRMOVQ, IRMMOVQ, IMRMOVQ , IIADDQ};#changed# Does fetched instruction require a constant word?

bool need_valC =icode in { IIRMOVQ, IRMMOVQ, IMRMOVQ, IJXX, ICALL , IIADDQ}};#changed################ Decode Stage ##################################### What register should be used as the A source?

word srcA = [icode in { IRRMOVQ, IRMMOVQ, IOPQ, IPUSHQ } : rA;icode in { IPOPQ, IRET } : RRSP;1 : RNONE; # Don't need register

];## What register should be used as the B source?

word srcB = [icode in { IOPQ, IRMMOVQ, IMRMOVQ, IIADDQ } : rB;#changedicode in { IPUSHQ, IPOPQ, ICALL, IRET } : RRSP;1 : RNONE; # Don't need register

];## What register should be used as the E destination?

word dstE = [icode in { IRRMOVQ } && Cnd : rB;icode in { IIRMOVQ, IOPQ, IIADDQ} : rB;#changedicode in { IPUSHQ, IPOPQ, ICALL, IRET } : RRSP;1 : RNONE; # Don't write any register

];## What register should be used as the M destination?

word dstM = [icode in { IMRMOVQ, IPOPQ } : rA;1 : RNONE; # Don't write any register

];################ Execute Stage ##################################### Select input A to ALU

word aluA = [icode in { IRRMOVQ, IOPQ } : valA;icode in { IIRMOVQ, IRMMOVQ, IMRMOVQ , IIADDQ} : valC;#changedicode in { ICALL, IPUSHQ } : -8;icode in { IRET, IPOPQ } : 8;# Other instructions don't need ALU

];## Select input B to ALU

word aluB = [icode in { IRMMOVQ, IMRMOVQ, IOPQ, ICALL, IPUSHQ, IRET, IPOPQ , IIADDQ} : valB;#changedicode in { IRRMOVQ, IIRMOVQ } : 0;# Other instructions don't need ALU

];## Set the ALU function

word alufun = [icode == IOPQ : ifun;1 : ALUADD;

];## Should the condition codes be updated?

bool set_cc = icode in { IOPQ , IIADDQ};#changed################ Memory Stage ##################################### Set read control signal

bool mem_read = icode in { IMRMOVQ, IPOPQ, IRET };## Set write control signal

bool mem_write = icode in { IRMMOVQ, IPUSHQ, ICALL };## Select memory address

word mem_addr = [icode in { IRMMOVQ, IPUSHQ, ICALL, IMRMOVQ } : valE;icode in { IPOPQ, IRET } : valA;# Other instructions don't need address

];## Select memory input data

word mem_data = [# Value from registericode in { IRMMOVQ, IPUSHQ } : valA;# Return PCicode == ICALL : valP;# Default: Don't write anything

];## Determine instruction status

word Stat = [imem_error || dmem_error : SADR;!instr_valid: SINS;icode == IHALT : SHLT;1 : SAOK;

];################ Program Counter Update ############################## What address should instruction be fetched atword new_pc = [# Call. Use instruction constanticode == ICALL : valC;# Taken branch. Use instruction constanticode == IJXX && Cnd : valC;# Completion of RET instruction. Use value from stackicode == IRET : valM;# Default: Use incremented PC1 : valP;

];

#/* $end seq-all-hcl */相关文章:

深入理解计算机系统 家庭作业4.52

练习题4.3 p.254 \sim\seq\seq-full.hcl文件内已经说的很清楚了哪些不能更改,哪些是题目要求更改的控制逻辑块. 依据家庭作业4.51的答案,在seq-full.hcl文件内更改对应的HCL描述即可 以下答案注释了#changed的就是更改部分 #/* $begin seq-all-hcl */ ######################…...

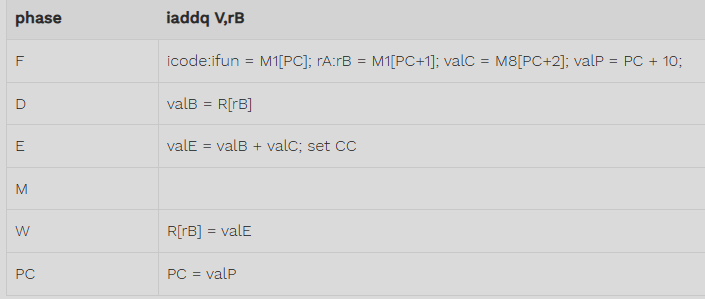

深度学习:手撕 RNN(2)-RNN 的常见模型架构

本文首次发表于知乎,欢迎关注作者。 上一篇文章我们介绍了一个基本的 RNN 模块。有了 这个 RNN 模块后,就像搭积木一样,以 RNN 为基本单元,根据不同的任务或者需求,可以构建不同的模型架构。本节介绍的所有结构&#…...

【Linux进程篇】Linux进程管理——进程创建与终止

W...Y的主页 😊 代码仓库分享💕 目录 进程创建 fork函数初识 写时拷贝 fork常规用法 fork调用失败的原因 进程终止 进程退出场景 _exit函数 exit函数 return退出 进程创建 fork函数初识 在linux中fork函数时非常重要的函数,它从已…...

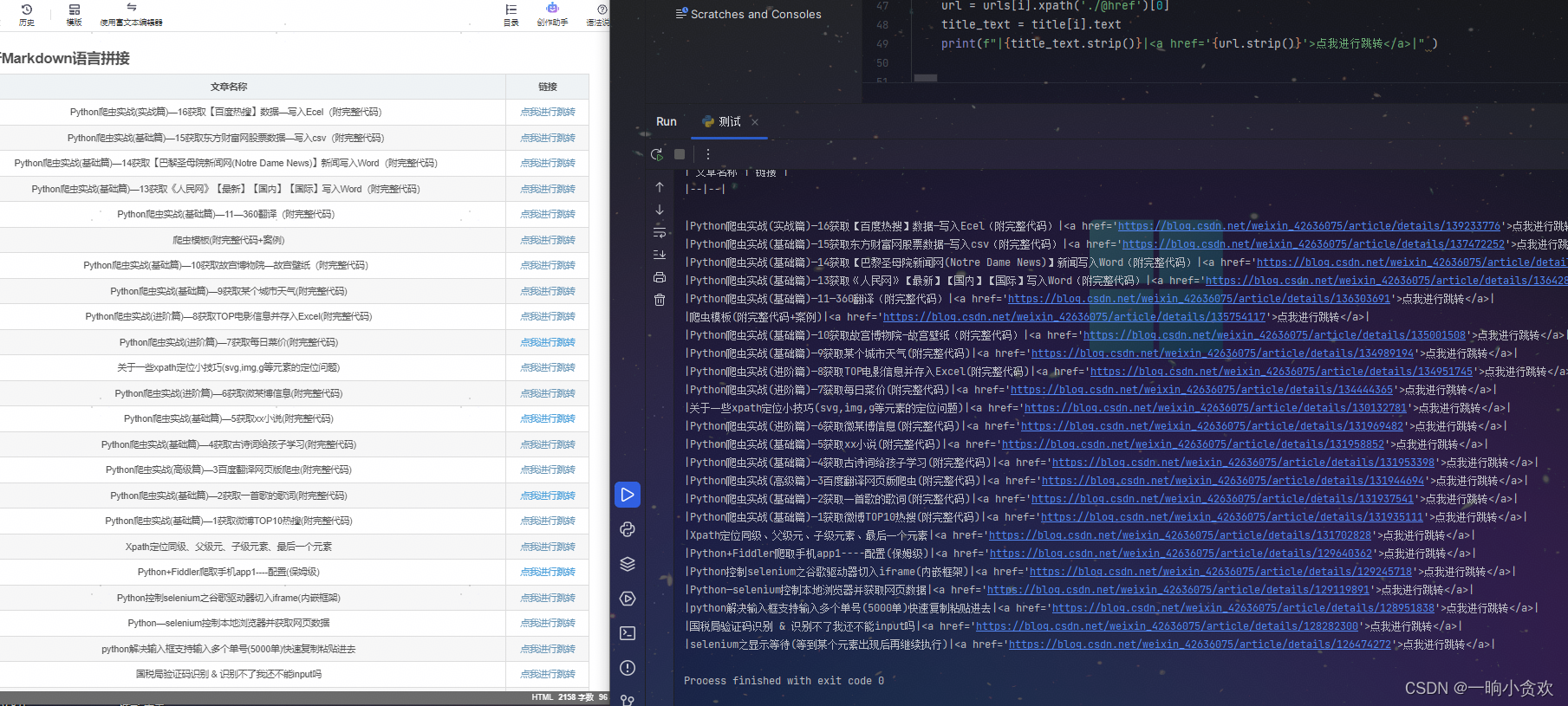

Python爬虫实战(实战篇)—17获取【CSDN某一专栏】数据转为Markdown列表放入文章中

文章目录 专栏导读背景结果预览1、页面分析2、通过返回数据发现适合利用lxmlxpath3、进行Markdown语言拼接总结 专栏导读 在这里插入图片描述 🔥🔥本文已收录于《Python基础篇爬虫》 🉑🉑本专栏专门针对于有爬虫基础准备的一套基…...

Go语言-big.Int

文章目录 Go 语言 big.Int应用场景:大整数位运算使用举例: go sdk中crypto/ecdsa 椭圆曲线生成私钥相关结构中就有使用 Go 语言 big.Int Go 语言 big.Int 参考URL: https://blog.csdn.net/wzygis/article/details/82867793 math/big 作为 Go 语言提供的…...

); 会导致内存泄露吗?里面有SurfaceView ViewBinding)

getContentView(mBinding.getRoot()); 会导致内存泄露吗?里面有SurfaceView ViewBinding

在上述代码中,ActivityTestingBinding 是一个 Data Binding 库生成的类,用于绑定 XML 布局到 Activity 中。inflate(getLayoutInflater()) 用于将布局文件解析并转换为对应的视图层次结构。然后 getWindow().setFlags() 设置窗口属性,保持屏幕…...

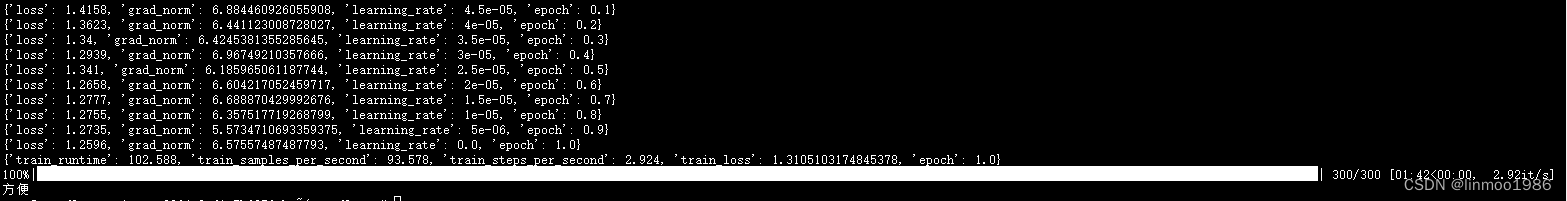

基于transformers框架实践Bert系列6-完形填空

本系列用于Bert模型实践实际场景,分别包括分类器、命名实体识别、选择题、文本摘要等等。(关于Bert的结构和详细这里就不做讲解,但了解Bert的基本结构是做实践的基础,因此看本系列之前,最好了解一下transformers和Bert…...

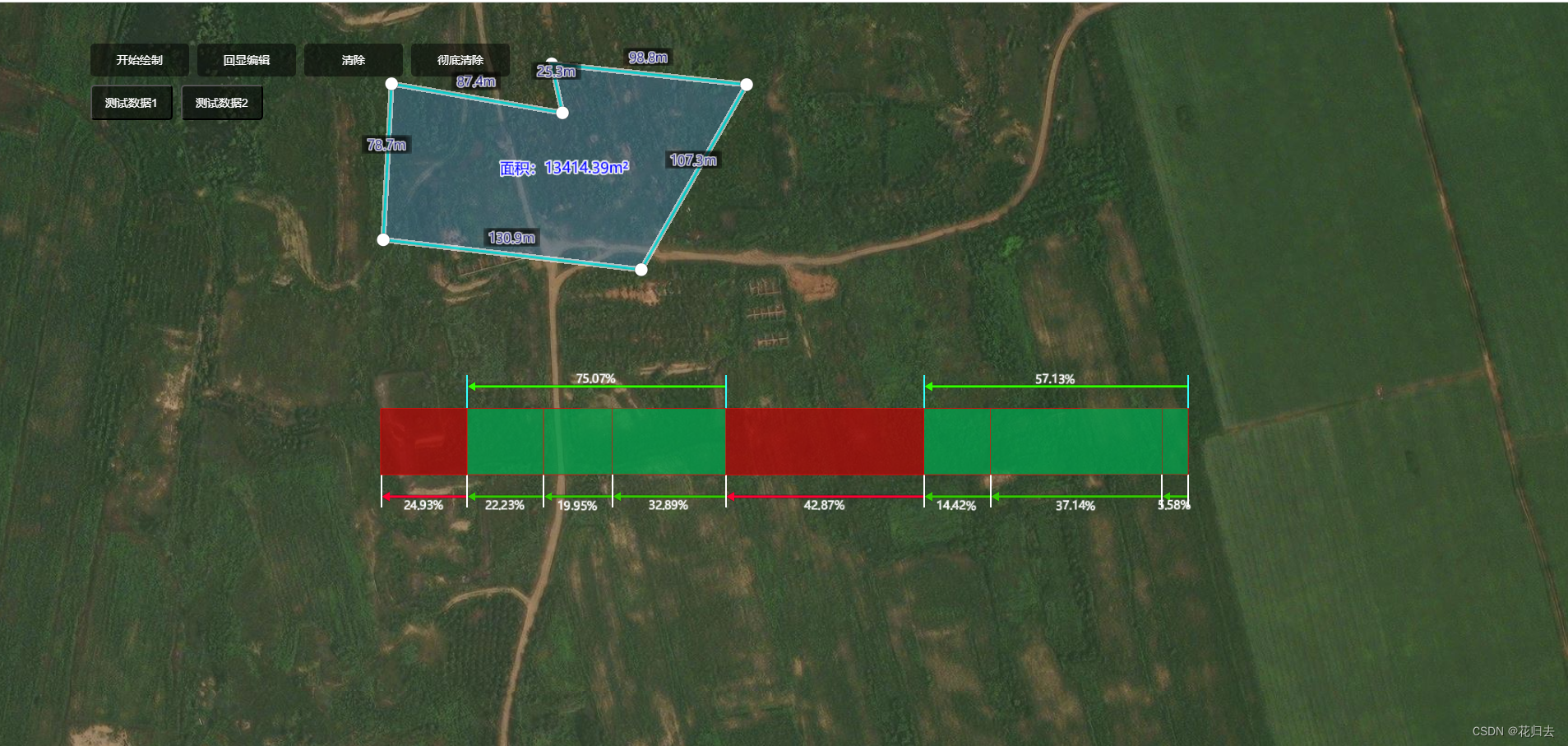

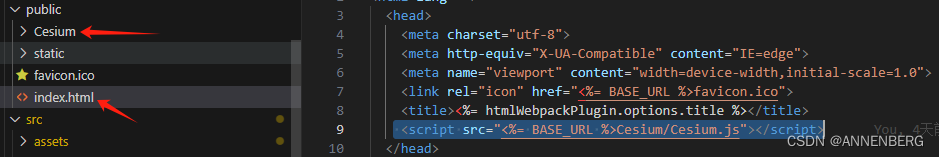

cesium绘制编辑区域

npm 安装也是可以的 #默认安装最新的 yarn add cesium#卸载插件 yarn remove cesium#安装指定版本的 yarn add cesium1.96.0#安装指定版本到测试环境 yarn add cesium1.96.0 -D yarn install turf/turf token记得换成您自己的!!! <t…...

数据库攻防之MySQL

MySQL 是最流行的关系型数据库,与此同时也是 web 应用中最好的关系型数据库管理应用软件。我们在渗透过程中碰到的 PHP 站点大部分都会搭配 MySQL 数据库,因此它是红队攻防中最常遇到的数据库。 0x01 MySQL简介 MySQL 是典型的关系型数据库,…...

八国多语言微盘微交易所系统源码 单控点控 K线完好

安装环境linux NGMySQL5.6PHP7.2(函数全删)pm2管理器(node版本选择v12.20.0) config/ database.php 修改数据库链接 设置运行目录 public 伪静态thinkphp...

爪哇,我初学乍道

>>上一篇(学校上课,是耽误我学习了。。) 2016年9月,我大二了。 自从我发现上课会耽误我学习,只要我认为不影响我期末学分的,我就逃课了。 绝大多数课都是要签到的,有的是老师突击喊名字…...

-限制)

【MySQL精通之路】全文搜索(5)-限制

主博客:【MySQL精通之路】全文搜索功能-CSDN博客 全文搜索仅支持InnoDB和MyISAM表。 分区表不支持全文搜索。参见“分区的限制和限制”。 全文搜索可用于大多数多字节字符集。 例外的是,对于Unicode,可以使用utf8mb3或utf8mb4字符集ÿ…...

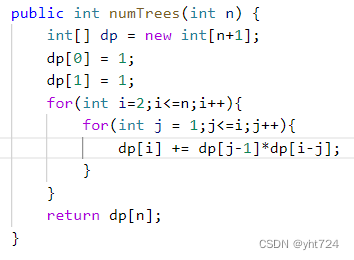

动态规划part03 Day43

LC343整数拆分(未掌握) 未掌握分析:dp数组的含义没有想清楚,dp[i]表示分解i能够达到的最大乘积,i能够如何分解呢,从1开始遍历,直到i-1;每次要不是j和i-j两个数,要不是j和…...

Activity->Activity生命周期和启动模式

<四大组件 android:name"xxx"android:exported"true" // 该组边能够被其他组件启动android:enabled"true" // 该组件能工与用户交互 </四大组件>Activity常用生命周期 启动Activity 2024-05-29 03:53:57.401 21372-21372 yang …...

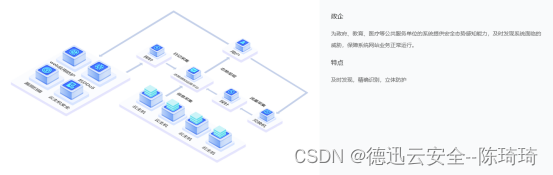

浅谈网络安全态势感知

前言 网络空间环境日趋复杂,随着网络攻击种类和频次的增加,自建强有力的网络安全防御系统成为一个国家发展战略的一部分,而网络态势感知是实现网络安全主动防御的重要基础和前提。 什么是网络安全态势感知? 态势感知一词来源于对…...

cesium本地文档-天空盒-arcgis切片404-服务查询

1.vite-plugin-cesium // vite-plugin-cesium 是一个 Vite 插件,用于在 Vite 项目中轻松集成和使用 Cesium 地图引擎。它简化了在 Vite 项目中使用 Cesium 的配置和引入过程。 // 具体来说,vite-plugin-cesium 主要提供了以下功能: // 自动…...

OpenMv图片预处理

本博客讲述的是获取一张图片首先对图像进行处理,比如畸形矫正,图像滤波等操作。 1.histeq()自适应直方图均衡 # 自适应直方图均衡例子 # # 此示例展示了如何使用自适应直方图均衡来改善图像中的对比度。 #自适应直方图均衡将图像分割成区域,然后均衡这些区域中的直方图,…...

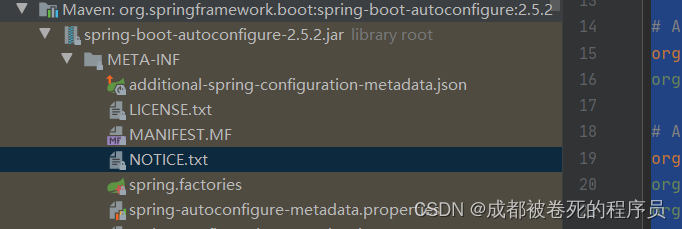

Springboot 实战运用

一,基本配置 1,pom文件配置介绍 1.1继承 <parent><groupId>org.springframework.boot</groupId><artifactId>spring-boot-starter-parent</artifactId><version>2.5.2</version><relativePath/> <…...

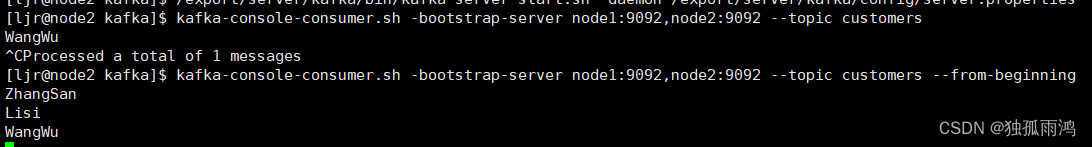

kafka的安装与简单使用

下载地址:Apache Kafka 1. 上传并解压安装包 tar -zxvf kafka_2.13-3.6.2.tgz 修改文件名:mv kafka_2.13-3.6.2 kafka 2. 配置环境变量 sudo vim /etc/profile #配置kafka环境变量 export KAFKA_HOME/export/server/kafka export PATH$PATH:$KAFKA…...

【服务器部署篇】Linux下Node.js的安装和配置

作者介绍:本人笔名姑苏老陈,从事JAVA开发工作十多年了,带过刚毕业的实习生,也带过技术团队。最近有个朋友的表弟,马上要大学毕业了,想从事JAVA开发工作,但不知道从何处入手。于是,产…...

StructBERT中文语义匹配实战:Kubernetes集群中StructBERT服务弹性伸缩配置

StructBERT中文语义匹配实战:Kubernetes集群中StructBERT服务弹性伸缩配置 在自然语言处理的实际应用中,语义相似度判断是一个高频且核心的需求。无论是智能客服中的问题匹配、内容平台上的文本查重,还是知识库里的同义句检索,都…...

Stable-Diffusion-v1-5-archive行业落地:教育课件配图、自媒体封面、独立游戏素材生成

Stable Diffusion v1.5 Archive:教育课件、自媒体封面与独立游戏素材的生成利器 1. 引言:一个经典模型,三个创意场景 如果你是一位教育工作者,是否曾为找不到合适的课件配图而烦恼?如果你是一名自媒体创作者…...

BetterNCM Installer完整指南:三步打造个性化网易云音乐工作站

BetterNCM Installer完整指南:三步打造个性化网易云音乐工作站 【免费下载链接】BetterNCM-Installer 一键安装 Better 系软件 项目地址: https://gitcode.com/gh_mirrors/be/BetterNCM-Installer 还在为网易云音乐的功能限制感到困扰吗?BetterNC…...

Intv_AI_MK11助力后端开发:构建基于大模型的智能API服务

Intv_AI_MK11助力后端开发:构建基于大模型的智能API服务 1. 智能API服务的时代机遇 最近跟几个做后端开发的朋友聊天,发现大家都在讨论同一个问题:如何把大模型能力快速集成到现有系统中。传统做法要么调用第三方API(贵且慢&…...

XPay项目结构深度解析:Maven多模块架构与支付系统最佳实践

XPay项目结构深度解析:Maven多模块架构与支付系统最佳实践 【免费下载链接】xpay XPay个人免签收款支付系统 完全免费 资金直接到达本人账号 支持 支付宝 微信 QQ 云闪付 无需备案 无需签约 无需挂机监控APP 无需插件 无需第三方支付SDK 无需营业执照身份证 只需收款…...

OpenClaw异常处理设计:Qwen3.5-9B图片任务失败自动恢复方案

OpenClaw异常处理设计:Qwen3.5-9B图片任务失败自动恢复方案 1. 为什么需要异常处理机制? 上周我尝试用OpenClawQwen3.5-9B实现证件照自动裁剪时,遇到了典型的"三连击"问题:网络波动导致图片上传中断、模型响应超时、输…...

汽车电子电器之整车控制器VCU功能解析与测试实践)

(一篇入门)汽车电子电器之整车控制器VCU功能解析与测试实践

1. 整车控制器VCU:新能源汽车的"大脑" 第一次拆解新能源汽车时,我盯着那个巴掌大的金属盒子看了半天——这就是传说中的VCU(整车控制器)。它就像乐高套装里的核心积木,所有其他模块都得听它指挥。记得有次测…...

OpenClaw跨平台实战:Mac与Windows双端配置Qwen3-4B

OpenClaw跨平台实战:Mac与Windows双端配置Qwen3-4B 1. 为什么选择OpenClawQwen3-4B组合 去年我在整理个人知识库时,发现手动处理上千份PDF和网页存档效率极低。尝试过各种自动化工具后,最终被OpenClaw的"AI直接操控电脑"理念吸引…...

零基础玩转OpenClaw:SecGPT-14B安全问答机器人搭建指南

零基础玩转OpenClaw:SecGPT-14B安全问答机器人搭建指南 1. 为什么选择OpenClawSecGPT-14B组合 去年我在处理公司内网安全审计时,发现很多基础安全问题反复出现。当时就想:如果能有个24小时在线的安全助手,随时解答团队疑问该多好…...

终极指南:如何为Evil Icons添加专属品牌图标

终极指南:如何为Evil Icons添加专属品牌图标 【免费下载链接】evil-icons Simple and clean SVG icon pack with the code to support Rails, Sprockets, Node.js, Gulp, Grunt and CDN 项目地址: https://gitcode.com/gh_mirrors/ev/evil-icons Evil Icons是…...