【FPGA】Verilog:时序电路设计 | 二进制计数器 | 计数器 | 分频器 | 时序约束

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载

示例:计数器与分频器

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

目录

Ⅰ. 前置知识

0x00 二进制计数器

0x01 利用IP核构造计数器

Ⅱ. Verilog实现

0x00 分频器

0x01 时序约束

Ⅰ. 前置知识

0x00 二进制计数器

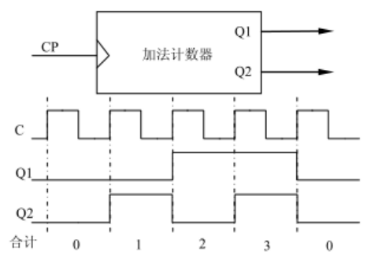

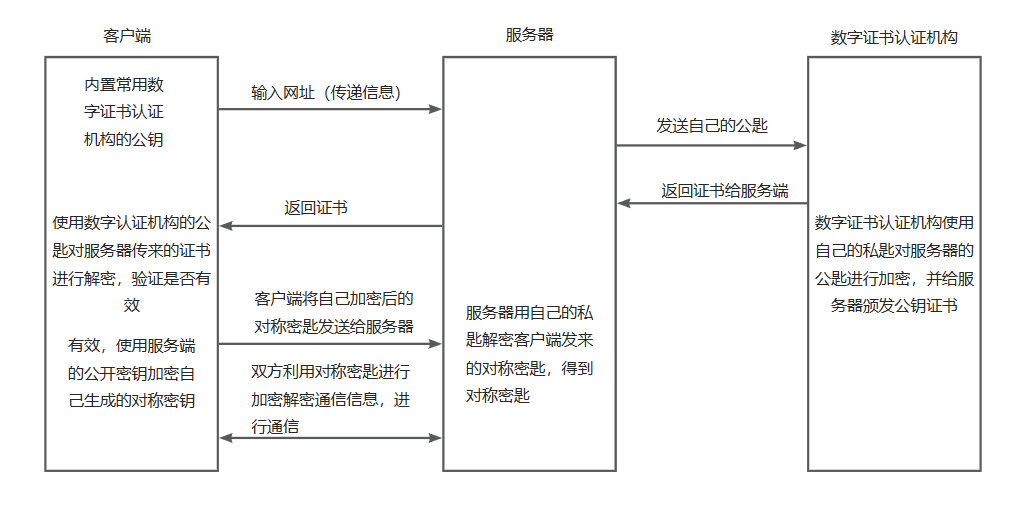

一个简单的二进制计数器通过二进制序列反复循环实现计数。以两位加法计数为例,每次时钟脉冲信号clk 为上升沿时,计数器会将计数值加1。所以计数值(由Q1Q0组成),依次是 00,01,10,11,00,11…,周而复始。在图中的波形图里,透露了这样几个信息:

[i] 一个两bit计数器,它所能计数的范围是 0~3(即22-1)。同理,n bits的计数器所能计数的范围是0~2n-1。

[ii] 如果将Q0、Q1作为单独信号线引出,由Q0、Q1得到的波形频率是时钟脉冲信号clk的1/2、1/4,亦即是将时钟脉冲信号的clk频率除2、除4。因此图示计数器又常被称为除4计数器。

[iii] 由上讨论推广可知,n bits计数器可获得的信号之多是频率除2n的结果。

参考如下源程序,试分析其分频系数:

1.

module addcounter(clk,Q) ;

input clk ;

output[1:0] Q ;

reg[1:0] Q ;

always @(posedge clk)begin

Q<=Q+1 ;

end

endmodule2.

module counter3(clr,clk,Q)

input wire clr; input wire clk;

output reg[2:0] Q;

input wire [2:0] D;

assign D[2] = ~Q[2] & Q[1] & Q[0] | Q[2] & ~Q[1] | Q[2] & ~Q[0]

assign D[1] = ~Q[1] & Q[0] | Q[1] & ~Q[0]

assign D[0] = ~Q[0]

always @ (posedge clk or posedge clr) beginif(clr==1) Q<=0;else Q <=D

end

endmodule通用型的二进制计数器一般具备更多功能,例如可以增/减计数、预置初值、同步清零、暂停等。74LS161就是一种常用的可预置4位二进制同步加法计数器。其功能表如下图表:

| 输入 | 输出 | |||||||||||

| P | T | CP | D0 | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 | ||

| 0 | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 0 | 0 | 0 | 0 |

| 1 | 0 | Ⅹ | Ⅹ | ↑ | D0 | D1 | D2 | D3 | D0 | D1 | D2 | D3 |

| 1 | 1 | 1 | 1 | ↑ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 计数 | |||

| 1 | 1 | 0 | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 保持 | |||

| 1 | 1 | Ⅹ | 0 | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 保持 | |||

0x01 利用IP核构造计数器

(1)根据上述74LS161的原理和参考代码,在vivado中设计计数电路:

module CNT161( input CR, input CP, input [3:0] D , input LD, input EP, input ET, output wire [3:0] Q);

wire [3:0] Din;

reg [3:0] Dout;

assign Din=D;

assign Q=Dout;

always@(posedge CP or negedge CR) begin

if (CR==0) Dout<=0;

else if (LD==0) Dout<=Din;

else if (LD==1 && EP==0 && ET==0) Dout<=Dout;

else if (LD==1 && EP==0 && ET==1) Dout<=Dout;

else if (LD==1 && EP==1 && ET==0) Dout<=Dout;

else if (LD==1 && EP==1 && ET==1) Dout<=Dout+1;

end

endmodule (2)实验板时钟为100MHZ,利用计数器构造分频输出1H:

module slowClock(clk, reset, clk_1Hz);

input clk, reset;

output clk_1Hz;

reg clk_1Hz = 1'b0; // provide initial condition for this register.

reg [27:0] counter;

// counter size calculation according to input and output frequencies

parameter sys_clk = 100000000; // 50 MHz system clock

parameter clk_out = 1; // 1 Hz clock output

parameter max = sys_clk / (2*clk_out); // max-counter size

always@(posedge reset or posedge clk) beginif (reset == 1'b1) beginclk_1Hz <= 0;counter <= 0;endelse begincounter <= counter + 1;if ( counter == max) begincounter <= 0;clk_1Hz <= ~clk_1Hz;endend

end

endmodule Ⅱ. Verilog实现

0x00 分频器

设计代码:

module slowClock(clk, reset,Q);input clk, reset;output [3:0] Q;reg [3:0] Q = 4'b0000;// provide initial condition for this register.reg [27:0] counter;// counter size calculation according to input and output frequencies

parameter sys_clk = 1;

parameter clk_out = 1;

parameter max = sys_clk / (2*clk_out); // max-counter sizealways@(posedge reset or posedge clk) beginif (reset == 1'b1) beginQ <= 0;counter <= 0;endelse begincounter <= counter + 1;if (counter == max) begincounter <= 0;Q<=Q+4'b0001;endendend

endmodule❗ 注:

parameter sys_clk = 1;

parameter clk_out = 1;

parameter max = sys_clk / (2*clk_out); // max-counter size

是根据EGO1板子的频率编写的,不同的板子可用设置不同的分频

仿真代码:

module sim_slowClock();reg clk ,reset;wire [3:0] Q;slowClock test(.clk(clk),.reset(reset),.Q(Q));initial clk=0;initial reset=1;always begin#10;clk=~clk;reset=0;end

endmodule

在Vivado中点击”RTL ANALYSIS->Open Elaborated Design”,可以查看综合得到的逻辑电路,如图所示:

仿真代码:

- 从图中可以看出上升沿有效且为异步电路;

- reset高电平有效,一开始为1,进行置数,置为0000;

- 从波形图可以看出为十六分频;

0x01 时序约束

由于需要时钟信号,所以还要进行时序约束。

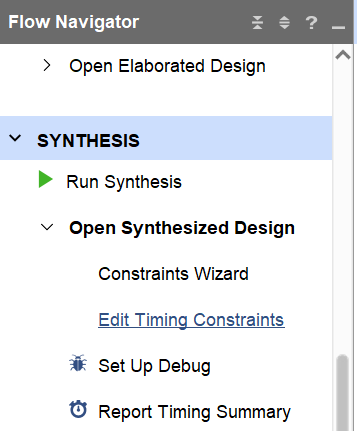

【a】选择在Flow Navigator 中选择Synthesis > Synthesized Design > Edit Timing Constraints。

【b】打开时序约束界面,开始进行时序约束。

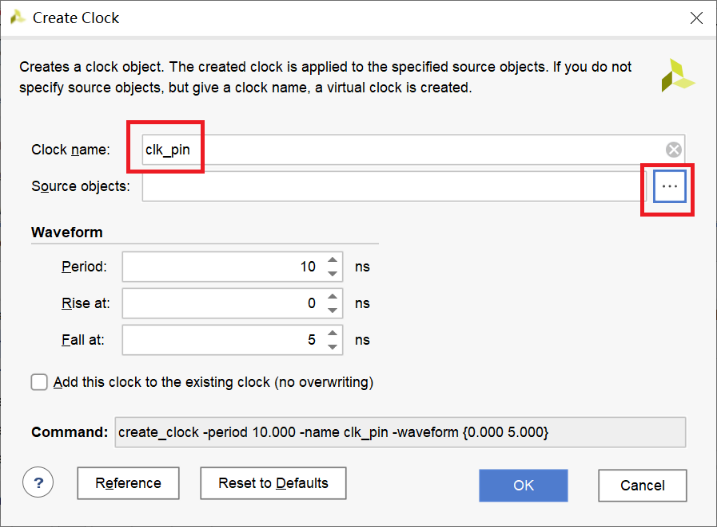

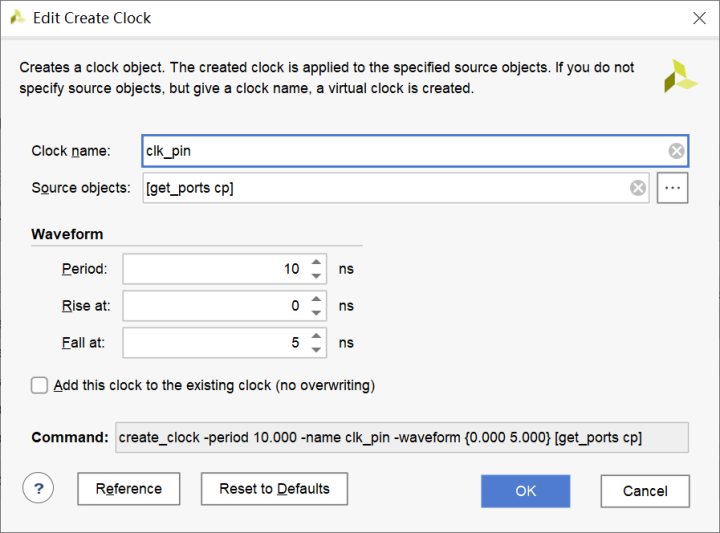

【c】双击左边Clock->Create Clock,进入Create Clock界面,在Clock name中输入clk_pin。在Source objects中选择右边的按钮。

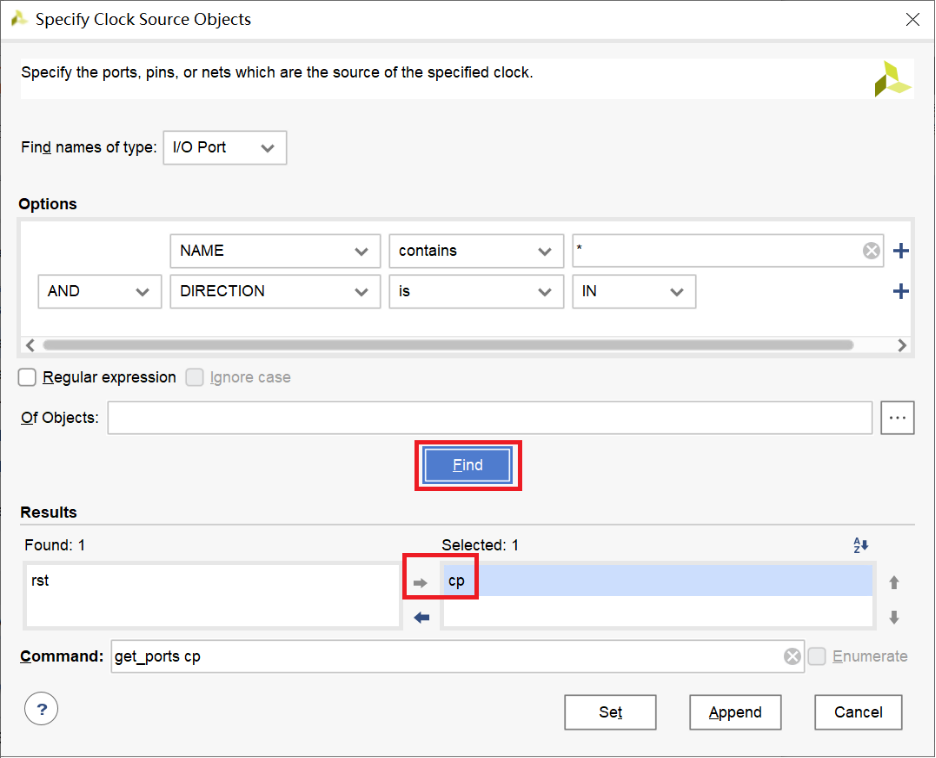

【d】在Specify Clock Source Object中Find names of type选择I/O Ports后点击Find,并将查找到的cp选中,如图:

完成选择后点击Set。对话框切换至如图:

点击ok完成时钟创建,结果参考下图:

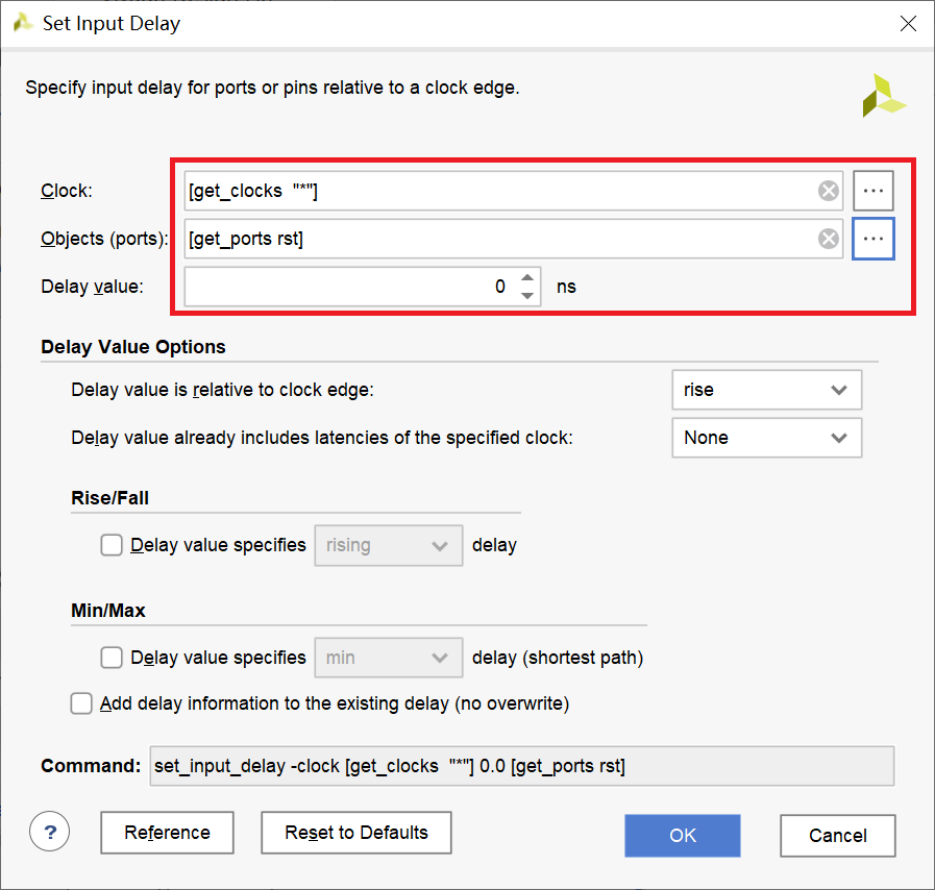

【e】设置Input Setup Delay ,双击左边Input->Input Setup Delay,如图:

进入Set Input Delay,按照下图配置:Clock选择clk_pin,Objects选择rst,Delay选择0 ns。完成设置后点击OK。

【f】接下来将设置Delay value specifies <min/max> delay,双击左边Input->Input Setup Delay。

将Clock选择为clk_pin、Objects选择rst、Delays value选择-0.5 ns、并选中Delay value specifies,

Delay设置成min。完成设置后点击ok。

【g】接下来设置Output Delay,双击左边Output->Set Output Delay。Clock选择clk_pin、Objects选择所有输出,Delay value设置为0ns。

【h】完成以上约束后可以在All Constraints看到如下约束结果。选择File->Save Constraints将设置的约束保存。

这时候如果打开Sources界面中的constraints,就可以看到XDC文件中增加了约束条件。

【i】在Flow Navigator中选择Synthesized Design ->Report Timing Summary。并将Options标签里将Path delay type设置成min_max。

再次综合后查看时序报告,如果在报告中看到有地方显示了红色,说明时序约束后,需求没有满足。然后在进行Implementation的时候,Vivado会自动优化布线路径,来满足用户设定的约束时间。如果在Implementation中还是显示无法满足,则需要分析电路进行进一步约束。

相关文章:

【FPGA】Verilog:时序电路设计 | 二进制计数器 | 计数器 | 分频器 | 时序约束

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载 示例:计数器与分频器 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片 配置方式:USB-JTAG/SPI Flash 高达100MHz 的内部时钟速度 存储器&#…...

国外SEO策略指南:确保你的网站排名第一!

如果你想在谷歌等搜索引擎中获得更高的排名并吸引更多的流量和潜在客户,那么你需要了解一些国外SEO策略。 下面是一些可以帮助你提高谷歌排名的关键策略。 网站结构和内容优化 谷歌的搜索算法会考虑网站的结构和内容。 因此,你需要优化网站结构&…...

Tik Tok新手秘籍,做好五点可轻松起号

新手做TikTok需要有一个具体的规划布局,如果没有深思熟虑就上手开始的话,很有可能会导致功亏一篑,甚至是浪费时间。因此,想要做好 TikTok,就必须从最基本的运营细节开始,一步一步来,下面为大家分…...

【Linux】网络入门

🎇Linux: 博客主页:一起去看日落吗分享博主的在Linux中学习到的知识和遇到的问题博主的能力有限,出现错误希望大家不吝赐教分享给大家一句我很喜欢的话: 看似不起波澜的日复一日,一定会在某一天让你看见坚持…...

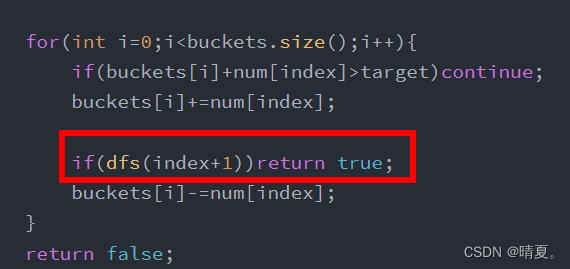

回溯法——力扣题型全解【更新中】

(本文源自网上教程的笔记) 回溯基础理论 回溯搜索法,它是一种搜索的方式。 回溯是递归的副产品,只要有递归就会有回溯。 所以以下讲解中,回溯函数也就是递归函数,指的都是一个函数。 回溯法的效率 虽然…...

【华为机试真题详解 Python实现】分奖金【2023 Q1 | 100分】

文章目录 前言题目描述输入描述输出描述示例 1题目解析参考代码前言 《华为机试真题详解》专栏含牛客网华为专栏、华为面经试题、华为OD机试真题。 如果您在准备华为的面试,期间有想了解的可以私信我,我会尽可能帮您解答,也可以给您一些建议! 本文解法非最优解(即非性能…...

netlink进行网卡重命名

#include <stdio.h> #include <stdlib.h> #include <string.h> #include <errno.h> #include <unistd.h> #include <sys/socket.h> #include <linux/if.h> #include <linux/netlink.h>#define MAX_PAYLOAD 1024 // 最大负载长…...

-1:针对COVID-19,使用聚类方法有效提取生物特性关联进而识别预防COVID-19的药物)

2023年春【数据分析与挖掘】文献精读(一)-1:针对COVID-19,使用聚类方法有效提取生物特性关联进而识别预防COVID-19的药物

分享给大家——动漫《画江湖之不良人》第四季片尾,主人公 李星云所说的一段话: 悠悠众生,因果循环,大道至简,世间若尽是不如意事, 越是执着,便越是苦,不如安下心来,看该看的风景,做好该做之事。 初行娆疆,所悟如此, 就像曾经有一位紫衣姑娘,第一次来中原时,一样…...

用法)

【Go自学第三节】Go的范围(Range)用法

Go 语言中 range 关键字用于 for 循环中迭代数组(array)、切片(slice)、通道(channel)或集合(map)的元素。在数组和切片中它返回元素的索引和索引对应的值,在集合中返回 key-value 对。 在讲Go语言的range之前,我们先回顾下Python中range的用法 for i …...

【备战面试】每日10道面试题打卡-Day6

本篇总结的是计算机网络知识相关的面试题,后续也会更新其他相关内容 文章目录1、HTTP 与 HTTPS 有哪些区别?2、HTTPS的加密过程是什么?3、GET与POST有什么区别?4、讲讲HTTP各个版本的区别?5、HTTP与FTP的区别ÿ…...

Stable Diffusion 个人推荐的各种模型及设置参数、扩展应用等合集(不断更新中)

一、说明 | 表示或者 表示 以上 二、模型 适用风景、房子、车子等漫画类风格 模型的VAE不要用模型附带的,好像就是naifu的官方vae,很老了,用 vae-ft-mse-840000-ema-pruned.ckpt 或者是 kl-f8-anime2.ckpt; 嵌入模型要下载作者…...

Salesforce 2023财年逆风增长,现金流达历史最高!

在过去的一年里,Salesforce一直是华尔街最关注的公司之一。3月1日,CRM领域的全球领导者Salesforce公布了截至2023年1月31日的第四季度和整个财年的业绩。 Salesforce主席兼首席执行官Marc Benioff表示: Salesforce全年实现了314亿美元的收入…...

2023年3月全国数据治理工程师认证DAMA-CDGA/CDGP考试怎么通过?

弘博创新是DAMA中国授权的数据治理人才培养基地,贴合市场需求定制教学体系,采用行业资深名师授课,理论与实践案例相结合,快速全面提升个人/企业数据治理专业知识与实践经验,通过考试还能获得数据专业领域证书。 DAMA认…...

【安卓软件】KMPlayer-一款完美的媒体播放器 可以播放所有格式的字幕和视频

KM PlayerKM Player是一款未编码的视频播放器,让您无需编码即可方便地播放各种格式的视频,并为您的新体验添加了字幕支持、视频播放速度和手势等功能。KMPlayer 拥有美观和直观的设计,让您可以更方便地管理和播放视频!功能高品质视…...

ClickHouse--分布式查询多副本的路由规则

前言在集群情况下,数据写入可以有写本地表和写分布式表2种方案,但是面向集群查询时,只能通过Distributed表引擎实现。本文主要介绍分布式查询多副本的路由规则。该配置项为:load_balancerandom/nearest_hostname/in_order/first_o…...

Linux 常用命令总结

本篇博客记录读研以来高频使用的 linux 系统下的命令合集 命令分类程序运行系统相关文件处理文件传输相关命令文件显示相关命令文件排列相关命令Anaconda 相关命令tmux 终端复用神器使用tips程序运行 自动保存日志,替代write命令: xxx | tee ./xxx.log…...

超分扩散模型 SR3 可以做图像去雨、去雾等恢复任务吗?

文章目录前言代码及原文链接主要的点如何进行图像恢复前言 关于扩散模型以及条件扩散模型的介绍,大家可以前往我的上一篇博客:扩散模型diffusion model用于图像恢复任务详细原理 (去雨,去雾等皆可),附实现代码。 SR3是利用扩散模…...

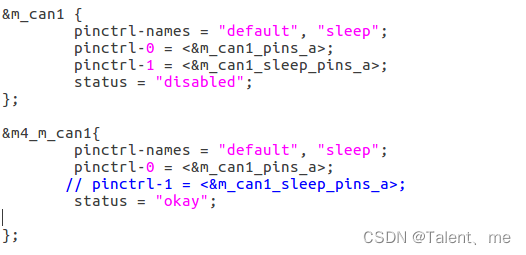

STM32Cube STM32MP157 M4端CAN通讯实战

1、环境 开发系列:STM32MP157 开发软件:STM32CubeIDE 1.4.0 例程目的:在M4端实现CAN通讯 2、目的 近日,有客户需要在STM32MP157中的M4端实现CAN通讯,我也是初次在M4端编写CAN通讯代码,上网研究了其他人写…...

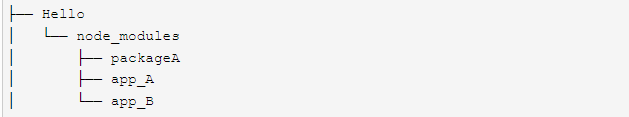

npm install报错unable to resolve dependency tree

一、问题背景npm install安装项目依赖时报错PS D:\test> npm install npm ERR! code ERESOLVE npm ERR! ERESOLVE unable to resolve dependency tree npm ERR! npm ERR! While resolving: vue-admin-template4.2.1 npm ERR! Found: webpack5.74.0 npm ERR! node_modules/we…...

力扣sql简单篇练习(二十六)

力扣sql简单篇练习(二十六) 1 每家商店的产品价格 1.1 题目内容 1.1.1 基本题目信息 1.1.2 示例输入输出 1.2 示例sql语句 # 多行变成多列,考虑用sum if分组 SELECT product_id,sum(IF(storestore1,price,null)) store1,sum(IF(storestore2,price,null)) store2, sum(IF(st…...

从零构建智能Line机器人:基于ChatGPT API的即时通讯AI助手开发指南

1. 项目概述:一个能帮你“翻译”一切的Line机器人 如果你经常使用Line,并且对ChatGPT这类AI助手的能力感到好奇,那么“ChatGPT-Line-Bot”这个项目,可能就是为你量身定做的。简单来说,它是一个架设在Line平台上的聊天…...

OBS Source Record插件深度解析:5个实战技巧实现多源独立录制

OBS Source Record插件深度解析:5个实战技巧实现多源独立录制 【免费下载链接】obs-source-record 项目地址: https://gitcode.com/gh_mirrors/ob/obs-source-record 你是否曾经在直播或视频制作中,想要单独录制某个摄像头画面、游戏窗口或浏览器…...

如何在PC上快速配置yuzu模拟器:完整游戏体验指南

如何在PC上快速配置yuzu模拟器:完整游戏体验指南 【免费下载链接】yuzu 任天堂 Switch 模拟器 项目地址: https://gitcode.com/GitHub_Trending/yu/yuzu 想在电脑上畅玩任天堂Switch游戏吗?yuzu模拟器是你的最佳选择!作为目前最成熟的…...

MCP Analytics Suite:用自然语言驱动AI数据分析,零代码生成专业报告

1. 项目概述:当AI助手遇上专业数据分析如果你和我一样,日常工作中需要处理大量的业务数据——可能是Shopify的订单报表、Stripe的支付流水,或者是一堆从各个渠道导出的CSV文件——那你一定体会过那种“数据在手,却无从下手”的焦虑…...

我让 AI 学会了“拆“App——Antigravity 逆向分析能力搭建手记

你能想象吗?对着 AI 说一句"帮我分析这个 APK",它就自己打开 IDA、拆解代码、Hook 运行时、提取密钥、还原源码……全程不用你碰一下鼠标。先说结论我给 AI 编程助手 Antigravity 装上了 4 把"瑞士军刀",让它从一个只会写…...

AI建站工具怎么选?一份让你不踩坑的选型标准与对比指南

AI建站工具怎么选?一份让你不踩坑的选型标准与对比指南市面上号称AI建站的工具层出不穷,有的只是给模板加了个AI抠图功能,有的则能真正从0生成代码。对于非技术背景的中小企业主或运营来说,选错工具不仅浪费钱,更浪费时…...

Claude API开发实战:从模型选型到工具调用,一站式资源与代码详解

1. 项目概述与核心价值最近在折腾AI应用开发的朋友,估计没少为Claude API的调用和管理头疼。官方文档虽然详尽,但当你需要快速查找某个特定端点、对比不同模型参数,或者只是想找个现成的代码片段时,那种在多个页面间跳转、反复搜索…...

Marko导入导出完全指南:掌握模块化组件的终极导入导出机制

Marko导入导出完全指南:掌握模块化组件的终极导入导出机制 【免费下载链接】marko A declarative, HTML-based language that makes building web apps fun 项目地址: https://gitcode.com/gh_mirrors/ma/marko Marko是一款声明式、基于HTML的语言࿰…...

Redux Thunk终极性能优化指南:从2秒到200毫秒的惊人提升

Redux Thunk终极性能优化指南:从2秒到200毫秒的惊人提升 【免费下载链接】redux-thunk Thunk middleware for Redux 项目地址: https://gitcode.com/gh_mirrors/re/redux-thunk Redux Thunk是Redux生态中最受欢迎和广泛使用的中间件,它为处理异步…...

Claude Code / Cursor 写的代码,你敢直接上线吗?我踩过一次坑,再也不敢

👉 这是一个或许对你有用的社群🐱 一对一交流/面试小册/简历优化/求职解惑,欢迎加入「芋道快速开发平台」知识星球。下面是星球提供的部分资料: 《项目实战(视频)》:从书中学,往事上…...