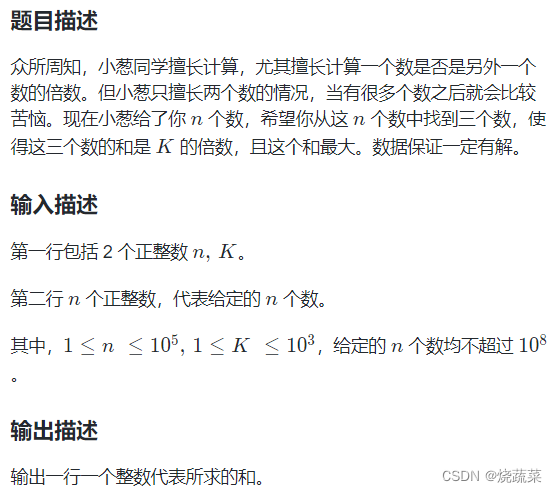

verilog specify语法

specify block用来描述从源点(source:input/inout port)到终点(destination:output/inout port)的路径延时(path delay),由specify开始,到endspecify结束,并且只能在模块内部声明,具有精确性(accuracy)和模块性(modularity)的特点。specify block可以用来执行以下三个任务:

一、描述横穿整个模块的各种路径及其延时。(module path delay)

二、脉冲过滤限制。(pulse filtering limit)

三、时序检查。(timing check)

specify block有一个专用的关键字specparam用来进行参数声明,用法和parameter一样,不同点是两者的作用域不同:specparam只能在specify block内部声明及使用,而parameter只能在specify block外部声明及使用。

第一个任务:模块路径延时(module path delay)

一条模块路径可以是一条简单的路径(simple path),或者是一条边沿敏感的路径(edge sensitive path),或者是一条状态依赖的路径(state dependent path)。

(1)simple path,可以由以下两种格式中的任意一种来声明:

1)、并行连接(patallel connection):source => destination

2)、全连接(full connection): source *> destination

例: (a, b => q, qn) = 1; 等价于:

(a => q) = 1; (b => qn) = 1;

而(a, b *> q, qn) = 1; 等价于:

(a => q) = 1; (b => q) = 1; (a => qn) = 1; (b => qn) = 1;

(2)edge sensitive path,是那些源点(source)使用边沿触发的路径,并使用边沿标示符指明触发条件(posedge/negedge),如果没有指明的话,那么就是任何变化都会触发终点(destination)的变化。

例1:(posedge clk => (out +: in)) = (1,2);

在clk的上升沿,从clk到out的模块路径,其上升延时是1,下降延时是2,从in到out的数据路径是同向传输,即out = in。

例2:(negedge clk => (out -: in)) = (1,2);

在clk的下降沿,从clk到out的模块路径,其上升延时是1,下降延时是2,从in到out的数据路径是反向传输,即out = ~in。

例3:(clk => (out : in)) = (1,2);

clk的任何变化,从clk到out的模块路径,其上升延时是1,下降延时是2,从in到out的数据路径的传输是不可预知的,同向或者反向或者不变。

Note:模块路径的极性(module path polarity):未知极性(unknown polarity,无),正极性(positive polarity,+),负极性(negative polarity,-)。

(3)state dependent path,是那些源点(source)以来指定条件状态的路径,使用if语句(不带else)。在条件=1 or X or Z的情况下,认为条件成立。如果有一条路经,存在多个条件同时成立的情况,那么使用延时最小值的那条限制。

例1: specify

if(a) (b => out) = (1,2);

if(~a) (b => out) = (2,3);

if(b) (a => out) = (1,2);

if(~b) (a => out) = (2,3);

endspecify

例2: specify

if(rst) (posedge clk => (q +: data)) = (1,2);

if(~rst) (posedge clk => (q +: data)) = (2,3);

endspecify

需要注意的是,所有输入状态都应该说明,否则没有说明的路径使用分布延时(distributed delay),如果也没有声明分布延时(distributed delay)的话,那么使用零延时(zero delay)。如果路径延时和分布延时同时声明的话,则选择最大的延时作为路径延时。另外,也可以使用ifnone语句,在其它所有条件都不满足的情况下,说明一个缺省的状态依赖路径延时。

例3: specify

(posedge clk => (q +: data)) = (1,2);

ifnone (clk => q) = (2,3);

endspecify

第二个任务,脉冲过滤限制(pulse filtering limit)

由于每条传播路径都具有一定的电容性和电阻性,电荷无法在一瞬间积累或消散,所以信号变化的物理特性是具有惯性的。为了更准确地描述这种能力,使用惯性延时(inertial delay),它可以抑制持续信号比传播延时短的输入信号的变化。

两个脉宽限制值:e-limit(error limit)和r-limit(rejection limit),并且要求e-limit >= r-limit,否则报错。当pulse width >= e-limit时,输出相应的逻辑值;当e-limit > pulse width >= r-limit时,输出X值;当r-limit > pulse width时,输出不发生变化。默认情况下,e-limit = r-limit = module transition delay,也可以使用以下3种控制方式中的任意一种改变路径脉冲限制值:

1、使用verilog提供的PATHPULSE$参数,有些仿真器还要求同时使能相应的选项:比如VCS,添加+pathpulse选项。

PATHPULSE$ = (<reject-limit>, <error-limit>);

PATHPULSE$<path_source>$<path_destination> = (<reject-limit>, <error-limit>);

例: specify

(en => q) = 12;

(data => q) = 10;

(clr, pre *> q) = 4;

specparam

PATHPULSE$ = 3, PATHPULSE$en$q = (2,9), PATHPULSE$clr$q = 1;

endspecify

en => q的路径:reject-limit = 2, error-limit =9;

clr => q和pre => q的路径:reject-limit = error-limit = 1;

data => q的路径:reject-limit = error-limit = 3;

2、使用仿真器专用的编译指导。

3、使用SDF文件反标,并且SDF文件中的延时信息具有最高的优先级。SDF文件格式将在后面介绍。

脉冲过滤限制的默认格式存在两个缺点:

1、X状态的持续时间比较短。

2、在上升延时和下降延时不相等的情况下,如果脉冲过窄,那么可能出现跟随边沿(trailing edge)先于或等于导引边沿(leading edge)的现象,这时就会淹没X状态。

第三个任务,时序检查(timing check)

描述设计要求的时序性能,所有的时序检查有一个参考事件(reference event)和一个数据事件(data event),它们通过一个布尔表达式相联接,还包括一个可选的notifier寄存器选项,这个寄存器用来打印错误信息或者传播X状态。

这里把时序检查分成两组来说明:

第一组,检查时序窗口的稳定性,包括:setup、hold、recovery和removal。

setup:$setup (data_event, reference_event, limit, notifier);

当reference_event time - limit < data_event time < reference_event time时,就会报告setup time violations。

hold: $hold (reference_event, data_event, limit, notifier);

当reference_event time < data_event time < reference_event time + limit时,就会报告hold time violations。

setup/hold:$setuphold (reference_event, data_event, setup_limit, hold_limit, notifier);

$setuphold是$setup和$hold两者的联合。例如:

$setuphold (posedge clk, negedge d, 2, 1, notifier); 等于

$setup (negedge d, posedge clk, 2, notifier); 和 $hold (posedge clk, negedge d, 1, notifier);

数据事件常常是数据信号,而参考事件常常是时钟信号。

recovery:$recovery (reference_event, data_event, limit, notifier);

当data_event time - limit < reference_event time < data_event time时,就会报告recovery time violations。

removal: $removal (reference_event, data_event, limit, notifier);

当data_event time < reference_event time < data_event time + limit时,就会报告removal time violations。

recovery/removal:$recrem (reference_event, data_event, recovery_limit, removal_limit, notifier);

$recrem是$recovery和$removal两者的联合。

$recrem (posedge clr, posedge clk, 2, 3, notifier); 等于

$recovery (posedge clr, posedge clk, 2, notifier); 和 $removal (posedge clr, posedge clk, 3, notifier);

数据事件常常是时钟信号,而参考事件常常是控制信号。

$setuphold和$recrem可以接受负值,同时需要激活仿真器的负值时序检查选项(比如VCS:+neg_tchk),同时还有一个限制:

setup_limit + hold_limit > 仿真精度(simulation unit of precision),

recovery_limit + removal_limit > 仿真精度(simulation unit of precision),

否则仿真器会把负值当成0处理。

第二组,检查时钟和控制信号在指定事件之间的时间间隔,包括:skew、width、period和nochange。

skew:$skew (reference_event, data_event, limit, notifier); 限制最大偏斜

$skew (posedge clk1, posedge clk2, 1, notifier);

当data_event time - reference_event > limit,则会报告skew time violations。

$skew是基于事件(event-based)的,如果监测到一个reference_event,那么就开始评估脉宽,只要监测到一个data_event,就会生成相应的报告,直到监测到下一个reference_event,才重新开始新的监测。如果在监测到一个data_event之前,又监测到一个reference_event,那么就放弃本次评估,重新开始新的评估。

width:$width (controlled_reference_event, limit, threshold, notifier); 限制最小脉宽

$width (posedge in, 2, notifier);

这里data_event是隐含的,它等于reference_event的相反边沿,当width < limit时,就会报告width time violations。

period:$period (controlled_reference_event, limit, notifier); 限制最小周期

$period (negedge clk, 10, notifier);

这里data_event是隐含的,它等于reference_event的相同边沿,当period < limit时,就会报告period time violations。

nochange:$nochange (reference_event, data_event, start_edge_offset, end_edge_offset, notifier);

当leading reference event time - start_edge_offset < data_event < trailing reference event time + end_edge_offset时,就会报告nochange time violations。例如:

$nochange (posedge clk, data, 0 , 0);

当在clk高电平期间,data发生任何变化,就会报告nochange time violations。

有时候,路径上的时序检查是在一定条件成立的前提下进行的,这就需要引入条件操作符:&&&。需要注意的是,当存在两个及以上的条件时,要求这些条件首先在specify块外部经过适当的组合逻辑产生一个新的控制信号,然后再引入到specify块内部使用。

例如:

and u1 (clr_and_set, clr, set);

specify

$setup (negedge data, posedge clk &&& clr_and_set, 3, notifier);

endspecify

相关文章:

verilog specify语法

specify block用来描述从源点(source:input/inout port)到终点(destination:output/inout port)的路径延时(path delay),由specify开始,到endspecify结束&…...

CMake编译学习笔记

CMake学习笔记CMake编译概述CMake学习资源CMake编译项目架构cmake指令CMakeList基础准则CMakeList编写项目构建cmake_minimum_required() 和 project()set()find_package()add_executable()aux_source_directory()连接库文件include_directories()和target_include_directories…...

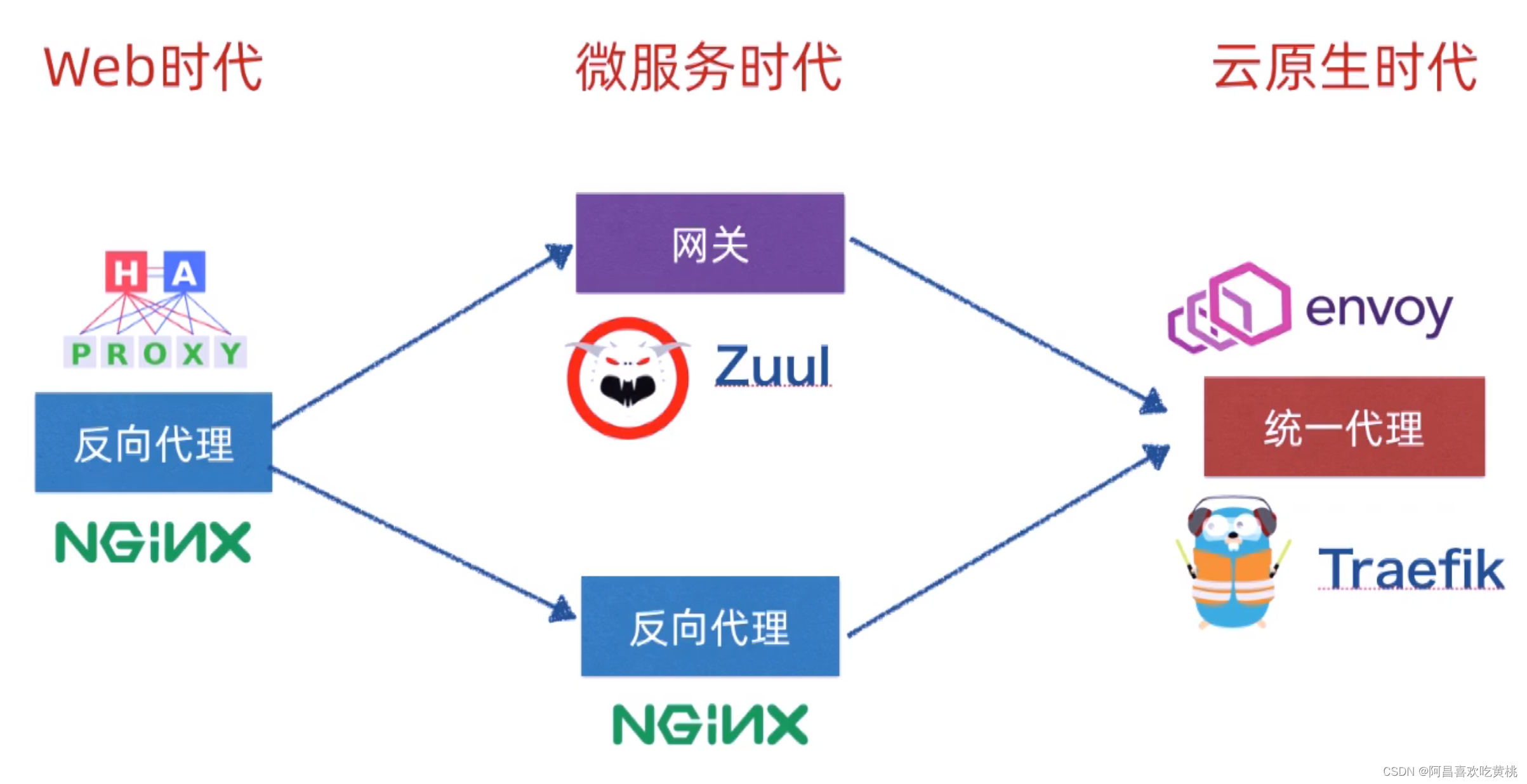

Day913.反向代理和网关是什么关系 -SpringBoot与K8s云原生微服务实践

反向代理和网关是什么关系 Hi,我是阿昌,今天学习记录的是关于反向代理和网关是什么关系的内容。 一、反向代理 反向代理 是一种网络技术,用于将客户端的请求转发到一个或多个服务器上,并将响应返回给客户端。与正向代理不同&am…...

IT行业就业趋势显示:二季度平均月薪超8千

我国的IT互联网行业在近些年来规模迅速扩大,技能和技术水平也明显提升,目前IT互联网行业已经成为社会发展中新型产业的重要组成部分,行业的人才队伍也在不断的发展壮大,选择进入入互联网行业工作的人也越来越多。 根据58同城前段…...

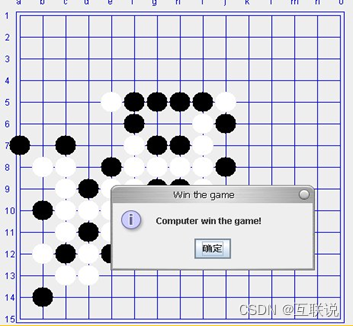

【毕业设计】基于Java的五子棋游戏的设计(源代码+论文)

简介 五子棋作为一个棋类竞技运动,在民间十分流行,为了熟悉五子棋规则及技巧,以及研究简单的人工智能,决定用Java开发五子棋游戏。主要完成了人机对战和玩家之间联网对战2个功能。网络连接部分为Socket编程应用,客户端…...

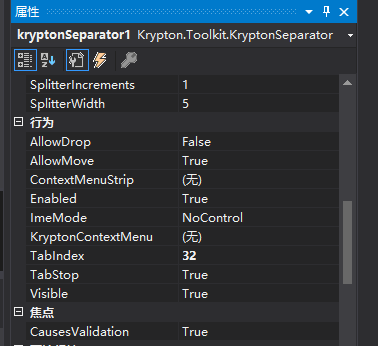

C#:Krypton控件使用方法详解(第十四讲) ——kryptonSeparator

今天介绍的Krypton控件中的kryptonSeparator。下面介绍控件的外观属性如下图所示:Cursor属性:表示鼠标移动过该控件的时候,鼠标显示的形状。属性值如下图所示:DrawMoveIndicator属性:表示确定移动分隔符时是否绘制移动…...

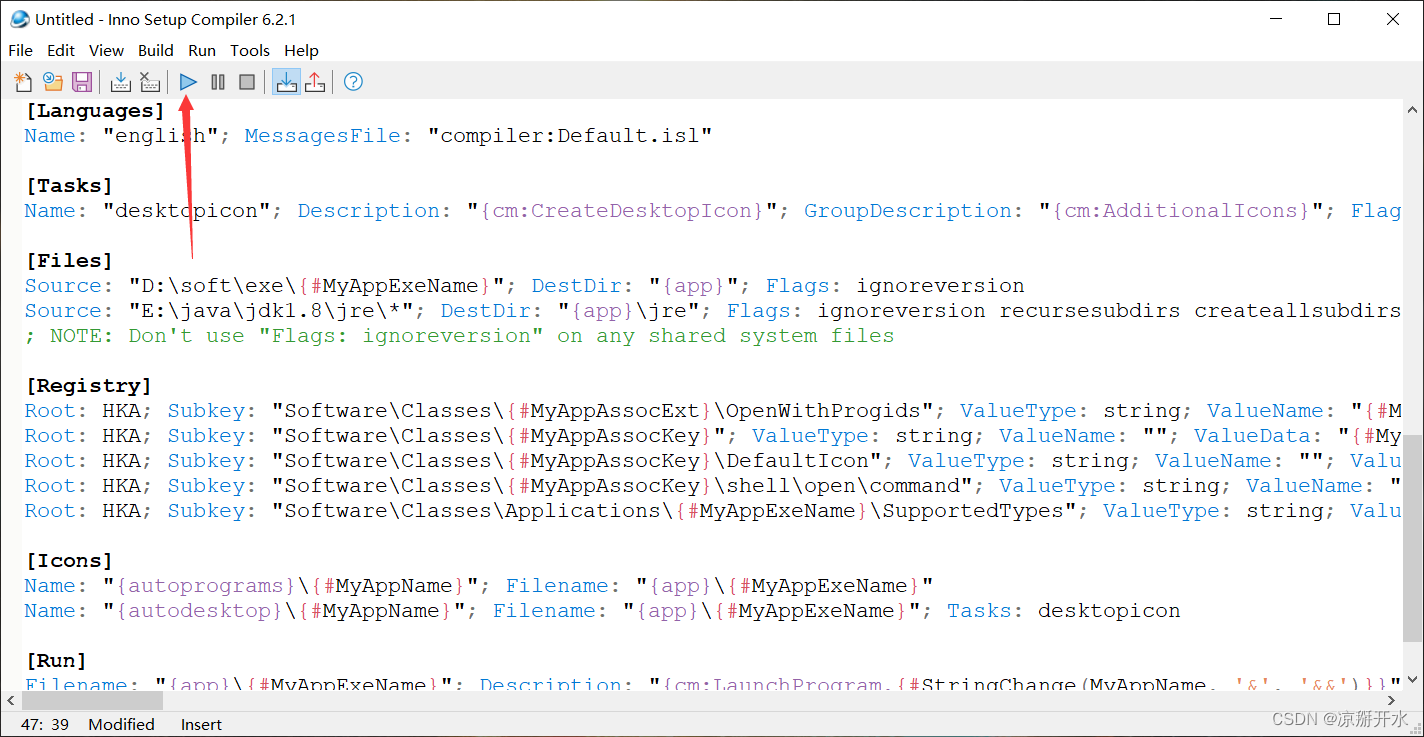

Java的jar包打包成exe应用

将springboot项目使用maven打出的jar包,打成windows平台下exe应用程序包(自带jre环境)。 工具:1、exe4j 2、Inno Setup 工具放到网盘,链接:https://pan.baidu.com/s/1ZHX8P7u-7GBxaC6uaIC8Ag 提取码&#x…...

Latex学习笔记

Latex 学习笔记 快速入门 编译软件: TeX Live TexStudio, Ctex, 线上: Overleaf第一个示例代码: \documentclass{article} % 设置文档使用的文档类 % 导言区 \title{my first Latex document} \author{Jclian91} \date{\today} \begin{document} % 正文区\maket…...

)

【c++复习】C++的基础知识(常用关键字、缺省参数、函数重载、引用)

C基础写在开头C基础常用关键字using namespace流插入和流提取操作符内联函数(inline)宏auto关键字 (c11nullptr (c11缺省参数函数重载引用写在开头 C基础部分我想介绍如下几个关键点: 常见关键字命名空间的定义和使用缺省参数函数重载引用、指针和引用的区别内联函…...

Docker入门建议收藏 第二部分

二、Docker 容器技术与虚拟机的区别 Docker 到底是个什么东西呢?我们在理解 Docker 之前,首先得先区分清楚两个概念,容器和虚拟机。 虚拟机 虚拟机(Virtual Machine)指通过软件模拟的具有完整硬件系统功能的、运行在…...

蓝桥杯三月刷题 第7天

文章目录💥前言😉解题报告💥三角回文数🤔一、思路:😎二、代码:💥数数🤔一、思路:😎二、代码:💥数组切分🤔一、思路:😎二、…...

面试官问百万数据excel导出功能如何实现?

文章目录 背景实现1.异步处理1.1 使用job1.2 使用mq2.使用easyexcel4.多个sheet5.计算limit的起始位置6.文件上传到OSS7.通过WebSocket推送通知8.总条数可配置9.order by商品编号总结背景 用户在UI界面上点击全部导出按钮,就能导出所有商品数据。 咋一看,这个需求挺简单的。…...

理解HTTPS及配置

HTTP的弊端及HTTPS的由来 众所周知HTTP协议是以TCP协议为基石诞生的一个用于传输Web内容的一个网络协议,在“网络分层模型”中属于“应用层协议”的一种.那么在这里我们并不研究该协议标准本身,而是从安全角度去探究使用该协议传输数据本身存在的安全问题:(1)、通信使用明文(不…...

IP-guard浏览器上传下载智能加解密,让管理更省心省力

现在员工日常工作中经常会通过浏览器访问公司的业务系统(OA、JIRA等),或者访问其他外部系统,访问下载服务器的文档变得更便捷,工作地点也不再局限于办公室中。为确保应用系统机密安全且又不影响员工的正常工作…...

leetcode day22 位运算

位运算咋这么老难 剑指 Offer 56 - I. 数组中数字出现的次数 借评论区大佬答案:nums [1,2,10,4,1,4,3,3] a^a0a^0aa^b^ca^c^ba&(-a)最低位为1的二进制(从又到左)所有的异或结果得到sum2^108flag-8&88可分为两组,一组为与…...

java中如何判断map是否为空

java中判断map是否为空的方法是:利用isEmpty()函数来判断。函数介绍:isEmpty()是Java中用于判断某种容器是否有元素的系统库函数。如用来判断ArrayList,HashSet,HashMap是否有元素等。在Java中,可以用isEmpty();判断一…...

C语言数据结构:链表的增删改查及动态创建

目录 一,链表与数组 ① 定义区别 ② 实现区别 二,链表遍历和计算链表中节点数量 ① 链表遍历 ② 计算节点数量 三,查找链表节点 四,增加节点到链表中 ① 在节点后方插入 ② 在节点前方插入 ● 在头节点前方插入 ● 在…...

「Python 基础」I/O 编程、正则表达式

文章目录1. I/O 编程文件读写StringIO 和 BytesIO操作文件和目录序列化2. 正则表达式进阶re 模块1. I/O 编程 I/O指Input/Output; Input Stream 从外面(磁盘、网络)流进内存; Output Stream 从内存流到外面; 同步 …...

java 把pdf图片文档和文章文档转成文字的方法

java 提供了一些库和工具可以用来把 PDF 文档和图片文档转成文本。 Apache PDFBox:这是一个开源的 PDF 库,可以用来提取 PDF 文件中的文本内容。 iText:这是一个用于创建和处理 PDF 文件的库,可以用来提取 PDF 文件中的文本内容。…...

JavaScript 中的全部对象

宿主对象(host Objects):由 JavaScript 宿主环境提供的对象,它们的行为完全由宿主环境决定。 【 浏览器环境宿主,全局对象window,window 上又有很多属性,如 document。 全局对象 window 上的属…...

Gemini 辅助做创意写作:故事大纲、角色设定、世界观构建的 AI 协作

很多作者在创作卡壳时,其实不是“没有灵感”,而是缺一套可迭代的设计流程:大纲松散、角色像说明书、世界观看似宏大却前后不一致。2026 年的写作新趋势,是把 Gemini 当作“创作协作伙伴”而不是“代写引擎”,让它参与结…...

从‘幂的末尾’到RSA加密:一个模运算技巧如何贯穿编程竞赛与网络安全?

从竞赛编程到网络安全:模运算的双面人生 第一次在OpenJudge上遇到"幂的末尾"这道题时,我盯着屏幕上的数字发愣——计算a^b的最后三位数,这不就是求a^b模1000的结果吗?当时的我并不知道,这个看似简单的数学技…...

分布式缓存策略:提升应用性能和可扩展性

分布式缓存策略:提升应用性能和可扩展性 一、分布式缓存概述 1.1 分布式缓存的定义 分布式缓存是一种将数据存储在多个节点上的缓存系统,它通过在内存中存储常用数据,减少对后端数据库的访问,从而提高应用性能和可扩展性。 1.…...

开关电源传导共模噪声抑制:Y电容原理、安规限制与EMI滤波器设计

1. 项目概述:理解隔离式开关电源中的传导共模噪声在开发离线式开关电源,比如我们常见的手机充电器、笔记本电脑适配器或者工业电源模块时,工程师们常常会遇到一个既棘手又必须解决的难题:传导电磁干扰(Conducted EMI&a…...

SAR ADC性能优化:电压基准设计与THD改善方案

1. 电压基准对SAR ADC性能的影响机制在精密数据采集系统设计中,工程师们常常花费大量精力选择高性能的模数转换器(ADC)和优化输入驱动电路,却容易忽视一个关键因素——电压基准的质量及其驱动能力。对于逐次逼近型(SAR)ADC而言,基准电压的稳定…...

ARMv8 A64指令集内存访问优化与LDRH/LDRSB指令详解

1. A64指令集与内存访问基础在ARMv8架构中,A64指令集作为64位执行状态的核心指令系统,其内存访问指令的设计直接影响处理器性能。与32位的A32指令集相比,A64在寄存器数量、地址空间和指令编码等方面都有显著改进。1.1 ARMv8内存访问特点ARM架…...

BaiduPCS-Go深度解析:从原理到实践的性能调优进阶指南

BaiduPCS-Go深度解析:从原理到实践的性能调优进阶指南 【免费下载链接】BaiduPCS-Go iikira/BaiduPCS-Go原版基础上集成了分享链接/秒传链接转存功能 项目地址: https://gitcode.com/GitHub_Trending/ba/BaiduPCS-Go BaiduPCS-Go作为一款功能强大的命令行百度…...

动手写一个 JVM 调优学习项目:6 个真实场景带你掌握性能优化

动手写一个 JVM 调优学习项目:6 个真实场景带你掌握性能优化 项目地址: https://gitee.com/jiucenglou/jvm-tuning-lab 技术栈: Java 8 Maven 适合人群: Java 开发者、性能调优初学者、面试准备者 🤔 为什么写这个项目? 在实际开发和面试中…...

)

K8s原生ML编排进入“编译期优化”时代(SITS 2026首次披露:eBPF驱动的模型感知调度器Alpha版已交付头部5家云厂商)

更多请点击: https://intelliparadigm.com 第一章:AI原生Kubernetes编排:SITS 2026 K8s for ML工作负载 SITS 2026 引入了专为机器学习工作负载深度优化的 AI-native Kubernetes 编排层,突破传统 K8s 在资源弹性、异构设备调度与…...

SteamAutoCrack技术深度解析:架构设计与实现原理揭秘

SteamAutoCrack技术深度解析:架构设计与实现原理揭秘 【免费下载链接】Steam-auto-crack Steam Game Automatic Cracker 项目地址: https://gitcode.com/gh_mirrors/st/Steam-auto-crack SteamAutoCrack是一款基于.NET 10.0框架开发的Steam游戏自动破解工具&…...