SpinalHDL之VHDL 和 Verilog 生成

本文作为SpinalHDL学习笔记第十六篇,记录使用SpinalHDL代码生成Verilog/VHDL代码的方法。

SpinalHDL学习笔记总纲链接如下:

SpinalHDL 学习笔记_spinalhdl blackbox-CSDN博客

目录:

1.从 SpinalHDL 组件生成 VHDL 和 Verilog

2.生成的 VHDL 和 Verilog

3.VHDL 和 Verilog 属性

1.从 SpinalHDL 组件生成 VHDL 和 Verilog

要 从 SpinalHDL 组 件 生 成 VHDL, 只 需 在 Scala main 函 数 中 调 用 SpinalVhdl(new

YourComponent) 即可。

生成 Verilog 完全相同,但用 SpinalVerilog 代替 SpinalVHDL。

import spinal.core._

// A simple component definition.

class MyTopLevel extends Component {

// Define some input/output signals. Bundle like a VHDL record or a Verilog␣

,→struct.

val io = new Bundle {

val a = in Bool()

val b = in Bool()

val c = out Bool()

}

// Define some asynchronous logic.

io.c := io.a & io.b

}

// This is the main function that generates the VHDL and the Verilog corresponding␣

,→to MyTopLevel.

object MyMain {

def main(args: Array[String]) {

SpinalVhdl(new MyTopLevel)

SpinalVerilog(new MyTopLevel)

}

}

Note:SpinalVhdl 和 SpinalVerilog 可能需要创建组件类的多个实例,因此第一个参数不是Component 引用,而是返回新组件的函数。

2.生成的 VHDL 和 Verilog

如何将 SpinalHDL RTL 描述转换为 VHDL 和 Verilog 非常重要:

• Scala 中变量的名称将保留在 VHDL 和 Verilog 中。

• Scala 中的 Component 组件层次结构会保留在 VHDL 和 Verilog 中。

• Scala 中的 when 语句会生成为 VHDL 和 Verilog 中的 if 语句。

• Scala 中的 switch 语句在所有标准情况下都生成为 VHDL 和 Verilog 中的 case 语句。

组织:

当使用 VHDL 生成器时,所有模块都会生成到一个文件中,其中包含三个部分:

1. 包含所有 Enum 定义的包

2. 包含架构中所有元素使用函数的包

3. 您的设计所需的所有组件

当使用 Verilog 生成时,所有模块都会生成到一个文件中,其中包含两个部分:

1. 使用的所有枚举定义

2. 您的设计需要的所有模块

组合逻辑

Scala:

class TopLevel extends Component {

val io = new Bundle {

val cond = in Bool()

val value = in UInt(4 bits)

val withoutProcess = out UInt(4 bits)

val withProcess = out UInt(4 bits)

}

io.withoutProcess := io.value

io.withProcess := 0

when(io.cond) {

switch(io.value) {

is(U"0000") {

io.withProcess := 8

}

is(U"0001") {

io.withProcess := 9

}

default {

io.withProcess := io.value+1

}

}

}

}VHDL:

entity TopLevel is

port(

io_cond : in std_logic;

io_value : in unsigned(3 downto 0);

io_withoutProcess : out unsigned(3 downto 0);

io_withProcess : out unsigned(3 downto 0)

);

end TopLevel;

architecture arch of TopLevel is

begin

io_withoutProcess <= io_value;

process(io_cond,io_value)

begin

io_withProcess <= pkg_unsigned("0000");

if io_cond = '1' then

case io_value is

when pkg_unsigned("0000") =>

io_withProcess <= pkg_unsigned("1000");

when pkg_unsigned("0001") =>

io_withProcess <= pkg_unsigned("1001");

when others =>

io_withProcess <= (io_value + pkg_unsigned("0001"));

end case;

end if;

end process;

end arch;时序逻辑

Scala:

class TopLevel extends Component {

val io = new Bundle {

val cond = in Bool()

val value = in UInt (4 bits)

val resultA = out UInt(4 bits)

val resultB = out UInt(4 bits)

}

val regWithReset = Reg(UInt(4 bits)) init(0)

val regWithoutReset = Reg(UInt(4 bits))

regWithReset := io.value

regWithoutReset := 0

when(io.cond) {

regWithoutReset := io.value

}

io.resultA := regWithReset

io.resultB := regWithoutReset

}VHDL:

entity TopLevel is

port(

io_cond : in std_logic;

io_value : in unsigned(3 downto 0);

io_resultA : out unsigned(3 downto 0);

io_resultB : out unsigned(3 downto 0);

clk : in std_logic;

reset : in std_logic

);

end TopLevel;

architecture arch of TopLevel is

signal regWithReset : unsigned(3 downto 0);

signal regWithoutReset : unsigned(3 downto 0);

begin

io_resultA <= regWithReset;

io_resultB <= regWithoutReset;

process(clk,reset)

begin

if reset = '1' then

regWithReset <= pkg_unsigned("0000");

elsif rising_edge(clk) then

regWithReset <= io_value;

end if;

end process;

process(clk)

begin

if rising_edge(clk) then

regWithoutReset <= pkg_unsigned("0000");

if io_cond = '1' then

regWithoutReset <= io_value;

end if;

end if;

end process;

end arch;3.VHDL 和 Verilog 属性

在某些情况下,为设计中的某些信号提供属性以修改它们的综合方式很有用。

为此,可以对设计中的任何信号或存储器调用以下函数:

| 语法 | 描述 |

|---|---|

| addAttribute(name) | 添加一个名为 name 的布尔属性,并将给定值设置为 true |

| addAttribute(name, | 添加一个字符串属性,并将给定的 name 设置为 value |

val pcPlus4 = pc + 4

pcPlus4.addAttribute("keep")用 VHDL 生成声明:

attribute keep : boolean;

signal pcPlus4 : unsigned(31 downto 0);

attribute keep of pcPlus4: signal is true;用 Verilog 生成声明:

(* keep *) wire [31:0] pcPlus4;相关文章:

SpinalHDL之VHDL 和 Verilog 生成

本文作为SpinalHDL学习笔记第十六篇,记录使用SpinalHDL代码生成Verilog/VHDL代码的方法。 SpinalHDL学习笔记总纲链接如下: SpinalHDL 学习笔记_spinalhdl blackbox-CSDN博客 目录: 1.从 SpinalHDL 组件生成 VHDL 和 Verilog 2.生成的 VHD…...

c语言中的字符串函数

strstr函数 函数介绍 strstr 用于在一个字符串中查找另一个字符串的首次出现。 我们来看这个函数的参数名字:haysytack(干草堆)needle(针),这个其实就是外国的一句谚语:在干草堆中找一根针,就…...

[AI 大模型] 百度 文心一言

文章目录 [AI 大模型] 百度 文心一言简介模型架构发展新技术和优势API 代码示例 [AI 大模型] 百度 文心一言 [外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-0DwAIh0T-1720667576892)(https://i-blog.csdnimg.cn/direct/283919e5d78b4951ba1ade5dcfc…...

机器学习开源分子生成系列(2)-基于三维形状和静电相似性的DeepFMPO v3D安装及使用

前言 本文是基于 3D 的分子生成方法DeepFMPO v3D的介绍及安装使用。 一、DeepFMPO v3D是什么? github代码介绍文章 在药物发现中,如何寻找具新颖性和结构多样性的候选分子是颇受药物设计科学家关注的问题。通过虚拟筛选的化学空间搜索往往会受限于筛选…...

机器学习-16-分布式梯度提升库XGBoost的应用

参考XGBoost库 1 XGBoost分布式梯度提升库 XGBoost,全称为eXtreme Gradient Boosting,是一个优化的分布式梯度提升库,旨在高效、灵活且便携。它在Gradient Boosting框架下实现了机器学习算法,并广泛用于分类、回归和排序任务。XGBoost之所以受到广泛欢迎,主要归功于它的…...

视觉/AIGC面经->多模态

1.ocr检测如何做?qwen的文本检测是否合理? paligemma: <loc0110><loc0124><loc0224><loc0389> plate ; <loc0244><loc0130><loc0281><loc0430> plate ; <loc0364><loc0820><loc0403><loc0951> pl…...

<数据集>钢板缺陷检测数据集<目标检测>

数据集格式:VOCYOLO格式 图片数量:1986张 标注数量(xml文件个数):1986 标注数量(txt文件个数):1986 标注类别数:7 标注类别名称:[crescent gap, silk spot, water spot, weld line, oil spot, punchin…...

EdgeOne安全能力开箱测评挑战赛

活动地址:EdgeOne安全能力开箱测评挑战赛-腾讯云开发者社区-腾讯云 随着网络攻击日益频繁,企业网站面临着数据泄露、DDoS攻击、CC攻击等多种安全威胁。如何有效保护企业网站安全,成为企业IT部门的重要任务。腾讯云EdgeOne作为一款集成了CDN和…...

神经网络识别数字图像案例

学习资料:从零设计并训练一个神经网络,你就能真正理解它了_哔哩哔哩_bilibili 这个视频讲得相当清楚。本文是学习笔记,不是原创,图都是从视频上截图的。 1. 神经网络 2. 案例说明 具体来说,设计一个三层的神经网络。…...

c++包管理器

conan conan search,查看网络库 conan profile detect,生成缓存信息conan new cmake_exe/cmake_lib,创建cmakelists.txtconan install .,执行Conanfile.txt中的配置,生成相关的bat文件 项目中配置Conanfile.txt(或者…...

监控易V7.6.6.15升级详解7,日志分析更高效

随着企业IT系统的日益复杂,日志管理成为了保障系统稳定运行、快速定位问题的重要工具。为了满足广大用户对日志管理功能的更高需求,监控易系统近日完成了重要版本升级,对日志管理功能进行了全面优化和新增。 一、Syslog日志与SnmpTrap日志统…...

HTML表格、表单标签

目录 一、表格 (1)关于表格中标签说明 (2)关于表格中属性说明 (3)简单操作演示 (4)表格小结 二、表单 (1)简单操作演示 (2)注…...

(Windows环境)FFMPEG编译,包含编译x264以及x265

本文使用 MSYS2 来编译 ffmpeg 一、安装MSYS2 MSYS2 是 Windows 下的一组编译套件,它可以在 Windows 系统中模拟 Linux 下的编译环境,如使用 shell 运行命令、使用 pacman 安装软件包、使用 gcc (MinGW) 编译代码等。 MSYS2 的安装也非常省心&#x…...

notepad++中文出现异体汉字,怎么改正

notepad显示异体字,如何恢复? 比如 “门” 和 “直接” 的"直"字,显示成了 方法 修改字体, 菜单栏选择 Settings(设置),Style Configurator…(语言格式设置…)…...

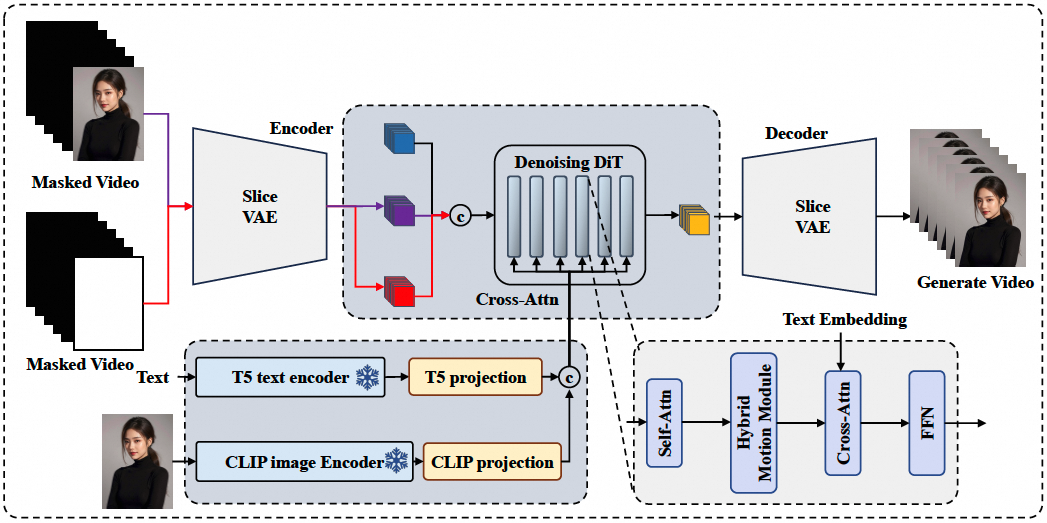

EasyAnimate-v3版本支持I2V及超长视频生成

阿里云人工智能平台(PAI)自研开源的视频生成项目EasyAnimate正式发布v3版本: 支持 图片(可配合文字) 生成视频 支持 上传两张图片作为起止画面 生成视频 最大支持720p(960*960分辨率) 144帧视…...

最新PHP自助商城源码,彩虹商城源码

演示效果图 后台效果图 运行环境: Nginx 1.22.1 Mysql5.7 PHP7.4 直接访问域名即可安装 彩虹自助下单系统二次开发 拥有供货商系统 多余模板删除 保留一套商城,两套发卡 源码无后门隐患 已知存在的BUG修复 彩虹商城源码:下载 密码:chsc 免责声明&…...

Vue2打包部署后动态修改后端接口地址的解决方法

文章目录 前言一、背景二、解决方法1.在public文件夹下创建config文件夹,并创建config.js文件2.编写config.js内容3.在index.html中加载config.js4.在封装axios工具类的js中修改配置 总结 前言 本篇文章将介绍使用Vue2开发前后端分离项目时,前端打包部署…...

【后端开发实习】用MongoDB实现仓库管理的出库入库实战

用MongoDB实现仓库管理的出库入库 MongoDB什么是MongoDBMongoDB安装以及开始运行配置启动以及mongoshmongodb的基础使用命令启动和使用MongoDB服务数据库操作集合操作文档操作 项目部署在数据库中创建一张商品信息表提供信息表的增删改查操作接口 MongoDB 什么是MongoDB Mong…...

内网信息收集——用户凭据窃取

文章目录 一、获取域内单机密码和hash1.1 在线读取lsass进程内存1.2 离线读取lsass.exe进程内存1.3 在线读取本地SAM文件1.4 离线读取本地SAM文件 二、域hash获取三、windows凭据导出 一、获取域内单机密码和hash 在windows中,SAM文件是windows用户的账户数据库&am…...

组串式逆变器散热分析

1 引言 组串式逆变器散热方式主要有强制风冷和自然冷却两种,针对两种散热方式的实际效果,笔者抽取了不同厂家不同散热方式的两款组串式逆变器进行实验对比,发现在同样的环境温度下,强制风冷的逆变器内部环境温度及核心器件温升比…...

)

保姆级教程:手把手教你用Dify 0.6.0源码搭建自己的AI工作流引擎(附避坑指南)

从零构建AI工作流引擎:Dify 0.6.0源码实战指南 当你第一次打开Dify的源码仓库,可能会被那些复杂的目录结构和抽象类搞得一头雾水。别担心,三周前我也和你一样,直到我亲手将这套系统跑起来并修改了第一个工作流节点。本文将带你用最…...

Cosmos-Reason1-7B在计算机组成原理教学中的应用:图解CPU工作流程

Cosmos-Reason1-7B在计算机组成原理教学中的应用:图解CPU工作流程 计算机组成原理这门课,对很多学生来说,就像在学一门“黑魔法”。课本上那些抽象的指令周期、数据通路、控制器,听起来都懂,但一合上书,脑…...

LC滤波器选型避坑指南:为什么你的高频噪声总是滤不干净?

LC滤波器选型避坑指南:为什么你的高频噪声总是滤不干净? 作为硬件工程师,你是否遇到过这样的场景:精心设计的LC滤波器在低频段表现良好,一到高频就"原形毕露"?那些恼人的射频噪声像幽灵一样在电路…...

你的Xbox手柄电量还能撑多久?解决游戏中断的电量管家

你的Xbox手柄电量还能撑多久?解决游戏中断的电量管家 【免费下载链接】XB1ControllerBatteryIndicator A tray application that shows a battery indicator for an Xbox-ish controller and gives a notification when the battery level drops to (almost) empty.…...

实战应用:基于快马平台构建支持高并发的医院预约系统后端服务

今天想和大家分享一个实战项目:基于InsCode(快马)平台构建医院预约系统后端服务的经验。这个系统需要处理高并发预约、确保数据一致性,还要对接短信通知等第三方服务,对代码健壮性要求很高。 系统架构设计 医院预约系统的核心是要解决"…...

)

GPCC数据不止看趋势:手把手教你用MATLAB做降水信号的谐波分析(附周年振幅相位代码)

GPCC数据不止看趋势:手把手教你用MATLAB做降水信号的谐波分析(附周年振幅相位代码) 长江流域的降水变化对农业生产、水资源管理和生态保护都具有重要意义。当我们拿到GPCC的月尺度降水数据时,除了绘制时间序列图观察趋势外&#x…...

效率提升神器:用快马AI自动诊断并修复npm 128错误,节省排错时间

效率提升神器:用快马AI自动诊断并修复npm 128错误,节省排错时间 最近在团队协作开发一个Node.js项目时,频繁遇到npm安装依赖报错128的问题。每次都要花大量时间排查SSH配置、网络代理或仓库源的问题,严重影响了开发效率。于是我开…...

[嵌入式系统]的[WiFi网络配置]:从[连接不稳定]到[可靠通信]的实践指南

[嵌入式系统]的[WiFi网络配置]:从[连接不稳定]到[可靠通信]的实践指南 【免费下载链接】arduino-esp32 Arduino core for the ESP32 项目地址: https://gitcode.com/GitHub_Trending/ar/arduino-esp32 1. 问题发现:WiFi连接的隐形障碍 当我们在开…...

OmenSuperHub终极指南:掌控惠普游戏本性能与散热的完整解决方案

OmenSuperHub终极指南:掌控惠普游戏本性能与散热的完整解决方案 【免费下载链接】OmenSuperHub 使用 WMI BIOS控制性能和风扇速度,自动解除DB功耗限制。 项目地址: https://gitcode.com/gh_mirrors/om/OmenSuperHub 你是否曾因惠普游戏本过热降频…...

避坑指南:ArcGIS核密度分析做POI研究,这3个参数设置错了等于白做

避坑指南:ArcGIS核密度分析做POI研究,这3个参数设置错了等于白做 在商业选址、城市规划或学术研究中,POI(兴趣点)数据的空间分布分析往往直接影响决策质量。核密度分析作为ArcGIS中最常用的空间统计工具之一࿰…...