FPGA 综合笔记

仿真时阻塞赋值和非阻塞赋值

Use of Non-Blocking Assignment in Testbench : Verilog

Use of Non-Blocking Assignment in Testbench : Verilog - Stack Overflow

non-blocking assignment does not work as expected in Verilog

non-blocking assignment does not work as expected in Verilog - Electrical Engineering Stack Exchange

This is actually quite similar to a question I answered previously, but I will try to build up a canonical answer for this somewhat common issue.

In a zero-delay simulation like this, the test flip-flop has a setup time and a hold time of zero:

```math

Tsetup=Thold=0

```

What this means is that the instant the sensitive clock edge occurs, the output is updated, regardless of what happened immediately before or after that instant. This is not like real hardware which would usually have a non-zero 𝑇𝑠𝑒𝑡𝑢𝑝 and 𝑇ℎ𝑜𝑙𝑑.

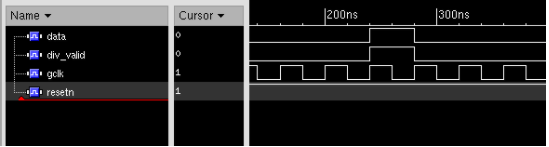

I ran your testbench, and the results are pretty clear. The valid signal changes at the same time the clock signal does. You have delayed them by precisely the same amount. So at the very edge when the clock is high, the valid signal has also changed:

Both the input (div_valid), and the clock (gclk) go high at the same time: 220 ns. Therefore, the DFF latches this new data, and the output changes instantly since there is also 0 propagation delay. This simulation would look less confusing if we just chose a different delay value for the input to the design:

In this case, we update the input on the falling edge of the clock (620 ns). It is much more clear now that the next clock edge (640 ns) will be when the DFF updates its output.

Curious state transitions in state machine RTL simulation

digital logic - Curious state transitions in state machine RTL simulation - Electrical Engineering Stack Exchange

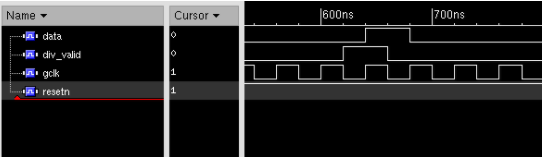

Pitfall: If your testbench updates the TxSync input exactly at the rising clock edge, You will just have a glitch in nextState. Your simulator may remove this glitch, making it look like nextState never entered State_WRITETOLANE1, when in fact it did, just for a very brief moment. This would make it look like currentState latched a value that nextState never had.

Remedy: Don't update the inputs exactly at the rising clock edge. Add some small delay so that the simulation can be more clearly understood. In my case, I updated the input at the falling clock edge. But the update time is arbitrary if you are doing a 0 delay simulation.

陷阱:如果您的测试台在上升的时钟边缘精确更新了 TxSync 输入,那么 nextState 中将会出现一个毛刺。您的模拟器可能会消除这个毛刺,使其看起来 nextState 从未进入过 State_WRITETOLANE1 状态,但实际上它确实进入过,只是非常短暂。这会让它看起来 currentState 捕获了一个 nextState 从未拥有的值。

解决方法:不要在上升的时钟边缘精确更新输入。增加一些小延迟,以便模拟更清晰地理解。在我的情况下,我是在下降的时钟边缘更新输入的。但如果您正在进行零延迟模拟,更新时间是任意的。

Quartus 编译错误

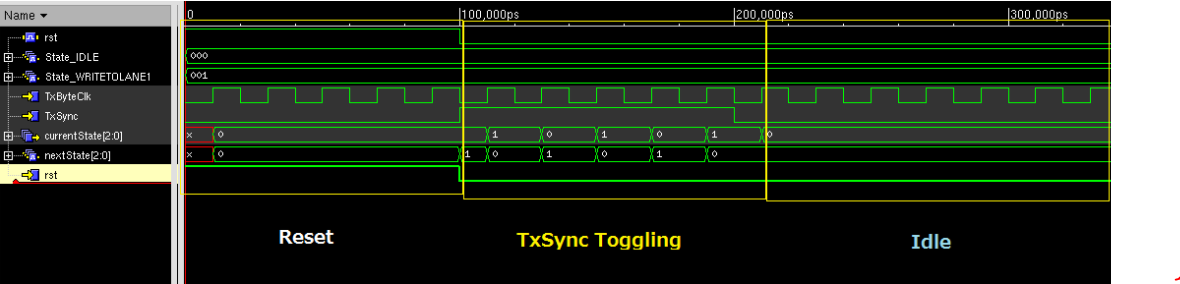

Can't place multiple pins assigned to pin location

Error (176310): Can't place multiple pins assigned to pin location Pin_101 (IOPAD_X34_Y18_N21) Info (176311): Pin ch1_dac[3] is assigned to pin location Pin_101 (IOPAD_X34_Y18_N21) Info (176311): Pin ALTERA_nCEO is assigned to pin location Pin_101 (IOPAD_X34_Y18_N21)

解决办法:

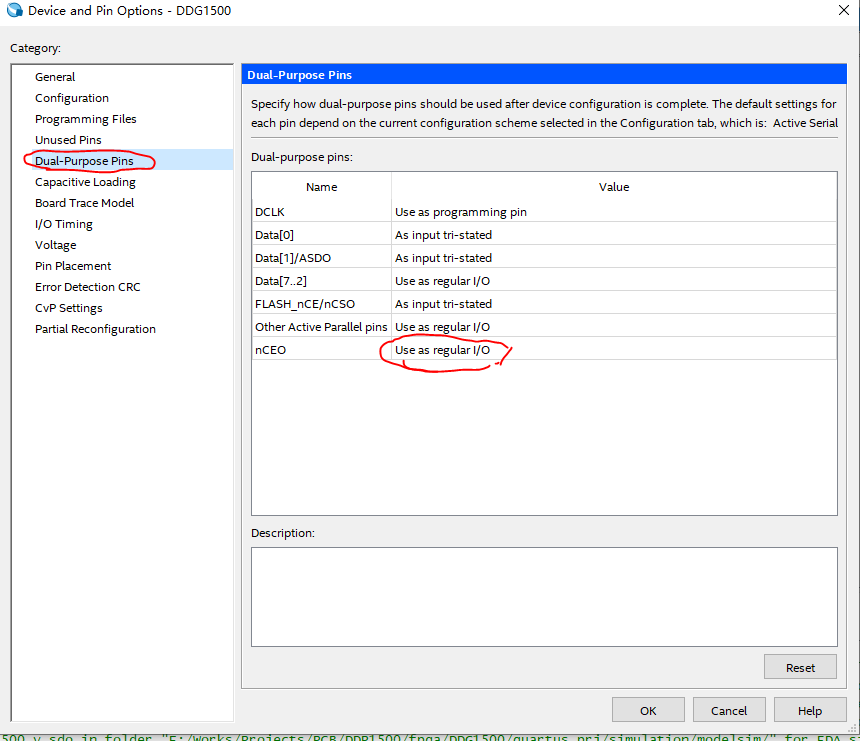

菜单->Assignments->Device->Device and Pin Options:

将相关引脚改为普通 IO:

仿真通过,上板验证失败

解决办法:板子断电,上电,再烧录

一个可能的原因:FPGA 器件支持除法吗?

固化程序启动失败

故障描述

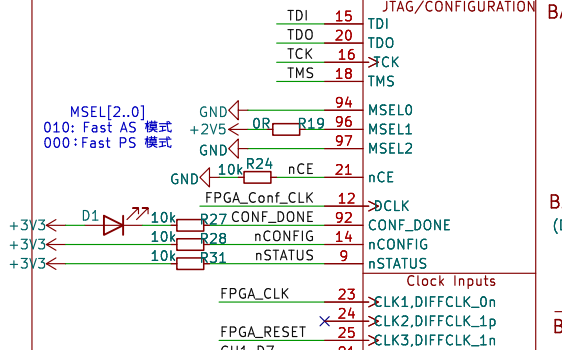

EP4CE6E22C8 通过 jic 文件固化成功,但是启动失败,FPGA 的 CONF_DONE 引脚输出总是低。实际该引脚在配置期间为低,配置成功后为高。

启动失败板子:带10k 上电阻,CONIFG_DONE 脚对地95M电阻,对VCC电阻:32k

启动 OK 的板子:CONFIG_DONE 脚对比:102M,, 对 VCC电阻:102M

故障原因

怀疑1:板子 FPGA 引脚有四根分线,怀疑是飞线过多,在操作时烧了板子。

怀疑2: CONF_DONE 引脚的 R27、D1 是手焊的,可能在焊接时烧了板子?

尝试

测量 FPGA 晶振频率: OK

尝试重新焊接 R19 ,失败

尝试更换 W25Q16: 失败

尝试重新编译: 失败

FPGA 坏了,只能更换FPGA

相关文章:

FPGA 综合笔记

仿真时阻塞赋值和非阻塞赋值 Use of Non-Blocking Assignment in Testbench : Verilog Use of Non-Blocking Assignment in Testbench : Verilog - Stack Overflow non-blocking assignment does not work as expected in Verilog non-blocking assignment does not work a…...

Android MVVM框架详解与应用

在Android开发中,随着应用复杂度的增加,如何有效地组织和管理代码成为了一个重要的问题。MVVM(Model-View-ViewModel)架构模式因其清晰的结构和高效的开发效率,逐渐成为Android开发者们青睐的架构模式之一。本文将详细…...

浅析KHD-厨帽检测算法从源码到实际应用的方案

厨帽检测算法,作为计算机视觉技术在食品安全领域的一项重要应用,其实际应用过程涉及多个方面。 厨帽检测算法主要基于深度学习技术,特别是卷积神经网络(CNN)和目标检测框架(如YOLO、Faster RCNN等ÿ…...

)

ESXi里的FreeBSD装bhyve Ubuntu子系统,外网不通,子系统里无法ping通外面(使用NAT解决)

ESXi里的FreeBSD装bhyve Ubuntu子系统,子系统里无法ping通外面,除了宿主机,其它ip都ping不通。(另一台FreeBSD物理机同样的bhyve ubuntu子系统,网络就是通的,但是TrinityCore服务lag延时很大) …...

Connectionist Logic Systems and Hybrid Systems by Translation

Connectionist Logic Systems Definition: Connectionist Logic Systems (CLS) are computational models that combine elements of connectionism (neural networks) with symbolic logic. These systems aim to leverage the strengths of both paradigms—connectionism’…...

盘点数据摆渡的8种常用方式 最推荐哪一种?

跨网数据摆渡是很多企业面临的一种传输场景,因为大部分企业为了保护核心数据,都会做不同级别的网络隔离,所以数据摆渡会涉及不同网络之间的数据传输和整合。这种情况下,数据需要从一个组织或地理位置传输到另一个组织或地理位置&a…...

仿照ContentLoadingProgressBar 的特点在Android项目中自定义Loading对话框

ContentLoadingProgressBar 是 Android 中的一个控件,继承自 ProgressBar。它在 ProgressBar 的基础上添加了一些特殊功能,主要用于在加载内容时显示进度。它的一些主要特点如下: 自动隐藏和显示:ContentLoadingProgressBar 会在…...

基于数据复杂度的数据库选型

数据模型的选择对于 IT 系统的开发至关重要,它不仅决定了数据存储和处理的方式,影响系统的性能、扩展性以及维护性等。本质上来说,不同的数据模型反映了我们对业务问题的不同思考和抽象程度。 今天我们从不同数据模型对于复杂数据和关系的支…...

QT基础知识5

思维导图 client.cpp #include "widget.h" #include "ui_widget.h"Widget::Widget(QWidget *parent): QWidget(parent), ui(new Ui::Widget), socket(new QTcpSocket(this))//给客户端实例化分配空间 {ui->setupUi(this);//初始化界面ui->msgEdit-&…...

C++中vector存放内置数据类型

#include<iostream> using namespace std; #include<vector> #include<algorithm>//迭代器先理解为指针 void MyPrint(int val) {cout << val << endl; } void test01() {vector<int> v;v.push_back(1);v.push_back(2);vector<int>:…...

shell编程:安装部署前常见环境检查

脚本任务 监测主机是否联通正常 检查安装操作系统版本是否和需求一致 检查CPU是否满足规格要求 检查内存是否满足规格要求 检查数据磁盘是否满足规格要求 检查操作系统分区目录大小是否满足需求 检查集群主机时间是否一致 0.配置文件准备及脚本变量初始化 编写config.i…...

思特科技:国家宝藏数字体验馆展现东方美学 让“文物活起来”

01 思特科技为“国家宝藏数字体验展”提供“数字技术”支持,带来国宝的数字化演绎。以《国家宝藏》顶级IP为基础,打造的全新沉浸文化项目“国宝数字体验展“,借由文物的视角、站在历史的星河中,探寻时间长河中不变的智慧…...

ES6笔记总结(Xmind格式):第二天

Xmind鸟瞰图: 简单文字总结: ES6知识总结 Proxy(代理): 1.作用:实现数据的私有化处理 2.target 目标对象 handler处理函数 3.处理函数中有两个方法:get,set 4.读取数据会触发g…...

Kotlin 流flow、ShareFlow、StateFlow、Channel的解释与使用

一、介绍 随着Android接入kotlin开发,Android之前好多模式也渐渐被kotlin替代。开发模式也在做渐进的转型,从MVC到MVP在到MVVP以及现在的MVI等。 流IO在java中和kotlin中使用率都是比较高的,场景很多。如Java的IO和NIO,再到我们现…...

【个人学习】JVM(7):方法区概述、方法区内部结构、垃圾回收等

方法区 栈、堆、方法区的交互关系 从线程共享与否的角度来看 ThreadLocal:如何保证多个线程在并发环境下的安全性?典型场景就是数据库连接管理,以及会话管理。 栈、堆、方法区的交互关系 下面涉及了对象的访问定位 Person 类的 .class 信息存放在方法区中person 变量存放…...

@Scheduled 定时任务自定义

简介 Scheduled 定时任务自定义可以通过SchedulingConfigurer实现。 SchedulingConfigurer 是 Spring Framework 中的一个接口,用于配置定时任务。当你需要对定时任务进行更高级别的定制时,这个接口就显得非常有用。 可以通过SchedulingConfigurer 接口…...

一种新颖的面试方式

你好,我是 shengjk1,多年大厂经验,努力构建 通俗易懂的、好玩的编程语言教程。 欢迎关注!你会有如下收益: 了解大厂经验拥有和大厂相匹配的技术等 希望看什么,评论或者私信告诉我! 文章目录 一…...

【Linux】生产消费模型实践 --- 基于信号量的环形队列

你送出去的每颗糖都去了该去的地方, 其实地球是圆的, 你做的好事终会回到你身上。 --- 何炅 --- 基于信号量的环形队列 1 信号量2 框架构建3 代码实现4 测试运行 1 信号量 信号量本质是一个计数器,可以在初始化时对设置资源数量…...

Science Robotics 与蜜蜂群互动的蜂窝型机器人系统

蜜蜂,如黄蜂,蚂蚁和其他社会昆虫,建立大型自组织群体,通常被解释为自我调节的“超有机体”。这些超生物是生态系统的重要稳定剂,因此被认为是“关键物种”。例如,蜜蜂群落通过觅食授粉服务的生态效应对陆地…...

Vue 计算属性:优雅地处理数据逻辑

在 Vue.js 中,计算属性(Computed Properties)是一种非常实用的功能,它允许我们根据组件的响应式依赖进行缓存和派生状态。计算属性可以让我们以声明式的方式编写复杂的逻辑,而不必担心性能问题。 什么是计算属性&…...

JSON Lint for PHP:如何构建企业级JSON数据验证解决方案?

JSON Lint for PHP:如何构建企业级JSON数据验证解决方案? 【免费下载链接】jsonlint JSON Lint for PHP 项目地址: https://gitcode.com/gh_mirrors/jso/jsonlint 在现代Web开发和API设计中,JSON数据验证是确保系统稳定性的关键环节。…...

CircuitPython音频输出与PWM伺服电机控制实战指南

1. 项目概述与核心价值如果你正在用像Adafruit的Feather M0、ItsyBitsy或者Circuit Playground Express这类小巧的微控制器板子做项目,想让它们“开口说话”或者“动手干活”,那么音频输出和伺服电机控制就是你绕不开的两项核心技能。前者能让你的项目发…...

实战解析:XiaoMusic技术架构深度剖析与智能音箱语音控制实现方案

实战解析:XiaoMusic技术架构深度剖析与智能音箱语音控制实现方案 【免费下载链接】xiaomusic 使用小爱音箱播放音乐,音乐使用 yt-dlp 下载。 项目地址: https://gitcode.com/GitHub_Trending/xia/xiaomusic 在智能音箱生态中,小爱音箱…...

从Git历史到数据洞察:构建代码仓库统计分析工具的设计与实践

1. 项目概述:一个为开发者量身定制的代码统计工具 在软件开发的日常中,无论是个人复盘、团队汇报,还是项目交接,我们常常会遇到一个看似简单却颇为棘手的问题:如何客观、量化地评估一个代码仓库的“工作量”或“活跃度…...

Python爬虫利器PyQuery:用jQuery语法高效解析HTML与数据提取

1. PyQuery:让Python爬虫和数据处理拥有jQuery的丝滑体验如果你和我一样,既写Python脚本处理数据,又偶尔需要和前端HTML打交道,那你一定经历过这样的纠结:面对一堆杂乱无章的HTML标签,用正则表达式吧&#…...

ubuntu25 安装ORG flow

下载ORG flow https://github.com/infiniflow/ragflow 上传至home文件夹下 进入文件夹/ragflow-main/docker下 安装docker: sudo snap install docker 安装gnome-terminal sudo apt install gnome-terminal sudo install -m 0755 -d /etc/apt/keyrings sudo curl -fsSL …...

Midscene.js 2025技术演进:从自动化工具到智能操作平台的架构升级

Midscene.js 2025技术演进:从自动化工具到智能操作平台的架构升级 【免费下载链接】midscene AI-powered, vision-driven UI automation for every platform. 项目地址: https://gitcode.com/GitHub_Trending/mid/midscene 在人工智能技术快速发展的今天&…...

代码可视化工具:从AST解析到自动化图表生成的技术实践

1. 项目概述:从代码到图形的自动化桥梁在软件开发、架构设计乃至技术文档编写的日常工作中,我们常常面临一个共同的痛点:如何清晰、高效地向他人(或未来的自己)解释一段复杂的代码逻辑、一个系统的模块关系,…...

从create-codex项目看AI代码生成工具的工程化集成实践

1. 项目概述:从“create-codex”看AI代码生成工具的深度集成最近在GitHub上看到一个挺有意思的项目,叫ramonclaudio/create-codex。光看这个名字,很多开发者可能就会心一笑——“create”前缀加上“codex”,这不就是围绕OpenAI的C…...

基于MCP协议构建个人AI助手:本地化读取Mac消息数据库实践

1. 项目概述:一个让AI助手“读懂”你Mac消息的桥梁如果你和我一样,是个重度依赖Mac原生“信息”应用(也就是iMessage)来沟通的人,同时又希望自己的AI助手(比如Claude、Cursor里的AI)能更深入地了…...