AD7606工作原理以及FPGA控制验证(串行和并行模式)

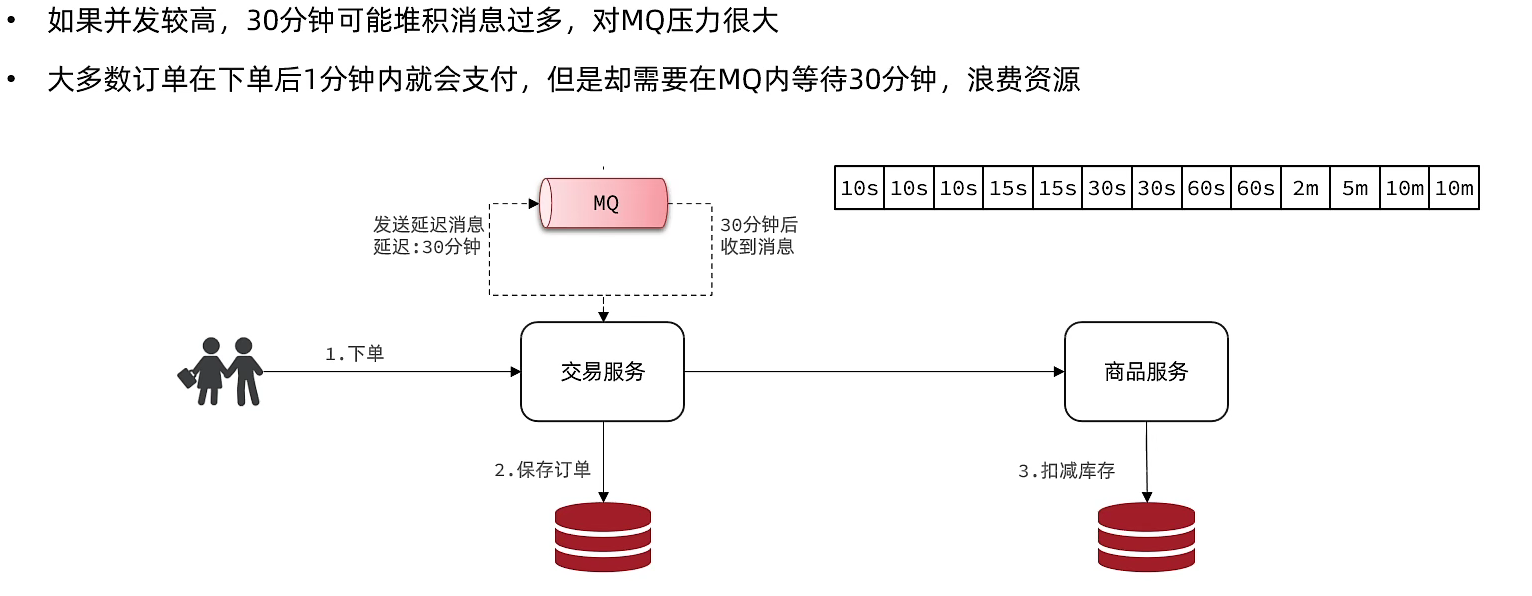

文章目录

- 一、AD7606介绍

- 二、AD7606采集原理

- 2.1 AD7606功能框图

- 2.2 AD7606管脚说明

- 三、AD7606并行模式时序分析以及实现

- 3.1 并行模式时序图

- 3.2 并行模式时序要求

- 3.3 代码编写

- 3.4 仿真观察

- 四、AD7606串行模式时序分析以及实现

- 4.1 串行模式时序图

- 4.2 串行模式时序要求

- 4.3 代码编写

- 4.4 添加仿真模型以及观察

一、AD7606介绍

AD7606有三种,分别有8个、6个或4个通道,采样深度有16位(即最小采样的电压为5V/(2^16) = 0,00007V,实际上达不到);采用5V单电源供电,可以处理±10V 和±5V 真双极性输入信号;具有内部的2.5V基准电压;同时所有通道均能以高达200kSPS的吞吐速率采样,提供过采样功能以及串行输出和并行输出两种模式;广泛用于低速采集场景。

二、AD7606采集原理

下图为AD7606-8的芯片封装图:

2.1 AD7606功能框图

下图为AD7606-8内部的功能框图:

ADC工作原理:采样:对模拟值进行采样 -> 保持:将开关保持一段时间以将电容充电到采集电压值 -> 量化 编码:将电压值转化为数字量。

2.2 AD7606管脚说明

7606的管脚很多,我们选一些重要的管脚来说明:

| 管脚名称 | 描述 |

| AVcc | 模拟电压源,4.75V至5.25V |

| AGNG | 接地 |

| OS[2:0] | 过采样模式引脚。逻辑输入。这些输入用来选择过采样倍率。OS2为MSB控制位,OS0则为LSB控制位。 |

| PAR(低电平有效)/SER/BYTE SEL | 并行/串行/字节接口选择输入。如果此引脚与逻辑低电平相连,则选择并行接口。如果此引脚与逻辑高电平相连,则选择串行接口 |

| RANG | 模拟输入范围选择输入,如果此引脚与逻辑高电平相连,则所有通道的模拟输入范围为+10V。如果此引脚与逻辑低电平相连,则所有通道的模拟输入范围为+5 V |

| CONVST A / CONVST B | 启动转换信号,CONVST A启动通道1,2,3,4;CONVST B启动通道5,6,7,8 |

| RESET | 复 位 输 入 。 当设 置 为 逻 辑 高 电 平 时 , RESET上 升 沿 复 位;RESET高脉冲宽度典型值为50ns。如果在转换期间施加RESET脉冲,转换将中断。如果在读取期间施加RESET脉冲, 输出寄存器的内容将复位为0。 |

| RD(低电平有效)/SCIK | 选择并行接口时为并行数据读取控制输入(RD_)/选择串行接口时为串行时钟输入(SCLK)。在并行模式下, 如果CS_和RD_均处于逻辑低电平, 则会启用输出总线。在串行模式下, 此引脚用作数据传输的串行时钟输入。CS_下降沿使数据输出线路DoutA和DoutB脱离三态, 并逐个输出转换结果的MSB。SCLK上升沿将随后的所有数据位逐个送至串行数据输出DoutA和DoutB。 |

| CS | 片选。此低电平有效。在并行模式下, 如果CS和RD均处于逻辑低电平, 则会使能输出总线DB[15:0]。在串行模式下, CS使能串行数据帧传输, 并逐个输出串行输出数据的最高有效位(MSB)。 |

| BUSY | 输出繁忙信号。CONVST A和CONVST B均达到上升沿之后, 此引脚变为逻辑高电平, 表示转换过程已开始。BUSY输出保持高电平, 直到所有通道的转换过程完成为止。BUSY下降沿表示转换数据正被锁存至输出数据寄存器, 经过时间t₄之后便可供读取。在BUSY为高电平时执行的数据读取操作应当在BUSY下降沿之前完成。当BUSY信号为高电平时, CONVST A或CONVSTB的上升沿不起作用。 |

| FRSTDATA | FRSTDATA输出信号指示何时在并行、字节或串行接口上回读第一通道V1。在并行模式下, 与V1结果相对应的RD下降沿随后将FRSTDATA引脚设为高电平, 表示输出数据总线可以提供V1的结果。在RD的下一个下降沿之后, FRSTDATA输出恢复逻辑低电平。在串行模式下, FRSTDATA在CS下降沿变为高电平, 因为此时将在DoutA上输出V1的MSB。在CS下降沿之后的第16个SCLK下降沿, 它恢复低电平。 |

| DB0 - DB15 | 读数据总线 |

OS[2:0]过采样模式选择

| OS2 ,OS1,OS0 | 说明 | 最大速率 |

| 000 | 无过采样 | 200Ksps |

| 001 | 2倍过采样 | 100Ksps |

| 010 | 4倍过采样 | 50Ksps |

| 011 | 8倍过采样 | 25Ksps |

| 100 | 16倍过采样 | 12.5Ksps |

| 101 | 32倍过采样 | 6.25Ksps |

| 110 | 64倍过采样 | 3.125Ksps |

| 111 | 无效 |

三、AD7606并行模式时序分析以及实现

3.1 并行模式时序图

3.2 并行模式时序要求

| 时间名称 | 时间长度 | 描述 |

| tRESET | 50ns | 高电平复位最小宽度 |

| t2 | 25ns | CONVST低电平脉冲最短宽度 |

| t7 | 25ns | RESET低电平到CONVST高电平之间最短宽度 |

| t5 | 0.5ms | CONVSTA和CONVSTB上升沿之间的最短延迟时间 |

| t1 | 40ns | CONVST上升沿到BUSY上升沿之间的最长延迟时间 |

| tCYCLE | 5us | CONVST上升沿到CONVST上升沿之间的最长延迟时间 |

| t3 | 25ns | CONVST高电平最短时间 |

| t4 | 0ns | BUSY下降沿到CS下降沿最短时间 |

| t8 | 0ns | cs下降沿和RD下降沿最短时间 |

| t10 | 16/21/25/32ns | RD低电平脉冲宽度,根据Vdrive电平判断 |

| t11 | 15ns | RD低电平脉冲宽度最小值 |

| t9 | 0ns | RD上升沿到CS上升沿的最小时间 |

| tCONV | 3.45us | 转换时间最低3.45us,最高4.15us |

3.3 代码编写

输入可以用一个开始信号控制启动转换:

module ad7606_ctrl_par(input i_clk , // 输入系统时钟,50minput i_rst , input i_start , // 7606开始转换控制信号 input [15:0] i_ad_data , // ad7606 采样数据input i_ad_busy , // ad7606 忙标志位 input i_first_data , // ad7606 第一个数据标志位 output [ 2:0] o_ad_os , // ad7606 过采样倍率选择output o_ad_cs , // ad7606 AD csoutput o_ad_rd , // ad7606 AD data readoutput o_ad_reset , // ad7606 AD resetoutput o_ad_convstA , // ad7606 AD convert startAoutput o_ad_convstB , // ad7606 AD convert startBoutput [15:0] o_ad_ch1 , // AD第1通道的数据output o_ad_ch1_valid , // AD第1通道的数据有效信号output [15:0] o_ad_ch2 , // AD第2通道的数据output o_ad_ch2_valid , // AD第2通道的数据有效信号output [15:0] o_ad_ch3 , // AD第3通道的数据output o_ad_ch3_valid , // AD第3通道的数据有效信号output [15:0] o_ad_ch4 , // AD第4通道的数据output o_ad_ch4_valid , // AD第4通道的数据有效信号output [15:0] o_ad_ch5 , // AD第5通道的数据output o_ad_ch5_valid , // AD第5通道的数据有效信号output [15:0] o_ad_ch6 , // AD第6通道的数据output o_ad_ch6_valid , // AD第6通道的数据有效信号output [15:0] o_ad_ch7 , // AD第7通道的数据output o_ad_ch7_valid , // AD第7通道的数据有效信号output [15:0] o_ad_ch8 , // AD第8通道的数据 output o_ad_ch8_valid // AD第8通道的数据有效信号

);

整个操作可以用一个状态机来控制,状态定义如下:

/***************parameter*************/

localparam RESET = 4'd0 ; //复位状态

localparam AD_CONSVT = 4'd1 ; //开启转换

localparam BUSY = 4'd2 ; //等待busy

localparam READ_CH1 = 4'd3 ; //读通道1数据

localparam READ_CH2 = 4'd4 ; //读通道2数据

localparam READ_CH3 = 4'd5 ; //读通道3数据

localparam READ_CH4 = 4'd6 ; //读通道4数据

localparam READ_CH5 = 4'd7 ; //读通道5数据

localparam READ_CH6 = 4'd8 ; //读通道6数据

localparam READ_CH7 = 4'd9 ; //读通道7数据

localparam READ_CH8 = 4'd10; //读通道8数据

localparam READ_DONE = 4'd11; //读完成

整个控制代码比较简单,这里就不全放出来了,直接看仿真:

3.4 仿真观察

仿真给出时钟复位即可,busy信号一直给0,data固定为d‘11,我们来看各信号的时序是否满足手册要求,仿真代码如下:

`timescale 1ns / 1psmodule tb_ad7606_ctrl_par();reg i_clk;

reg i_rst;initial begini_clk =0;i_rst = 1;#250;i_rst = 0;

endalways #10 i_clk = ~i_clk;ad7606_ctrl_par u_ad7606_ctrl_par(.i_clk ( i_clk ),.i_rst ( i_rst ),.i_start ( 1'b1 ),.i_ad_data ( 16'd11 ),.i_ad_busy ( 1'b0 ),.i_first_data ( ),.o_ad_os ( ),.o_ad_cs ( ),.o_ad_rd ( ),.o_ad_reset ( ),.o_ad_convstA ( ),.o_ad_convstB ( ),.o_ad_ch1 ( ),.o_ad_ch1_valid ( ),.o_ad_ch2 ( ),.o_ad_ch2_valid ( ),.o_ad_ch3 ( ),.o_ad_ch3_valid ( ),.o_ad_ch4 ( ),.o_ad_ch4_valid ( ),.o_ad_ch5 ( ),.o_ad_ch5_valid ( ),.o_ad_ch6 ( ),.o_ad_ch6_valid ( ),.o_ad_ch7 ( ),.o_ad_ch7_valid ( ),.o_ad_ch8 ( ),.o_ad_ch8_valid ( )

);endmodule

放大局部来看

- 复位持续了120ns,最低时序要求是复位50ns,复位信号满足时序要求

- CONVST下降沿到CONVST上升沿之间为80ns,最低时序要求是25ns,满足时序要求

- CONVST高电平到CS低电平,手册写的转换时间tCONV最低3.45us、最长4.15us。我们这里取4.16us,满足最长转换时序。

- RD一个周期的时间为80ns,高低电平时间为40ns,满足时序要求最高的32ns

- 上一个CONVST上升沿在450ns,下一个上升沿在5470ns,一个tCYCLE时间为5.02us,满足手册要求的最长tCYCLE5us。

因此,所有输出信号都满足了手册的时序要求,AD7606并行模式仿真验证成功,后续有AD7606模块后再下板验证。

四、AD7606串行模式时序分析以及实现

4.1 串行模式时序图

串行我们使用转换期间读取模式

等busy信号拉低后,就可以拉低CS信号,然后提供SCLK给AD7606,数据按照每bit的传输,用户在SCLK上升沿采样,传输第一个通道的位数据时FRSTDATA会拉高。

4.2 串行模式时序要求

CS信号,CONVST信号和并行一致,剩下的时序如下所示:

4.3 代码编写

顶层我们设置三个参数变量,分别为系统时钟,SPI时钟,和采样周期,这样就能通过这些变量来计算出我们需要的分频计数值。

module ad7606_ctrl_ser#(parameter SYS_CLK_FREQ = 100_000_000, //系统时钟频率SPI_CLK_FREQ = 20_000_000, //SPI时钟频率AD_CAP_FREQ = 200_000 //AD7606采样频率最大200K

)

(input i_clk , // 输入系统时钟,100minput i_rst , input i_start , // 7606开始转换控制信号 input i_ad_data_A , // ad7606 1,2,3,4通道采样数据input i_ad_data_B , // ad7606 5,6,7,8通道采样数据input i_ad_busy , // ad7606 忙标志位 output [ 2:0] o_ad_os , // ad7606 过采样倍率选择output o_ad_cs , // ad7606 AD csoutput o_ad_sclk , // ad7606 AD data readoutput o_ad_reset , // ad7606 AD resetoutput o_ad_convstA , // ad7606 AD convert startAoutput o_ad_convstB , // ad7606 AD convert startBoutput [15:0] o_ad_ch1 , // AD第1通道的数据output [15:0] o_ad_ch2 , // AD第2通道的数据output [15:0] o_ad_ch3 , // AD第3通道的数据output [15:0] o_ad_ch4 , // AD第4通道的数据output [15:0] o_ad_ch5 , // AD第5通道的数据output [15:0] o_ad_ch6 , // AD第6通道的数据output [15:0] o_ad_ch7 , // AD第7通道的数据output [15:0] o_ad_ch8 , // AD第8通道的数据 output o_ad_cap_done // AD所有通道采集数据完成信号

);状态机和分频系数定义如下,由于是串行输入,所以设置一个READ状态即可

/***************parameter*************/

localparam T5US_DIV = SYS_CLK_FREQ / 200_000 -1 ; //200Kbps采样率,因此采样周期为5us

localparam SPI_DIV = SYS_CLK_FREQ / 20_000_000 -1 ; //SPI时钟分频系数

localparam SPI_DIV1 = SPI_DIV/2; //半周期分频

localparam RESET = 4'd0 ; //复位状态

localparam AD_CONSVT = 4'd1 ; //开启转换

localparam BUSY = 4'd2 ; //等待busy

localparam READ = 4'd3 ; //读数据

localparam READ_DONE = 4'd4 ; //读完成

设置两个64bit寄存器来存放几个通道的串行数据,然后再分别分配各各个通道:

reg [63:0] ad_dataA ;

reg [63:0] ad_dataB ;

assign o_ad_ch1 = ad_dataA[63:48] ;

assign o_ad_ch2 = ad_dataA[47:32] ;

assign o_ad_ch3 = ad_dataA[31:16] ;

assign o_ad_ch4 = ad_dataA[15: 0] ;

assign o_ad_ch5 = ad_dataB[63:48] ;

assign o_ad_ch6 = ad_dataB[47:32] ;

assign o_ad_ch7 = ad_dataB[31:16] ;

assign o_ad_ch8 = ad_dataB[15: 0] ;

4.4 添加仿真模型以及观察

仿真代码如下:

`timescale 1ns / 1ps

module tb_ad7606_ctrl_ser();reg i_clk ;

reg i_rst ;

wire i_ad_data_A ;

wire i_ad_data_B ;

wire i_ad_busy ;

wire o_ad_convstA ;

wire o_ad_convstB ;

wire o_ad_cs ;

wire o_ad_sclk ;

wire o_ad_reset ;initial begini_clk =0;i_rst =1;#250;i_rst = 0;

endalways #5 i_clk = ~i_clk;ad7606_ctrl_ser#(.SYS_CLK_FREQ( 100_000_000 ),.SPI_CLK_FREQ( 20_000_000 ),.AD_CAP_FREQ ( 200_000 )

)u_ad7606_ctrl_ser(.i_clk ( i_clk ),.i_rst ( i_rst ),.i_start ( 1'b1 ),.i_ad_data_A ( i_ad_data_A ),.i_ad_data_B ( i_ad_data_B ),.i_ad_busy ( i_ad_busy ),.o_ad_os ( ),.o_ad_cs ( o_ad_cs ),.o_ad_sclk ( o_ad_sclk ),.o_ad_reset ( o_ad_reset ),.o_ad_convstA ( o_ad_convstA ),.o_ad_convstB ( o_ad_convstB ),.o_ad_ch1 ( ),.o_ad_ch2 ( ),.o_ad_ch3 ( ),.o_ad_ch4 ( ),.o_ad_ch5 ( ),.o_ad_ch6 ( ),.o_ad_ch7 ( ),.o_ad_ch8 ( ),.o_ad_cap_done ( )

);ad7606 ad7606_inst

(

.ad_busy (i_ad_busy ), //ad7606 忙标志位 输出

.ad_cs (o_ad_cs ), //ad7606 CS信号输入,低电平SPI数据线输出AD7606寄存器数据

.ad_sclk (o_ad_sclk ), //ad7606 SCLK时钟输入

.ad_reset (o_ad_reset ), //ADC复位输入

.ad_convsta (o_ad_convstA ), //ad7606 A组通道转换

.ad_convstb (o_ad_convstB ), //ad7606 B组通道转换

.ad_range (1'b0 ), //ad7606 模拟输入范围,设置1范围:±10V,设置0范围±5V

.ad_out_a (i_ad_data_A ), //A组通道采集有效数据输出

.ad_out_b (i_ad_data_B ) //B组通道采集有效数据输出

); endmodule 采样周期5.07us,满足AD7606最大的5us

采样出来的仿真模型也是正确的,至此AD7606的串行和并行验证都完成。

本文资料获取:

AD7606串行输出verilog代码以及串行仿真模型和AD7606中文原理图

AD7606并行输出verilog代码以及AD7606中文原理图

相关文章:

AD7606工作原理以及FPGA控制验证(串行和并行模式)

文章目录 一、AD7606介绍二、AD7606采集原理2.1 AD7606功能框图2.2 AD7606管脚说明 三、AD7606并行模式时序分析以及实现3.1 并行模式时序图3.2 并行模式时序要求3.3 代码编写3.4 仿真观察 四、AD7606串行模式时序分析以及实现4.1 串行模式时序图4.2 串行模式时序要求4.3 代码编…...

如何查看Pod的Container资源占用情况

云原生学习路线导航页(持续更新中) 方法一:直接查看pod的资源占用 kubectl top pods ${pod-name} -n ${ns} 方法二:通过运行的进程,查看pod的某个容器资源占用 1.找到pod所在node容器号:kubectl descri…...

WordPress上可以内容替换的插件

插件下载地址:WordPress内容替换插件 – 果果开发 类型 替换的类型:文章、自定义文章类型、分类、标签、媒体库、页面、评论、数据库表,不同的类型可以替换不同的字段。 替换字段 替换的字段,哪些字段内容需要替换。除了数据库…...

C++ | Leetcode C++题解之第355题设计推特

题目: 题解: class Twitter {struct Node {// 哈希表存储关注人的 Idunordered_set<int> followee;// 用链表存储 tweetIdlist<int> tweet;};// getNewsFeed 检索的推文的上限以及 tweetId 的时间戳int recentMax, time;// tweetId 对应发送…...

构建并训练卷积神经网络(CNN)对CIFAR-10数据集进行分类

深度学习实践:构建并训练卷积神经网络(CNN)对CIFAR-10数据集进行分类 引言 在计算机视觉领域中,CIFAR-10数据集是一个经典的基准数据集,广泛用于图像分类任务。本文将介绍如何使用PyTorch框架构建一个简单的卷积神经…...

flowable 根据xml 字符串生成流程图

//获取xml InputStream stream repositoryService.getProcessModel(processDefinitionId); String result IOUtils.toString(stream, StandardCharsets.UTF_8); // 创建 XMLInputFactory XMLInputFactory factory XMLInputFactory.newInstance(); // 从字符…...

AI建模——AI生成3D内容算法产品介绍与模型免费下载

说明: 记录AI文生3D模型、图生3D模型的相关产品;记录其性能、功能、收费与免费方法 0.AI建模产品 Rodin MeshAnything Meshy 生成效果比较: Rodin效果最好、Meshy其次 1.Rodin 官网:gHyperHuman 支持:文生模型、…...

在Go中迅速使用RabbitMQ

文章目录 1 认识1.1 MQ分类1.2 安装1.3 基本流程 2 [Work模型](https://www.rabbitmq.com/tutorials/tutorial-two-go#preparation)3 交换机3.1 fanout3.2 direct3.3 [topic](https://www.rabbitmq.com/tutorials/tutorial-five-go) 4 Golang创建交换机/队列/Publish/Consume/B…...

Windows JDK安装详细教程

一、关于JDK 1.1 简介 Java是一种广泛使用的计算机编程语言,拥有跨平台、面向对象、泛型编程的特性,广泛应用于企业级Web应用开发和移动应用开发。 JDK(Java Development Kit)是用于开发 Java 应用程序的工具包。它由以下几个主要…...

Ribbon负载均衡底层原理

springcloude服务实例与服务实例之间发送请求,首先根据服务名注册到nacos,然后发送请求,nacos可以根据服务名找到对应的服务实例。 SpringCloudRibbon的底层采用了一个拦截器,拦截了openfeign发出的请求,对地址做了修…...

【C语言可变参数函数的使用与原理分析】

文章目录 1 前言2 实例2.1实例程序2.2程序执行结果2.3 程序分析 3 补充4 总结 1 前言 在编程过程中,有时会遇到需要定义参数数量不固定的函数的情况。 C语言提供了一种灵活的解决方案:变参函数。这种函数能够根据实际调用时的需求,接受任意…...

【笔记】Java EE应用开发环境配置(JDK+Maven+Tomcat+MySQL+IDEA)

一、安装JDK17 1.下载JDK17 https://download.oracle.com/java/17/archive/jdk-17.0.7_windows-x64_bin.zip 2.配置环境变量 下载后,解压到本地(目录中最好不要有中文或特殊字符) 打开【控制面板】-【系统和安全】-【系统】-【高级系统…...

一文讲懂扩散模型

一文讲懂扩散模型 扩散模型(Diffusion Models, DM)是近年来在计算机视觉、自然语言处理等领域取得显著进展的一种生成模型。其思想根源可以追溯到非平衡热力学,通过模拟数据的扩散和去噪过程来生成新的样本。以下将详细阐述扩散模型的基本原理…...

学习笔记八:基于Jenkins+k8s+Git+DockerHub等技术链构建企业级DevOps容器云平台

基于Jenkinsk8sGitDockerHub等技术链构建企业级DevOps容器云平台 测试jenkins的CI/CD在Jenkins中安装kubernetes插件安装blueocean插件配置jenkins连接到我们存在的k8s集群配置pod-template添加自己的dockerhub凭据测试通过Jenkins部署应用发布到k8s开发环境、测试环境、生产环…...

科研绘图系列:R语言柱状图分布(histogram plot)

文章目录 介绍加载R包读取数据画图介绍 柱状图(Bar Chart)是一种常用的数据可视化图表,用于展示和比较不同类别或组的数据。它通过在二维平面上绘制一系列垂直或水平的柱子来表示数据的大小,每个柱子的长度或高度代表一个数据点的数值。柱状图非常适合于展示分类数据的分布…...

vue3+ts封装类似于微信消息的组件

组件代码如下: <template><div:class"[voice-message, { sent: isSent, received: !isSent }]":style"{ backgroundColor: backgroundColor }"click"togglePlayback"><!-- isSent为false在左侧,为true在右…...

ES6 reduce方法详解:示例、应用场景与实用技巧

在JavaScript中,reduce 方法是一个非常强大的数组方法,它允许你将数组中的元素归并(reduce)为单个值。reduce 方法执行一个由你提供的reducer函数(归并函数),将其结果汇总为单一的返回值。 一.…...

java后端保存的本地图片通过ip+端口直接访问

直接上代码吧 package com.ydx.emms.datapro.controller;import org.springframework.context.annotation.Configuration; import org.springframework.web.servlet.config.annotation.ResourceHandlerRegistry; import org.springframework.web.servlet.config.annotation.…...

2024 年高教社杯全国大学生数学建模竞赛B题4小问解题思路(第二版)

原文链接:https://www.cnblogs.com/qimoxuan/articles/18399415 问题 1:抽样检测方案设计 详细解题思路: 确定抽样检测目标:企业需要确定一个可接受的次品率上限(标称值),以及在该次品率下&am…...

docker-nginx数据卷挂载

一、案例1-利用Nginx容器部署静态资源 1.1、需求: 创建Nginx容器, 修改nginx容器内的html目录下的index.html文件,查看变化将静态资源部署到nginx的html目录 1.2、修改html目录下的index.html文件,查看变化 因为docker运用得最小化系统环境,解决办法就…...

Pixel Dimension Fissioner 实战项目:复刻“黑马点评”首页视觉设计

Pixel Dimension Fissioner 实战项目:复刻"黑马点评"首页视觉设计 1. 开场白:当AI遇见UI设计 最近在设计师圈子里有个热门话题:如何用AI工具提升UI设计效率。作为从业多年的设计老鸟,我一直在寻找能真正帮到设计师的智…...

OpenClaw长期运行:Qwen3.5-9B-AWQ-4bit任务守护与自动恢复

OpenClaw长期运行:Qwen3.5-9B-AWQ-4bit任务守护与自动恢复 1. 为什么需要长期运行守护? 去年冬天,我部署了一个OpenClaw自动化流程来整理每日的技术文献。最初只是简单地在终端启动openclaw gateway,结果第三天就发现进程因为SS…...

gte-base-zh模型Java集成开发指南:SpringBoot构建语义搜索服务

gte-base-zh模型Java集成开发指南:SpringBoot构建语义搜索服务 你是不是也遇到过这样的问题?公司内部有海量的文档、产品说明或者用户反馈,想快速找到相关内容,用关键词搜索总是不准,要么搜不全,要么搜出一…...

比迪丽LoRA模型风格迁移实战:将名画风格应用于角色创作

比迪丽LoRA模型风格迁移实战:将名画风格应用于角色创作 最近在玩AI绘画的朋友,可能都遇到过这样的困惑:生成的角色虽然精致,但总觉得少了点“味道”,风格上总是千篇一律。有没有办法让你笔下的“比迪丽”角色…...

AIVideo进阶技巧:如何自定义视频模板和占位符系统

AIVideo进阶技巧:如何自定义视频模板和占位符系统 1. 为什么需要自定义视频模板 在内容创作领域,重复性工作占据了大量时间。以电商行业为例,每个新品发布都需要制作类似的视频结构:产品展示→功能讲解→价格促销→用户评价。传…...

Matlab七次非均匀B样条轨迹规划及基于NSGAII的优化方法

matlab-B样条轨迹规划-1 七次非均匀B样条轨迹规划, 基于NSGAII的时间-能量-冲击最优。 换上自己的关节值和时间就能用,简单好用,最近在搞机器人轨迹规划,发现七次非均匀B样条真是个好东西。它不仅能保证轨迹的平滑性,还…...

OpenClaw私人教练:Phi-3-mini定制健身计划系统

OpenClaw私人教练:Phi-3-mini定制健身计划系统 1. 为什么需要AI私人教练 去年夏天,我发现自己陷入了典型的"健身困境":办了昂贵的健身房会员卡,却因为缺乏科学指导而收效甚微。传统健身APP的模板化方案无法适应我不断…...

如何高效使用Dism++:Windows系统优化与管理的终极指南

如何高效使用Dism:Windows系统优化与管理的终极指南 【免费下载链接】Dism-Multi-language Dism Multi-language Support & BUG Report 项目地址: https://gitcode.com/gh_mirrors/di/Dism-Multi-language Dism是一款功能强大的Windows系统优化工具&…...

声音克隆新玩法:CosyVoice3教你融合多个音色生成独特声线

声音克隆新玩法:CosyVoice3教你融合多个音色生成独特声线 1. 引言:为什么需要声音融合技术 1.1 单一音色的局限性 在数字内容爆炸式增长的今天,声音克隆技术已经成为视频制作、有声读物、虚拟主播等领域的重要工具。然而,传统的…...

Limine混合ISO制作教程:BIOS/UEFI双启动镜像的完整流程

Limine混合ISO制作教程:BIOS/UEFI双启动镜像的完整流程 【免费下载链接】limine Modern, advanced, portable, multiprotocol bootloader and boot manager. 项目地址: https://gitcode.com/gh_mirrors/li/limine Limine是一款现代化、先进的可移植多协议引导…...