HNU-2023电路与电子学-实验3

写在前面:

本次实验是完成cpu设计的剩余部分,整体难度比上一次要小,细心完成就能顺利通过全部测评

一、实验目的

1.了解简易模型机的内部结构和工作原理。

2.分析模型机的功能,设计 8 重 3-1 多路复用器。

3.分析模型机的功能,设计 8 重 2-1 多路复用器。

4.分析模型机的工作原理,设计模型机控制信号产生逻辑。

二、实验内容

1.用 VERILOG 语言设计模型机的 8 重 3-1 多路复用器;

2.用 VERILOG 语言设计模型机的 8 重 2-1 多路复用器;

3.用 VERILOG 语言设计模型机的控制信号产生逻辑。

三、实验过程

1、8 重 3-1 多路复用器

A)创建工程(选择的芯片为 family=Cyclone II;name=EP2C5T144C8)

B) 编写源代码

module mux3_1(a,b,c,s,y);

input [7:0]a,b,c;

input [1:0]s;

output reg[7:0]y;

always @(*)

begin

if(s==2'b01) y<=b;

else if(s==2'b10) y<=c;

else y<=a;

end

endmoduleC) 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

调试过程无错误

D) RTL 视图

视图分析及结论:

视图分析:

通过观察 RTL 视图可知:左侧为输入,右侧为输入,电路中有很多的元器件进行连接,如:比较器(输入相等输出 1,输入不相等输入 0)等,以及含有多路复用器 mux2_1,输入信号包括控制信号 s 以及 8 位数字信号 a、b、c,输出信号为 s 对 a、b、c 信号的选择,各个输出端口以及输入端口由导线相连接。

结论:

一个功能的实现需要多重门的处理,Verilog 中简单的代码对应的实际元件内部的结构原理十分复杂。

E) 功能仿真波形

结果分析及结论:

结果分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

当 s=00 或者 11 时,输出 t=a;

当 s=01 时,输出 y=b;当 s=10 时,输出 y=c;

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误

差。

F) 时序仿真波形

结果分析及结论:

结果分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:

1、时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。

2、时序仿真不 仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

G) 时序分析

操作方法是:编译后,在 compilation report 中选择【timing analysis】-【summary】和【tpd】

结果分析及结论:

结果分析:

1、由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 c[7]到 y[7] 的最坏定时情况的 tpd 为 13.711ns。下面的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第五行中 a[2]到 y[2]的 tpd 为 13.132ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

2、8 重 2-1 多路复用器

A)创建工程(选择的芯片为 family=Cyclone II;name=EP2C5T144C8)

B) 编写源代码

module mux2_1(a,b,s,y);

input [7:0]a,b;

input s;

output reg[7:0] y;

always @(*)

begin

if(s==1'b0)y<=a;

else if(s==1'b1)y<=b;

end

endmoduleC) 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

D) RTL 视图

结果分析及结论:

视图分析:

通过观察 RTL 视图可知:左侧为输入,右侧为输入,电路中有很多的元器件进行连接,如:含有多路复用器,输入信号包括控制信号 s 以及 8 位数字信号 a、b,输出信号为 s 对 a、b 信号的选择,各个输出端口以及输入端口由导线相连接。

结论:

一个功能的实现需要多重门的处理,Verilog 中简单的代码对应的实际元件内部的结构原理十分复杂。

E) 功能仿真波形

结果分析及结论:

结果分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

当 s=0 时,输出 t=a;

当 s=1 时,输出 y=b;

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误差。

F) 时序仿真波形

结果分析及结论:

结果分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,又包含了器

件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:

1、时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。

2、时序仿真不 仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

G) 时序分析

结果分析及结论:

结果分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 s 到 y[6] 的最坏定时情况的 tpd 为 15.022ns。下面的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第五行中 b[6]到 y[6]的 tpd 为 13.864ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

3、控制信号产生逻辑

A)创建工程(选择的芯片为 family=Cyclone II;name=EP2C5T144C8)

B) 编写源代码

module con_signal(mova,movb,movd,movc,add,sub,jmp,jg,g,in1,out1,movi,halt,ir,sm,sm_en,ir_ld,ram_re,ram_wr,pc_ld,pc_in,reg_sr,reg_dr,reg_we,s,au_en,au_ac,gf_en,in_en,out_en,mux_s);

input mova,movb,movc,movd,add,sub,jmp,sm,jg,g,in1,out1,movi,halt;

input [7:0]ir;

output reg sm_en,ram_re,ir_ld,pc_in,ram_wr,pc_ld,reg_we,gf_en,in_en,out_en,mux_s,au_en;

output reg [1:0]reg_sr,reg_dr,s;

output reg [3:0]au_ac;

always @(*)beginau_en=mova | movb | add | out1 | sub;sm_en=~halt;ir_ld=~sm;ram_re=(~sm) | movc | movi;ram_wr=movb;gf_en=sub;pc_ld=jmp | (jg & g);pc_in=movi | (~sm);reg_we=movi | mova | movc | movd | sub | add | in1;in_en=in1;reg_dr=ir[3:2];out_en=out1;reg_sr=ir[1:0];if(movb) s=2'b10;else if(movc) s=2'b01;au_ac=ir[7:4];mux_s=mova | movb |movi | add | sub | in1;end

endmoduleC) 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

D) RTL 视图

结果分析及结论:

视图分析:

通过观察 RTL 视图可知:左侧为输入,右侧为输入,电路中有很多的元器件进行连接,如:与或门等,输入信号包括 mova,movb,movc,movd,add,sub,jmp,sm,jg,g,in1,out1,movi,halt 以及指令码 ir,输出信号为 sm_en、ram_re、ir_ld 等图示模型机执行的十六个相应的信号。

结论:

一个功能的实现需要多重门的处理,Verilog 中简单的代码对应的实际元件内部的结构原理十分复杂。

E) 功能仿真波形

结果分析及结论:(以下输出均为高电平有效)

-

指令码 ir 为 10100111 时,au_ac=1010,reg_dr=01,reg_sr=11;

-

mova 指令执行时,sm_en 输出为 1,au_en 输出为 1,mux_s 输出为 1,reg_we 输出为 1;

-

movb 指令执行时,sm_en 输出为 1,ram_wr 输出为 1,au_en 输出为 1,mux_s 输出为 1;

-

movc 指令执行时,sm_en 输出为 1,ram_re 输出为 1,reg_we 输出为 1;

-

movd 指令执行时,sm_en 输出为 1,reg_we 输出为 1;

-

add 指令执行时,sm_en 输出为 1,au_en 输出为 1,mux_s 输出为 1,reg_we 输出为 1;

-

sub 指令执行时,sm_en 输出为 1,au_en 输出为 1,gf_en 输出为 1,mux_s 输出为 1,reg_we输出为 1;

-

jmp 指令执行时,sm_en 输出为 1,pc_ld 输出为 1;

-

sm 指令为 1 时,表示为指令执行阶段,指令可以正常执行;sm 指令为 0 时表示取指阶段,此时 in_pc、ram_re、id_ir、sm_en 输出为 1;

-

jg 指令执行时,sm_en 输出为 1,au_en 输出为 1;

-

当 g 与 jg 指令共同执行时,pc_ld 输出为 1;

-

当 in1 指令执行时,sm_en 输出为 1,in_en 输出为 1,mux_s 输出为 1,reg_we 输出为 1;

-

当 out1 指令执行时,sm_en 输出为 1,au_en、out_en 输出为 1,mux_s 输出为 1,reg_we输出为 1;

-

当 movi 指令执行时,sm_en 输出为 1,pc_in 输出为 1,ram_re 输出为 1,mux_s 输出为1,reg_we 输出为 1;

-

当 halt 指令执行时,sm_en 输出为 0,sm 不反转,无法进行下一轮取指操作,指令机停机。

F) 时序仿真波形

结果分析及结论:

结果分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。结论:

1、时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。

2、时序仿真不 仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

G) 时序分析

结果分析及结论:

结果分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 add 到 mux_s 的最坏定时情况的 tpd 为 13.245ns。下面的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第六行中 mova 到 au_en 的 tpd 为12.731ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

四、思考题

1、任选一条指令,介绍指令的过程、信息流动的情况以及执行时控制信号的值。

答:选择 mova 指令,根据控制信号 SR1、SR0(即指令码 ir 的最后两位)将源寄存器 Rs的数据从通用寄存器 S 口输出,在 AC3~AC0 和 AU_EN 的控制下,经 AU 送入总线BUS,BUS 上的数据传送至通用寄存器的输入端;在 WE 和DR1、DR0 的控制下,时钟下降沿将输入端的数据写入目的寄存器 Rd。执行时sm_en、au_en、mux_s、reg_we 为 1,其他信号为 0。

2、如何产生正确的控制信号以及具体的编程实现?

答:应该去分析每一个控制信号在不同指令输入下的状态,使用逻辑函数进行分析得出最后的表达式,从而在 Quartus 中使用 Verilog 语言实现。

五、实验总结、必得体会及建议

1、从需要掌握的理论、遇到的困难、解决的办法以及经验教训等方面进行总结。

答:本实验需要掌握不同指令输入下各控制信号的状态以及信号在模型机中的流动情况,同时还需要了解模型机各部件的工作原理,在这次实验中我遇上的最大的问题就是不太会使用时序仿真对代码进行模拟,经过老师的耐心解答最终我顺利解决了这个问题并顺利完成了各板块的模拟,在经验教训方面,应该多使用功能仿真去对我们的代码功能进行检验,同时使用时序仿真则可以让我们直观地看见电路实际的输出情况,便于我们深层次的理解。

相关文章:

HNU-2023电路与电子学-实验3

写在前面: 本次实验是完成cpu设计的剩余部分,整体难度比上一次要小,细心完成就能顺利通过全部测评 一、实验目的 1.了解简易模型机的内部结构和工作原理。 2.分析模型机的功能,设计 8 重 3-1 多路复用器。 3.分析模型机的功能…...

html基础语法 看这一篇就够了!

HTML 一 概念 html:html 文件根标签 head:编写页面相关的属性 title:页面标题 body:页面内容展示信息 二 DOM 树: 所有的标签都是 html 的子标签 head 和 body 是兄弟标签,同一级别 head 和 title 为父子标签 1.第一个程序 <html><head>…...

【redis】redis的特性和主要应用场景

文章目录 redis 的特性在内存中存储数据可编程的扩展能力持久化集群高可用快 redis 的应用场景实时数据存储缓存消息队列 redis 的特性 redis 的一些特性(优点)成就了它 在内存中存储数据 In-memory data structures MySQL 主要是通过“表”的方式来…...

部署后端WebSocket服务到AWS云服务器

目录 1.创建AWS账户2.选择EC2实例3.配置EC2实例4.使用VSCode连接到EC2实例5.部署WebSocket服务6.配置域名和SSL(可选)7.监控和维护 1.创建AWS账户 如果你还没有AWS账户,你需要先在AWS官网注册一个。 2.选择EC2实例 登录到AWS管理控制台。搜…...

常见的集合

1、Collection 单列集合的根接口 遍历方法 Collection<String> c new ArrayList<>(); c.add("赵敏"); c.add("小昭"); c.add("素素"); c.add("灭绝"); System.out.println(c); //[赵敏, 小昭, 素素, 灭绝]//1、迭代器遍…...

Swift知识点---RxSwift学习

1. 什么是RxSwift RxSwift是Swift函数响应式编程的一个开源库,由Github的ReactiveX组织开发、维护 RxSwift的目的是:让数据/事件流 和 异步任务能够更方便的序列化处理,能够使用Swift进行响应式编程 RxSwift本质上还是观察者模式ÿ…...

驾驭不断发展的人工智能世界

从很多方面来看,历史似乎正在重演。许多企业正争相采用生成式人工智能 (Gen AI),就像它们争相采用云计算一样,原因也是一样的:效率、成本节约和竞争优势。 然而,与云一样,GenAI 仍是一项发展中的技术&…...

冒泡排序——基于Java的实现

简介 冒泡排序(Bubble Sort)是一种简单的排序算法,适用于小规模数据集。其基本思想是通过重复遍历待排序的数组,比较相邻的元素并交换它们的位置,以此将较大的元素逐步“冒泡”到数组的末尾。算法的名称源于其运行过程…...

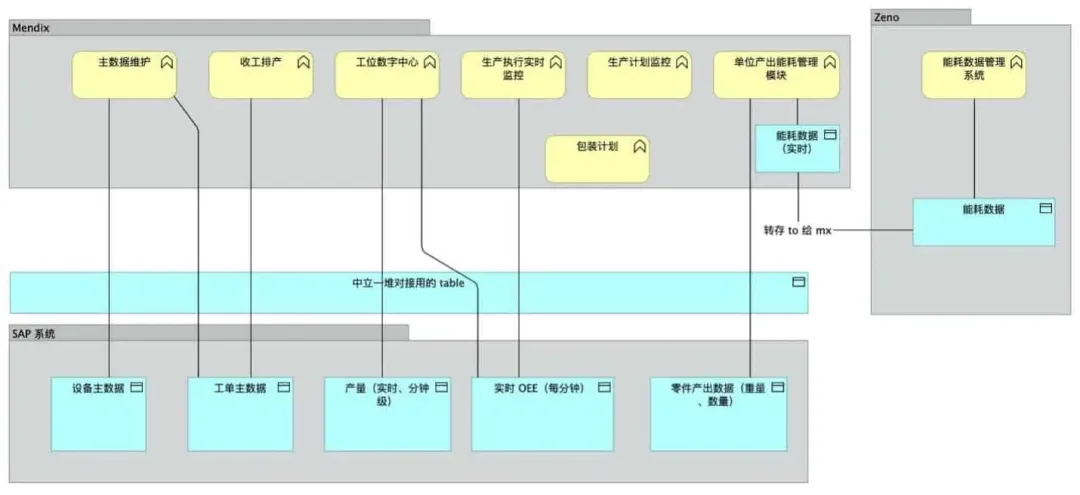

Mendix 创客访谈录|Mendix赋能汽车零部件行业:重塑架构,加速实践与数字化转型

在当前快速发展的技术时代,汽车行业正经历着前所未有的数字化转型。全球领先的汽车零配件制造商面临着如何利用最新的数字技术优化其制造车间管理的挑战。从设备主数据管理到生产执行工单管理,再到实时监控产量及能耗,需要一个灵活、快速且高…...

船舶机械设备5G智能工厂物联数字孪生平台,推进制造业数字化转型

船舶机械设备5G智能工厂物联数字孪生平台,推进制造业数字化转型。在当今数字化浪潮推动下,船舶制造业正经历着前所未有的变革。为了应对市场的快速变化,提升生产效率,降低成本,并增强国际竞争力,船舶机械设…...

什么是jsonp请求

JSONP(JSON with Padding)是一种解决跨域请求问题的技术。它允许网页从不同的域名请求数据,而不受同源策略的限制。JSONP 通过动态创建 script 标签来实现跨域请求,因为 script 标签不受同源策略的限制。 一、工作原理 客户端&a…...

【C++】STL容器详解【上】

目录 一、STL基本概念 二、STL的六大组件 三、string容器常用操作 3.1 string 容器的基本概念 3.2 string 容器常用操作 3.2.1 string 构造函数 3.2.2 string基本赋值操作 3.2.3 string存取字符操作 3.2.4 string拼接字符操作 3.2.5 string查找和替换 3.2.6 string比…...

助贷行业的三大严峻挑战:贷款中介公司转型债务重组业务

大家是否察觉到一种趋势?现如今,众多贷款辅助服务机构与专注于债务再构的公司之间形成了紧密的“联动”。有的选择将获取的贷款需求转介给债务重组方,有的则直接下场,动用自身资本参与债务重组业务。这一现象背后,究竟…...

力扣第42题 接雨水

前言 记录一下刷题历程 力扣第42题 接雨水 接雨水 原题目:给定 n 个非负整数表示每个宽度为 1 的柱子的高度图,计算按此排列的柱子,下雨之后能接多少雨水。 示例 1: 输入:height [0,1,0,2,1,0,1,3,2,1,2,1] 输出&…...

轻松录制每一刻:探索2024年免费高清录屏应用

你不会还在用一些社交工具来录屏吧?现在的市面上有不少免费录屏的软件了。别看如软件是免费的,它的功能比起社交工具的录屏功能来说全面的多。这次我就分享几款我用过的录屏工具。 1.福晰录屏大师 链接直达:https://www.foxitsoftware.cn/R…...

【小沐学OpenGL】Ubuntu环境下glfw的安装和使用

文章目录 1、简介1.1 OpenGL简介1.2 glfw简介 2、安装glfw2.1 直接命令二进制安装2.2 源码安装 3、测试glfw3.1 测试1,glfwglew3.2 测试2,glfwglad3.3 测试3 结语 1、简介 1.1 OpenGL简介 OpenGL作为图形界的工业标准,其仅仅定义了一组2D和…...

[数据集][目标检测]汽油检泄漏检测数据集VOC+YOLO格式237张2类别

数据集格式:Pascal VOC格式YOLO格式(不包含分割路径的txt文件,仅仅包含jpg图片以及对应的VOC格式xml文件和yolo格式txt文件) 图片数量(jpg文件个数):237 标注数量(xml文件个数):237 标注数量(txt文件个数):237 标注类别…...

图文解析保姆级教程:Postman专业接口测试工具的安装和基本使用

文章目录 1. 引入2. 介绍3. 安装4. 使用 此教程摘选自我的笔记:黑马JavaWeb开发笔记16——请求(postman、简单参数、实体参数、RequestParam映射)想要详细了解更多有关请求各种参数介绍的知识可以移步此篇笔记。 1. 引入 在当前最为主流的开…...

jenkins配置流水线

新建任务,随便选一个名字,选中流水线 配置git的用户名和密码,记录ID,后面配置流水线的时候用。 pipeline {agent anystages {stage(stop app){steps {script {def remote [:]//配置服务地址,用户名和密码remote.na…...

SQL 编程基础

SQL(结构化查询语言)广泛应用于数据库操作,是每个程序员都需要掌握的技能之一。这篇文章将带你从基础入门,了解SQL编程中的常量、变量及流程控制语句。我们将采用简单易懂的语言,结合实际示例,帮助你轻松理…...

Wan2.2-T2V-A5B保姆级使用指南:手把手教你用文字秒出创意视频

Wan2.2-T2V-A5B保姆级使用指南:手把手教你用文字秒出创意视频 1. 为什么选择Wan2.2-T2V-A5B? 在短视频内容爆炸式增长的今天,快速将创意转化为视频内容已经成为刚需。Wan2.2-T2V-A5B正是为解决这一需求而生的轻量级文本到视频生成模型。 这…...

微信小程序语音交互实战:长按录制与点击播放的完整实现方案

1. 微信小程序语音交互功能概述 语音交互已经成为现代移动应用不可或缺的功能之一。在微信小程序中实现语音录制与播放,能够极大提升用户体验,特别适合社交、教育、工具类小程序。我最近在一个社交类小程序项目中实现了完整的语音交互模块,踩…...

pvr.iptvsimple技术解构:IPTV直播系统构建的底层逻辑与实践指南

pvr.iptvsimple技术解构:IPTV直播系统构建的底层逻辑与实践指南 【免费下载链接】pvr.iptvsimple IPTV Simple client for Kodi PVR 项目地址: https://gitcode.com/gh_mirrors/pv/pvr.iptvsimple 问题定位:IPTV直播系统的技术痛点与架构挑战 IP…...

Dynamic Deep Learning for Li-ion Battery Fault Detection: A Practical Approach with Real-world EV Da

1. 动态深度学习在锂电池故障检测中的核心价值 锂电池作为电动汽车的核心部件,其健康状况直接关系到整车的安全性和可靠性。传统基于阈值的检测方法在面对复杂多变的实际工况时,往往表现不佳。我们团队在实际测试中发现,某品牌车辆在低温环境…...

老旧设备重生:开源工具OpenCore Legacy Patcher让旧Mac焕发新生的终极解决方案

老旧设备重生:开源工具OpenCore Legacy Patcher让旧Mac焕发新生的终极解决方案 【免费下载链接】OpenCore-Legacy-Patcher Experience macOS just like before 项目地址: https://gitcode.com/GitHub_Trending/op/OpenCore-Legacy-Patcher 您是否拥有一台被苹…...

OpCore-Simplify:三步解决黑苹果配置难题的零代码自动化工具

OpCore-Simplify:三步解决黑苹果配置难题的零代码自动化工具 【免费下载链接】OpCore-Simplify A tool designed to simplify the creation of OpenCore EFI 项目地址: https://gitcode.com/GitHub_Trending/op/OpCore-Simplify 问题诊断:黑苹果配…...

QuickSnap:提升三维建模效率的快速对齐工具——三维建模爱好者的精准对齐解决方案

QuickSnap:提升三维建模效率的快速对齐工具——三维建模爱好者的精准对齐解决方案 【免费下载链接】quicksnap Blender addon to quickly snap objects/vertices/points to object origins/vertices/points 项目地址: https://gitcode.com/gh_mirrors/qu/quicksna…...

Metro性能监控终极指南:如何快速分析和优化React Native打包构建过程

Metro性能监控终极指南:如何快速分析和优化React Native打包构建过程 【免费下载链接】metro 🚇 The JavaScript bundler for React Native 项目地址: https://gitcode.com/gh_mirrors/me/metro Metro作为React Native的官方JavaScript打包工具&a…...

ENet核心架构深度解析:从主机管理到对等通信

ENet核心架构深度解析:从主机管理到对等通信 【免费下载链接】enet ENet reliable UDP networking library 项目地址: https://gitcode.com/gh_mirrors/en/enet ENet是一款高性能的可靠UDP网络库,专为实时多人游戏和低延迟应用设计。它通过创新的…...

手把手教你用FUTURE POLICE:会议录音秒变带时间轴字幕

手把手教你用FUTURE POLICE:会议录音秒变带时间轴字幕 1. 为什么需要高精度字幕对齐? 在日常工作中,我们经常遇到这样的场景:重要会议录音需要整理成文字稿,但人工听写耗时耗力;视频剪辑时需要添加字幕&a…...