硬件语言Verilog HDL牛客刷题day05 时序逻辑部分

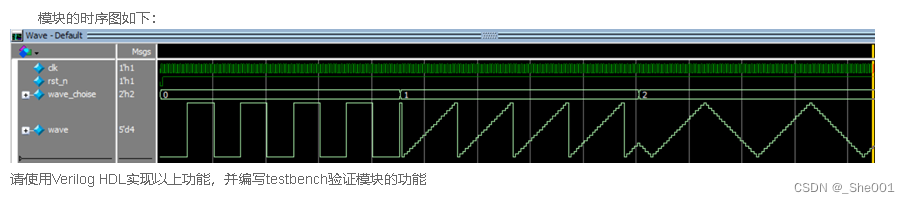

1.VL29 信号发生器

1.题目:

题目描述:

请编写一个信号发生器模块,根据波形选择信号wave_choise发出相应的波形:wave_choice=0时,发出方波信号;wave_choice=1时,发出锯齿波信号;wave_choice=2时,发出三角波信号。

2.解题思路,

2.1 时序逻辑的题目使用状态机。

2.2 三角波模式需要设置一个标志位flag。flag仅在三角波模式也就是wave_chosie==2时工作。当flag==0时,wave减少;当flag==1时,wave增加。

3. 解题代码

`timescale 1ns/1ns

module signal_generator(input clk,input rst_n,input [1:0] wave_choise,output reg [4:0]wave);reg [4:0] cnt;reg flag;// 方波模式下,计数器控制always@(posedge clk or negedge rst_n) beginif(~rst_n)cnt <= 0;elsecnt <= wave_choise!=0 ? 0:cnt ==19? 0:cnt + 1;end// 三角波模式下,标志位控制always@(posedge clk or negedge rst_n) beginif(~rst_n)flag <= 0;elseflag <= wave_choise!=2 ? 0:wave ==1 ? 1:wave ==19? 0:flag;end// 更新wave信号always@(posedge clk or negedge rst_n) beginif(~rst_n) wave <= 0;else case(wave_choise)0 : wave <= cnt == 9? 20 : cnt ==19? 0 :wave;1 : wave <= wave==20? 0 : wave+1;2 : wave <= flag==0 ? wave-1: wave+1;default: wave <= 0;endcaseend

endmodule

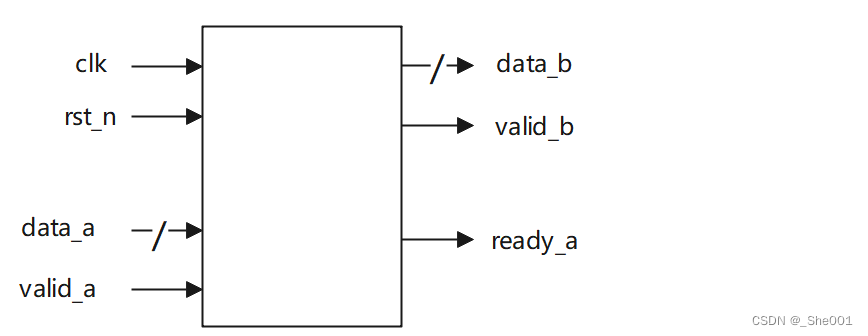

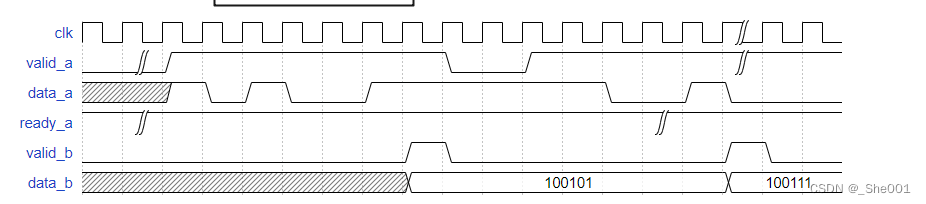

2.VL30 数据串转并电路 (这个容易)

1.题目:

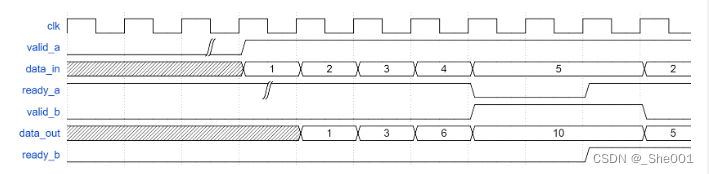

实现串并转换电路,输入端输入单bit数据,每当本模块接收到6个输入数据后,输出端输出拼接后的6bit数据。本模块输入端与上游的采用valid-ready双向握手机制,输出端与下游采用valid-only握手机制。数据拼接时先接收到的数据放到data_b的低位。

电路的接口如下图所示。valid_a用来指示数据输入data_a的有效性,valid_b用来指示数据输出data_b的有效性;ready_a用来指示本模块是否准备好接收上游数据,本模块中一直拉高;clk是时钟信号;rst_n是异步复位信号。

2.解题思路:

2.1注意开始的时候 和复位 的时候 ready_a = 0; 就行。

3.解题代码

`timescale 1ns/1nsmodule s_to_p(input clk , input rst_n ,input valid_a ,input data_a ,output reg ready_a ,output reg valid_b ,output reg [5:0] data_b

);

reg[5:0] data;// Data buffer 数据缓存区

reg[3:0] cnt;// counter 计数器 always@(posedge clk or negedge rst_n)beginif(~rst_n)begindata_b <=6'b0;valid_b <=1'b0;ready_a <=1'b0;cnt <=0;endelsebegin ready_a <=1'b1; if(valid_a == 1'b1)begincnt <= cnt +1;data <= {data_a , data[5:1]};valid_b <= 1'b0;if(cnt == 3'd5)begincnt <=0;data_b <= {data_a,data[5:1]};valid_b <=1'b1;endendendendendmodule3.VL31 数据累加输出

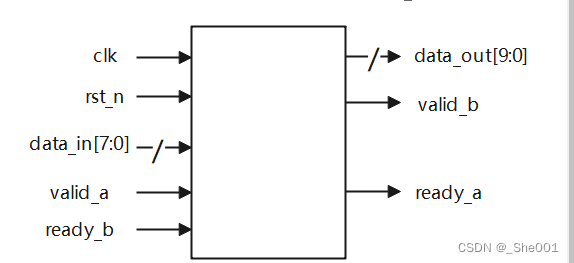

1.题目:

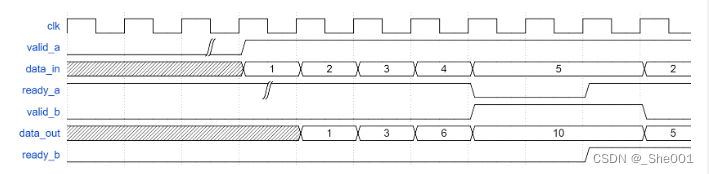

实现串行输入数据累加输出,输入端输入8bit数据,每当模块接收到4个输入数据后,输出端输出4个接收到数据的累加结果。输入端和输出端与上下游的交互采用valid-ready双向握手机制。要求上下游均能满速传输时,数据传输无气泡,不能由于本模块的设计原因产生额外的性能损失。

电路的接口如下图所示。valid_a用来指示数据输入data_in的有效性,valid_b用来指示数据输出data_out的有效性;ready_a用来指示本模块是否准备好接收上游数据,ready_b表示下游是否准备好接收本模块的输出数据;clk是时钟信号;rst_n是异步复位信号。

2.解题思路

2.1 时序逻辑 采用状态机。

2.1 这个题目要注意看细节, 就是计数的条件 和各个 变量 变化的条件。

①ready_a:为高表示我现在没啥事,告诉上游我准备好了,你可以发数据了;

②valid_b:为高表示给下游说我发数据了;

③data_out:给下游发的数据,配合valid_b,只有valid_b为高时,发送的才是有效数据。

那么分别来处理:

①ready_a: 如果下游ready_b拉高,表示下游可以接收模块输出数据,那么此时ready_a应拉高;同时,如果valid_b为低,表示4个数据还没收完,所以也拉高继续接收。

②valid_b: 当和上游正常通讯时(即valid_a和ready_a均为高),数据正常接收,但注意计数了4个就得加起来输出一次,所以data_cnt == 2'd3时拉高valid_b;而等待下游接收,即当ready_a也拉高表示接收完成,则拉低valid_b,保证只有在四个数之和的时候才拉高。

③data_out: 同理,当和上游正常通讯时(即valid_a和ready_a均为高),数据正常接收,数据累加,当计数器data_cnt == 2'd0表示需要从头再加,清零,但注意需要等到ready_b拉高,表示下游接收完成才能清空重新累加。

3.解题代码

`timescale 1ns/1nsmodule valid_ready(input clk , input rst_n ,input [7:0] data_in ,input valid_a ,input ready_b ,output ready_a ,output reg valid_b ,output reg [9:0] data_out

);assign ready_a = ready_b | ~valid_b;reg [1:0] data_cnt;always@(posedge clk or negedge rst_n) beginif(!rst_n)data_cnt <= 2'd0;else if(valid_a && ready_a)data_cnt <= data_cnt +2'd1;elsedata_cnt <= data_cnt;endalways@(posedge clk or negedge rst_n) beginif(!rst_n)valid_b <= 1'b0;else if(valid_a && ready_a && data_cnt == 2'd3)valid_b <= 1'd1;else if(valid_b && ready_b)valid_b <= 1'd0;endalways@(posedge clk or negedge rst_n) beginif(!rst_n)data_out <= 10'b0;else if(valid_a && ready_a && data_cnt == 2'd0 && ready_b) //这里要接收的时候才清零data_out <= data_in; //相当于清零,重新累加else if(valid_a && ready_a)data_out <= data_out + data_in;endendmodule

4.VL32 非整数倍数据位宽转换24to128

1.题目:

实现数据位宽转换电路,实现24bit数据输入转换为128bit数据输出。其中,先到的数据应置于输出的高bit位。

电路的接口如下图所示。valid_in用来指示数据输入data_in的有效性,valid_out用来指示数据输出data_out的有效性;clk是时钟信号;rst_n是异步复位信号。

2.解题思路,

2.1 定义一个可以存储 128 位的寄存器。

2.2列出 计数器 对应的每个信号的位数。 (简单,看得出)

2.3 使用状态机来作, 主要是 15个状态。 因为 24 *16 = 128 *3

3.解题代码

`timescale 1ns/1nsmodule width_24to128(input clk , input rst_n ,input valid_in ,input [23:0] data_in ,output reg valid_out ,output reg [127:0] data_out

);

reg[128:0] data;//data duffer //128 x3 = 24 *16

reg[3:0] cnt;// counter 16个状态always@(posedge clk or negedge rst_n)

beginif(~rst_n)begincnt <=0;data <=0;endelsebeginif(cnt == 4'd0 && valid_in == 1'd1)begincnt <= cnt+1;data <= data_in;endelse if(cnt == 4'd15 && valid_in == 1'd1)begincnt <= 0;data <={data[119:0],data_in};endelse if(valid_in == 1'd1)begincnt <= cnt +1;data <= {data[119:0],data_in};endend

endalways@(posedge clk or negedge rst_n)beginif(~rst_n)beginvalid_out <=0;data_out <=0;endelsebeginif(cnt == 4'd5)begindata_out <= {data[119:0],data_in[23:16]};valid_out <=1;endelse if(cnt == 4'd10)begindata_out <= {data[111:0],data_in[23:8]};valid_out <=1;endelse if(cnt == 4'd15)begindata_out <= {data[103:0],data_in[23:0]};valid_out <=1;endelsebeginvalid_out <=0;data_out <= data_out;endendendendmodule相关文章:

硬件语言Verilog HDL牛客刷题day05 时序逻辑部分

1.VL29 信号发生器 1.题目: 题目描述: 请编写一个信号发生器模块,根据波形选择信号wave_choise发出相应的波形:wave_choice0时,发出方波信号;wave_choice1时,发出锯齿波信号;wave…...

Ajax 入门

前端技术:在浏览器中执行的程序都是前端技术。如 html、css、js 等 后端技术:在服务器中执行的长须,使用 Java 等语言开发的后端程序。servlet,jsp,jdbc,mysql,tomacat 等 全局刷新 使用表单…...

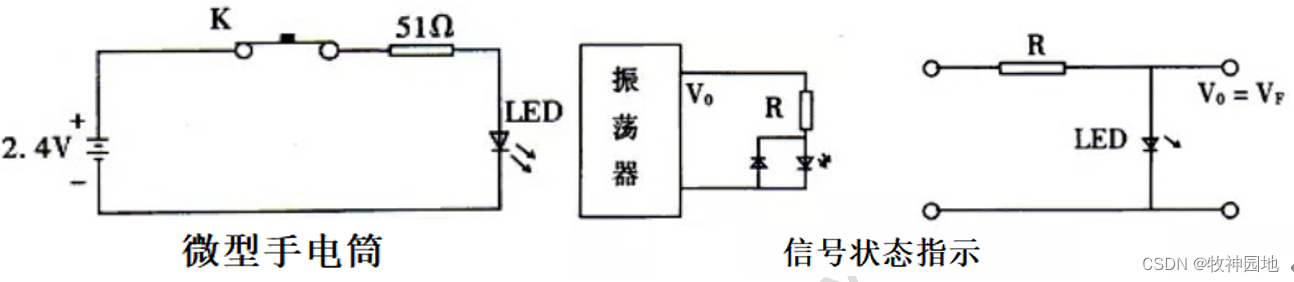

半导体器件基础06:发光二极管

说在开头:关于玻尔原子模型(1) 卢瑟福的模型面临着与经典电磁波理论的矛盾,按照经典电磁波理论,卢瑟福的原子不可能稳定存在超过1秒钟。玻尔面临着选择:要么放弃卢瑟福模型,要么放弃麦克斯韦伟…...

AutoCV第二课:Python基础

目录Python基础前言1.流程控制1.1 条件语句1.2 循环语句1.2.1 while循环语句1.2.2 for循环语句1.3 作业1.4 拓展-try except语法2.函数2.1 函数定义2.2 函数的参数2.2.1 位置参数2.2.2 命名参数2.2.3 默认参数2.2.4 可变参数2.2.5 参数展开2.3 递归函数2.3.1 递归函数定义2.3.2…...

LeetCode算法 打家劫舍 和 打家劫舍II C++

目录题目 打家劫舍参考答案题目 打家劫舍II参考答案题目 打家劫舍 你是一个专业的小偷,计划偷窃沿街的房屋。每间房内都藏有一定的现金,影响你偷窃的唯一制约因素就是相邻的房屋装有相互连通的防盗系统,如果两间相邻的房屋在同一晚上被小偷闯…...

蓝桥杯刷题冲刺 | 倒计时10天

作者:指针不指南吗 专栏:蓝桥杯倒计时冲刺 🐾马上就要蓝桥杯了,最后的这几天尤为重要,不可懈怠哦🐾 文章目录1.有边数限制的最短路2.九进制转十进制1.有边数限制的最短路 题目 链接: 853. 有边数…...

个人练习-Leetcode-剑指 Offer II 109. 开密码锁

题目链接:https://leetcode.cn/problems/zlDJc7/ 题目大意:给出一个四位数字的密码锁,初始状态是0000,目标是targer。每一次转动只能让一个位的轮盘转动一下(0往后转是9)。有一个vector<string> dea…...

四个常见的Linux面试问题

四个常见的Linux面试问题。 刚毕业要找工作了,只要是你找工作就会有面试这个环节,那么在面试环节中,有哪些注意事项值得我的关注呢?特别是专业技术岗位,这样的岗位询问一般都是在职的工程师,如何在面试环节…...

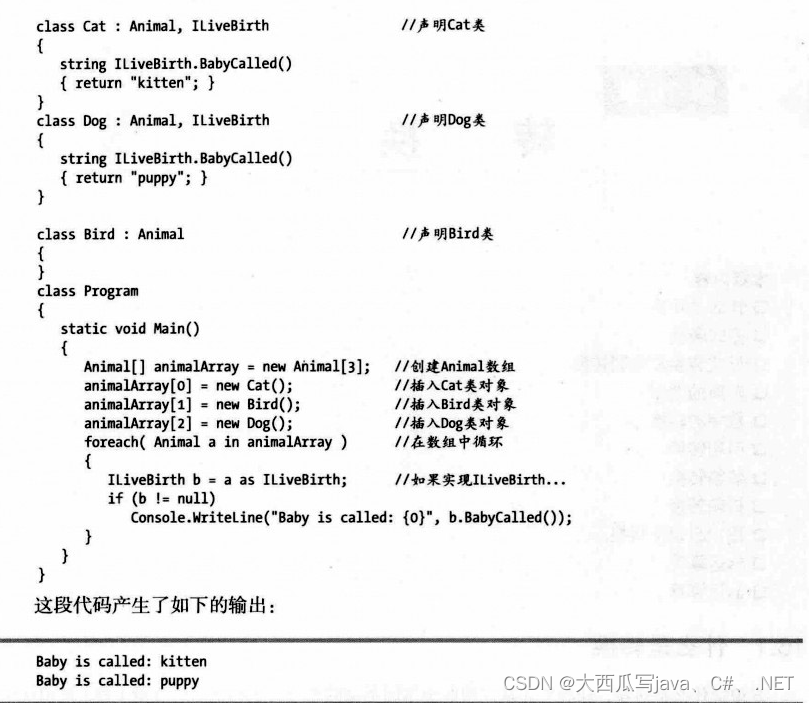

15、接口(C#)

15.1 什么是接口 接口是指定一组函数成员而不实现它们的引用类型。所以只能类和结构实现接口。 15.2 声明接口 接口声明不能包含以下成员 数据成员静态成员 接口声明只能包含以下类型的费静态成员函数声明: 方法事件索引器属性 这些函数成员的声明不能包含任何实…...

)

C++中常见的容器类使用方法举例(vector、deque、map、set)

cpp中常见的容器类有vector、list、deque、map、set、unordered_map和unordered_set。 下面将举例直接说明各个容器的使用方法。 文章目录综合示例1. vector:动态数组,支持随机访问2. list:双向链表,支持双向遍历和插入删除3. de…...

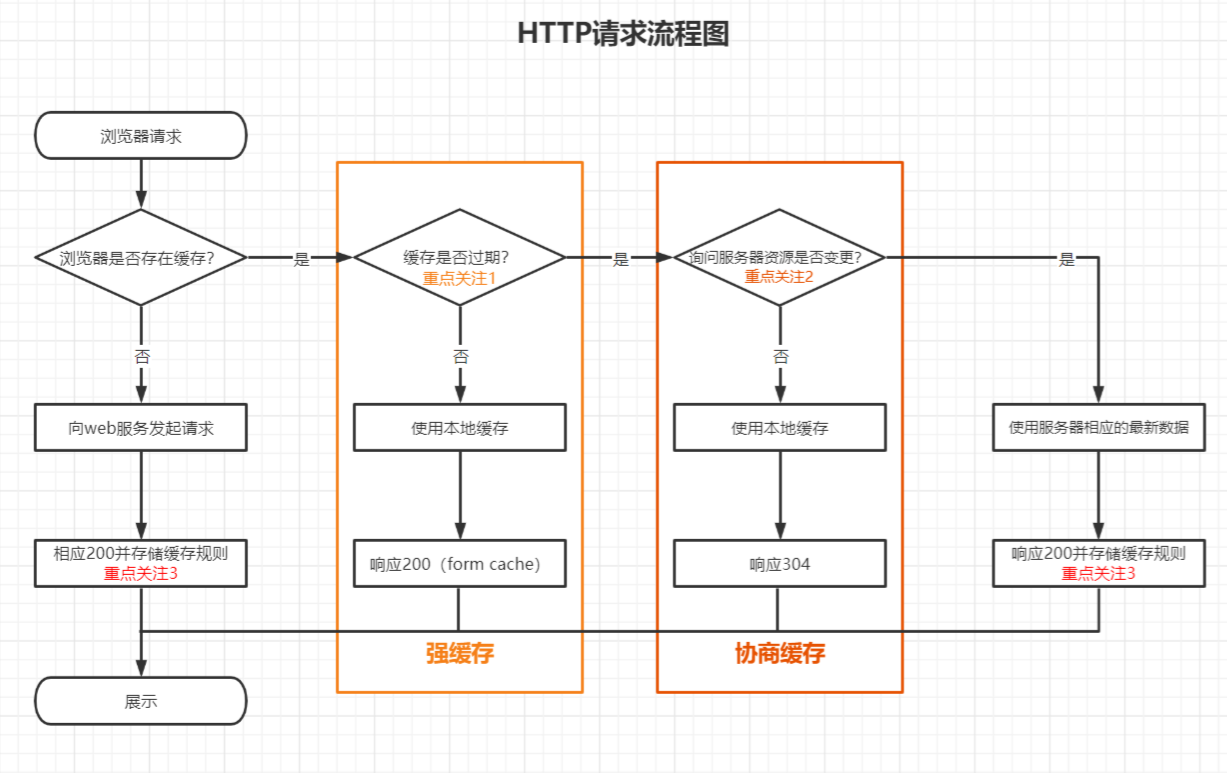

什么是强缓存和协商缓存

什么是缓存 浏览器缓存就是把一个已经请求过的Web资源(如html页面,图片,js,数据等)拷贝一份副本储存在浏览器中。缓存会根据进来的请求保存输出内容的副本。当下一个请求来到的时候,如果是相同的URL&#…...

算法刷题之堆

1. heapq 堆 Python 中只有最小堆: import heapqa [] heapq.heappush(a, 3) # 添加元素 heapq.heappush(a, 2) heapq.heappush(a, 1) while len(a): # 判断堆的长度print(heapq.heappop(a)) # 弹出堆顶元素# 将列表转换为最小堆 nums [2, 3, 1, 4, 5, 6] hea…...

javaweb导师选择系统

本文以JSP为开发技术,实现了一个导师选择系统。导师选择系统分为三大模块,包括管理员:学员信息管理、导师信息管理、导师选择管理、导师分布图、公告信息管理、系统管理,学生:个人资料管理、导师选择管理、导师分布图管…...

LeetCode150 逆波兰表达式求值

题目: 给你一个字符串数组 tokens ,表示一个根据 逆波兰表示法 表示的算术表达式。请你计算该表达式。返回一个表示表达式值的整数。 注意: 有效的算符为 ‘’、‘-’、‘*’ 和 ‘/’ 。每个操作数(运算对象)都可以…...

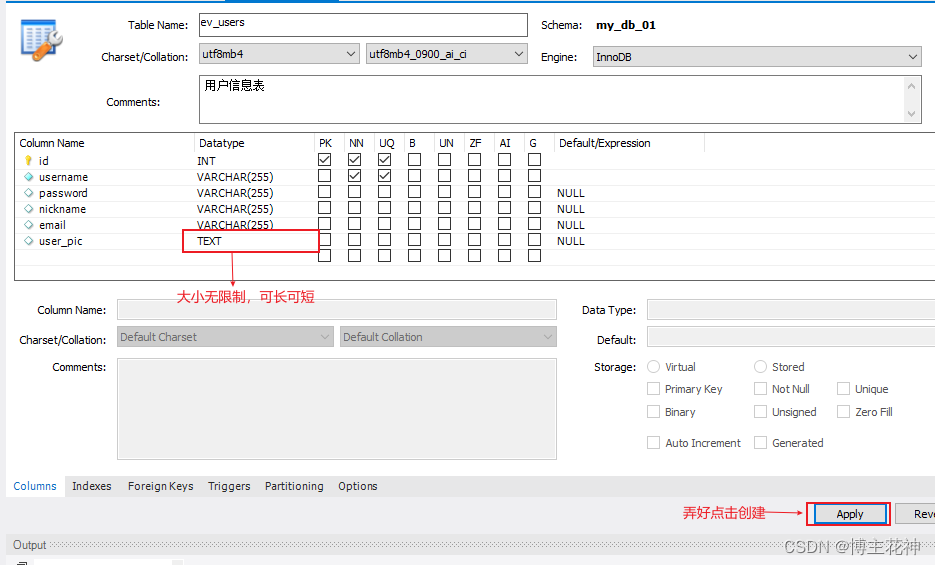

【Node.js】项目开发实战(中)

开发用户的注册和登录接口步骤1,打开MySQL Workbench,打开自己的数据库进入创建用户信息表新建 ev_users表安装并配置mysql模块安装mysql模块新建db文件夹下index.js,导入并配置mysql模块安装bcryptjs对密码进行加密处理新建/router_handler/user.js中&a…...

记录一次 New Bing 英语陪练

记录一次 New Bing 英语陪练 Now I start to speak english to chat with you . Help me find the mistake in my word and help me improve my english I’m glad you want to practice your English with me. I can help you find the mistakes in your words and help you i…...

【Python】照片居然能变素描?不会画画但是咱会代码

文章目录前言一、准备二、下载预训练模型总结前言 Photo-Sketching 一个能将照片的轮廓识别出来并将其转化为“速写”型图像的开源模块。 比如,这只小狗: 经过模型的转化,会变成卡通版的小狗: 非常秀,这很人工智能…...

已解决正确配置git环境变量

已解决git没有配置环境变量,抛出异常ERROR: Cannot find command ‘git’- do you have ‘git’ installed and in your PATH?,附上正确配置git环境变量的教程 文章目录报错问题报错翻译报错原因解决方法《100天精通Python》专栏推荐白嫖80g Python全栈…...

【逐步剖C】-第十章-自定义类型之结构体、枚举、联合

一、结构体 前言:有关结构体的声明、定义、初始化以及结构体的传参等结构体的基本使用在文章【逐步剖C】-第六章-结构体初阶中已进行了详细的介绍,需要的朋友们可以看看。这里主要讲解的是有关结构体的内存问题。 1. 结构体的内存对齐 (1&…...

Windows Server 2016 中文版、英文版下载 (updated Mar 2023)

Windows Server 2016 Version 1607,2023 年 3 月更新 请访问原文链接:https://sysin.org/blog/windows-server-2016/,查看最新版。原创作品,转载请保留出处。 作者主页:sysin.org 本站将不定期发布官方原版风格月度更…...

应用间自动化网关:构建私有化、可编程的跨平台工作流中枢

1. 项目概述与核心价值最近在折腾一些跨平台、跨设备的自动化流程,发现一个痛点:不同应用、不同服务之间的数据流转,经常需要手动“搭桥”。比如,想把手机上的一个链接快速推送到电脑上处理,或者把某个文档从A服务同步…...

终极指南:如何使用Etcher安全快速烧录系统镜像到SD卡和USB驱动器

终极指南:如何使用Etcher安全快速烧录系统镜像到SD卡和USB驱动器 【免费下载链接】etcher Flash OS images to SD cards & USB drives, safely and easily. 项目地址: https://gitcode.com/GitHub_Trending/et/etcher Etcher(BalenaEtcher&am…...

抖音无水印下载神器:3分钟实现高效批量下载的完整指南

抖音无水印下载神器:3分钟实现高效批量下载的完整指南 【免费下载链接】douyin-downloader A practical Douyin downloader for both single-item and profile batch downloads, with progress display, retries, SQLite deduplication, and browser fallback suppo…...

Sonos语音控制功能大揭秘:常用指令、局限与第三方助手对比

ZDNET核心要点Sonos音箱内置语音助手,其语音控制虽不如其他助手智能,但并非一无是处,每日闹钟、天气预报和定时器能提升使用体验。Sonos语音控制使用体验并非智能家居爱好者,但家里有好几台Sonos智能音箱。虽不太喜欢自动语音助手…...

3分钟上手:Windows上直接安装Android应用的最佳工具APK Installer

3分钟上手:Windows上直接安装Android应用的最佳工具APK Installer 【免费下载链接】APK-Installer An Android Application Installer for Windows 项目地址: https://gitcode.com/GitHub_Trending/ap/APK-Installer 还在为复杂的Android模拟器配置而烦恼吗&…...

ComfyUI ControlNet Aux预处理器深度解析:从模型下载到性能优化全攻略

ComfyUI ControlNet Aux预处理器深度解析:从模型下载到性能优化全攻略 【免费下载链接】comfyui_controlnet_aux ComfyUIs ControlNet Auxiliary Preprocessors 项目地址: https://gitcode.com/gh_mirrors/co/comfyui_controlnet_aux ComfyUI ControlNet Aux…...

3分钟掌握跨平台鼠标连点器:免费开源自动化工具快速上手指南

3分钟掌握跨平台鼠标连点器:免费开源自动化工具快速上手指南 【免费下载链接】MouseClick 🖱️ MouseClick 🖱️ 是一款功能强大的鼠标连点器和管理工具,采用 QT Widget 开发 ,具备跨平台兼容性 。软件界面美观 &#…...

Linux小白避坑指南:Resilio Sync安装后权限配置与Web界面访问失败的常见问题解决

Linux权限迷宫:Resilio Sync安装后的深度避坑实战 当8888端口沉默时:一次真实的故障排查记录 上周五晚上11点,我正准备将团队的设计素材库同步到本地开发环境。按照官方文档,我在Ubuntu 22.04上顺利安装了Resilio Sync,…...

如何5步将小爱音箱改造成专属AI语音助手:MiGPT终极指南

如何5步将小爱音箱改造成专属AI语音助手:MiGPT终极指南 【免费下载链接】mi-gpt 🏠 将小爱音箱接入 ChatGPT 和豆包,改造成你的专属语音助手。 项目地址: https://gitcode.com/GitHub_Trending/mi/mi-gpt 你是否曾想过让小爱音箱摆脱&…...

茉莉花插件:终极中文文献管理解决方案,三步搞定Zotero中文文献难题

茉莉花插件:终极中文文献管理解决方案,三步搞定Zotero中文文献难题 【免费下载链接】jasminum A Zotero add-on to retrive CNKI meta data. 一个简单的Zotero 插件,用于识别中文元数据 项目地址: https://gitcode.com/gh_mirrors/ja/jasmi…...