Vivado时序报告七:Report Clock NetworkReport Clock Interaction详解

目录

一、前言

二、Report Clock Network

2.1 Report Clock Network流程

2.2 Report Clock Network报告

三、Report Clock Interaction

3.1 示例设计

3.2 配置选项

3.2.1 Options

3.2.2 Timer_Settings

3.3 Clock Interaction报告

3.3.1 Clock Pair Classification

3.3.2 Inter-clock Constraints

3.3.3 interaction图颜色调整

3.3.4 示例报告解说

一、前言

本文介绍时序报告中关于时钟的两个报告:Report clock network和Report Clock interaction,Report clock network报告主要是以树状结构报告设计中各时钟驱动的load,Report Clock interaction则是报告设计中时钟间的关系,如同步时钟还是异步时钟等,与load无关。

二、Report Clock Network

2.1 Report Clock Network流程

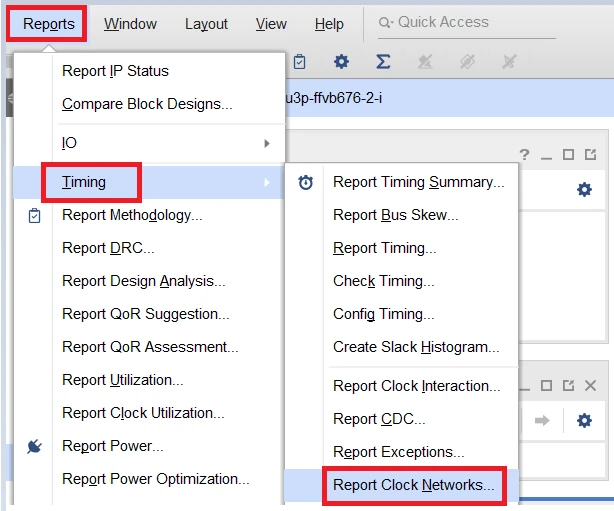

Report Clock Network从菜单栏的“Reports->Timing->Report Clock Networks”进入

报告无特殊的配置项,主要是报告名称的设置

2.2 Report Clock Network报告

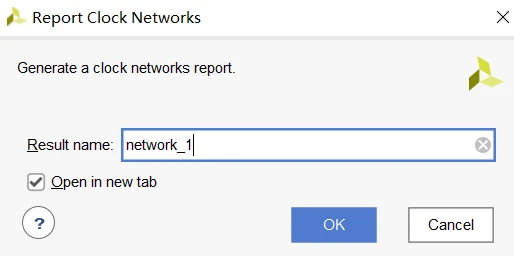

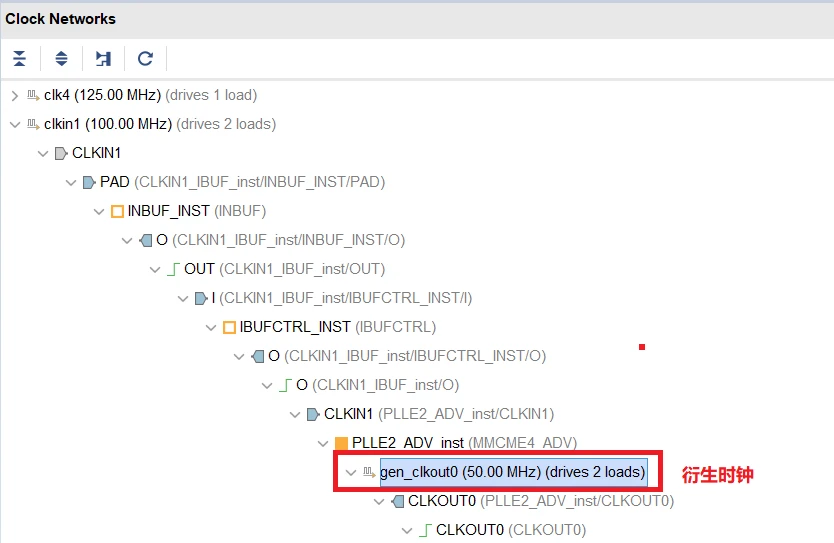

下图是clock network报告,包含了设计中的所有时钟及时钟所驱动的loads

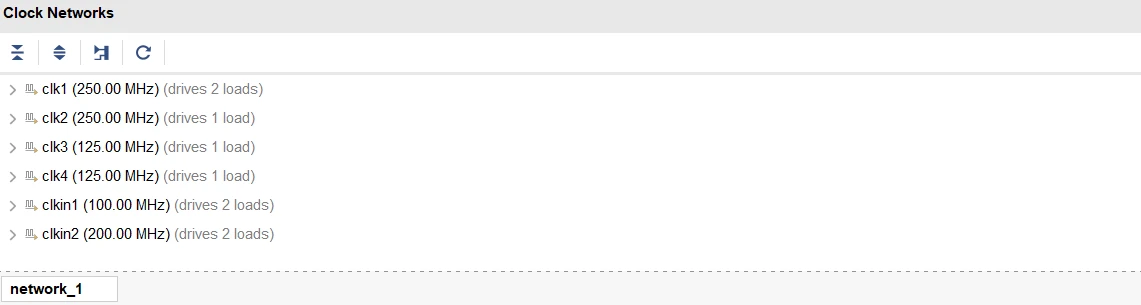

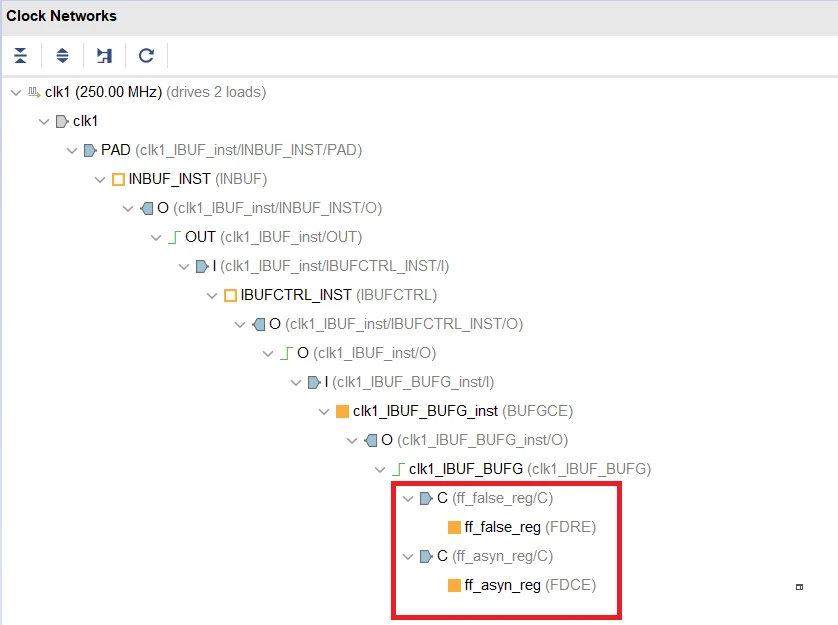

展开后可以查看时钟驱动的具体load单元

对于衍生时钟不会单独显示,统计到主时钟下面

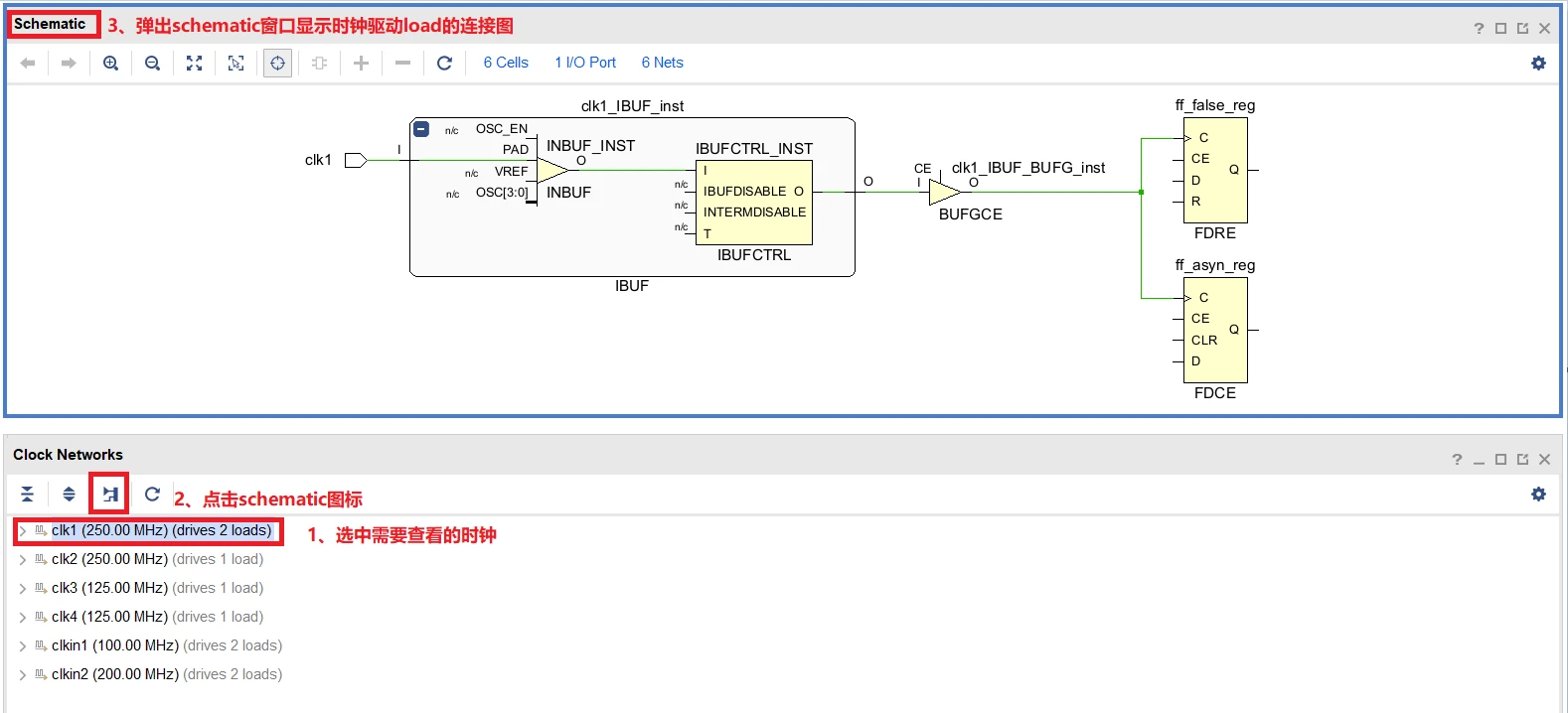

选中时钟后,通过schematic图标或按"F4"或者右键弹出弹框选择"Schematic"可以查看时钟驱动的load连接图

三、Report Clock Interaction

3.1 示例设计

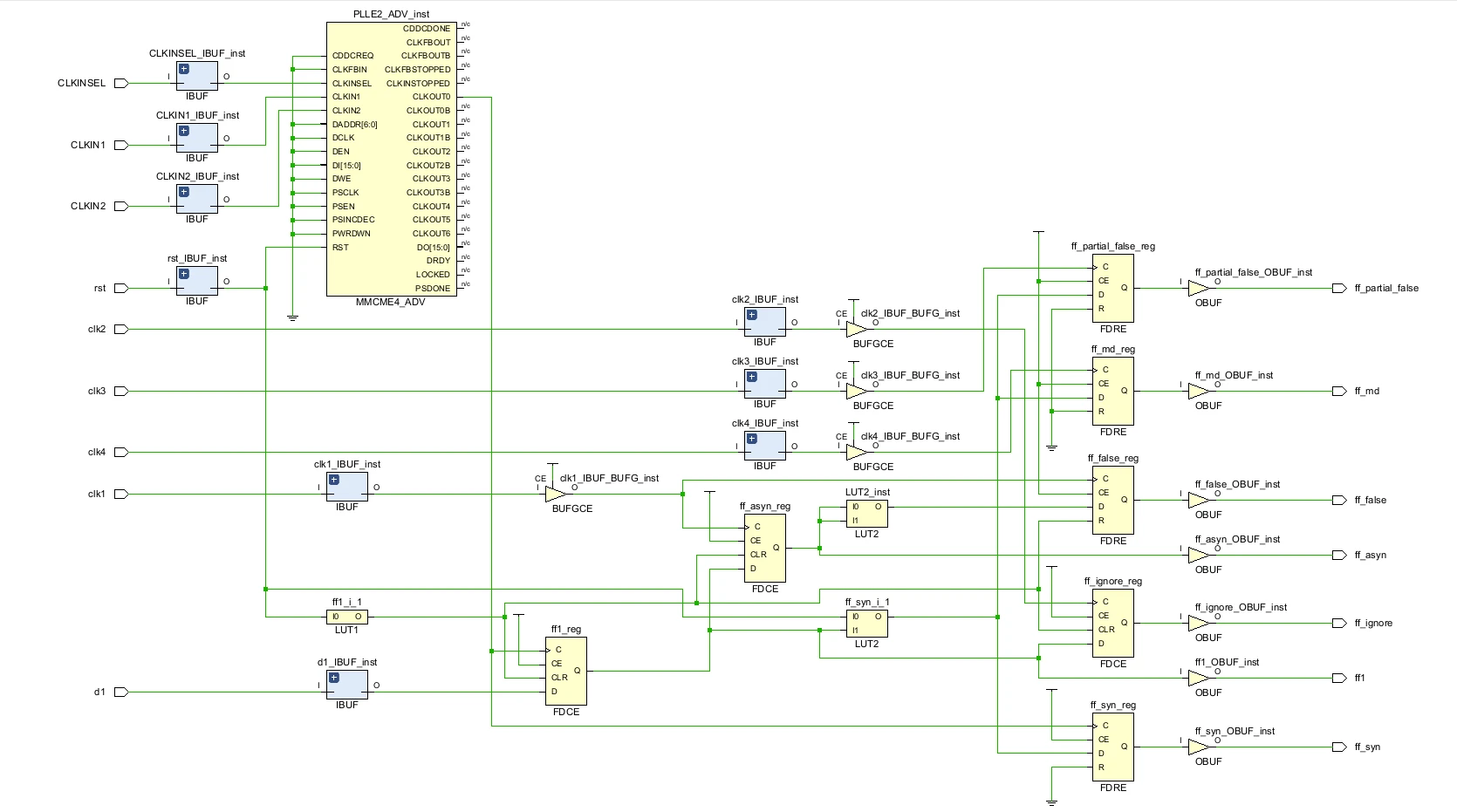

module Report_clock(CLKIN1,CLKIN2,CLKINSEL,clk1,clk2,clk3,clk4,rst,d1,ff1,ff_syn,ff_asyn,ff_md,ff_ignore,ff_false,ff_partial_false);

input CLKIN1,CLKIN2,CLKINSEL,clk1,clk2,clk3,clk4,rst,d1;

output reg ff1,ff_syn,ff_asyn,ff_md,ff_ignore,ff_false,ff_partial_false;

wire o_lut;PLLE2_ADV #(.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT, (2-64).CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB, (-360.000-360.000).// CLKIN_PERIOD: Input clock period in nS to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN1_PERIOD(0.0),.CLKIN2_PERIOD(0.0),// CLKOUT0_DIVIDE - CLKOUT5_DIVIDE: Divide amount for CLKOUT (1-128).CLKOUT0_DIVIDE(1),.CLKOUT1_DIVIDE(2),.CLKOUT2_DIVIDE(4),.CLKOUT3_DIVIDE(5),.COMPENSATION("EXTERNAL"), // ZHOLD, BUF_IN, EXTERNAL, INTERNAL.DIVCLK_DIVIDE(1), // Master division value (1-56)// REF_JITTER: Reference input jitter in UI (0.000-0.999)..STARTUP_WAIT("FALSE") // Delay DONE until PLL Locks, ("TRUE"/"FALSE"))PLLE2_ADV_inst (// Clock Outputs: 1-bit (each) output: User configurable clock outputs.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.RST(rst) // 1-bit input: Reset// Feedback Clocks: 1-bit (each) input: Clock feedback ports);

always@(posedge CLKOUT0,negedge rst)beginif(!rst)ff1<=1'b0;else ff1<=d1;end

always@(posedge CLKOUT0)beginif(!rst)ff_syn<=1'b0;else ff_syn<=ff1;end

always@(posedge clk1,negedge rst)beginif(!rst)ff_asyn<=1'b0;else ff_asyn<=ff1;end

always@(posedge clk4)beginif(!rst)ff_md<=1'b0;else ff_md<=ff1;endalways@(posedge clk2,negedge rst)beginif(!rst)ff_ignore<=1'b0;else ff_ignore<=ff1;endLUT2 #(.INIT(4'h16) // Specify LUT Contents) LUT2_inst (.O(o_lut), // LUT general output.I0(ff_asyn), // LUT input.I1(ff_asyn) // LUT input);

always@(posedge clk1)beginif(!rst)ff_false<=1'b0;else ff_false<=o_lut;end

always@(posedge clk3)beginif(!rst)ff_partial_false<=1'b0;else ff_partial_false<=ff1;end

endmodule 时序约束

create_clock -period 10.000 -name clkin1 -waveform {0.000 5.000} -add [get_ports CLKIN1]

create_clock -period 5.000 -name clkin2 -waveform {0.000 2.500} -add [get_nets CLKIN2]

create_clock -period 4.000 -name clk2 -waveform {0.000 2.000} -add [get_ports clk2]

create_clock -period 4.000 -name clk1 -waveform {0.000 2.000} -add [get_ports clk1]

create_clock -period 8.000 -name clk3 -waveform {0.000 4.000} [get_ports clk3]

create_clock -period 8.000 -name clk4 -waveform {0.000 4.000} [get_ports clk4]

create_generated_clock -name gen_clkout0 -source [get_ports CLKIN1] -divide_by 2 -add -master_clock clkin1 [get_pins PLLE2_ADV_inst/CLKOUT0]

set_clock_groups -name clk2_grp -asynchronous -group [get_clocks clk2]

set_max_delay -datapath_only -from [get_cells ff1_reg] -to [get_cells ff_md_reg] 2.000

set_false_path -hold -from [get_cells ff1_reg] -to [get_cells ff_partial_false_reg]

set_false_path -from [get_cells ff_asyn_reg] -through [get_pins LUT2_inst/I1] -to [get_cells ff_false_reg]schematic图,总的结构是pll->ff->各种interaction下的ff

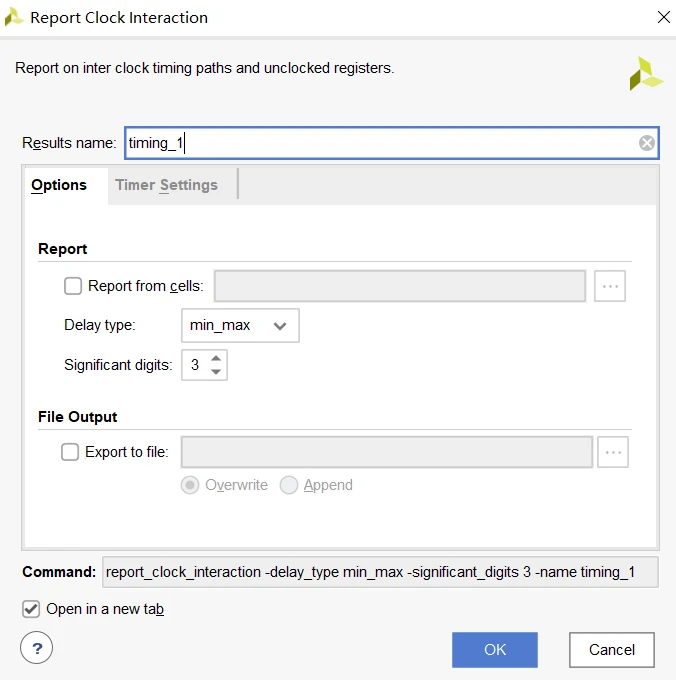

3.2 配置选项

3.2.1 Options

Report from cells: 指定对特定的cells单元进行分析,报告只包含与该单元有关的时序

Delay type: 设置运行分析的类型,可设为min,max,min_max,综合阶段和实现阶段默认max和min都会分析,如果选择min,则只进行hold和removal分析

Significant digits:控制报告中数字显示的精度,默认是3位小数

Export to file:默认的时序报告结果是写入时序窗口中,可以指定导出到指定的文件,写入时可以指定时覆盖overwrite或追加append写入

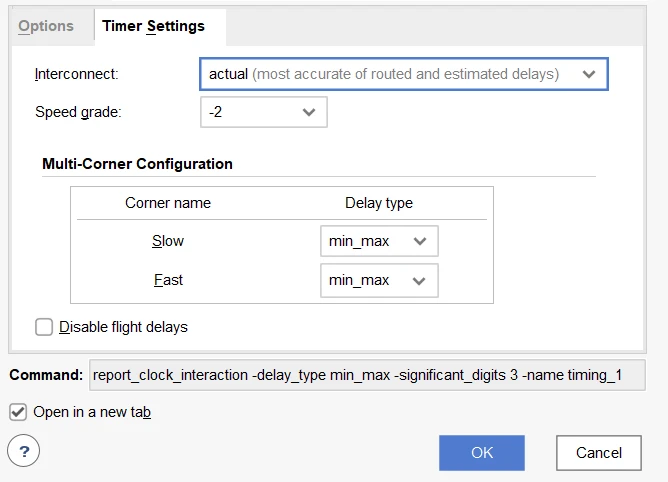

3.2.2 Timer_Settings

Interconnect:用于控制net的时延值的计算方式,可以是评估的cell间的布线距离,实际的布线或者时序分析时移除net的时延。默认情况下,综合后阶段是用估算的net延时值,实现阶段后是用实际的net时延。可以设置值:actual,estimated,none

Speed grade:设置器件的速度等级,通常情况下该值和工程创建时设置的速度一致,也可以不需要重新运行综合和实现,直接改变速度等级进行时序分析,等效的tcl命令为 set_speed_grade

Multi-corner configuration:指定fast/slow corner(可以理解为芯片运行的外部环境的好坏)下分析的路径时延类型,可以为none,min,max,min_max

Disable flight delays:勾选后时序分析不会考虑I/O端口的封装时延

3.3 Clock Interaction报告

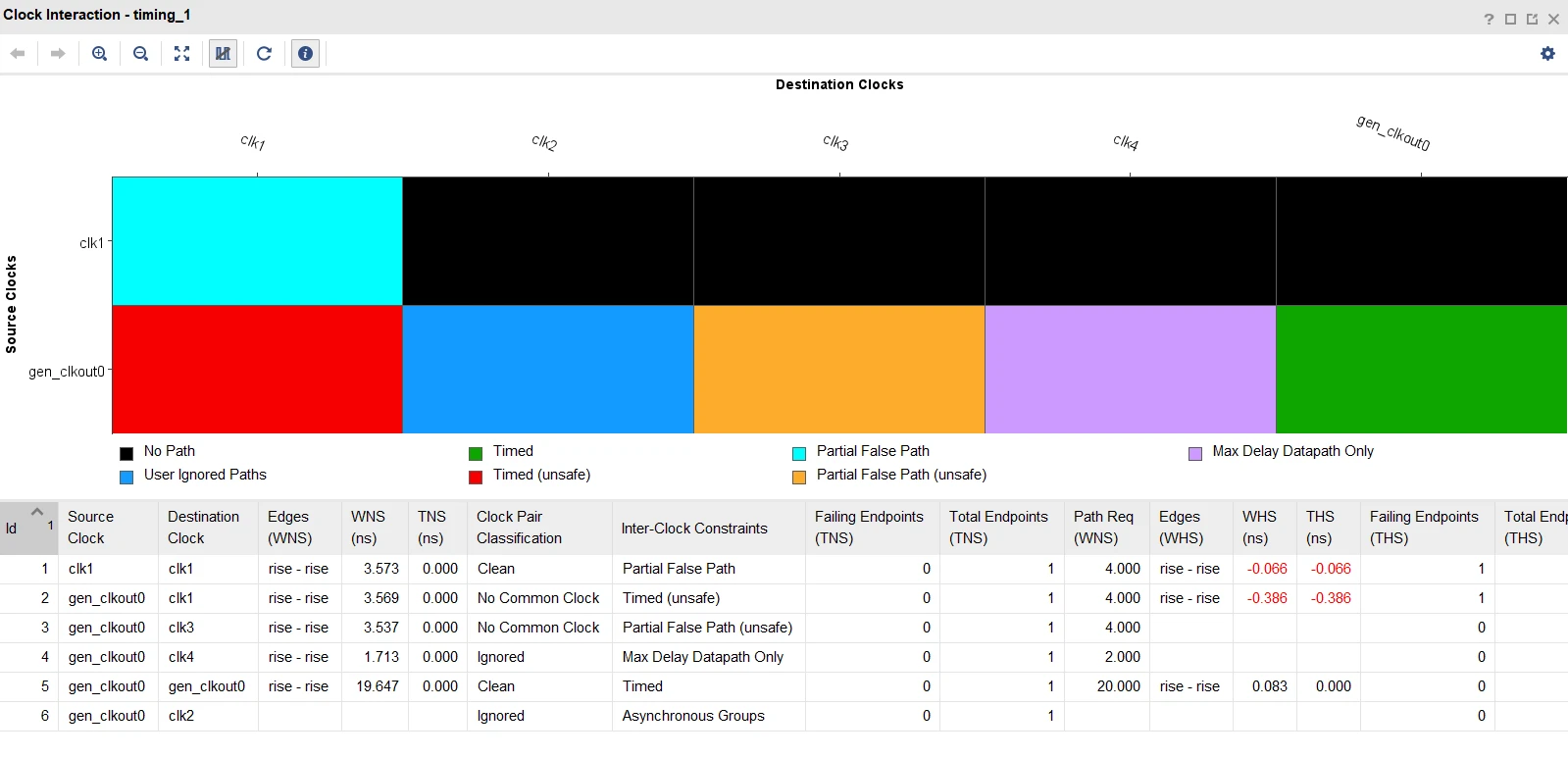

下图是上述设计默认配置下的interaction报告,覆盖率时钟interaction中的七种关系,横坐标为destination clock,纵坐标为source clock

对于报告主要解释几列关键的内容

Source clock:源时钟,时序路径的起点,也是launch时钟

Destination clock:目的时钟,时序路径的终点,也是capture clock

WNS(Worst Negative Slack):一对时钟组中最差时序的slack值,

TNS(Total Negative Slack):一对时钟组中所有slack为负的总和,如示例中gen_clkout0到clk3为0说明对应时钟路径都满足时序要求。

3.3.1 Clock Pair Classification

Clock Pair Classification时钟组分类提供有关两个时钟之间缺少公共主时钟、缺少公共节点、缺少公共相位以及缺少公共周期的信息, 以及是否有虚拟时钟。

下面从优先级最高到最低的顺序列出了可能的值,一旦检测到符合任一条件, 报告命令就不会执行剩余的检查。

Ignored : 当“Clock Group” (时钟组) 、“False Path” (伪路径) 或“Max Delay Datapath

Only” (仅最大延迟数据路径) 完全覆盖时钟对时, 将不会分析。

Virtual Clock : 至少有一个时钟是虚拟时钟, 并且不适用公共主时钟或公共节点检查。

No Common Clock: 两个时钟没有共同的主时钟。

No Common Period: 两个时钟的周期不可扩展。

Partial Common Node: 两个时钟为同步时钟, 但一小部分交汇路径不具有公共节点, 并且

没有安全的时间。

No Common Node : 两个时钟为同步, 但交汇路径无公共节点。

No Common Phase : 两个时钟没有共同的的相位关系。

Clean: 以上情况均不符合

3.3.2 Inter-clock Constraints

Inter-clock Constraints从时序约束角度来展示两个时钟间的关系

No Path(无路径): 源时钟与目的时钟不存在时序路径, 无需报告,黑色块。

Timed(已定时):源时钟与目的时钟存在同步关系, 并且时序约束正常。 时序分析工具根据 2 个时钟具有共同的主时钟和简单的周期比来判定是否符合此状态,绿色块。

User Ignored Paths(用户忽略的路径): 用户定义的伪路径false path或时钟组clock group 约束覆盖从源时钟到目的时钟的所有路径。当运行interaction报告仅仅是为了进行保持时间分析 (-delay_type min) 并且 set_max_delay -datapath_only 约束已覆盖源时钟和目的时钟, Clock Pair Classification(时钟对分类) 会报告为“ignored”,蓝色块 。

Partial False Path(部分伪路径): 用户定义的伪路径false path约束覆盖从源时钟到目的时钟的部分时序路径, 其中源时钟与目的时钟存在同步关系,浅蓝色。

Timed (Unsafe)已定时(不安全): 源时钟与目标时钟存在异步关系。在此情况下, 不存在公共主时钟, 也不存在可扩展周期 ,红色块。

Partial False Path (Unsafe)部分伪路径(不安全): 此类和Timed (Unsafe)相似, 区别在于从源时钟到目的时钟的至少 1 条路径因false path而被忽略,橙色块。

Max Delay Datapath Only(仅最大延迟数据路径): set_max_delay -datapath_only 约束覆盖从源时钟到目的时钟的所有路径,灰色块。

注意! 矩阵中单元颜色反映了时钟域之间约束的状态, 而不是时钟域之间时序路径最差slack的状态。如绿色块并不表示满足时序, 仅表示跨时钟域的所有时序路径已正确分析, 并且两时钟间具有已知的相位关系。

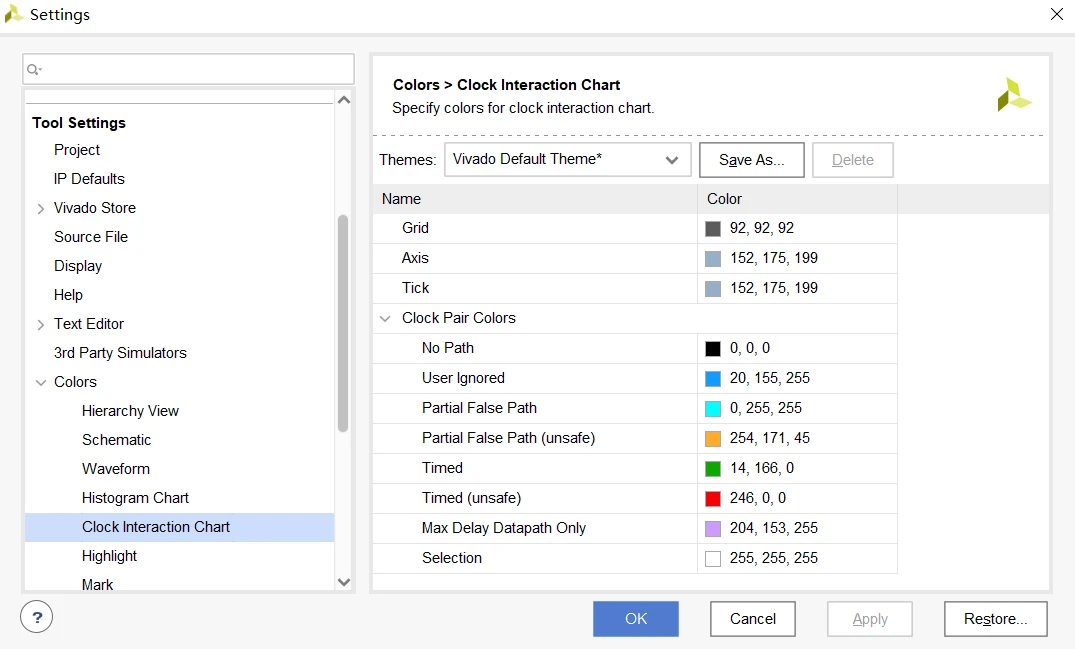

3.3.3 interaction图颜色调整

通过“Tools->Settings->Colors->Clock Interaction Chart”可进入颜色设置界面

3.3.4 示例报告解说

partial false path为ff_asyn_reg到ff_false_reg间存在两条路径,但只对其中的一条设置了set_false_path,对应的约束为

set_false_path -from [get_cells ff_asyn_reg] -through [get_pins LUT2_inst/I1] -to [get_cells ff_false_reg]Time(unsafe)的路径为gen_clkout0到clk1,两者为异步时序路径,无其他时序例外约束

Partial False path(unsafe)为gen_clkout0到clk3,两者为异步时序路径,但设置了set_false_path约束,

set_false_path -hold -from [get_cells ff1_reg] -to [get_cells ff_partial_false_reg]Max Delay Datapath Only为gen_clkout0到clk4,两者间的ff1_reg到ff_md_reg只存在data_path -only约束,约束如下

set_max_delay -datapath_only -from [get_cells ff1_reg] -to [get_cells ff_md_reg] 2.000Timed为gen_clkout0到gen_clkout0,为同步时钟域路径,故时序约束分析正常,无其他时序例外约束

Asynchronous Groups为gen_clkout0到clk2,对clk2设置了clock_group约束,约束如下

set_clock_groups -name clk2_grp -asynchronous -group [get_clocks clk2]相关文章:

Vivado时序报告七:Report Clock NetworkReport Clock Interaction详解

目录 一、前言 二、Report Clock Network 2.1 Report Clock Network流程 2.2 Report Clock Network报告 三、Report Clock Interaction 3.1 示例设计 3.2 配置选项 3.2.1 Options 3.2.2 Timer_Settings 3.3 Clock Interaction报告 3.3.1 Clock Pair Classification …...

HarmonyOS 组件样式@Style 、 @Extend、自定义扩展(AttributeModifier、AttributeUpdater)

1. HarmonyOS Style 、 Extend、自定义扩展(AttributeModifier、AttributeUpdater) Styles装饰器:定义组件重用样式 ;Extend装饰器:定义扩展组件样式 自定义扩展:AttributeModifier、AttributeUpdater 1.1. 区…...

信息安全工程师(73)网络安全风险评估过程

一、确定评估目标 此阶段需要明确评估的范围、目标和要求。评估目标通常包括特定的网络系统、信息系统或网络基础设施,评估范围可能涉及整个组织或仅特定部门。明确评估要求有助于确保评估过程的针对性和有效性。 二、收集信息 在评估开始之前,需要对目标…...

在MacOS玩RPG游戏 - RPGViewerPlus

背景知识 由于我一直使用Mac电脑,所以一直对Mac如何玩RPGMV/RPGMZ游戏的方式有进一步的想法。 网上能给出的方案都是自行启动一个HTTP服务进行,进行服务加载。这个方法有效,但兼容性较差。涉及到自定义功能模块的游戏,都会有报错…...

2024.10.27 直接插入排序 非递归后序遍历(复杂版)

直接插入排序 思路:用temp变量存放需要插入前面有序序列的变量,然后用里面的那个for循环寻找到需要插入的位置。 额外注意的点:arr[j1]temp;这个是因为内置循环每次出来之后所指向的位置是我们要插入的位置的前一个(-1或者插入…...

Ubuntu 22.04系统启动时自动运行ROS2节点

在 Ubuntu 启动时自动运行 ROS2 节点的方法 环境:Ubuntu 系统,ROS2 Humble,使用系统自带的 启动应用程序 目标:在系统启动时自动运行指定的 ROS2 节点 效果展示 系统启动后,自动运行小乌龟节点和键盘控制节点。 实践…...

张三进阶之路 | 基于Spring AOP的Log收集

前情提要 📌 张三对于公司的日志处理系统不满意,认为其性能不佳且功能有限。为了展示自己的能力和技术实力,他决定利用Spring AOP(面向切面编程)开发一个更高效的日志处理系统,并将其存储在Redis中。 首先…...

ubuntu新装ubuntu,重启黑屏

现象:双系统电脑向移动硬盘安装Ubuntu系统后,重启黑屏并显示Minimal BASH-like line editing is supported. For the first word, TAB lists possible command completions. Anywhere else TAB lists possible device or file completions. 又拔下无法启…...

太极安全监控系统0.8

完善后的代码及功能详细介绍 完善后的代码 python import os import sys import subprocess import re import datetime import threading import tkinter as tk from tkinter import messagebox, simpledialog, ttk import scapy.all as scapy import whois import numpy as …...

E-清楚姐姐的布告规划【01背包】

就当一个01背包写就行,只不过需要保证不交叉,w[i]覆盖i点,用一个if来判断即可 #include<bits/stdc.h> #define int long long using namespace std; int w[5005]; int f[5005]; int t,n,m; signed main() {cin>>t;while(t--){…...

哪款宠物空气净化器噪音低?希喂、美的、安德迈测评分享

今年双11,宠物空气净化器到底应该如何选?在所有的家电品类里,宠物空气净化器算是比较特殊的那个,产品迭代太快,我们把今年双11在售的各大主流品牌的宠物空气净化器统一汇总整理,发现基本一多半都是24年下半…...

2024年10月23日第一部分

1.马小民要不要承担责任 2.主动 我就是那种平常沉默寡言孤僻内向自卑又宅又无趣,感觉不管在哪里都是比较边缘不合群的人。6月份遇到一个女生,还是人家主动加的我,断断续续聊了一个月就没下文了,可能我没谈过恋爱吧,快…...

医院信息化与智能化系统(9)

医院信息化与智能化系统(9) 这里只描述对应过程,和可能遇到的问题及解决办法以及对应的参考链接,并不会直接每一步详细配置 如果你想通过文字描述或代码画流程图,可以试试PlantUML,告诉GPT你的文件结构,让他给你对应的…...

逻辑回归与神经网络

从逻辑回归开始学习神经网络 神经网络直观上解释,就是由许多相互连接的圆圈组成的网络模型: 而逻辑回归可以看作是这个网络中的一个圆圈: 圆圈被称为神经元,整个网络被称为神经网络。 本节的任务是我们究竟如何理解具体的一个神…...

隨筆 20241024 Kafka 数据格式解析:批次头与数据体

Kafka作为分布式流处理平台,以其高吞吐量、可扩展性和强大的数据传输能力,成为了现代大数据和实时处理的核心组件之一。在Kafka中,数据的存储和传输遵循一种高效的结构化格式,主要由 批次头(Batch Header)和…...

【WiFi7】 支持wifi7的手机

数据来源 Smartphones with WiFi 7 - list of all latest phones 2024 Motorola Moto X50 Ultra 6.7" 1220x2712 Snapdragon 8s Gen 3 16GB RAM 1024 GB 4500 mAh a/b/g/n/ac/6e/7 Sony Xperia 1 VI 6.5" 1080x2340 Snapdragon 8 Gen 3 12GB RAM 512 G…...

LabVIEW偏振调制激光高精度测距系统

在航空航天、汽车制造、桥梁建筑等先进制造领域,许多大型零件的装配精度要求越来越高,传统的测距方法在面对大尺寸、高精度测量时,难以满足工业应用的要求。绝对测距技术在大尺度测量上往往会因受环境影响大、测距精度低而无法满足需求。基于…...

Python Pandas 数据分析的得力工具:简介

Python Pandas 数据分析的得力工具:简介 在如今的大数据与人工智能时代,数据的收集和处理能力变得至关重要。无论是在科学研究、商业分析还是人工智能领域,如何快速、高效地分析和处理数据都是不可忽视的课题。在众多的数据分析工具中&#…...

Llama 3.2-Vision 多模态大模型本地运行教程

Ollama 刚刚放出了对 Llama 3.2-Vision 的支持!这让人想起了新游戏发布带来的兴奋感——我期待着探索 Ollama 对 Llama 3.2-Vision 的支持。该模型不仅在自然语言理解方面表现出色,而且可以无缝处理图像,最好的部分是什么?它是免费…...

iOS 18.2 可让欧盟用户删除App Store、Safari、信息、相机和照片应用

升级到 iOS 18.2 之后,欧盟的 iPhone 用户可以完全删除一些核心应用程序,包括 App Store、Safari、信息、相机和 Photos 。苹果在 8 月份表示,计划对其在欧盟的数字市场法案合规性进行更多修改,其中一项更新包括欧盟用户删除系统应…...

保姆级排错:Keil里J-Link选项神秘消失?手把手教你定位GD32E23等ARM-M23内核芯片的调试器兼容问题

当Keil调试器选项消失时:深度解析ARM-M23内核芯片的调试兼容性问题 第一次在Keil的Debug配置界面发现J-Link选项神秘消失时,我盯着屏幕愣了几秒钟——前一天明明还能正常使用的工具链,怎么突然就"罢工"了?这种看似"…...

构建可复用技能库:从代码片段到自动化工作流的工程实践

1. 项目概述:从零构建一套可复用的“副爪”技能库在技术社区里,我们常常会看到一些零散的代码片段、脚本工具或者临时的解决方案,它们像散落的“爪子”一样,能解决特定问题,但不成体系,难以复用和传承。我自…...

4sapi 企业级实战:统一模型网关与全生命周期管理解决方案

引言随着大模型技术在企业中的广泛应用,越来越多的企业开始面临 "模型碎片化" 的挑战。不同部门、不同业务线各自对接不同的大模型厂商,使用不同的 API 接口,导致企业内部出现了多个独立的 AI 孤岛,带来了一系列严重的问…...

Agentfiles:统一管理AI编码助手技能文件的Obsidian插件

1. 项目概述:一个为AI编码助手打造的“技能管理中心” 如果你和我一样,同时在使用Claude Code、Cursor、Windsurf这些新一代的AI编码助手,那你一定也面临过同样的困扰:每个工具都有自己的一套“技能”(Skills…...

SteamAutoCrack技术深度解析:架构设计与实现原理揭秘

SteamAutoCrack技术深度解析:架构设计与实现原理揭秘 【免费下载链接】Steam-auto-crack Steam Game Automatic Cracker 项目地址: https://gitcode.com/gh_mirrors/st/Steam-auto-crack SteamAutoCrack是一款基于.NET 10.0框架开发的Steam游戏自动破解工具&…...

Vivado时序约束实战:输入/输出延时设置背后的时序模型与设计考量

1. 时序约束的本质:从理论到实践的桥梁 刚接触FPGA设计时,我最头疼的就是时序约束。那些建立时间、保持时间的概念看得人云里雾里,更别说要在Vivado里实际设置了。直到有一次项目因为时序问题导致整板无法工作,我才真正明白时序约…...

HBase集群启动后秒退?手把手教你排查ZooKeeper路径配置与htrace-core缺失问题

HBase集群启动后秒退?深度排查ZooKeeper路径与依赖缺失问题 当你在深夜部署HBase集群时,看到服务启动后几秒钟内突然消失,那种感觉就像在黑暗中摸索开关。这不是简单的配置错误,而是系统在向你发出求救信号。让我们像侦探一样&…...

VisualCppRedist AIO:一站式高效解决Windows运行库依赖问题

VisualCppRedist AIO:一站式高效解决Windows运行库依赖问题 【免费下载链接】vcredist AIO Repack for latest Microsoft Visual C Redistributable Runtimes 项目地址: https://gitcode.com/gh_mirrors/vc/vcredist VisualCppRedist AIO是一个专门为Windows…...

Ajax技术和Axois工具库

前端如何才能动态展示数据?如何动态获取后端的数据呢? 目录 文章目录 一、什么是Ajax? 二、什么是Axios? 核心用途 三、如何在Vue项目中使用Axios? 1、安装Axios 2、引入Axios 3、基础使用 4、拦截器 5、async/await是什么? 总…...

BUUCTF实战:从内存镜像到加密容器——[VN2020]内存取证全流程解析

1. 初识内存取证:从CTF赛题到实战思维 第一次接触内存取证是在去年的BUUCTF比赛中,当时看到那道[V&N2020]公开赛题目完全摸不着头脑。现在回想起来,内存取证就像是在案发现场收集指纹——只不过我们面对的是计算机运行时留下的"数字…...