VHDL语言基础-Testbech

目录

VHDL仿真概述:

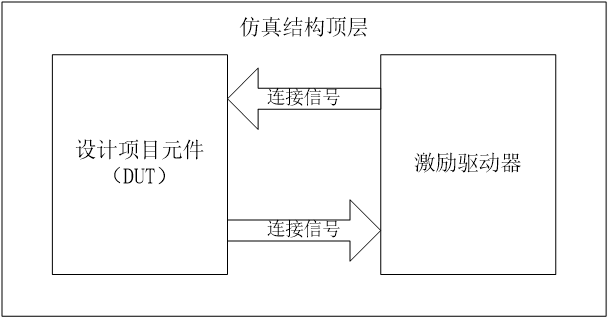

基本结构:

VHDL一般仿真过程:

仿真测试平台文件:

编写测试平台文件的语言:

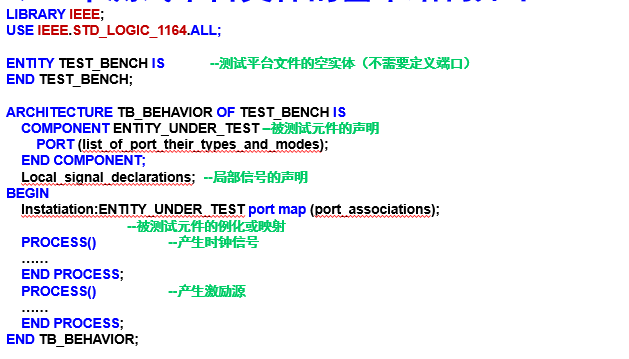

一个测试平台文件的基本结构如下:

测试平台文件包含的基本语句:

产生激励信号的方式:

时钟信号:

复位信号:

周期信性信号:

使用延迟DELAYD:

一般的激励信号:

动态激励信号:

使用测试矢量:

测试平台文件:

定义所测试元件的VHDL程序,该程序是一个简单的Mealy型状态机演示程序:

仿真响应:

控制仿真:

断言语句(ASSERT):

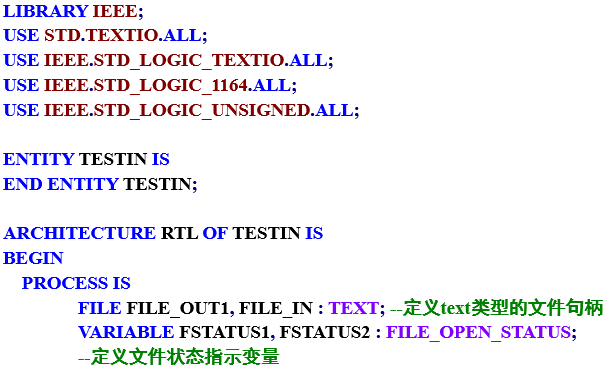

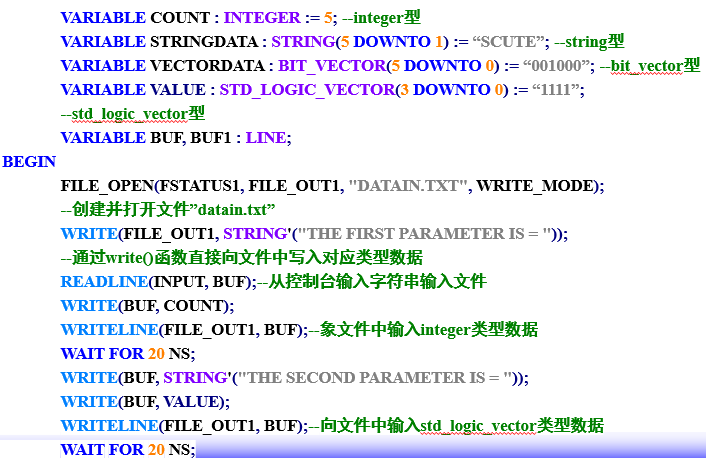

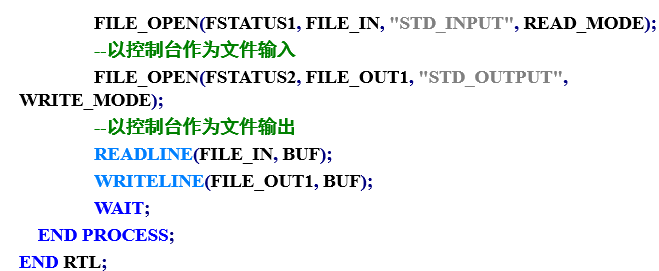

文件I/O的读写:

从文件加载数据或将数据存储到文件中:

定义文件:

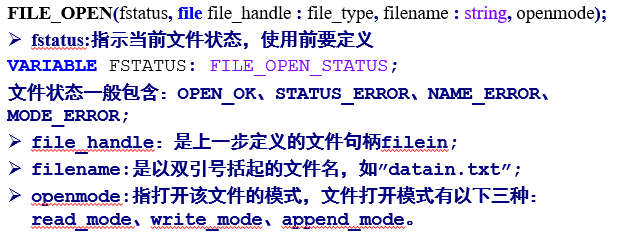

打开文件:

定义文件句柄后就可以在程序中打开指定文件,同时指定打开模式。

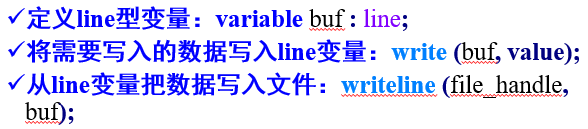

读写文件:

关闭文件:

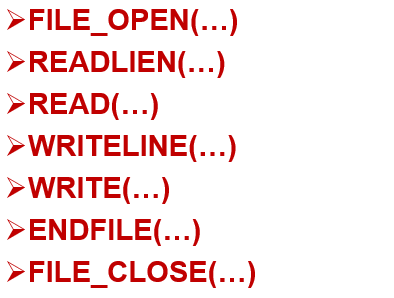

VHDL’93标准包括如下重要的文件I/O操作子程序:

VHDL仿真概述:

VHDL仿真器,如modelsim,需要以下输入

设计的描述(项目的VHDL程序)

驱动设计的激励

在VHDL本身是自激励时则无需此输入

基本结构:

VHDL一般仿真过程:

仿真测试平台文件:

测试平台文件:

定义:可以用来验证所设计的硬件模型的正确性的VHDL模型。

作用:为所测试的原件提供了激励信号,仿真结果可以以波形的方式显示或存储测试结果到文件中。

激励信号:

可以直接集成在测试平台文件中,也可以从外部文件中加载。

编写测试平台文件的语言:

一个测试平台文件的基本结构如下:

测试平台文件包含的基本语句:

实体的定义语句

不需要定义端口,只和被测试元件(DUT)通过内部信号相连接

所测试元件的例化语句

产生时钟信号语句

产生激励源语句

产生激励信号的方式:

以一定的离散时间间隔产生激励信号

基于实体的状态产生激励信号

下面通过实例,讲述激励信号的产生

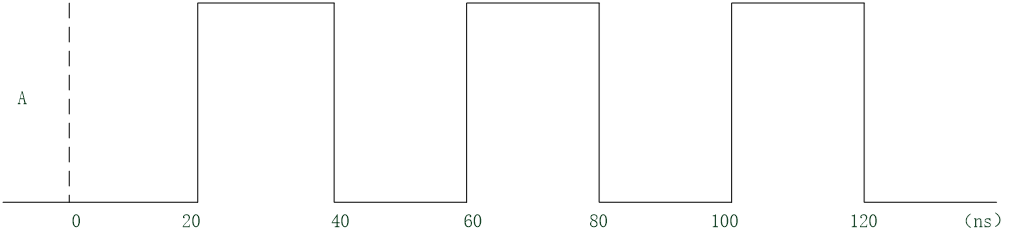

时钟信号:

一个周期性的激励信号可以使用一个并行的信号赋值语句来建立;

例如下面的语句即是建立周期为40ns的信号。

A <= not A after 20 ns; --产生一个周期为40ns的信号A

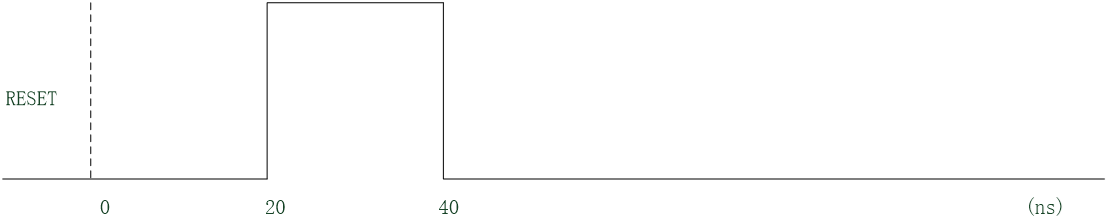

其对应的时钟波形如下图: 时钟信号是同步设计中最重要的信号之一。它既可以使用并行的信号赋值语句产生(如上面的语句),也可以使用时钟产生的进程来实现定义。当使用并行的信号赋值语句时,产生的时钟信号可以是对称的或不对称的,但是信号的初始值不能为‘u’

时钟信号是同步设计中最重要的信号之一。它既可以使用并行的信号赋值语句产生(如上面的语句),也可以使用时钟产生的进程来实现定义。当使用并行的信号赋值语句时,产生的时钟信号可以是对称的或不对称的,但是信号的初始值不能为‘u’

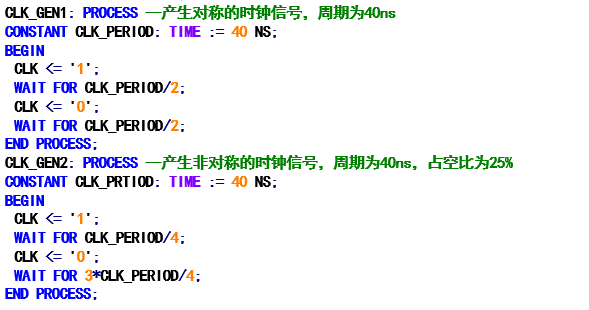

如果使用进程来定义信号,也可以产生各种时钟信号,包括对称和不对称的。在大部分情况下,时钟信号是一直运行的,并且是对称的。当定义不对称的时钟信号,如果使用并行信号幅值语句,则需要使用条件信号赋值语句;如果使用进程,则比较简单,使用顺序逻辑就可以。下面语句使用条件信号赋值语句,定义了一个25%占空比的时钟信号:

W_CLK <= '0' after PERIOD/4 when W_CLK = '1' else

'1' after 3*PERIOD/4 when W_CLK = '0' else

'0';

上述两个对称和不对称的时钟信号,也可以使用进程来定义,如下:

复位信号:

实现方式

使用并行赋值语句

在进程中设定

例如下面复位信号设置:仿真开始时,复位信号为’0’;经过20ns后,复位信号变为’1’;再经过20ns后,复位信号变为’0’。

RESET <= '0', '1' after 20 ns, '0' after 40 ns;

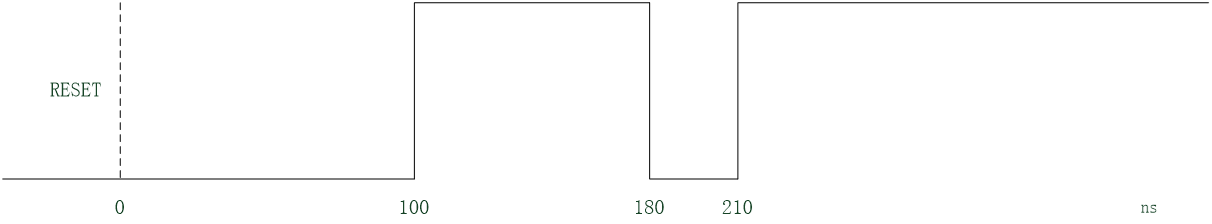

再例如另一个复位信号设置实例,代码如下:

再例如另一个复位信号设置实例,代码如下:

RESET <= '0', '1' after 100 ns, '0' after 180 ns, '1' after 210 ns;

RESET信号初始为’0’,经过100ns后,变为’1’;再经过80ns,该信号变为’0’;再经过30ns,该信号返回到’1’。其波形如下:

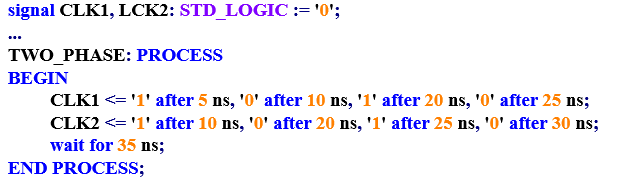

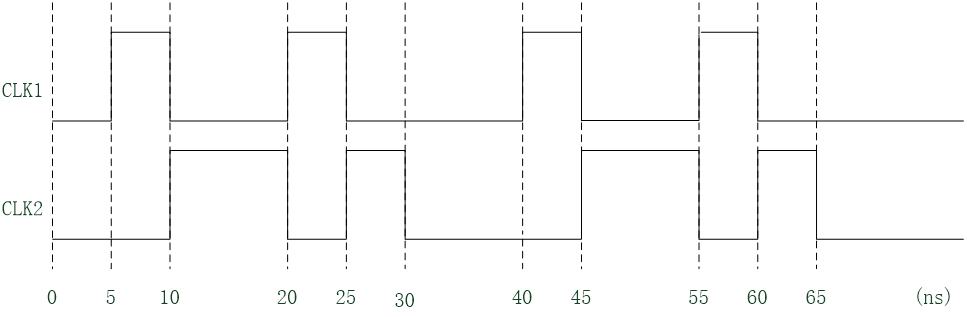

周期信性信号:

可以在进程中使用信号赋值语句实现信号的周期性信号设置。

上例定义了两个周期性信号,为了实现信号的周期性变化,后面使用一个WAIT语句。其波形如下:

使用延迟DELAYD:

可使用预定义属性DELAYD关键词来产生信号。如果已经产生了一个时钟信号,在这个时钟信号的基础上,可以使用DELAYD来使已经产生的时钟信号延迟一定的时间,从而获得另一个时钟信号。

假如我们已经使用如下的语句定义了一个时钟信号W_CLK:

W_CLK <= '1' after 30 ns when W_CLK = '0' else

'0' after 20 ns;

然后可以使用如下的延迟语句获得一个新的时钟信号DLY_W_CLK,它比W_CLK延迟了10ns:

DLY_W_CLK <= W_CLK'DELAYED(10 ns);

以上两个时钟信号波形如下:

一般的激励信号:

所定义的普通的激励信号来用作模型的输入信号;

通常在进程中定义;

一般使用WAIT语句来定义。

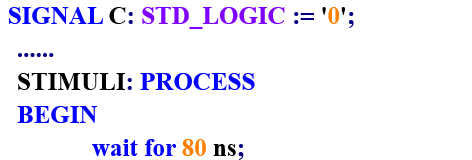

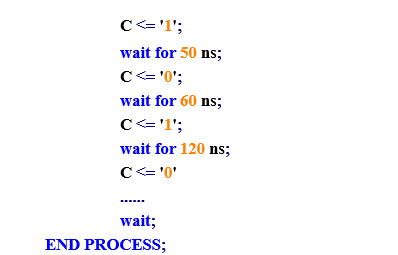

例如下面的激励信号定义:

其波形如下:

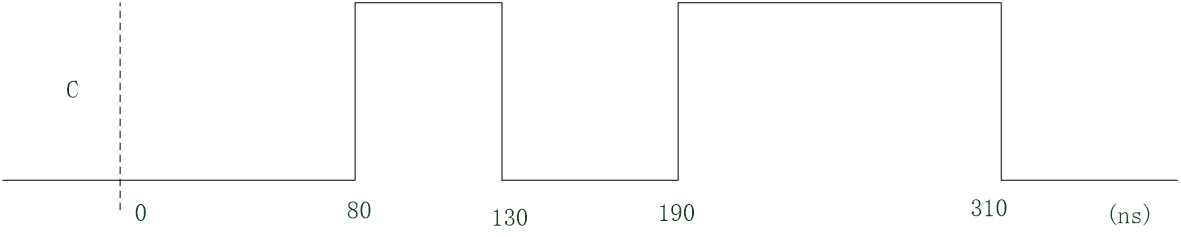

动态激励信号:

动态激励信号,就是被仿真的实体(DUT)的行为模型相关,即DUT的输入激励信号受模型的行为所影响。

如下信号的定义,模型的输入信号Sig_A和模型输出信号Count相关。

使用测试矢量:

将一组固定的输入输出矢量值存储在一个常量表或一个ascii文件中,然后将这些值应用到输入信号从而产生激励信号;

矢量的值序列可以使用多维数组或使用多列记录来描述。

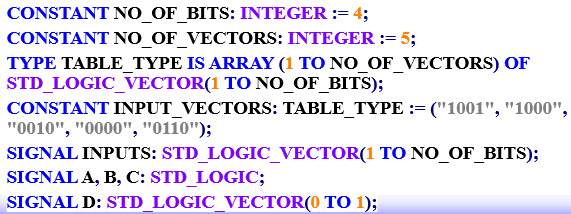

如下面的数据表存储了输入矢量:

假设所测试的实体(DUT)具有4个输入:A、B、C和D信号,如果以一般的时间间隔应用测试矢量,则可以使用一个GENERATE语句,例:

如果将信号应用于任意时间间隔,则需要使用并行的信号赋值语句产生多个信号的波形;使用这种方法可以将一个矢量赋值给多个信号,例如下面的代码:

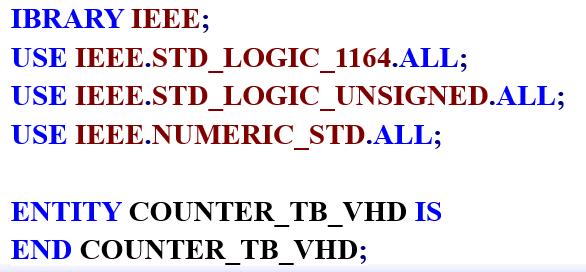

测试平台文件:

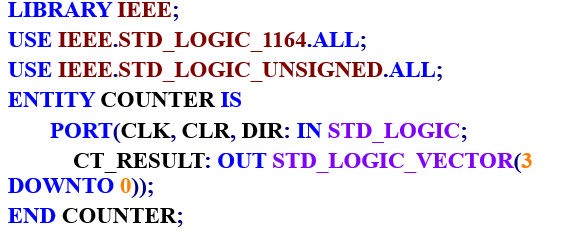

时钟周期为20ns,在一个时钟波形产生进程中定义。激励信号波形在另一个进程中产生。实体为一个空实体,没有输入输出信号端口。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY S_MACHINE_TB IS

END;ARCHITECTURE BHV OF S_MACHINE_TB ISCOMPONENT S_MACHINEPORT (CLK, RESET: IN STD_LOGIC;STARE_INPUTS: IN STD_LOGIC_VECTOR (0 TO 1);COMB_OUTPUTS: OUT STD_LOGIC_VECTOR (0 TO 1));END COMPONENT;--INPUT SIGNALSIGNAL CLK: STD_LOGIC := '0';

SIGNAL RESET: STD_LOGIC := '0';

SIGNAL STARE_INPUTS: STD_LOGIC_VECTOR (0 TO 1) := "00";

--OUTPUT SIGNAL

SIGNAL COMB_OUTPUTS: STD_LOGIC_VECTOR (0 TO 1);--TIMER PERIOD DEFINE

CONSTANT CLK_PERIOD: TIME := 20 NS;

BEGIN--component instantiationDUT:S_MACHINE PORT MAP(CLK=>CLK, RESET=>RESET, STARE_INPUTS=>STARE_INPUTS, COMB_OUTPUTS=>COMB_OUTPUTS);--generate clock signalclk_gen: PROCESSBEGIN

CLK <= '1';WAIT FOR CLK_PERIOD/2;CLK <= '0';WAIT FOR CLK_PERIOD/2;END PROCESS;--drive signalTB: PROCESSBEGINWAIT FOR 20 NS;RESET <= '1';WAIT FOR 20 NS;RESET <= '0';WAIT FOR 210 NS;STARE_INPUTS <= "01";WAIT FOR 20 NS;STARE_INPUTS <= "10"; WAIT FOR 20 NS;

STARE_INPUTS <= "11";WAIT FOR 20 NS;STARE_INPUTS <= "00";WAIT FOR 20 NS;STARE_INPUTS <= "11";WAIT FOR 20 NS;STARE_INPUTS <= "10";WAIT FOR 20 NS;STARE_INPUTS <= "01";WAIT FOR 20 NS;STARE_INPUTS <= "00";WAIT FOR 20 NS;WAIT;END PROCESS; END;定义所测试元件的VHDL程序,该程序是一个简单的Mealy型状态机演示程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY S_MACHINE ISPORT (CLK, RESET: IN STD_LOGIC;STARE_INPUTS: IN STD_LOGIC_VECTOR(0 TO 1);COMB_OUTPUTS: OUT STD_LOGIC_VECTOR(0 TO 1));

END;ARCHITECTURE ART OF S_MACHINE ISTYPE STATES IS (ST0, ST1, ST2, ST3); --define STATES as enumSIGNAL CURRENT_STATE, NEXT_STATE: STATES;BEGIN

REG: PROCESS (RESET, CLK)BEGINIF RESET = '1' THENCURRENT_STATE <= ST0;ELSIF(CLK = '1' AND CLK'EVENT) THENCURRENT_STATE <= NEXT_STATE;END IF;END PROCESS;COM: PROCESS(CURRENT_STATE, STARE_INPUTS) --feedback signalBEGINCASE CURRENT_STATE ISWHEN ST0=>COMB_OUTPUTS<="00";IF STARE_INPUTS="00" THENNEXT_STATE<=ST0;ELSENEXT_STATE<=ST1;END IF;WHEN ST1=>COMB_OUTPUTS<="01";IF STARE_INPUTS = "00" THENNEXT_STATE <= ST1;ELSENEXT_STATE <= ST2;END IF;WHEN ST2=>COMB_OUTPUTS <= "10";IF STARE_INPUTS = "11" THEN

NEXT_STATE <= ST2;ELSENEXT_STATE <= ST3;END IF;WHEN ST3=>COMB_OUTPUTS <= "11";IF STARE_INPUTS = "11" THENNEXT_STATE <= ST3;ELSE NEXT_STATE <= ST0;END IF;END CASE;END PROCESS;END ART;使用以上测试平台文件对元件进行功能仿真,仿真结果如下图:

仿真响应:

控制仿真:

无控制,则仿真会一直持续到时间等于设定的仿真时间;

如果想在某个时间终止仿真,可使用断言语句ASSERT来实现;

另外,ASSERT语句可以实现对某些值或行为作出响应。

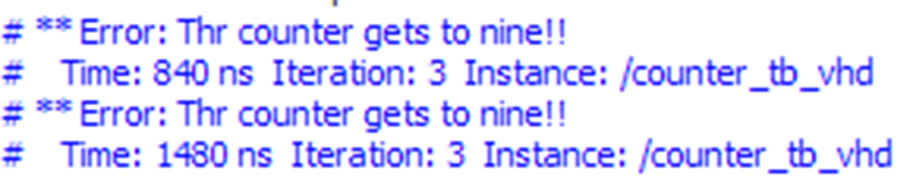

断言语句(ASSERT):

最适合于执行仿真的自动响应;

可以检查一个条件并报告信息;

根据所选择的严重级别和仿真工具的设置,在ASSERT语句报告了信息后,仿真可以继续执行(警告级别WARNING)或者停止(错误ERROR或致命错误FAILURE),默认的严重级别为ERROR

使用断言语句判断仿真的时间,如果当前时间为1000ns,则仿真完成,使用ERROR严重级别终止仿真过程。

断言语句判断条件时,如果条件的判断结果为FALSE,则执行后面的报告及严重级语句,否则仿真会忽略后面的报告和严重级语句并继续执行。

可以使用ASSERT语句设定一个判断条件,以便对仿真的某个结果或值做出响应,例如:

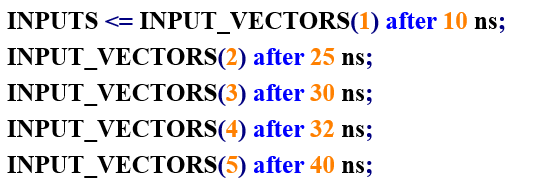

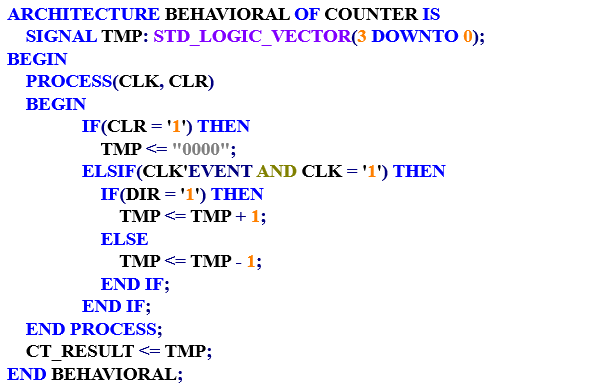

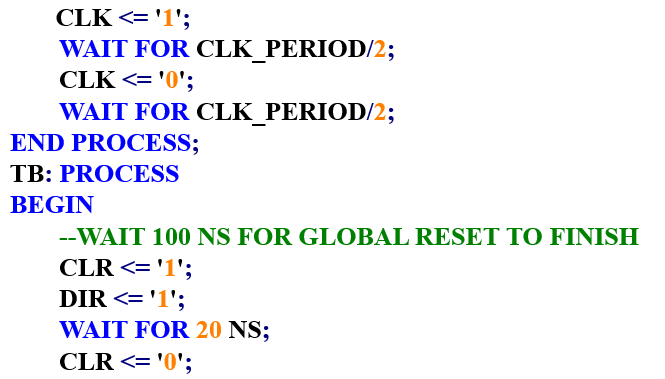

下面的程序为4位计数器的行为模型,计数器的位数为4位。方向由信号DIR决定,如果DIR为高电平,则正向计数,如果DIR为低电平,则反向计数。计数结果保存在CT_RESULT信号中。

下面的程序为测试平台,在程序中,一个断言语句用于判断计数结果是否等于”1001”。条件判断使用了“不等于(/=)逻辑”,如果判断条件为FALSE,即等于“1001”,则报告信息,并终止仿真。

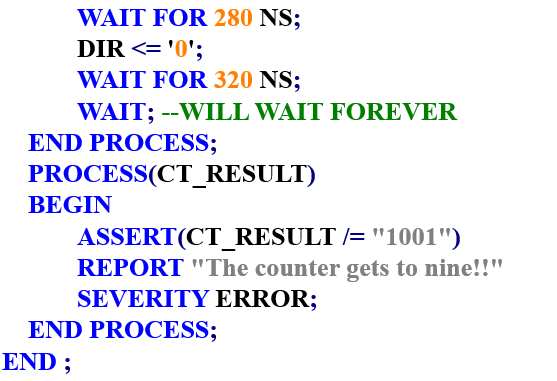

以上测试文件在Modelsim中的仿真波形如下:

当计数到”1001”,在Modelsim的信息栏输出所要报告的信息,如下:

文件I/O的读写:

从文件加载数据或将数据存储到文件中:

例如用户定义的测试矢量可以保存在文件中,然后在仿真时从文件中读取这些测试矢量。

另外,仿真的结果可以保存在文件中。

VHDL’93的文件I/O读写主要是用于仿真,综合工具并不支持文件I/O的读写。

如果想在仿真时进行文件操作,必须包括标准库STD中的TEXTIO定义的程序库,该程序库中包含了文件啊你输入输出所需要的基本子程序(函数和过程)。

定义文件:

文件的两个类型:

Integer:文件中的数据是以二进制存取的,不能被人识别,只有integer型的数据能够存入这列文件。

String:文件是以ascii码形式读取的,可以被人识别;integer、bit_vector(x downto y)、string(x downto 1)、std_logic_vector(x downto o)、bit等都可以被存入此类文件。

定义语法:

FILE FILEIN : TEXT;

TYPE INTEGERFILE IS FILE OF INTEGER;

FILE FILEIN : INTEGERFILE;

打开文件:

定义文件句柄后就可以在程序中打开指定文件,同时指定打开模式。

读写文件:

打开文件后就可以对文件进行读写操作,其语句格式如下:

![]()

使用以上语句只能写入指定类型的数据,如integer类型的只能写入integer型数据。如果写入其他类型需要遵循以下步骤:

关闭文件:

在文件读写完毕后,需使用file_close(file_handle);关闭文件。

ENDFILE(file_handle);判断在文件操作中是否读取到文件的末尾

VHDL’93标准包括如下重要的文件I/O操作子程序:

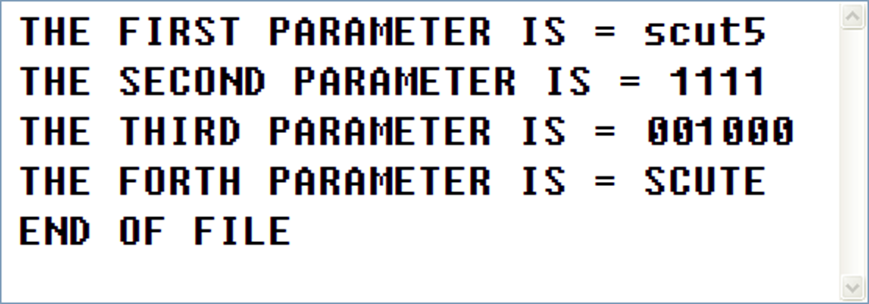

下面举一个例子,使用了上面介绍的各种语法:

h3

modelsim控制台做如下操作:

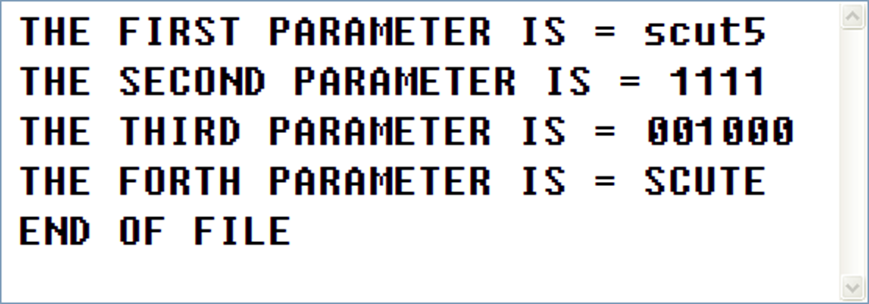

等待数秒后,在modelsim工程目录下将会新建一个”DATAIN.TXT”文本文档,打开文档其内容如下:

相关文章:

VHDL语言基础-Testbech

目录 VHDL仿真概述: 基本结构: VHDL一般仿真过程: 仿真测试平台文件: 编写测试平台文件的语言: 一个测试平台文件的基本结构如下: 测试平台文件包含的基本语句: 产生激励信号的方式: 时钟信号: 复位信号: 周期信性信号: 使用延迟DELAYD: 一般的激励信号…...

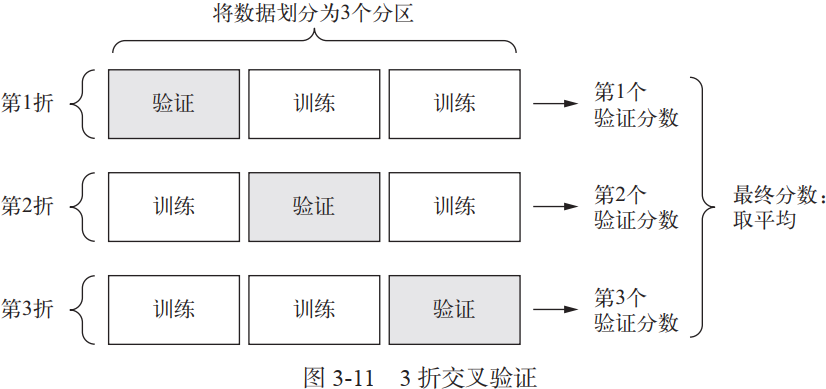

机器学习基础总结

一,机器学习系统分类 机器学习系统分为三个类别,如下图所示: 二,如何处理数据中的缺失值 可以分为以下 2 种情况: 缺失值较多:直接舍弃该列特征,否则可能会带来较大噪声,从而对结果造成不良影…...

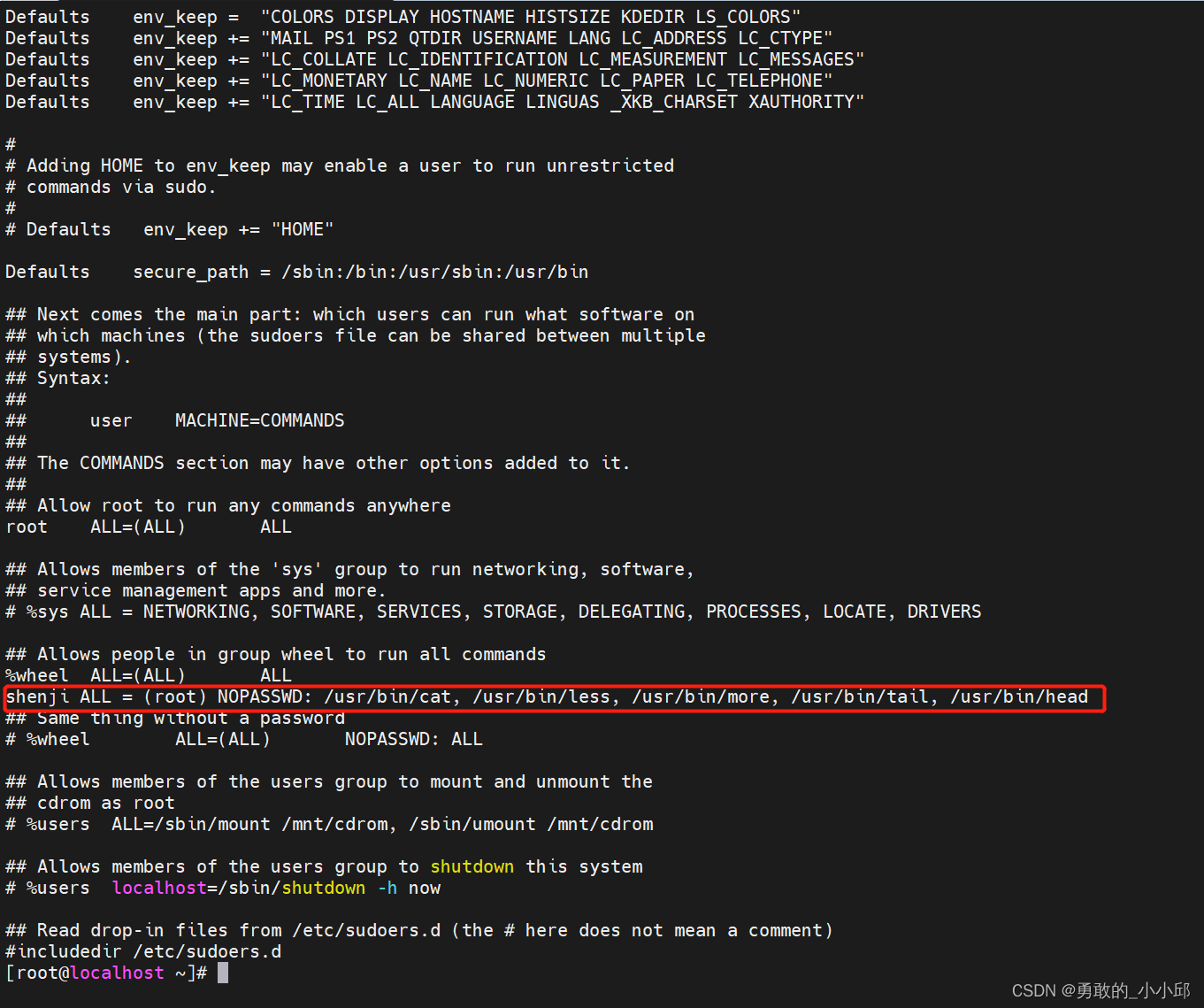

linux的三权分立设计思路和用户创建(安全管理员、系统管理员和审计管理员)

目录 一、三权分立设计思路 1、什么是三权 2、三员及权限的理解 3、三员之三权 4、权限划分 5、“三员”职责 6、“三员”配置要求 二、linux三权分立的用户创建 1、系统管理员 2、安全管理员 3、审计管理员 一、三权分立设计思路 1、什么是三权 三权指的是配置、…...

revit中如何创建有坡度的排水沟及基坑?

一、revit中如何创建有坡度的排水沟? 先分享一张有坡度排水沟的族的照片给大家加深一下印象,有了一个粗略的直观认识,小编就来说说做这个族的前期思路吧。 一、前期思路: 1、 用拼接的方式把这个族形状拼出来,先用放样࿰…...

Web自动化测试——selenium篇(一)

文章目录一、环境准备二、Web 自动化测试 Demo三、元素定位常用方法四、元素定位失败可能原因五、测试对象操作六、等待操作七、信息打印在学习 Web 自动化测试的过程中,selenium 是其中的常用工具。除了其开源免费,包含丰富的 API 以外,它还…...

认识 CSS pointer-events 属性

pointer-events 的基本信息 pointer-events 属性用来控制一个元素能否响应鼠标操作,常用的关键字有 auto 和 none pointer-events: none; // 让一个元素忽略鼠标操作 pointer-events: auto; // 还原浏览器设定的默认行为 规范定义 条目状态初始值auto可用值适用所…...

【java】springboot和springcloud区别

文章目录1、含义不同2、作用不同3、使用方式不同4、特征不同5、注释不同6、优势不同7、组件不同8、设计目的不同1、含义不同 springboot:一个快速开发框架,它简化了传统MVC的XML配置,使配置变得更加方便、简洁。 springcloud:是…...

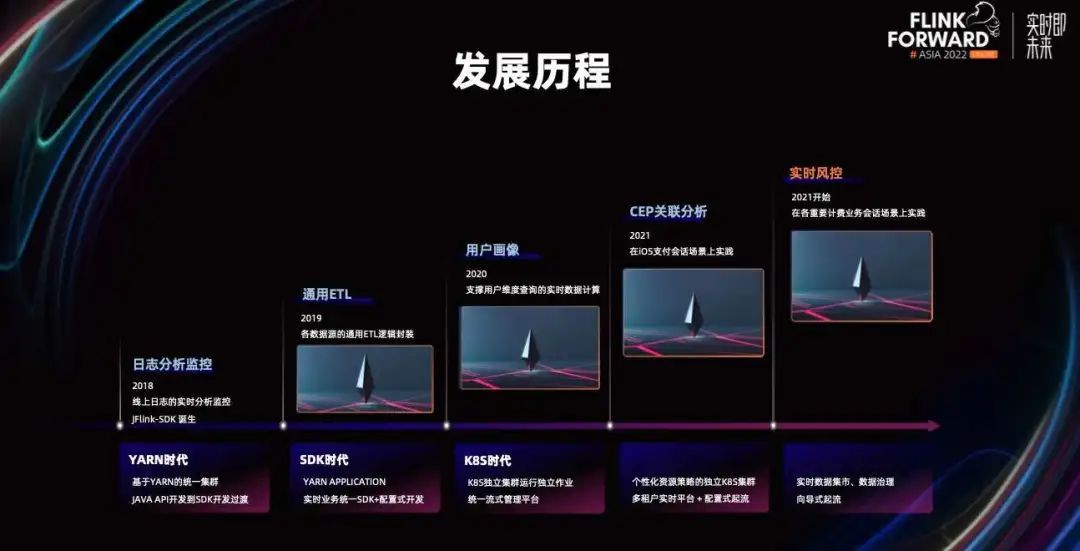

网易游戏实时 HTAP 计费风控平台建设

本文整理自网易互娱资深工程师, Flink Contributor, CDC Contributor 林佳,在 FFA 实时风控专场的分享。本篇内容主要分为五个部分: 实时风控业务会话会话关联的 Flink 实现HTAP 风控平台建设提升风控结果数据能效发展历程与展望未来 众所周知ÿ…...

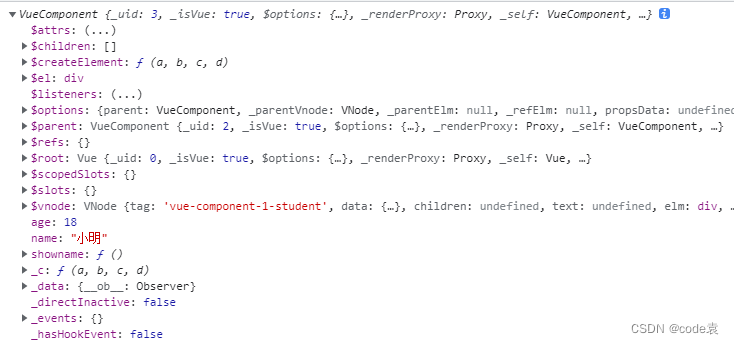

vue组件

文章目录1.vue组件2.非单文件组件2.1组件创建2.2祖册组件2.3使用组件3.组件的嵌套3.1 school组件嵌套student3.2 app组件嵌套school和hellozujain3.3 vm里面引入app组件4.VueCompent5.单文件组件1.vue组件 组件是实现应用中功能的局部代码和资源的集合 2.非单文件组件 2.1组件…...

让mybatis-plus支持null字段全量更新

文章目录背景方案一使用方案二方案二原理介绍背景 如果仅仅只是标题所列的目标,那么mybatis-plus 中可以通过设置 mybatis-plus.global-config.db-config.field-strategyignored 来忽略null判断,达到实体字段为null时也可以更新数据为null 但是一旦使用…...

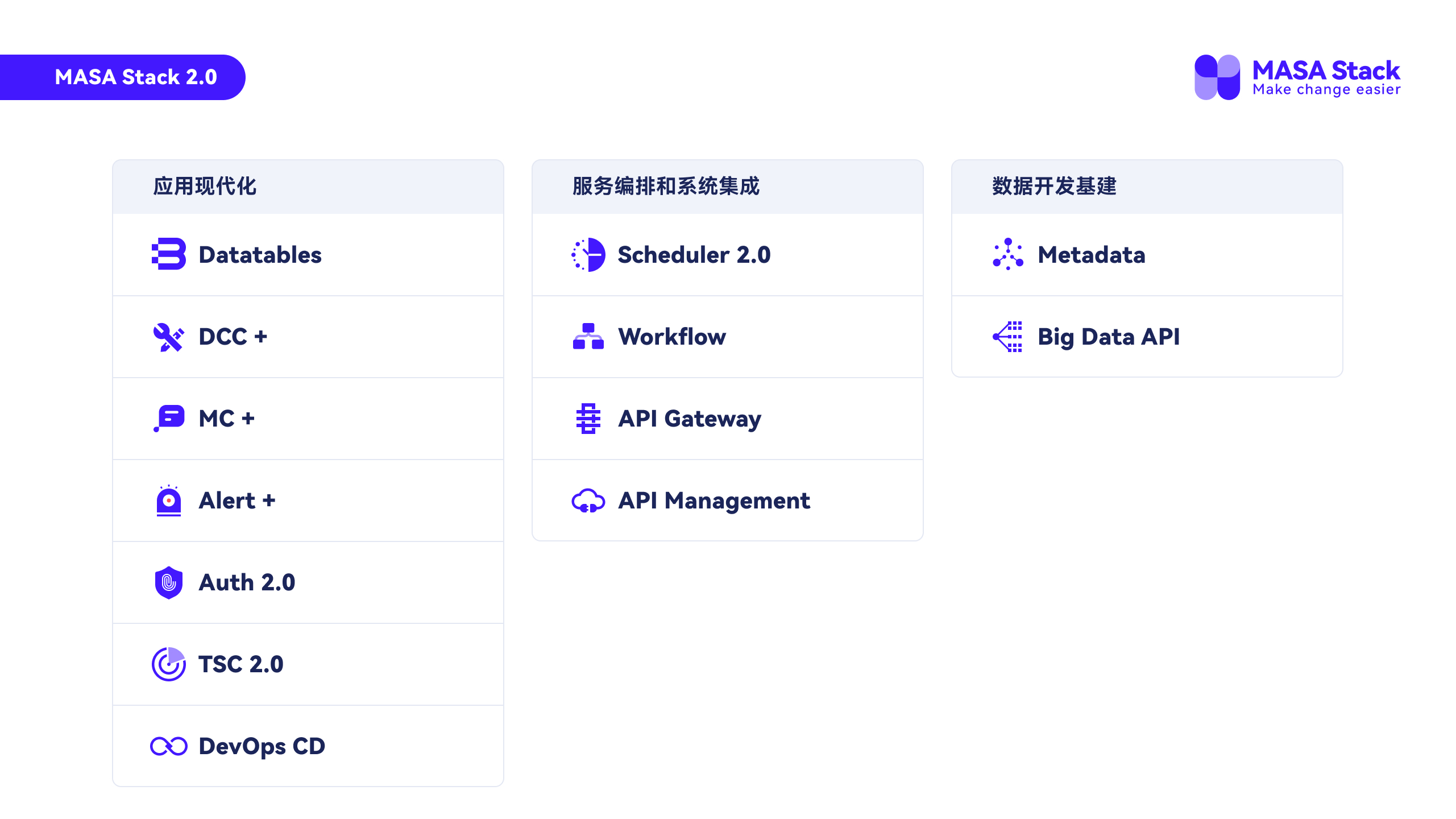

MASA Stack 1.0 发布会讲稿——生态篇

2022年运营回顾 贡献者 首先感谢贡献者们为MASA Stack社区所作的积极贡献,这些贡献者给我们提出了很多宝贵的建议,更是积极的提交PR帮助我们一起让产品更健壮,更完善,还在各种场合推广我们的解决方案,非常给力&#x…...

| 真题+思路++考点+代码)

华为OD机试 - 火星文计算2(JS)| 真题+思路++考点+代码

火星文计算2 题目 已知火星人使用的运算符号为#;$ 其与地球人的等价公式如下 x#y4*x3*y2 x$y2*xy3 x y是无符号整数 地球人公式按照c语言规则进行计算 火星人公式中#符优先级高于$ 相同的运算符按从左到右的顺序运算 输入 火星人字符串表达式结尾不带回车换行 输入的字符串…...

从春节后央行的首批罚单,看金融反欺诈反洗钱的复杂性

目录 个人信息保护的问题 征信管理的问题 反洗钱与反欺诈的问题 金融欺诈愈加复杂多变 金融机构如何增强反欺诈反洗钱 春节后,央行公示首批罚单。其中,厦门银行被中国人民银行福州中心支行给予警告,并没收违法所得767.17元,处…...

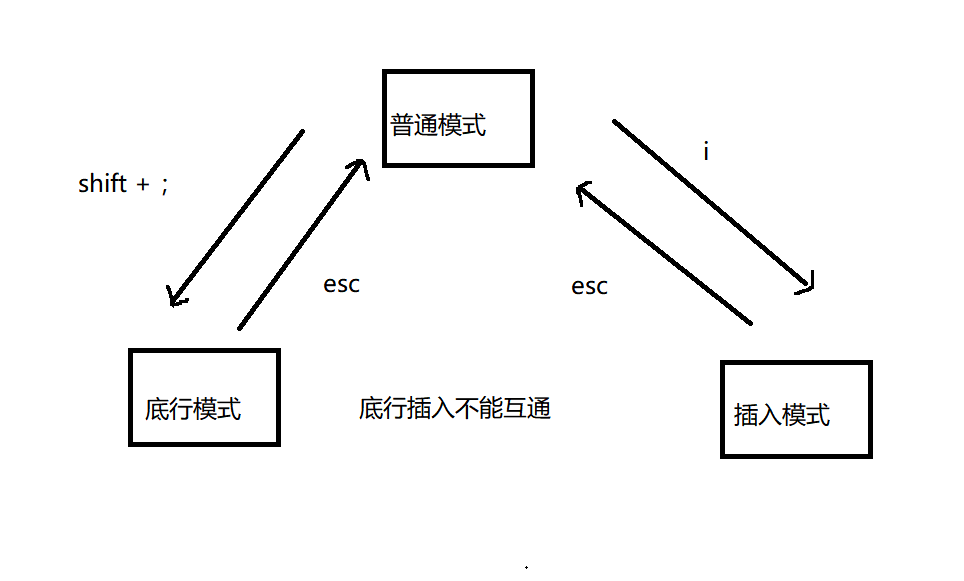

【Hello Linux】Linux工具介绍 (yum vim)

作者:小萌新 专栏:Linux 作者简介:大二学生 希望能和大家一起进步! 本篇博客简介:介绍Linux的常用工具 yum和vim Linux工具介绍Linux中的软件管理工具 -- yum在windows下安装软件的方式在Linux下安装软件的方式认识yum…...

多种充电模式_手持无线充气泵方案

一、手持无线充气泵手持无线充气泵是一个通过锂电池供电达到无需插电就能使用的便携式充气泵,它的适用场景大部分是为身处户外没有办法接通电源的人而设计的,方便人们的出行也可解燃眉之急。不仅如此,为预防手持无线充气泵的锂电池电量用完而…...

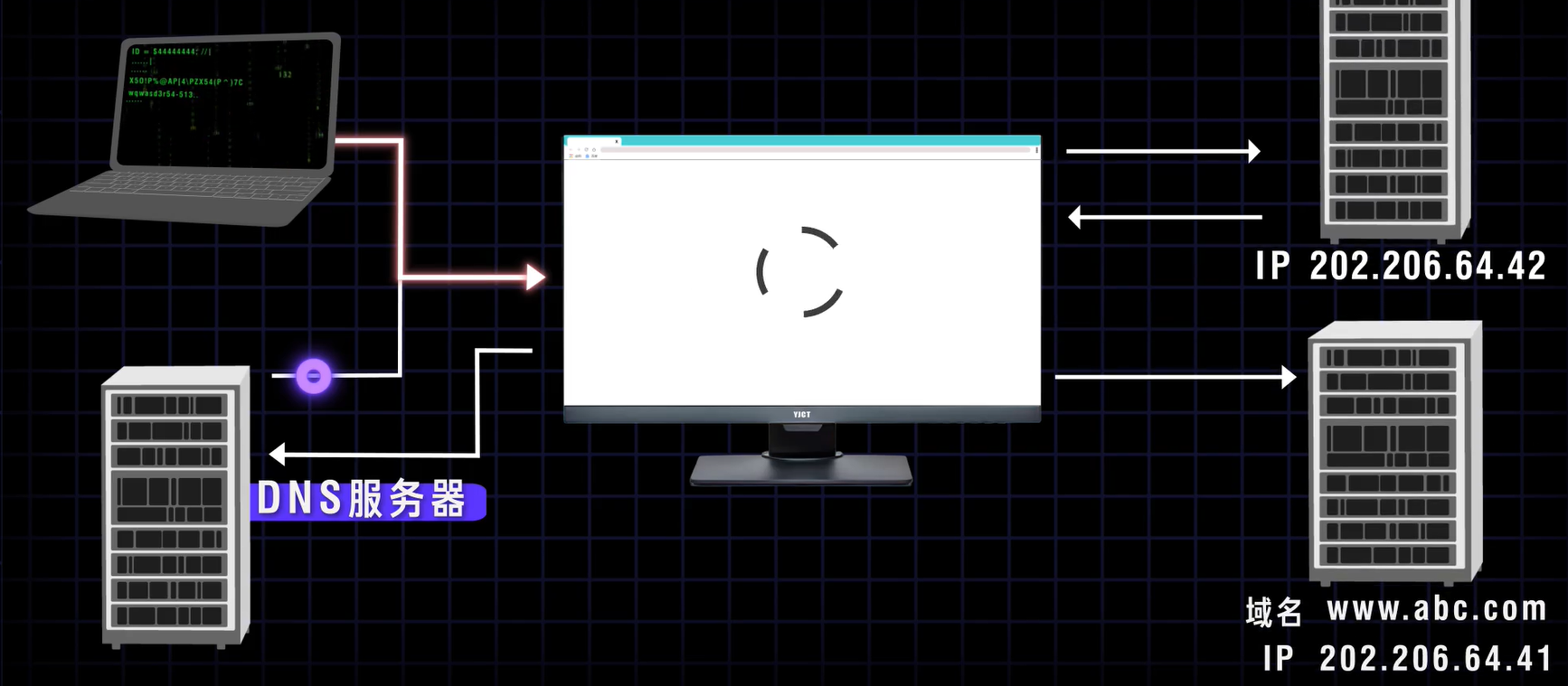

【网络基础】DNS是什么

本文不会直接引入复杂枯燥概念,用形象例子通俗讲解,旨在入门理解。 DNS作用 DNS是用来做域名解析的。 相当于把网址翻译成实际ip地址,供其他设备访问。 一个例子 有一个网站的服务器IP地址为1.1.1.1,用电脑访问该网站的话只需…...

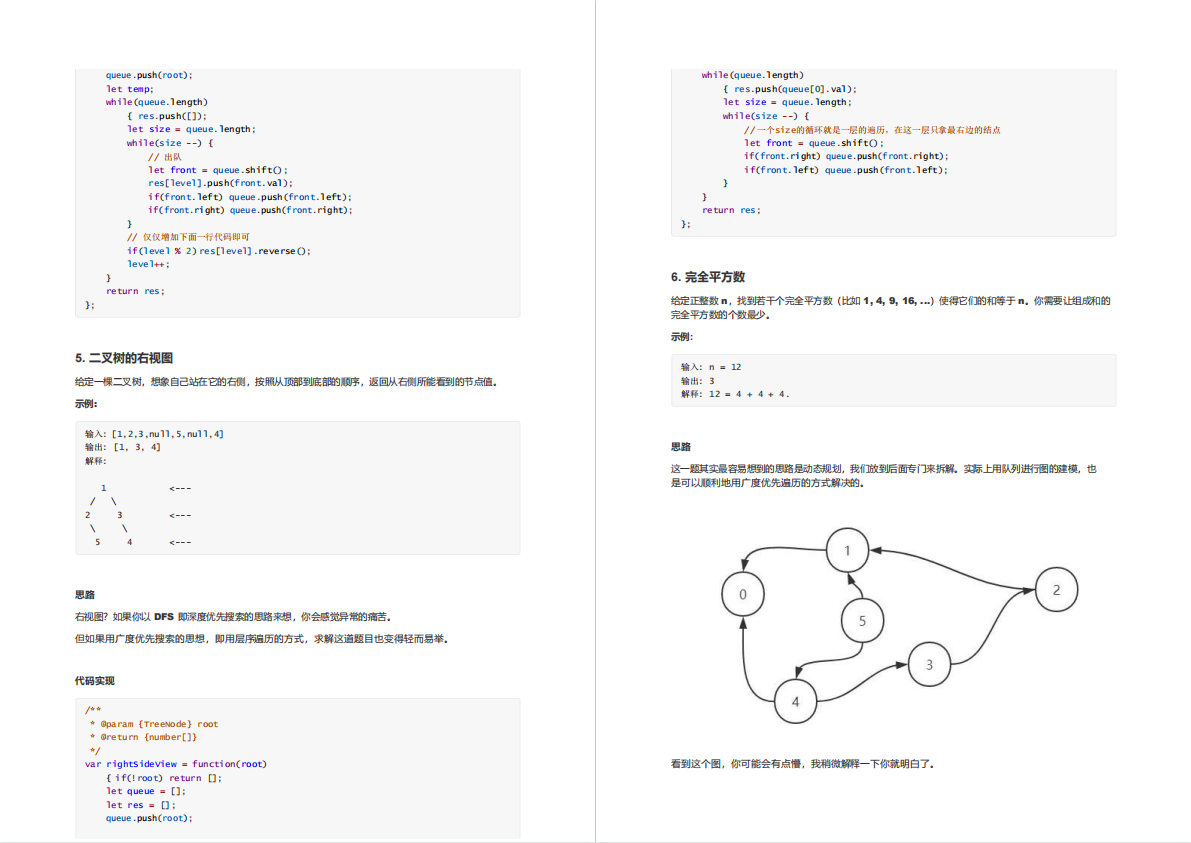

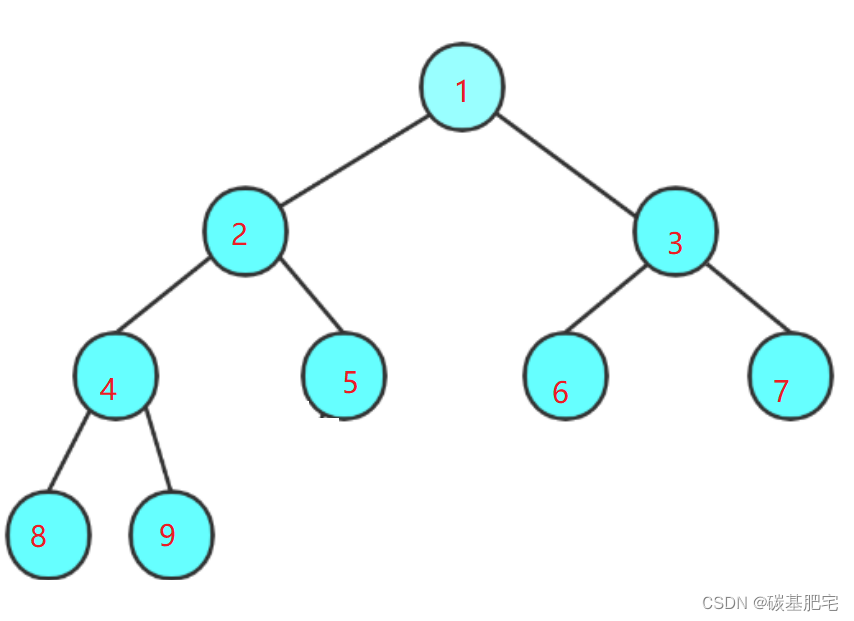

二叉树的性质与推导及常见习题整理

目录 一、性质推导 二、常见的二叉树性质习题 1. 某二叉树共有 399 个结点,其中有 199 个度为 2 的结点,则该二叉树中的叶子结点数为()。 2.在具有 2n 个结点的完全二叉树中,叶子结点个数为(ÿ…...

亚马逊卖家测评补单的重要性和缺点

对于亚马逊、沃尔玛、ebay、wish、newegg、速卖通、阿里国际站、shopee、lazada、temu、乐天、toktok、joom、ozon等卖家来说,测评补单是一个比较常见的话题,因为测评可以给自己产品留下优质的评价,让国外真实买家更加明确,便捷的…...

Java类和对象超详细整理,适合新手入门

目录 一、驼峰命名法 二、Java注释 三、转义符 四、Java程序它的基本结构是什么? 五、Java中的类 六、创建类 七、定义main方法 八、执行代码输出语句 九、Java中的对象 十、创建对象 十一、类与对象的关系 一、驼峰命名法 包名:多单词组成所…...

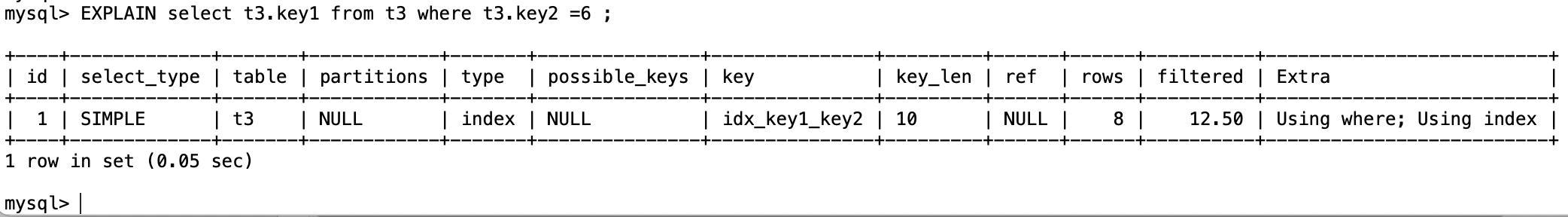

MySQL:连explain的type类型都没搞清楚,怎敢说精通SQL优化?

我们在使用SQL语句查询表数据时,提前用explain进行语句分析是一个非常好的习惯。通过explain输出sql的详细执行信息,就可以针对性的进行sql优化。 今天我们来分析一下,在explain中11种不同type代表的含义以及其应用场景。 1,sys…...

从单场到多场并发:知识竞赛平台的弹性扩展能力

🚀 从单场到多场并发:知识竞赛平台的弹性扩展能力动态调度 平滑扩容 稳定支撑📌 演进中的需求:从单一活动到复杂场景传统的知识竞赛活动往往以单场、线下或小规模在线形式进行,对技术平台的压力相对有限。然而&#…...

游戏开发资源宝库:从计算机图形学到Unity生态的全栈知识索引

1. 项目概述:一份游戏开发者的“藏宝图”如果你是一名游戏开发者,无论是刚入行的新人,还是摸爬滚打多年的老兵,大概都经历过这样的时刻:为了实现一个特定的效果,或是解决一个棘手的技术难题,在搜…...

普遍认为赠送福利越多客户留存越高,编程统计福利投入,客户留存数据过度福利,会造成客户贪婪流失率上升。

“福利投入强度与客户留存的非线性关系分析” 为主题。一、实际应用场景描述(Business Context)在 SaaS、电商、会员制平台、在线教育等商业场景中,赠送福利(优惠券、积分、试用权益、赠品等)被广泛用于:- …...

CentOS7网络配置与XShell连接实战:从零搭建远程管理环境

1. 环境准备与工具安装 第一次接触Linux服务器管理的新手,往往会被网络配置和远程连接这两个基础操作难住。我自己刚开始学习时,光是让虚拟机联网就折腾了大半天。其实只要掌握正确的方法,整个过程完全可以像搭积木一样简单明了。 首先需要准…...

技术深度解析CoverM在PacBio HiFi宏基因组测序数据覆盖率分析中的应用

技术深度解析CoverM在PacBio HiFi宏基因组测序数据覆盖率分析中的应用 【免费下载链接】CoverM Read alignment statistics for metagenomics 项目地址: https://gitcode.com/gh_mirrors/co/CoverM CoverM作为一款专门用于计算基因组覆盖率的生物信息学工具,…...

安全巡检执行率能解决哪些场景痛点?一套安全巡检执行率提升方案实战

在工厂的安全管理中,安全巡检是发现隐患、预防事故的最前线。然而,很多企业的安全巡检流于形式,执行率长期低下,带来了一系列连锁反应。那么,安全巡检执行率到底能解决哪些场景痛点?如何系统性地提升执行率…...

python网上书店系统vue

目录技术栈选择前端模块划分后端API设计关键实现细节开发流程示例代码片段项目技术支持源码获取详细视频演示 :文章底部获取博主联系方式!同行可合作技术栈选择 前端采用Vue 3(Composition API) TypeScript Vite构建工具&#…...

一键批量下载网易云音乐FLAC无损音乐:Golang高效解决方案

一键批量下载网易云音乐FLAC无损音乐:Golang高效解决方案 【免费下载链接】NeteaseCloudMusicFlac 根据网易云音乐的歌单, 下载flac无损音乐到本地.。 项目地址: https://gitcode.com/gh_mirrors/nete/NeteaseCloudMusicFlac 你是否曾梦想拥有一个完整的无损…...

IP集成时代CDC验证新思路:用户灰盒方法解析与实践

1. 项目概述与核心问题在FPGA和ASIC设计领域,时钟域交叉(CDC)问题就像一颗深埋的“定时炸弹”。随着设计复杂度的飙升,尤其是IP(知识产权核)复用成为主流,这颗炸弹的引线变得越来越隐蔽…...

)

PyTorch预训练模型‘解剖课’:以VGG19为例,彻底搞懂如何自定义输出层(避坑指南)

PyTorch预训练模型‘解剖课’:以VGG19为例,彻底搞懂如何自定义输出层(避坑指南) 当你第一次拿到一个预训练好的VGG19模型,兴奋地准备用它提取图像特征时,却发现自己被卡在了第一步——这个"黑箱"…...