Xilinx DCI技术

Xilinx DCI技术

- DCI技术概述

- Xilinx DCI技术实际使用

- 某些Bank特殊DCI要求

- DCI级联技术

- DCI端接方式

- 阻抗控制驱动器(源端接)

- 半阻抗控制阻抗驱动器(源端接)

- 分体式DCI(戴维宁等效端接到VCCO/2)

- DCI和三态DCI(T_DCI)

- Vivado设置DCI与内部参考电压

- DCI与内部参考电压

- 创建DCI_CASCADE约束

- 创建INTERNAL_VREF约束

DCI技术概述

随着FPGA容量越来越大,系统时钟速度越来越快,PC电路板设计和制造更加困难。随着更快的信号边沿速率,保持信号完整性成为关键问题。PC电路板必须恰当的端接避免反射和振铃。如下图为信号过冲波形。

为了端接PCB走线,附加的电阻需要添加到接收器或者驱动器以匹配走线阻抗。然而随着随着器件I/O数量增加,附加的电阻会增加电路板面积和组件数量,在某些情况下增加电路板尺寸是不可能的。为了解决此问题达到更好的信号完整性,Xilinx开发了数字阻抗控制(DCI,Digitally Controlled Impedance)技术。包括两个功能:

- 控制驱动器的输出阻抗

- 为驱动器或发送器添加一个并行端接,在传输线上得到精确的特征阻抗匹配,以提高信号完整性。

基于I/O标准,DCI可以控制输出驱动阻抗或者添加一个并行端接在驱动器或者接收器,最终的目标都是精确匹配传输线阻抗,保证信号传输完整性。DCI主动调整I/O内部的阻抗,以校准VRN和VRP引脚上的外部精密参考电阻。它可以补偿因逻辑处理、温度和电压变化而引起的I/O阻抗变化。

对于可控阻抗驱动器的I/O标准,DCI控制驱动器阻抗匹配两个参考电阻,或者对于某些标准,匹配一半这些参考电阻的值。

对于使用可控并行端接I/O标准,DCI为驱动器和接收器提供并行端接。这消除了电路板上端接电阻,较小了PCB布线的难度和器件数量,并且改善信号完整性。DCI特性只能在HP bank中应用,HR bank不具有该特性。

HR bank虽然没有DCI功能,但也支持内部的阻抗匹配,也称为IN_TERM。它和DCI差异可以总结为不支持自动校正和补偿,只是固定40欧、50欧和60欧,通过约束方式来调整。当然,这里我们需要选择支持IN_TERM的电气标准。

NET "pad_net_name"IN_TERM=“UNTUNED_SPLIT_50”;

Xilinx DCI技术实际使用

在每个bank中,DCI使用两个多功能参考管脚控制驱动器阻抗或者并行端接值。N参考管脚(VRN)必须通过参考电阻上拉到VCCO,P参考管脚(VRP)必须通过另外一个参考电阻下拉到GND。每个参考电阻的值等于电路板走线特性阻抗或者2倍于特征阻抗值。

在设计中实现DCI:

- 分配DCI I/O标准到HP bank

- 将VRN多功能管脚通过精确电阻上拉到该bank的VCCO电源轨

- 将VRP多功能管脚通过精确电阻下拉到GND

下面的部分内容将讨论如何决定不同I/O标准的VRN和VRP管脚的精确电阻值。同一个bank内的所有DCI标准共享相同的外部精确电阻。如果在相同的I/O bank列中,几个I/O bank使用DCI,并且这几个bank使用相同的VRN/VRP电阻值,则内部VRN/VRP节点可以级联,此时,这同一列中的所有 I/O bank要求的精确电阻只需要一对管脚连接,无需每个I/O bank都要连接精确电阻。这种特性称为DCI级联。该部分也会描述如何判定I/O bank位于相同的I/O bank列中。如果DCI I/O标准在该bank中使用,则该bank可以作为普通I/O使用。

DCI通过选择打开或关闭I/O内部的晶体管调整I/O阻抗,该阻抗匹配外部参考电阻。该调整发生在器件启动时。默认情况下,DONE管脚不会拉高直到第一部分阻抗调整完毕。DCI校准可以通过例化DCIRESET原句实现复位。

DCI配置输出驱动器有以下两种类型:

- 控制阻抗驱动器(源端接)

- 使用半阻抗控制阻抗驱动器(源端接)

对于支持并行端接的I/O标准,DCI产生一个戴维宁等效或者分割阻抗到VCCO/2。

某些Bank特殊DCI要求

如果用户将任何bank14或者15(任何器件)或者bank11,12,17,18,20和21(SSI技术器件)的I/O标准设计为DCI I/O,则DCIRESET原句应该包含在设计中。这种情况下,设计应该产生RST复位脉冲给DCIRESET原句,直到该原句产生LOCKED信号后,才可以将这些管脚作为DCI标准 I/O使用。这是因为这些类型的bank I/O在器件正常初始化时没有进行初始化DCI校准功能。

DCI级联技术

使用DCI I/O标准的7系列FPGA HP I/O Bank可以选择从另一个HP I/O Bank导出DCI阻抗值。如图所示。内部分配的数控总线通过bank控制每个I/O的阻抗。下图为单个bank内的DCI使用。

使用DCI级联,一个I/O bank(主bank)必须将VRN/VRP管脚连接到外部参考电阻。其他和主bank在同一列的I/O bank(Slave banks)可以使用DCI标准,并且阻抗值和主bank阻抗相同。这些从bank无需将VRN/VRP管脚连接外部电阻,级联的DCI阻抗控制来自I/O主bank。下图显示了多个I/O bank实现DCI级联,其中B bank为主bank,A和C为从bank。

使用DCI级联时,推荐遵循以下指导:

- DCI级联只能用于同一列中的HP I/O banks

- DCI级联不能跨过器件边界,特别大容量器件,如Virtex-7器件

- 主、从bank必须具有相同的VCCO和VREF电压

- 同一HP I/O列中的I/O bank,不使用DCI标准的banks不用遵循VCCO和VREF电压

- 所有主、从bank都必须满足DCI I/O bank兼容性规则

- Xilinx推荐未使用的bank应该供电,因为不使用的I/O bank的VCCO不供电会降低这些管脚的ESD管脚保护等级。如果bank未供电,级联的DCI任然可以通过未供电的bank。

DCI端接方式

下图为DDR3 VRP和VRN的连接和阻值

下图为SSTL18_I和SSTL18_II两种电气标准的DCI应用对比

阻抗控制驱动器(源端接)

为了优化高速或者高性能应用信号完整性,驱动器必须有输出阻抗以匹配传输线特征阻抗,否则由于阻抗不连续将会引起信号反射。为了解决此问题,设计者有时需要在高驱动,低阻抗驱动器放置外部串行端接电阻。该电阻的阻值和驱动器输出阻抗之和应该和传输线阻抗相等。

DCI I/O标准支持:LVDCI_15/LVDCI_18/HSLVDCI_15/HSLVDCI_18/HSUL_12_DCI/DIFF_HSUL_12_DCI。

下图举例了控制阻抗驱动器(DCI驱动器)。

半阻抗控制阻抗驱动器(源端接)

该端接方式支持LVDCI_DV2_15和LVDCI_DV2_18电平标准。下图举例了这种端接方式驱动器(半阻抗DCI驱动器),其中R等于2×Z0,Z0为传输线阻抗。

分体式DCI(戴维宁等效端接到VCCO/2)

一些I/O标准(例如,HSTL和SSTL)要求输入端接电阻R上拉到VTT电压,即VCCO/2电压,如下图所示,输入端接到VCCO/2,未使用DCI。

上图为等效的戴维宁并行端接,为了满足图中要求,通常将VRN/VRP管脚连接100Ω精密电阻,支持DCI分立端接的标准如下图所示,所有支持分立端接的DCI I/O标准。

Xilinx 7系列器件分立端接DCI举例如下图所示。输入端接DCI控制,外部VRN/VRP电阻 =2R。

DCI和三态DCI(T_DCI)

I类SSTL和HSTL I/O标准只支持单向信号,它们要么只能作为输入或者只能作为输出,不支持双向。I类SSTL和HSTL I/O只支持输入分立端接DCI。II类SSTL和HSTL(或者SSTLII和HSTLII)支持单向和双向信号,该标准信号支持输入、输出、双向管脚分立端接DCI。使用DCI分离端接(外接电阻VRN/VRP = 2R)如下图所示。

当使用分立端接驱动时,DCI只控制端接阻抗,不控制驱动器。T_DCI只用于双向I/O管脚。对于单向输入管脚可以使用DCI版本标准,对于单向输出管脚non-DCI和DCI版本表均可分配。支持分离端接DCI I/O标准如下图所示,支持分离端接DCI I/O标准。

支持分立T_DCI I/O标准如下图所示。注意:T_DCI标准只能用于双向管脚。

Vivado设置DCI与内部参考电压

DCI与内部参考电压

带有差分输入缓冲区的单端I/O需要一个参考电压Vref,可以使用专用的Vref管脚为每个I/O bank提供参考电压。另外也可以使用INTERNAL_VREF约束来生成内部参考电压,这样PCB上就不需要为Vref提供电源线,也可以释放Vref管脚作为通用I/O使用。每个bank都可以设置一个可选的内部参考电压。

ug471和ug571分别介绍了7系列和UltraScale系列中DCI和INTERNAL_VREF的详细信息。下文介绍在Vivado中设置与之相关的DCI_CASCADE和INTERNAL_VREF属性。

创建DCI_CASCADE约束

DCI_CASCADE约束可以将多个相邻的I/O bank级联在一起,共享DCI参考电压。其中包含DCI参考电压的称作主bank;级联的其它I/O bank称作从bank。每个级联链都必须有一个主bank和至少一个从bank。

在Device Constraints窗口中,选择DCI Cascade:

Unused文件夹中显示了未添加到DCI级联链中的I/O bank,选择需要添加的所有bank,右键->Add DCI Cascade创建级联链,弹出如下窗口:

选择主bank,点击OK则创建好级联链,显示在窗口中:

或者直接将某一bank拖动到另一bank上也可以完成相应操作。设置DCI_CASCADE约束对应的XDC命令如下:

set_property DCI_CASCADE {33} [get_iobanks 34]

get_iobanks选择的为主bank,{}中的是添加到级联链中的从bank,以空白为间隔。上述创建的约束需要点击保存,如果设计已经有了XDC约束文件,约束命令会添加到文件末尾。

创建INTERNAL_VREF约束

使用INTERNAL_VREF约束可以生成FPGA的内部参考电压。这样就不需要在PCB上提供Vref电源线,且可以释放Vref管脚作为通用I/O使用。

在Device Constraints窗口中选择“Internal VREF”,列出了该芯片支持的内部参考电压,NONE文件夹中的I/O bank表示没有设置INTERNAL_VREF约束。

创建INTERNAL_VREF约束,只需要将I/O bank拖到对应参考电压的文件夹中即可;拖到NONE中表示撤销参考电压设置。该设置对应着约束命令,需要保存到XDC约束文件中,示例如下:

set_property INTERNAL_VREF 0.75 [get_iobanks 14]

set_property INTERNAL_VREF 0.675 [get_iobanks 15]

参考:

Vivado使用技巧(12):设置DCI与内部参考电压

Xilinx 7系列FPGA架构之SelectIO结构(一)

相关文章:

Xilinx DCI技术

Xilinx DCI技术 DCI技术概述Xilinx DCI技术实际使用某些Bank特殊DCI要求 DCI级联技术DCI端接方式阻抗控制驱动器(源端接)半阻抗控制阻抗驱动器(源端接)分体式DCI(戴维宁等效端接到VCCO/2)DCI和三态DCI&…...

Kubernetes Pod 优雅关闭:如何让容器平稳“退休”?

Kubernetes Pod 优雅关闭:如何让容器平稳“退休”? 在 Kubernetes 中,Pod 是应用的基本单元。你可能会遇到需要停止某个 Pod 或容器的情况,可能是因为要更新、调整或故障恢复。在这种情况下,Pod 的优雅关闭࿰…...

鸿蒙应用开发(1)

可能以为通过 鸿蒙应用开发启航计划(点我去看上一节) 的内容,就足够了,其实还没有。 可是我还是要告诉你,你还需要学习新的语言 -- ArkTS。 ,ArkTS是HUAWEI开发的程序语言。你需要学习这门语言。这会花费你…...

SimForge HSF 案例分享|复杂仿真应用定制——UAVSim无人机仿真APP(技术篇)

导读 「神工坊」核心技术——「SimForge HSF高性能数值模拟引擎」支持工程计算应用的快速开发、自动并行,以及多域耦合、AI求解加速,目前已实现航发整机数值模拟等多个系统级高保真数值模拟应用落地,支持10亿阶、100w核心量级的高效求解。其低…...

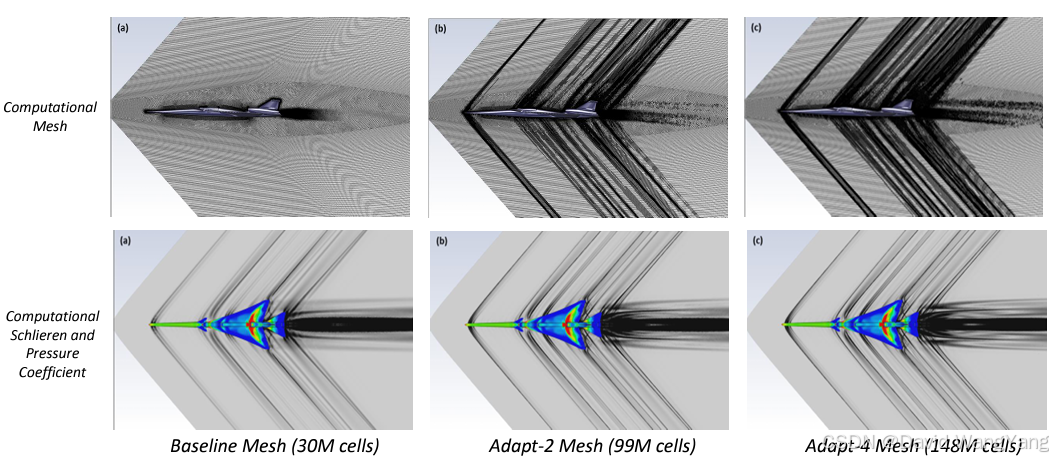

使用 Adaptive Mesh Refinement 加速 CFD 仿真:最佳实践

CFD 仿真中的网格划分挑战 技术的进步正在增强设计探索,数值仿真在优化工程设计方面发挥着至关重要的作用。通常,计算流体动力学 (CFD) 仿真从定制的手工网格开始,具有精细和粗糙的区域,以平衡分辨率和单元…...

前端-动画库Lottie 3分钟学会使用

目录 1. Lottie地址 2. 使用html实操 3. 也可以选择其他的语言 1. Lottie地址 LottieFiles: Download Free lightweight animations for website & apps.Effortlessly bring the smallest, free, ready-to-use motion graphics for the web, app, social, and designs.…...

智能工厂的设计软件 应用场景的一个例子:为AI聊天工具添加一个知识系统 之5

本文要点 前端 问题描述语言 本文继续完善 “描述” ---现在我们应该可以将它称为 “问题problem描述语言 ”。 它 通过对话框的question 引发 表征的issue 的“涌现” 最终 厘清应用程序的“problem”。即它合并了 ISO七层模型中的上面三层,通过将三层 分别形成…...

java web

流程 1.浏览器发送http协议的格式数据和url给服务器软件tomcat 2.浏览器解析http格式数据并创建request和response对象,把数据封装到request对象里。 3.tomcat解析url确定访问路径,如果是静态资源html等,直接将html数据作为http格式响应体返回&#x…...

【嵌入式软件开发】嵌入式软件计时逻辑的两种实现:累加与递减的深入对比

本文主要从四个方面详细阐述了嵌入式软件编程中计时逻辑的两种实现方式:累加和递减。让我为您详细解析各个部分: 1. 基本概念对比 累加方式 从0开始向上计数每个周期增加固定值(通常为1)类似于我们日常生活中的秒表计时方式递减方式 从预设值开始向下计数每个周期减少固定…...

如何将vCenter6.7升级7.0?

vCenter是什么? vCenter是一种虚拟化管理软件,由VMware公司开发和发布。它是VMware vSphere虚拟化平台的核心组件之一,主要用于集中管理和监控虚拟化环境中的虚拟机、虚拟存储和网络资源。vCenter可以实现对多个ESXi主机的集中管理ÿ…...

服务器网卡绑定mode和交换机的对应关系

互联网各领域资料分享专区(不定期更新): Sheet 模式类别 网卡绑定mode共有七种(0~6): bond0、bond1、bond2、bond3、bond4、bond5、bond6 mode详解 mode0 ,即:(balance-rr) Round-robin policy(平衡轮循环策略,需要配置交换机静态聚合) mode…...

Maven (day04)

什么是maven? Maven 是 Apache 旗下的一个开源项目,是一款用于管理和构建 java 项目的工具。 官网:Welcome to Apache Maven – Maven https://maven.apache.org/ Maven的作用 依赖管理(方便快捷的管理项目依赖的资源(jar包)ÿ…...

Echart实现3D饼图示例

在可视化项目中,很多地方会遇见图表;echart是最常见的;这个示例就是用Echart, echart-gl实现3D饼图效果,复制即可用 //需要安装,再引用依赖import * as echarts from "echarts"; import echar…...

UE5 Debug的一些心得

1、BUG粗略可分为两类: 一种是显性的,编译直接就通不过,必须马上解决。 第二种是隐性的,新功能完成后,编译成功顺利运行,洋洋自得,而问题隐藏在幕后,测试之后才逐渐发现有问题&…...

java中多线程的一些常见操作

Java 中的多线程是通过并发编程来提高应用程序的效率和响应速度。Java 提供了多个机制和类来支持多线程编程,包括继承 Thread 类、实现 Runnable 接口、使用线程池等。以下是 Java 中一些常见的多线程操作和应用场景。 1. 创建线程 1.1 通过继承 Thread 类创建线程…...

【gopher的java学习笔记】什么是Spring - IoC和DI

一聊到java,离不开的一个东西就是spring;当我想了解什么是spring的时候,一查,基本上都是围绕着两个词来展开的:IoC和AOP。 对于我自己来说,AOP我觉得比较好理解,因为不管是之前写golang还是pyt…...

【开源免费】基于SpringBoot+Vue.JS校园社团信息管理系统(JAVA毕业设计)

本文项目编号 T 107 ,文末自助获取源码 \color{red}{T107,文末自助获取源码} T107,文末自助获取源码 目录 一、系统介绍二、数据库设计三、配套教程3.1 启动教程3.2 讲解视频3.3 二次开发教程 四、功能截图五、文案资料5.1 选题背景5.2 国内…...

设计模式 创建型 工厂模式(Factory Pattern)与 常见技术框架应用 解析

工厂模式(Factory Pattern)是一种创建型设计模式,它提供了一种封装对象创建过程的方式,使得对象的创建与使用分离,从而提高了系统的可扩展性和可维护性。 一、核心思想 工厂模式的核心思想是将“实例化对象”的操作与…...

pip 下载安装时使用国内源配置

pip 是 Python 的包管理工具,用于安装和管理第三方库。然而,在某些情况下,默认的 PyPI(Python Package Index)源可能由于网络原因导致下载速度慢或者连接不稳定。幸运的是,我们可以轻松地配置 pip 使用国内…...

【数据结构】数据结构简要介绍

数据结构是计算机科学中用于组织、管理和存储数据的方式,以便于高效地访问和修改数据。 数据结构的分类: 数据结构可以大致分为两类:线性结构和非线性结构。 1. 线性结构 线性结构中的数据按顺序排列,每个元素有唯一的前驱和后…...

基于SUMO与PPO的智能换道决策实战:从环境构建到模型部署

1. 环境准备与基础配置 在开始构建智能换道决策系统之前,我们需要先搭建好开发环境。这里我推荐使用Anaconda来管理Python环境,它能很好地解决不同项目之间的依赖冲突问题。我习惯为每个项目创建独立的环境,比如这次我们可以命名为"sumo…...

Agent+可穿戴设备:心率、睡眠、活动数据如何变成有价值的健康建议

可穿戴设备每天都会产生心率、睡眠、步数、活动强度等数据,但开发者真正要解决的不是“采集更多指标”,而是把这些指标转成可解释、可追踪、可配置的健康提示。本文从工程角度搭建一个简化版 Agent 服务,演示如何完成数据接入、趋势计算、规则…...

从设计到验证:如何用ADS的HB2TonePAE_FPswp模板快速评估你的PA线性度?

射频功放线性度评估实战:ADS高级仿真模板深度解析 在射频功率放大器(PA)的设计流程中,线性度评估往往是最耗时的环节之一。传统方法需要工程师手动搭建测试平台,不仅效率低下,还容易引入人为误差。Keysight ADS软件内置的HB2ToneP…...

HS2-HF_Patch:一键解决《Honey Select 2》三大核心问题的终极增强补丁

HS2-HF_Patch:一键解决《Honey Select 2》三大核心问题的终极增强补丁 【免费下载链接】HS2-HF_Patch Automatically translate, uncensor and update HoneySelect2! 项目地址: https://gitcode.com/gh_mirrors/hs/HS2-HF_Patch 厌倦了《Honey Select 2》原版…...

慢时钟域到快时钟域控制信号传递:原理、方案与实战

1. 控制信号跨时钟域传递:一个资深工程师的实战拆解在数字电路设计里,尤其是涉及多时钟域的复杂系统,比如SoC、高速接口或者异构计算单元,控制信号的跨时钟域传递(CDC, Clock Domain Crossing)绝…...

)

py之paho mqtt客户端代码示例(亲测可用)

from paho.mqtt import client as mqtt_clientdef on_connect(client, userdata, flags, reasonCode, properties):"""连接成功回调reasonCode: 0 表示成功,其他值表示失败"""print...

如何免费使用AI图像放大神器Upscayl?一文掌握所有技巧

如何免费使用AI图像放大神器Upscayl?一文掌握所有技巧 【免费下载链接】upscayl 🆙 Upscayl - #1 Free and Open Source AI Image Upscaler for Linux, MacOS and Windows. 项目地址: https://gitcode.com/GitHub_Trending/up/upscayl 想要将模糊…...

不止是怀旧:用Docker部署超级马里奥,聊聊容器化对经典软件保存的意义

容器化时光机:用Docker守护数字文化遗产的技术实践 在数字时代洪流中,经典软件如同沙漏中的细沙,正以惊人的速度从我们的指尖流逝。那些曾经定义了一个时代的程序、游戏和工具,正面临着"数字消亡"的威胁——操作系统迭代…...

告别黑盒:手把手教你用VTK在QT中‘组装’并驱动SolidWorks导出的机械臂模型

从STL零件到可交互机械臂:VTKQT三维可视化开发实战 机械臂的数字化仿真一直是工业自动化与机器人教学中的核心课题。想象一下,当你从SolidWorks中导出一堆零散的STL文件,如何在代码中让它们"活"起来——每个关节都能独立旋转&#…...

)

Cadence Virtuoso新手避坑指南:手把手教你画反相器原理图(附3.3V工艺库设置)

Cadence Virtuoso新手避坑指南:3.3V工艺库反相器设计全流程解析 第一次打开Cadence Virtuoso时,那个充满专业术语的界面就像面对一架航天飞机的控制台——每个按钮都暗藏玄机,每次点击都可能引发未知错误。作为模拟IC设计的行业标准工具&…...