Verilog语法之常用行为级语法

摘要:本文主要介绍了一些在verilog中的行为级语法,并且提供了大量的运行实际例子,可以通过这些例子感受行为级语法在仿真中的巨大作用。

概述:行为级语法是RTL级的上一层,或者说是比RTL级更高级的语法,其语法更加符合人类思维的描述方式。行为级语法可用于快速验证算法的正确性,或快速构建一个复杂的系统模型。仿真验证中使用行为级的语法可以充分发挥仿真平台的优越性,用更加简介、高效的语法语句简化并加快仿真系统的构建,让设计者把更多的时间和精力集中在设计和调试上。行为级多以直接赋值、指定延迟、算术运算等不可综合的形式进行,不关注电路的具体结构,因为其并不需要直接综合成实际的电路结构并运行到FPGA器件中。

1.initial和always

initial和always语句所实现的行为级语法遵循硬件固有的并行性特点,在仿真过程中可以独立并行地运作。在一个测试脚本中无论是有一个还是多个initial或always语句,它们都会从仿真的0ns开始并行工作。initial语句在整个仿真过程中只会运行一次,而always语句则会不断重复运行,直到仿真运行停止。

`timescale 1ns/1nsmodule testbench_top();reg a, b;initial begina='b1;b='b0;endinitial begin#1000;$stop;endalways begin#50 a=~a;endalways begin#100 b=~b;endendmodule2.时间刻度`timescale

`timescale对事件单位代表的物理时间进行定义,其后接时间单位和事件精度,两者之间用反斜杠/进行分隔。语法结构为`timescale (时间单位)/(时间精度)。

3.时间戳 $time

时间戳$time是一个系统函数,可以返回一个64位的整数来表示当前的仿真时刻,返回值的单位和`timescale定义的时间单位一致。时间戳$time在使用$display打印时,若指定输出格式为%t,则输出数据以`timescale定义的时间精度为单位;若指定输出格式为%d,则输出数据以`timescale定义的时间单位为单位。示例代码如下:

`timescale 1ns/1psmodule testbench_top();initial begin#10;$display("%0tps", $time);#5.481;$display("%0tps", $time);#10.58289;$display("%0tps", $time);$display("%0dns", $time);$stop;endendmodule运行结果如下:

此处$time返回的是一个整数值,因此虽然时间精度为ps,返回的整数值也会将后面的小数进行四舍五入,因此我们得到的是整数的时间单位。

4.时间戳$realtime

时间戳$realtime是一个系统函数,返回的时间数字是一个实型数;该实型数也是以时间尺度为基准的。时间戳$realtime在使用$display进行打印时,若指定输出格式为%t,则输出数据以`timescale定义的时间精度为单位;若指定输出格式为%f,则输出数据以`timescale定义的时间单位为单位。示例代码如下:

`timescale 1ns/1psmodule testbench_top();initial begin#10;$display("%0fns", $realtime);#5.481;$display("%0fns", $realtime);#10.58289;$display("%0fns", $realtime);$display("%0tps", $realtime);$stop;endendmodule运行结果如下:

5.持续赋值assign和deassign

使用assign语句可以对变量进行持续的赋值,deassign则恰恰相反,可以结束assign语句对某个变量的持续赋值。示例代码如下:

`timescale 1ns/1psmodule testbench_top();`define CLK_PERIORD 10reg clk;initial beginclk <= 0;

endalways #(`CLK_PERIOD/2) clk = ~clk;reg a;

initial begina=0;#100;assign a=clk;#100;deassign a;#100;$stop;

endendmodule6.持续赋值force和release

force语句和assign语句有类似的功能,可以实现持续地赋值。但是force语句除了可以对变量进行持续赋值,甚至还可以对一个已经使用assign赋值了的变量进行强制赋值,而release语句则可以终止force语句的赋值。示例代码如下:

`timescale 1ns/1psmodule testbench_top();`define CLK_PERIOD 10reg clk;initial beginclk <= 0;

endalways #(`CLK_PERIOD/2) clk = ~clk;reg a;

initial beginassign a = clk;#100;force a = 0;#100;release a;#100;$stop;

end

endmodule

7.循环语句forever、repeat、while和for

行为级语法支持forever、repeat、while和for这4类循环语句,可以实现对一段代码的不执行、一次执行或多次执行。

(1)forever

forever意为永远,表示连续执行forever语句后的逻辑功能;当最后一行代码执行完成后,再从第一行代码开始重新执行,如此反复,直到仿真结束。如果用begin...end规定执行范围,执行范围从begin开始,以end结束。forever语句必须写到initial语句中。其语法结构如下:

(2)repeat

repeat意为重复,表示连续执行repeat后的逻辑功能,其后括号中的数值是执行的次数,当最后一行代码执行完成后,再从第一行代码开始执行,直到完成执行的次数后停止。如果用begin...end规定执行范围,执行范围从begin开始,以end结束。forever语句必须写到initial语句中。其语法结构如下:

示例代码如下:

module testbench_top();integer cnt;reg en;initial beginen=0;cnt=0;#100;repeat(8) beginen=1;cnt=cnt+1;#10;enden=0;cnt=0;#100;$stop;end

endmodule(3)while

while表示“当...时”,当while后括号中的表达式为TRUE时,连续执行while语句后的逻辑功能;当最后一行代码执行完成后,再从第一行代码开始执行,直到表达式为FALSE时停止。如果用begin...end规定执行范围,执行范围从begin开始,以end结束。其语法结构如下:

示例代码如下:

module testbench_top();`define CLK_PERIOD 10

reg clk;initial beginclk <=0;

endalways #(`CLK_PERIOD/2) clk = ~clk;reg [7:0] cnt=0;

always @(posedge clk)cnt <= cnt + 1;initial begin$display("Simulation Start.");while(cnt < 8) begin$display("cnt=%0d", cnt);@(posedge clk);#1;end$display("Simulation End.");$stop;

endendmodule

运行结果如下:

(4)for语句根据其表达式中的变量初始、变化和判断条件,实现其后逻辑功能的多次执行。for后面的括号中有3个表达式;首先以for后面括号中的第一个表达式为初始条件;当for后面括号中第2个表达式为TRUE时,连续执行for语句后的逻辑功能;当最后一行代码执行完成之后,执行一次for后面括号中的第3个表达式;再回头执行for后面的第2个表达式,若为TRUE,则继续执行其后的逻辑功能,如此反复,直到第二个表达式为FALSE时停止。其语法结构如下:

示例代码如下:

module testbench_top();`define CLK_PERIOD 10

reg clk;initial beginclk <= 0;

endalways #(`CLK_PERIOD/2) clk = ~clk;integer cnt;

initial begin$display("Simulation Start.");for (cnt=4; cnt<=8; cnt=cnt+1) begin$display("cnt=%0d", cnt);@(posedge clk);endend

endmodule运行结果如下:

8.时间控制

在行为级语法的过程赋值中的事件控制主要有两大类,一类使用#实现精确的时间延时控制,另一类使用事件表达式(如@和wait语句)实现事件触发的时间控制。

(1)时间延时#

时间延时#可后接数值、常量表达式(如定义的参数)或变量,表示延时若干个时间单位,时间单位和精度由`timescale语法申明。若#后的延时时间设置值中某些位出现x或z,则延时时间将被强制设定为0;若#后的延时时间设置值为负数,则延时时间将被强制设定为2s。示例代码如下:

`timescale 1ns/1psmodule testbench_top();parameter DELAY_PARA=50;

real delay_vari;

real t1,t2,t3,t4;initial begindelay_vari=25.338;t1=$realtime;#100;t2=$realtime;$display("#100 = %0fns", (t2-t1));#delay_vari;t3=$realtime;$display("#delay_vari=%0fns", (t3-t2));#DELAY_PARA;t4=$realtime;$display("#DELAY_PARA=%0fns", (t4-t3));$finish;

endendmodule运行结构如下:

(2)事件触发@

事件触发@可以基于某个信号或变量的取值变化,也可以基于某个数据位的方向变化,如使用posedge或negedge分别表示取值从0变化为1或从1变化为0。示例代码如下:

`timescale 1ns/1psmodule testbench_top();reg en;integer dly;initial beginen=0;#10;en=1;#10;en=0;endinitial begindly=0;#20;dly=1;#20;dly=3;#20;dly=4;endinitial begin@(posedge en);$display("@(negedhe en) at %0fns", $realtime);@(negedge en);$display("@(negedge en) at %0fns", $realtime);@(dly == 3);$display("@(dly == 3) at %0fns", $realtime);endendmodule运行结果如下:

(3)事件等待wait

事件等待wait为电平敏感的事件控制语法。wait后的括号内的表达式若为false,则一致等待,直到表达式为true,才执行后续逻辑代码。示例代码如下:

`timescale 1ns/1psmodule testbench_top();reg [7:0] cnt=0;always #10 cnt=cnt+1;initial beginwait(cnt==10) begin$display("cnt==10 at %0dns", $time);end$stop;end

endmodule9.顺序块begin end和并行块

行为级仿真中,begin end之间的多个使用阻塞赋值=的赋值语句,是按照顺序依次执行的;fork join之间的多个赋值语句则是并行执行的。具体的示例代码如下:

`timescale 1ns/1psmodule testbench_top();reg a1=0, b1=0, c1=0;reg a2=0, b2=0, c2=0;initial begin$monitor("a1=%b, b1=%b, c1=%b, a2=%b, b2=%b, c2=%b at %0dns", a1, b1, c1, a2, b2, c2, $time);endinitial begin#10 a1=1;#10 b1=1;#10 c1=1;end#10;$stop;initial beginfork#5 a2=1;#5 b2=1;#5 c2=1;joinend

endmodule运行结果如下:

10.数据类型转换函数

以下4个系统函数支持real和int、real和bit数据类型之间的互相转换。real_data为任意real类型的数据,调用$rtoi(real_data)函数将返回real_data转换为int类型后的数据。int_data为任意int类型的数据,调用$itor(int_data)函数将返回int_data转换为real类型后的数据。real_data为任意real类型的数据,调用$realtobits(real_data)函数将返回real_data转换为64位二进制寄存器类型后的数据。bits_data为任意64位二进制寄存器类型的数据,调用$bitstoreal(bits_data)函数将返回bits_data转换为real类型后的数据。

示例代码如下:

`timescale 1ns/1psmodule testbench_top();integer int_a=108;

real real_a=59.23;

integer int_b;

real real_b;initial beginint_b = $rtoi(real_a);real_b = $itor(int_a);$display("int_b=$rtoi(real_a) = $rtoi(%0f) = %0d", real_a, int_b);$display("real_b=$itor(int_a) = $itor(%0d) = %0f", int_a, real_b);$stop;

endendmodule11.随机数生成$random

每次调用系统函数$random(seed)都可以产生一个新的32位随机数。如果不设置seed,则每次取得的随机数都是相同的。也就是说,$random所产生的随机数,其实对于系统而言,不过是提前预设好的32位数据数组而已。使用$random产生的随机数,在seed一致的情况下,都是调用了系统中预设的同一套数据数组,因此它们的值总是一致的。示例代码如下:

reg [23:0] rand;rand = $random % 100; // 产生一个-99~99范围内的随机数reg [23:0] rand;rand = {$random} % 100; // 通过位拼接操作产生0~99范围的随机数,添加位拼接会认为是random[23]...random[0]拼接而成reg [23:0] rand;rand = min + {$random} % (max - min + 1); //产生一个在min,max之间的随机数12.显示任务$display和$write

系统显示任务$display和$write在仿真测试中是最为常用的信息显示方式。$display和$write任务最主要的区别在于,$display在一次输出后自动换行,而$write则不会,其余用法基本类似。其语法结构如下:

![]()

任务名可以是$display、$displayb、$displayo、$displayh、$write、$writeb、$writeo或$writeh。格式由%和格式字符组成,信号为要显示的信号名,信号数量和格式数量必须对应。若不指定显示信号的格式,即使用$display或$write,则信号现实的格式会默认为十进制,其余类似。下面给出可用输出格式列表以及一些常用的特殊字符如下:

示例代码如下:

`timescale 1ns/1nsmodule testbench_top();reg [31:0] rval;initial beginrval=101;$display("rval = %h hex %d decimal", rval, rval);$display("rval = %0h hex %0d decimal", rval, rval);$display("rval = %o octal \n %b bin", rval, rval);$display("rval has %c ascii character valuel", rval);$display("current scope is %m");$display("%s is ascii value for 101", 101);#101;$display("Simulation time is %t", $time);$stop;endendmodule运行结果如下:

注意,除了十进制显示之外,高位的0会默认以空格填充,其他进制显示时会将高位的0显示出来。在%和格式字符之间可以添加数字0,就可以隐藏前置的0或空格,是的第一个非0数字顶格显示。

13.监视任务$monitor

系统监视任务$monitor在仿真测试脚本中可以实现对任何变量或表达式取值的监视和显示。$monitor语法结构以及用法都与$display类似。当$monitor任务中包含一个或多个监控信号并运行时,若参数列表中有任何的变量或表达式的值发生变化,则所有参数列表中的信号值都将输出并显示。同一时刻,若两个或多个参数的值同时发生变化,则此时将会合并一次输出并显示。$monitor任务在申明后默认开启,在其运行器件,若调用系统任务$monitoroff,则关闭$monitor,直到调用系统任务$monitoron后将重新开启$monitor。其语法结构如下:

![]()

示例代码如下:

initial begin@(posedge rst_n);$display("o_cnt is %d at %0dns", o_cnt, $time);

endalways @(posedge clk) beginif (o_cnt == 4'd5) $monitoroff;else if(o_cnt == 4'd12) $monitoron;

end14.仿真终止$finish和$stop

系统任务$finish被调用时将会退出仿真工具并返回操作系统。其语法结构如下:

![]()

系统任务$stop被调用时,仿真工具被挂起,仿真运行停止。语法结构与num取值与$finish一样。

End!

相关文章:

Verilog语法之常用行为级语法

摘要:本文主要介绍了一些在verilog中的行为级语法,并且提供了大量的运行实际例子,可以通过这些例子感受行为级语法在仿真中的巨大作用。 概述:行为级语法是RTL级的上一层,或者说是比RTL级更高级的语法,其语…...

PADS Logic原理图中有很多页原理图,如何(怎样)删除其中一页或者多页

我们在进行PADS Logic进行原理图设计的时候,有时候可能遇到一次性设计了很多页的原理图,比如说十几页的原理图。那么我们在进行PADS Layout的时候,可能将这些原理图绘制两块板或者多块PCB板,那么这时候我们需要将其中的一张原理图…...

蓝色简洁引导页网站源码

一款蓝色的简洁引导页,适合资源分发和网站备用引导。 1.源码上传至虚拟机或者服务器 2.绑定域名和目录 3.访问域名安装 4.安装完成后就行了 https://pan.quark.cn/s/b2d8b9c5dc7f https://pan.baidu.com/s/17h1bssUNhhR9DMyNTc-i9Q?pwd84sf https://caiyun.139.com…...

Apache PDFBox添加maven依赖,pdf转成图片

要使用Apache PDFBox将PDF文件转换为图片,并将其添加到Maven项目中,您可以按照以下步骤操作: 1. 添加Maven依赖 在您的pom.xml文件中添加Apache PDFBox的依赖。请确保使用最新版本的PDFBox库。截至2025年,以下是推荐的配置&…...

mybatis 和 mybatisPlus 兼容性问题

项目采用的是 mybatis, 后续引入了 mybatisPlus,用 mybatisX 创建的四个类一直报错,提示找不到符号,意识到 mybatis 和 mybatisPlus 的兼容性问题,通过修改配置 两者的配置如下 #配置mybatis配置 mybatis:type-aliase…...

Mono里运行C#脚本23—mono_jit_exec

前面已经分析一部分代码,可以打下基础知识,当然还有很多其它部分的内容,没有深入去了解。 接着下来,我们去探索一下怎么样找到执行应用程序的入口。 在这个嵌入脚本程序里,有一个这样的函数调用: main_function (domain, file, argc - 1, argv + 1); 这个函数的作用,…...

第十一章 图论

/* * 题目名称:连通图 * 题目来源:吉林大学复试上机题 * 题目链接:http://t.cn/AiO77VoA * 代码作者:杨泽邦(炉灰) */#include <iostream> #include <cstdio>using namespace std;const int MAXN 1000 10;int fathe…...

纯前端实现将pdf转为图片(插件pdfjs)

需求来源 预览简历功能在移动端,由于用了一层iframe把这个功能嵌套在了app端,再用一个iframe来预览,只有ios能看到,安卓就不支持,查了很多资料和插件,原理基本上都是用iframe实现的。最终转换思路…...

【IT人物系列】之MySQL创始人

前言 当今世界有无数的人构成,其中有些人做了一些改变世界的事情,比如:乔布斯缔造了Apple帝国,詹姆斯高斯林创造了Java语言等。正是这些优秀的人做的这些优秀的事情,让这个世界更加美好。因此他们值得铭记。 从今天…...

在Typora中实现自动编号

文章目录 在Typora中实现自动编号1. 引言2. 准备工作3. 自动编号的实现3.1 文章大纲自动编号3.2 主题目录(TOC)自动编号3.3 文章内容自动编号3.4 完整代码 4. 应用自定义CSS5. 结论 在Typora中实现自动编号 1. 引言 Typora是一款非常流行的Markdown编辑…...

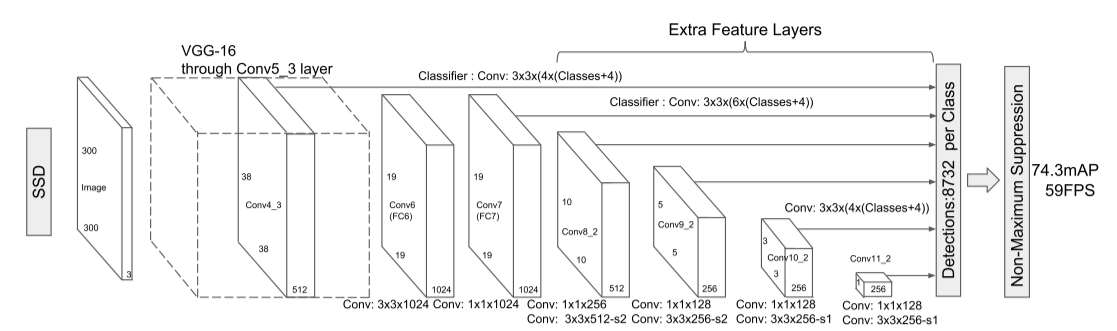

Single Shot MultiBox Detector(SSD)

文章目录 摘要Abstract1. 引言2. 框架2.1 网络结构2.2 损失函数2.3 训练细节 3. 创新点和不足3.1 创新点3.2 不足 参考总结 摘要 与Faster R-CNN相比,SSD是一个真正的单阶段多目标检测模型,同时也是一个全卷积网络,不仅检测准确率高ÿ…...

kafka生产者专题(原理+拦截器+序列化+分区+数据可靠+数据去重+事务)

目录 生产者发送数据原理参数说明代码示例(同步发送数据)代码示例(异步) 异步和同步的区别同步发送定义与流程特点 异步发送定义与流程特点 异步回调描述代码示例 拦截器描述代码示例 消息序列化描述代码示例(自定义序…...

【React+TypeScript+DeepSeek】穿越时空对话机

引言 在这个数字化的时代,历史学习常常给人一种距离感。教科书中的历史人物似乎永远停留在文字里,我们无法真正理解他们的思想和智慧。如何让这些伟大的历史人物"活"起来?如何让历史学习变得生动有趣?带着这些思考&…...

公共数据授权运营系统建设手册(附下载)

在全球范围内,许多国家和地区已经开始探索公共数据授权运营的路径和模式。通过建立公共数据平台,推动数据的开放共享,促进数据的创新应用,不仅能够提高政府决策的科学性和公共服务的效率,还能够激发市场活力࿰…...

基于HTML和CSS的旅游小程序

一、技术基础 HTML(HyperText Markup Language):超文本标记语言,用于定义网页的内容和结构。在旅游小程序中,HTML用于搭建页面的基本框架,包括标题、段落、图片、链接等元素,以及用于交互的表单…...

maven之插件调试

当使用maven进行项目管理的时候,可能会碰到一些疑难问题。网上资料很少,可能会想着直接调试定位问题。这里以maven-compiler-plugin为例: (1)准备maven-compiler-plugin源码 进入maven 官网-》Maven Plugins-》找到对…...

SQL Sever 数据库损坏,只有.mdf文件,如何恢复?

SQL Sever 数据库损坏,只有.mdf文件,如何恢复 在SQL Server 2008中,如果只有MDF文件而没有LDF文件,附加数据库的过程会稍微复杂一些。以下是几种可能的方法 一、使用紧急模式重建日志文件 1、新建一个同名的数据库。 2、停止SQ…...

【AWS SDK PHP】This operation requests `sigv4a` auth schemes 问题处理

使用AWS SDK碰到的错误,其实很简单,要装个扩展库 保持如下 Fatal error: Uncaught Aws\Auth\Exception\UnresolvedAuthSchemeException: This operation requests sigv4a auth schemes, but the client currently supports sigv4, none, bearer, sigv4-…...

primevue的<Menu>组件

1.使用场景 2.代码 1.给你的menu组件起个引用名 2.<Menu>组件需要一个MenuItem[] 3.你要知道MenuItem[ ]的特殊的数据格式,就像TreeNode[ ]一样,数据格式不对是不渲染的。。。。 常用的属性就这几种,js语言和java不一样,J…...

利用Deeplearning4j进行 图像识别

目录 图像识别简介 神经网络 感知器 前馈神经网络 自动编码器 受限玻尔兹曼机 深度卷积网络 理解图像内容以及图像含义方面,计算机遇到了很大困难。本章先介绍计算机理解图像教育方面 遇到的难题,接着重点讲解一个基于深度学习的解决方法。我们会…...

GBase 8s ER 影子列解析

影子列是复制的表上被隐藏的列,其包含由数据库服务器提供的值。数据库服务器使用影子列来执行内部操作。可以 CREATE TABLE 或 ALTER TABLE 语句来将影子列添加至复制的表。 要查看影子列的内容,必须在 SELECT 语句的投影列表中显式地指定该列࿱…...

如何突破Windows应用程序的尺寸限制?WindowResizer的底层技术解析与应用实践

如何突破Windows应用程序的尺寸限制?WindowResizer的底层技术解析与应用实践 【免费下载链接】WindowResizer 一个可以强制调整应用程序窗口大小的工具 项目地址: https://gitcode.com/gh_mirrors/wi/WindowResizer 在Windows生态系统中,应用程序…...

)

Windows 10 下 Node.js 16.15.1 保姆级安装与环境变量配置(含 npm 报错解决)

Windows 10 下 Node.js 16.15.1 完整安装与深度配置指南 对于刚接触 Node.js 开发的 Windows 用户来说,从零开始搭建开发环境往往会遇到各种"坑"。本文将带你一步步完成 Node.js 16.15.1 LTS 版本的安装、环境变量配置以及常见问题的解决方案,…...

Degrees of Lewdity汉化版完整指南:5分钟完成中文游戏配置

Degrees of Lewdity汉化版完整指南:5分钟完成中文游戏配置 【免费下载链接】Degrees-of-Lewdity-Chinese-Localization Degrees of Lewdity 游戏的授权中文社区本地化版本 项目地址: https://gitcode.com/gh_mirrors/de/Degrees-of-Lewdity-Chinese-Localization …...

)

别再被XML命名空间坑了!手把手教你用JAXB解析带命名空间的XML(附完整代码)

深度解析JAXB处理XML命名空间的五种实战方案 金融报文、Web服务响应、企业级数据交换——在这些需要处理标准化XML格式的场景中,命名空间就像一把双刃剑。它本是为了解决元素命名冲突而设计,却常常成为Java开发者使用JAXB解析时的"拦路虎"。当…...

CVAT、LabelImg、Labelme怎么选?一文讲清不同标注工具的核心差异与适用场景

CVAT、LabelImg、Labelme深度对比:如何根据项目需求选择最佳标注工具 在计算机视觉项目的生命周期中,数据标注往往占据了70%以上的时间成本。面对市面上五花八门的标注工具,很多团队常常陷入"选择困难症":功能全面的工具…...

FutureRestore-GUI:iOS设备降级恢复的专业图形化工具完整指南

FutureRestore-GUI:iOS设备降级恢复的专业图形化工具完整指南 【免费下载链接】FutureRestore-GUI A modern GUI for FutureRestore, with added features to make the process easier. 项目地址: https://gitcode.com/gh_mirrors/fu/FutureRestore-GUI Futu…...

如何彻底告别城通网盘下载限速:3种创新方案对比分析

如何彻底告别城通网盘下载限速:3种创新方案对比分析 【免费下载链接】ctfileGet 获取城通网盘一次性直连地址 项目地址: https://gitcode.com/gh_mirrors/ct/ctfileGet 还在为城通网盘那令人抓狂的下载速度而烦恼吗?ctfileGet 是一个开源工具&…...

如何用Obsidian微信读书插件3步构建个人知识库

如何用Obsidian微信读书插件3步构建个人知识库 【免费下载链接】obsidian-weread-plugin Obsidian Weread Plugin is a plugin to sync Weread(微信读书) hightlights and annotations into your Obsidian Vault. 项目地址: https://gitcode.com/gh_mirrors/ob/obsidian-were…...

Kerberos运维踩坑实录:从JDK版本到DNS解析,这10个报错我帮你趟平了

Kerberos运维深度排错指南:十大典型故障场景与根治方案 凌晨三点,告警铃声划破寂静——"Client cannot authenticate via:[TOKEN, KERBEROS]"的红色警报在监控屏上闪烁。作为大数据平台的核心认证网关,Kerberos的每次异常都可能引发…...