FPGA实现UART对应的电路和单片机内部配合寄存器实现的电路到底有何区别?

一、UART相关介绍

UART是我们常用的全双工异步串行总线,常用TTL电平标准,由TXD和RXD两根收发数据线组成。

那么,利用硬件描述语言实现UART对应的电路和51单片机内部配合寄存器实现的电路到底有何区别呢?接下来我们对照看一下。

二、FPGA实现UART异步串行收发方式

对于FPGA而言,利用verilog实现这个过程,其实最重要的就是安排好对应的计数器并配合移位寄存器串并转换即可完成。

FPGA发送端对应的代码如下:

module uart_tx(input wire clk ,input wire rst_n ,input wire [7:0] pi_data ,input wire pi_flag ,output reg tx );reg [7:0] pi_data_reg;//用于寄存传进来的数据reg tx_flag ;reg [12:0] cnt_baud ;reg bit_flag1;reg [3:0] bit_cnt ;//在接收到pi_flag为高电平的时候寄存输入数?always@(posedge clk or negedge rst_n)beginif(!rst_n)pi_data_reg <= 'd0;else if(pi_flag == 1'b1)pi_data_reg <= pi_data ;endalways@(posedge clk or negedge rst_n)beginif(!rst_n)tx_flag <= 1'b0;else if(bit_flag1 == 1'b1 && bit_cnt == 'd8)tx_flag <= 1'b0;else if(pi_flag == 1'b1)tx_flag <= 1'b1;end always@(posedge clk or negedge rst_n)beginif(!rst_n)cnt_baud <= 'd0;else if(tx_flag == 1'b0)cnt_baud <= 'd0;else if(cnt_baud == 'd5207 && tx_flag == 1'b1)cnt_baud <= 'd0;else if(tx_flag == 1'b1)cnt_baud <= cnt_baud + 1'b1;endalways@(posedge clk or negedge rst_n)beginif(!rst_n)bit_flag1 <= 1'b0;else if(cnt_baud == 5206)bit_flag1 <= 1'b1;else bit_flag1 <= 1'b0;endalways@(posedge clk or negedge rst_n)beginif(!rst_n)bit_cnt <= 'd0;else if(bit_cnt == 'd8 && bit_flag1 == 1'b1)bit_cnt <= 'd0;else if(bit_flag1 == 1'b1)bit_cnt <= bit_cnt + 1'b1;end always@(posedge clk or negedge rst_n)beginif(!rst_n)tx <= 1'b1;//空闲状态else if(pi_flag == 1'b1)tx <= 1'b0;//起始?else if(bit_flag1 == 1'b1 && bit_cnt <= 'd7)tx <= pi_data_reg[bit_cnt];//8位数?else if(bit_cnt == 'd8 && bit_flag1 == 1'b1)tx <= 1'b1;//空闲?end

endmodule

FPGA接收端对应的代码如下:

module uart_rx(input wire clk ,input wire rst_n ,input wire rx ,output reg [7:0] po_data ,output reg po_flag);//用于打拍的寄存器reg rx1;reg rx2;reg rx2_reg ;reg rx_flag ;reg [12:0] cnt_baud ;reg bit_flag ;reg [3:0] bit_cnt ;//对接收到的外部信号进行打拍寄存always@(posedge clk)beginrx1 <= rx ;rx2 <= rx1 ;rx2_reg <= rx2 ;end//检测下降沿,拉高rx_flagalways @(posedge clk or negedge rst_n) beginif (!rst_n) beginrx_flag <= 1'b0;endelse if (rx2 == 1'b0 && rx2_reg == 1'b1) beginrx_flag <= 1'b1;endelse if(bit_flag == 1'b1 && bit_cnt == 'd8)rx_flag <= 1'b0;endalways @(posedge clk or negedge rst_n) beginif (!rst_n) cnt_baud <= 'd0;else if(rx_flag == 1'b0)cnt_baud <= 'd0;else if(cnt_baud == 'd5207 && rx_flag == 1'b1)//5207为波特率是9600时对应的计数值cnt_baud <= 'd0;else if(rx_flag == 1'b1)cnt_baud <= cnt_baud + 1'b1;endalways @(posedge clk or negedge rst_n) beginif (!rst_n) bit_flag <= 1'b0;else if(cnt_baud == 'd2603 && rx_flag == 1'b1)bit_flag <= 1'b1;else bit_flag <= 1'b0;end always @(posedge clk or negedge rst_n) beginif (!rst_n) bit_cnt <= 'd0;else if(bit_cnt == 'd8 && bit_flag == 1'b1)bit_cnt <= 'd0;else if(bit_flag == 1'b1 && rx_flag == 1'b1)bit_cnt <= bit_cnt + 1'b1;endalways @(posedge clk or negedge rst_n) beginif (!rst_n) po_data <= 'd0;else if(bit_flag == 1'b1 && bit_cnt >= 'd1)po_data <= {rx2_reg,po_data[7:1]};end always @(posedge clk or negedge rst_n) beginif (!rst_n) po_flag <= 1'b0 ;else if(bit_flag == 1'b1 && bit_cnt == 'd8)po_flag <= 1'b1 ;else po_flag <= 1'b0;endendmodule

顶层代码如下:

module top_uart(input wire clk ,input wire rst_n ,input wire rx ,output wire tx);wire [7:0] po_data ;wire po_flag ;uart_rx inst_uart_rx (.clk(clk), .rst_n(rst_n), .rx(rx), .po_data(po_data), .po_flag(po_flag));uart_tx inst_uart_tx (.clk(clk), .rst_n(rst_n), .pi_data(po_data), .pi_flag(po_flag), .tx(tx));endmodule

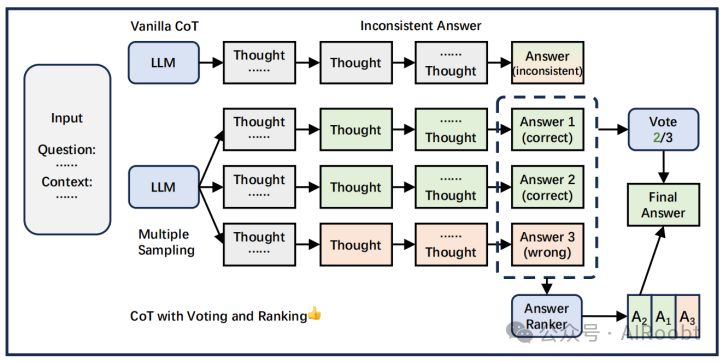

经过综合后,生成的对应原理图如下:

顶层:

tx:可以发现,这里其实每一位寄存器都对应着一个D触发器,剩余的逻辑由LUT实现。

rx:接收端同理。

三、单片机内部UART异步串行收发实现方式

对于51单片机而言,它内部是CPU控制一些在物理层面已经连接好寄存器,通过对寄存器的控制配合电路的改变完成整个任务。

对于串口通信这个任务而言,它的整个实现过程总结如下:

整个实现可分为三大部分,定时器、中断系统及对应的缓冲寄存器完成,三大部分配合内部CPU便可完成收发任务,具体示意图如下:

红色区域是定时器部分,它外部连接着晶振,通过对TH1和TL1寄存器写入初始值可实现具体溢出频率的控制,假设晶振频率位12MHz(12T模式下1us计数一次),TH1和TL1填入0xF3(对应十进制243),一共256,则每隔256-243=13个数就会溢出一次,则溢出率为1/13us=0.07692MHz,当SMOD=1时,频率只经过➗16也就对应4800Hz,就会对应波特率4800Baud。配合控制器即可完成对波特率的控制。

蓝色部分是用于发送和接收数据的缓冲区;

黄色部分是串口中断器,这个中断器在接收数据的时候需要使用,TI和RI是中断标志。

在使用方式上,对涉及的寄存器进行初始化后,将数据写入SBUF或通过中断读取SBUF内的数据即可完成发送接收任务。

对应配置代码如下:

#include <REGX51.H>/*** @brief 串口初始化,4800bps@11.0592MHz* @param 无 * @retval 无*/

void UART_Init()

{//对串行寄存器配置SCON=0x50; //串行控制寄存器,涉及模式选择PCON &= 0x7F; //电源控制寄存器(包括波特率)//对定时器0进行配置#11.0592MTMOD &= 0x0F; //设置定时器模式,低4位保持不变TMOD |= 0x20; //设置定时器模式,串口对应的模式需要是双8位模式TL1 = 0xFA; //设定定时初值TH1 = 0xFA; //设定定时器重装值ET1 = 0; //禁止定时器1中断TR1 = 1; //启动定定时器1//串口中断配置EA=1;//启动所有中断ES=1;//启动串口中断

}

/*** @brief 串口发送1个字节数据,4800bps@11.0592MHz* @param Byte 要发送的一个字节数据* @retval 无*/

void UART_SendByte(unsigned char Byte)

{SBUF=Byte;//将数据写入发送缓冲器即可while(TI==0);//是否有中断请求位TI=0;//软件置0

}//串口中断函数的模板,需要用的时候复制到主函数中

/*

//注意:一个函数不能既在主函数中出现,又在中断函数中出现

void UART_Routine() interrupt 4 //串口中断对应的中断号

{if(RI==1)//接收到了串口中断{P2=~SBUF;UART_SendByte(SBUF);RI=0;//需要由软件清0}}

*/主函数代码如下:

#include <REGX51.H>

#include "Delay.h"

#include "UART.h"void main()

{UART_Init();while(1){}

}//注意:一个函数不能既在主函数中出现,又在中断函数中出现

void UART_Routine() interrupt 4 //串口中断对应的中断号

{if(RI==1)//接收到了串口中断{P2=~SBUF;UART_SendByte(SBUF);RI=0;//需要由软件清0}}四、总结

均由寄存器加逻辑电路组成,只不过二者工作模式及灵活性差别很大,单片机依赖冯诺依曼架构需要控制器控制且电路固定(使得定时器、寄存器等资源有限),FPGA的并行及灵活性在这里体现的淋漓尽致。

相关文章:

FPGA实现UART对应的电路和单片机内部配合寄存器实现的电路到底有何区别?

一、UART相关介绍 UART是我们常用的全双工异步串行总线,常用TTL电平标准,由TXD和RXD两根收发数据线组成。 那么,利用硬件描述语言实现UART对应的电路和51单片机内部配合寄存器实现的电路到底有何区别呢?接下来我们对照看一下。 …...

数据库模型全解析:从文档存储到搜索引擎

目录 前言1. 文档存储(Document Store)1.1 概念与特点1.2 典型应用1.3 代表性数据库 2. 图数据库(Graph DBMS)2.1 概念与特点2.2 典型应用2.3 代表性数据库 3. 原生 XML 数据库(Native XML DBMS)3.1 概念与…...

【Java基础】Java异常捕捉,throws/throw、finally、try、catch关键字的含义与运用

1. Java 异常处理: 异常是程序中的一些错误,但并不是所有的错误都是异常,并且错误有时候是可以避免的。 比如说,你的代码少了一个分号,那么运行出来结果是提示是错 java.lang.Error;如果你用System.out.p…...

Android Studio 安装配置(个人笔记)

Android studio安装的前提是必须保证安装了jdk1.8版本以上 一、查看是否安装jdk cmd打开命令行,输入java -version 最后是一个关键点 输入 javac ,看看有没有相关信息 没有就下载jdk Android studio安装的前提是必须保证安装了jdk1.8版本以上 可以到…...

计算机网络——数据链路层-介质访问控制

一、介质访问控制方法 在局域网中, 介质访问控制(medium access control)简称MAC,也就是信道访问控制方法,可以 简单的把它理解为如何控制网络节点何时发送数据、如何传输数据以及怎样在介质上接收数据, 是解决当局域网中共用信道的使用产生竞…...

pytest日志显示

在 pytest 中,可以通过 钩子函数 和 配置文件 pytest.ini 配置日志的显示方式,实现对日志的灵活控制。以下是常用实现方式及配置说明。 方式一:使用 conftest.py 钩子函数自定义日志显示 通过 conftest.py 文件中的钩子函数,实现…...

【信息系统项目管理师】第15章:项目风险管理过程详解

更多内容请见: 备考信息系统项目管理师-专栏介绍和目录 文章目录 一、规划风险管理1、输入2、工具与技术3、输出二、识别风险1、输入2、工具与技术3、输出三、实施定性风险分析1、输入2、工具与技术3、输出四、实施定量风险分析1、输入2、工具与技术3、输出五、规划风险应对1、…...

Diffusers 使用 LoRA

使用diffusers 加载 LoRA,实现文生图功能。摘自 diffusers文档。 模型可以根据名称去modelscope找对应资源下载。使用的时候需要替换成具体路径。虽然modelscope和diffusers都使用了模型id,但是并不能通用。 不同的LoRA对应了不同的“trigger” words&am…...

云安全博客阅读(二)

2024-05-30 Cloudflare acquires BastionZero to extend Zero Trust access to IT infrastructure IT 基础设施的零信任 不同于应用安全,基础设置的安全的防护紧急程度更高,基础设施的安全防护没有统一的方案IT基础设施安全的场景多样,如se…...

SpringCloud系列教程:微服务的未来(六)docker教程快速入门、常用命令

对于开发人员和运维工程师而言,掌握 Docker 的基本概念和常用命令是必不可少的。本篇文章将带你快速入门 Docker,并介绍一些最常用的命令,帮助你更高效地进行开发、测试和部署。 目录 前言 快速入门 docker安装 配置镜像加速 部署Mysql …...

Vue 快速入门:开启前端新征程

在当今的 Web 开发领域,Vue.js 作为一款极具人气的 JavaScript 前端框架,正被广泛应用于各类项目之中。它以简洁的语法、高效的数据绑定机制以及强大的组件化开发模式,为开发者们带来了前所未有的开发体验。如果你渴望踏入前端开发的精彩世界…...

UVM:uvm_component methods configure

topic UVM component base class uvm_config_db 建议使用uvm_config_db代替uvm_resource_db uvm factory sv interface 建议:uvm_config_db 以下了解 建议打印error...

LLM 训练中存储哪些矩阵:权重矩阵,梯度矩阵,优化器状态

LLM 训练中存储哪些矩阵 目录 LLM 训练中存储哪些矩阵深度学习中梯度和优化器是什么在 LLM 训练中通常会存储以下矩阵: 权重矩阵:这是模型的核心组成部分。例如在基于 Transformer 架构的 LLM 中,每一层的多头注意力机制和前馈神经网络都会有相应的权重矩阵。以 BERT 模型为…...

大模型思维链推理的进展、前沿和未来分析

大模型思维链推理的综述:进展、前沿和未来 "Chain of Thought Reasoning: A State-of-the-Art Analysis, Exploring New Horizons and Predicting Future Directions." 思维链推理的综述:进展、前沿和未来 摘要:思维链推理&#…...

NLP 技术的突破与未来:从词嵌入到 Transformer

在过去的十年中,自然语言处理(NLP)经历了深刻的技术变革。从早期的统计方法到深度学习的应用,再到如今Transformer架构的普及,NLP 的发展不仅提高了模型的性能,还扩展了其在不同领域中的应用边界。 1. 词嵌…...

嵌入式中QT实现文本与线程控制方法

第一:利用QT进行文件读写实现 利用QT进行读写文本的时候进行读写,读取MP3歌词的文本,对这个文件进行读写操作。 实例代码,利用Qfile,对文件进行读写。 //读取对应文件文件,头文件的实现。 #ifndef MAINWINDOW_H #define MAINWINDOW_H#include <QMainWindow> #incl…...

云备份项目--服务端编写

文章目录 7. 数据管理模块7.1 如何设计7.2 完整的类 8. 热点管理8.1 如何设计8.2 完整的类 9. 业务处理模块9.1 如何设计9.2 完整的类9.3 测试9.3.1 测试展示功能 完整的代码–gitee链接 7. 数据管理模块 TODO: 读写锁?普通锁? 7.1 如何设计 需要管理…...

Node.js——fs(文件系统)模块

个人简介 👀个人主页: 前端杂货铺 🙋♂️学习方向: 主攻前端方向,正逐渐往全干发展 📃个人状态: 研发工程师,现效力于中国工业软件事业 🚀人生格言: 积跬步…...

SAP BC 同服务器不同client之间的传输SCC1

源配置client不需要释放 登录目标client SCC1...

CentOS: RPM安装、YUM安装、编译安装(详细解释+实例分析!!!)

目录 1.什么是RPM 1.1 RPM软件包命名格式 1.2RPM功能 1.3查询已安装的软件:rpm -q 查询已安装软件的信息 1.4 挂载:使用硬件(光驱 硬盘 u盘等)的方法(重点!!!) 1…...

)

⾃动化测试常⽤函数(下)

等待通常代码执⾏的速度⽐⻚⾯渲染的速度要快,如果避免因为渲染过慢出现的⾃动化误报的问题呢?可 以使⽤selenium中提供的三种等待⽅法:强制等待Thread.sleep()优点:使⽤简单,调试的时候⽐较有效…...

)

大模型落地总卡在“最后一公里”?SITS2026揭示5级成熟度断层,92%企业尚处L2以下(附自测清单)

第一章:SITS2026发布:大模型工程化成熟度模型 2026奇点智能技术大会(https://ml-summit.org) SITS2026(Software Intelligence & Trustworthiness Standard 2026)正式发布首个面向大模型全生命周期的工程化成熟度模型&#…...

如何快速掌握文本差异对比:Diff Checker完整使用指南

如何快速掌握文本差异对比:Diff Checker完整使用指南 【免费下载链接】diff-checker Desktop application to compare text differences between two files (Windows, Mac, Linux) 项目地址: https://gitcode.com/gh_mirrors/di/diff-checker 文本差异对比是…...

DeepSeek-OCR-2部署教程:Prometheus+Grafana OCR服务监控看板搭建

DeepSeek-OCR-2部署教程:PrometheusGrafana OCR服务监控看板搭建 1. 引言 如果你正在使用DeepSeek-OCR-2(深求墨鉴)这款文档解析工具,可能会遇到这样的问题:服务运行是否稳定?处理速度怎么样?…...

Flutter ClipRRect

ClipRRect 是 Flutter 中用于将子组件裁剪为圆角矩形的核心 Widget,常用于实现图片、容器、卡片的圆角效果。一、核心属性dartconst ClipRRect({Key? key,BorderRadiusGeometry borderRadius BorderRadius.zero, // 圆角CustomClipper<RRect>? clipper, …...

Lumafly:让空洞骑士模组管理变得像呼吸一样简单

Lumafly:让空洞骑士模组管理变得像呼吸一样简单 【免费下载链接】Lumafly A cross platform mod manager for Hollow Knight written in Avalonia. 项目地址: https://gitcode.com/gh_mirrors/lu/Lumafly 还在为空洞骑士模组安装的繁琐流程而烦恼吗…...

Visualized BGE批量推理实战:如何用Python代码将图片编码速度提升3倍

Visualized BGE批量推理实战:如何用Python代码将图片编码速度提升3倍 在当今多模态AI应用爆炸式增长的时代,高效处理图像嵌入已成为开发者面临的普遍挑战。Visualized BGE作为支持中文的多模态嵌入模型,其性能优化直接关系到实际业务落地的可…...

Windows平台微信/QQ/TIM防撤回补丁完整使用指南:如何实现消息保护与多开功能

Windows平台微信/QQ/TIM防撤回补丁完整使用指南:如何实现消息保护与多开功能 【免费下载链接】RevokeMsgPatcher :trollface: A hex editor for WeChat/QQ/TIM - PC版微信/QQ/TIM防撤回补丁(我已经看到了,撤回也没用了) 项目地址…...

Java中ThreadPoolExecutor 深度剖析

ThreadPoolExecutor 深度剖析(基于Java 21) 这是 JUC 中最核心、最复杂的并发组件之一。以下按维度逐一展开,辅以源码与图示。一、底层实现原理 1.1 核心控制字段:ctl ThreadPoolExecutor 用一个 AtomicInteger 类型的 ctl 字段同…...

)

实战指南 | 利用FRP与TOML配置实现高效内网穿透(含反向代理优化)

1. 为什么需要内网穿透? 想象一下这个场景:你家里有一台NAS存储设备,里面存满了家人照片和工作文档;或者你在本地开发了一个网站应用,想临时分享给异地同事测试。这时候你会发现——从外部网络根本无法访问这些服务&am…...